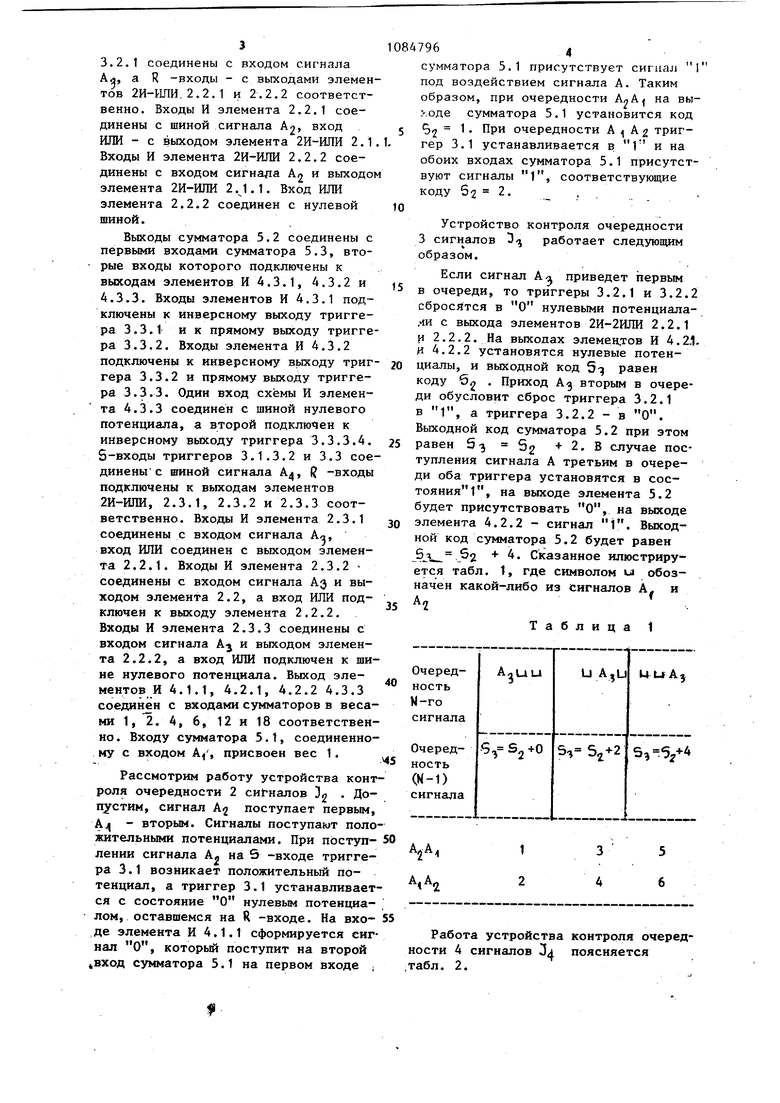

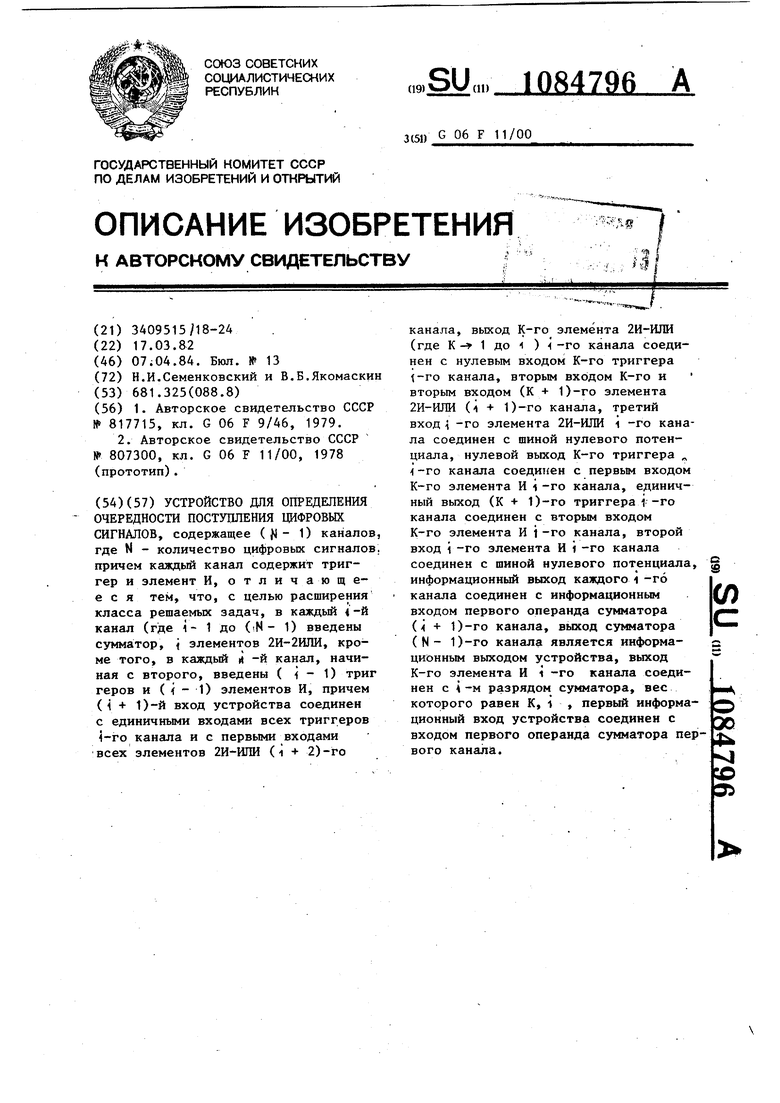

1 Изобретение относится к автомати ке и вычислительной технике и может быть использовано в устройствах для кодирования временных последователь ностей, устройствах для управления обслуживанием очередей, устройствах клавишного ввода-информации. Известно устройство контроля, содержащее элементы И, ИЛИ и инверто ры, служащее для определения сигнала, находящегося в очереди первым Недостатком данного устройства является неспособность его определять очередности сигналов, следующих за первым. Известно многоканальное устройст во для обслуживания запросов в поряд ке поступления, содержащее логические элементы и элементы памяти . Недостатком устройства является сложность и нерегулярность структуры Наиболее близким по технической сущности к изобретению является устройство для определения очереднос ти поступлениях цифровых сигналов, содержащее триггеры, инверторы, элементы И. При определенной очередности N сигналов на N выходах схемы присутствуют высокие потенциалы, что свидетельствует о правильности данной очередности. Недостатком известного устройства является неспособность его контролировать все очередности поступления команд. Целью изобретения является расширение класса решаемых задач. Поставленная цель достигается тем, что в устройство для определения очередности поступления цифровых сигналов, содержащее ( N- 1) каналов, где N - количество цифровых сигналов, причем каждьй канал содержит первый триггер и первый элемент И, в каждый и-и канал (где - 1 до (М- 1) введены сумматор, элементов 2И-ИЖ, кроме того, в каждый i-и.канал, начиная с второго, введены ( 1 - 1) триггеров и ( - 1) элементов И, причем (i + 1)-й вход уст ройства соединен с единичными входами всех триггеров i -го канала и с первыми входами всех элементов 2ИИЛИ ( + 2)-го канала,выход К-гр элемента 2И-ИЛИ ( где К - 1 до i ) -i-rc канала соединен с нулевым входом К-го триггера i-го канала, вторым входом К-го и вторым входном (К + 1)-го элемента 2И-ИЛИ ( + 1)-г 962 канала, третий вход i -го элемента 2И-ИЛИ 1 -го канала соединен с шиной нулевого потенциала, нулевой выход К-го триггера ц-го канала соединен с первым входом К-го элемента И 1-го канала, единичный выход (К+Отриггера -го канала соединен с вторьм входом К-го элемента И i -го канала, второй вход 11-го элемента И 1-го канала соединен с шиной нулевого потенциала, информационный выход каждого t-ro канала соединен с информационным входом первого операнда сумматора ( i + 1)-го канала, выход сумматора (К- 1)-го канала является информационным выходом устройства, выход К-го элемента И 4--го канала соединен с |-м разрядом сумматора, вес которого равен К , первый инфор мационный вход устройства соединен с входом первого сумматора первого канала. На чертеже представлена схема устройства. Предлагаемое устройство содержит устройства 1.4 контроля очередности двух, трех и четырех сигналов соответственно; элементы 2И-2ИЛИ 2.1 .1, 2.2.1, 2.2.2. Обозначения 2п.S. указывают, что это Е -и элемент, принадлежащий П-му каналу f . Устг ройство также содержит RS -триггеры 3.1, 3.2.1, 3.2.2, элементы И 4. 1, 4.2.1, 4.2.2, сумматоры 5.1, 5.2, 5, выход 6 устройства. Входы сумматора 5.1 подключены к входу сигнала и к выходу элемента И 4.1.1, один вход которого соединен с шиной нулевого потенциала, а второй вход подключен к инверсному выходу RS -триггера 3.1,5 -выход которого соединен с входом сигнала А„, а R -вход подключен к выходу элемента элемента 2И-2ИЛИ 2.1.1, И-входы которого соединены с входом сигнала А, а Ш1И-вход - с входом нулевого потенциала. Выходы сумматора 5.1 соединены с ервыми входами сумматора 5.2, к торым входам которого подключены ыходы элементов И 4.2.1, 4.2.2. ходы элемента И 4.2.1 соединены с нверсным выходом триггера 3.2.1 и рямым выходом триггера 3.2.2. Один ход элемента И 4.2.2 соединен с шиой нулевого потенциала, а второй ход соединен с инверсным выходом риггера 3.2.2. 5 -входы триггеров 3.2.1 соединены с входом сигнала а R -входы - с выходами элементов 2И-ИЛИ.2.2.1 и 2.2.2 соответственно. Входы И элемента 2.2.1 соединены с шиной сигнала А2, вход ИЛИ - с выходом элемента 2И-ИПИ 2.1 Входы И элемента 2И-ИЛИ 2.2.2 соединены с входом сигнала f и выходом элемента 2И-ИЛИ 2.J.1. Вход ИЛИ элемента 2.2.2 соединен с нулевой шиной. Выходы сумматора 5.2 соединены с первыми входами сумматора 5.3, вторые входы которого подключены к выходам элементов И 4.3.1, А.3.2 и 4.3.3. Входы элементов И 4.3.1 подключены к инверсноь у выходу триггера 3.3.1 и к прямому выходу триггера 3.3.2. Входы элемента И 4.3.2 подключены к инверсному вькоду триг гера 3.3.2 и прямому выходу триггера 3.3.3. Один вход схемы И элемента 4.3.3 соединен с шиной нулевого потенциала, а второй подклю ен к инверсному выходу триггера 3.3.3.4. S-входы триггеров 3.1.3.2 и 3.3 сое динены с шиной сигнала Ад, ( -входы подключены к выходам элементов 2И-Ш1И, 2.3.1, 2.3.2 и 2.3.3 соответственно. Входы И элемента .1 соединены с входом сигнала Аа, вход ИЛИ соединен с выходом элемента 2.2.1. Входы И элемента 2.3.2 соединены с входом сигнала Ад и выходом элемента 2.2, а вход ИЛИ подключен к выходу элемента 2.2.2. Входы И элемента 2.3.3 соединены с входом сигнала А и выходом элемента 2.2.2, а вход ИЛИ подключен к ши не нулевого потенциала. Выход элементов И 4.1.1, 4.2.1, 4.2.2 4.3.3 соединен с входами сумматоров в весами 1,.4, 6, 12 и 18 соответствен но . Входу сумматора 5.1, соединенно му с входом , присвоен вес 1. Рассмотрим работу устройства конт роля очередности 2 сигналов Dg . Допустим, сигнал АЗ поступает первым А - вторым. Сигналы поступают поло жительными потенциалами. При поступлении сигнала А- на 5 -входе триггера 3 . 1 возникает положительный потенциал, а триггер 3.1 устанавливает ся с состояние О нулевым потенциалом, оставшемся на R -входе. На входе элемента И 4.1.1 сформируется сиг нал О, который поступит на второй «вход сумматора 5.1 на первом входе 7964 сумматора 5.1 присутствует сигнал Г под воздействием сигнала А. Таким образом, при очередности АяА на выходе сумматора 5.1 установится код 2 1 При очередности А А 2 триггер 3.1 устанавливается в Г и на обоих входах сумматора 5.1 присутствуют сигналы 1, соответствующие коду 52 2. , . Устройство контроля очередности 3 Э работает следующим образом. Если сигнал А а приведет первым в очереди, то триггеры 3.2.1 и 3.2.2 сбросится в О нулевыми потенциала,1и с выхода элементов 2И-2ШШ 2.2.1 и 2.2.2. На выходах элементов И 4.2.1. )и 4.2.2 установятся нулевые потенциалы, и выходной код 5- равен коду б . Приход АЗ вторым в очереди обусловит сброс триггера 3.2.1 в 1, а триггера 3.2.2 - в О. Выходной код сумматора 5.2 при этом равен 5з - 2 2. В случае поступления сигнала А третьим в очереди оба триггера установятся в состояния 1, на выходе элемента 5.2 будет присутствовать О, на выходе элемента 4.2.2 - сигнал 1. Выходной код сумматора 5.2 будет равен 6з 62 + 4. Сказанное илюстрируется табл. 1, где символом и обозначен какой-либо из сигналов А. и Таблица 1 Работа устройства контроля очередости 4 сигналов Л поясняется абл. 2.

Таблица 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОСНОВАННЫЙ НА ИНТЕРФЕРОМЕТРЕ САНЬЯКА РАСПРЕДЕЛЁННЫЙ ДАТЧИК РЕГИСТРАЦИИ ВИБРАЦИОННЫХ ВОЗДЕЙСТВИЙ С ПОВЫШЕННОЙ ТОЧНОСТЬЮ ОПРЕДЕЛЕНИЯ КООРДИНАТЫ ВОЗДЕЙСТВИЯ | 2020 |

|

RU2752686C1 |

| Устройство для обнаружения и исправления ошибок | 1987 |

|

SU1578811A1 |

| Пересчетное устройство | 1984 |

|

SU1228273A1 |

| Устройство для умножения матриц | 1991 |

|

SU1835548A1 |

| ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ ПО УОЛШУ С УПОРЯДОЧЕНИЕМ ПО АДАМАРУ | 1992 |

|

RU2072554C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ МАТРИЦ | 1990 |

|

RU2006937C1 |

| Способ и устройство автоматизированного структурирования мультикультурных учебных групп | 2016 |

|

RU2618387C1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| Устройство определения знака числа, представленного в системе остаточных классов | 2020 |

|

RU2747371C1 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОЧЕРЕДНОСТИ ПОСТУПЛЕНИЯ ЦИФРОВЫХ СИГНАЛОВ, содержащее

Таким о&разом, в основу раооты устройства контроля очередности дву сигналов заложена способность RS триггера (например, из элементов 2И-НЕ) переходить из исходного состояния 1 (R 0;5 О, 1, Q 1) в состоян ие 2 ( Q 1, Q 0 или 3(Q 0, Q 1)в зависимости от очередности поступления положительных потенциалов на входы R и 6. В свою очередь, в основе работы устройств контроля очередности fl сигналов лежит работа Я (N - 1) устройств контроля очередности 2 сиг налов. Н( N - 1) устройства сравиивают очередность прихода М-го сигнала и групп сочетаний из 2, 2 ... ...( N - 1) сигналов. Группы сочетаний формируются логическими 2И-2ЙПИ -из сигналов предьздущего ,младшего устройства контроля очередности, образуя рекурсивную структуру построения схемы. Рассмотрим, как формируется выходной сигнал 2 элементов 2.3.2, pea лизующей Группы сочетаний из трех сигналов по два члена (,лГ2;, 1) л 1 где 12, Г2, r2,j - выходные сигналы элементов 2И-2ИЛИ 2.3.2 2.2.2, 2.1.1. Для сигналов Г2- и Г2 можно записать 7 . .к. 1(2) Г2з Л2ЛГ21 Г2 Г22ЧД2, гдеГ2з А,.(А) Решая совместно уравнения (1) и (4), получаем r2 A,A2vA A-:jvA.iA3 Аналогично выводятся вьфажения для выходных сигналов остальных (олементов 2Й-ИЛИ. Таким образом, введение в каждьй канал сумматоров с соответствующими связями обеспечивает получение на выходе устройства кода, который однозначно указывает на очередность прихода цифровых сигналов.

Ag

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальное устройство дляОбСлужиВАНия зАпРОСОВ B пОРядКЕпОСТуплЕНия | 1979 |

|

SU817715A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля выполненияпОСлЕдОВАТЕльНОСТи дЕйСТВий ОпЕРАТОРА | 1978 |

|

SU807300A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-07—Публикация

1982-03-17—Подача