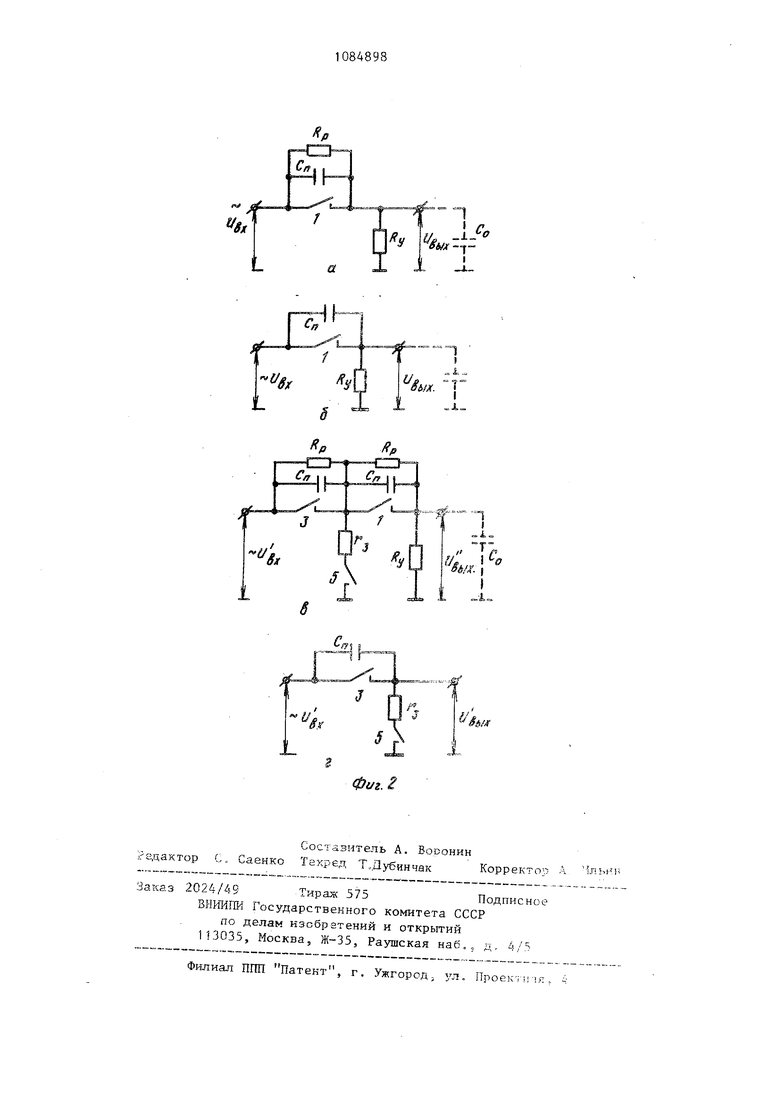

Изобретение относится к вычислительной т€;хнике и может быть исполь зовано в качестве входного устройст ва аналого-цифрового преобразовате ля для запоминания и хранения мгновенных значений напряжений, а также в схемах квантования аналоговьк сигналов по времени. Известно аналоговое запоминающее устройство, включающее в себя два входных операционных усилителя, три ключа, накопительньй элемент (конденсатор) и выходной операционный усилитель 11 : Однако данное устройство не в .полной мере снижает просачивание входного сигнала на накопительный элемент в режиме хранения напряжения. Наиболее близким к изобретению по технической сущности является аналоговое запоминающее устройствоj Содержащее два входных операционных усилителя, вторые входы которых являются входами.устройства, а первые входы соединены через пассивные элементы с выходами этих усилителей которые через первый и второй ключи соединены с разными обкладками накопительного элемента на конденсаторе, причем вьгход первого ключа соединен также с входом повторителя напряжения, выход которого соединен с первым входом дифференциального усилителя, а выход второго ключа со единен со вторым входом дифференциального усилителя, первый выход которого является выходом аналогового запоминающего устройства (АЗУ) С2. Недостатком известного устройств является то, что во время хранения конденсатором запомненного напряжения при разомкнутых первом и втором ключах вследствие наличия паразитной емкости между входом и выходом этих ключей при обработке скоростных динамических процессов появляется просачивание входного сигнала через разомкнутые ключи на обкладки ко1оденсатора5 Е результ те чего выходной сигнал АЗУ зависит в определенной степени от изменекия входного сигнала в режиме хра нения. Цель изобретения - повышение пом хозащищенности аналогового запомина щего устройства. Поставленная цель достигается те что в аналоговое запоминающее устройство, содержащее дифференциальный усилитель, выход которого является выходом устройства, накопительяьш элемент на конденсаторе, одна из обкладок которого соединена с первым входом дифференциального усилителя и с выходом первого ключа, второй ключ, выход которого соединен с другой обкладкой конденсатора, повторитель напряжения, шину управления и шину нулевого потенциала, введены элемент задержки, третий, четвертьш, пятый и шестой ключи,, первые входы первого, второго, третьего и четвертого ключей соединены с шиной управления, первые входы пятого и шестого ключей соединены с выходом элемента задержки, вход повторителя напряжения является входом устройства и соединен с вторым входом третьего ключа, выход которого соединен с вторыми входами первого И пятого ключей, выход повторителя напряжения соединен с вторым входом четвертого ключа, выход которого Соединен с вторыми входами второго и шестого ключей, выходы пятого и шестого ключей соединены с шиной нулевого потенциала, вход элемента задержки соединен с шиной управления, выход второго ключа соединен с вторым входом дифференциального ключа. На фиг, 1 изображена функциональная схема предложенного устройства; на фиг. 2 - эквивалентные схемы отдельных элементов известного и предложенного устройств. Устройство содержит ключи 1-6, элемент 7 задержки, накопительный элемент на конденсаторе 8, дифференциальный усилитель 9, повторитель 10 напряжения, шину 11 нулевого потенциала и шину 12 управления. Устройство работает следующим образом. Входной аналоговь й сигнал,, приходя на вход устройства, nccTiTsaeT непосредственно на второй вход ключа 3 и через повторитель 10 напряжения - на второй вход улглча 4. До прихода импульса выборки 3,451 и 2 разомкнуты, ключи 5 и 6 замкнуты, обкладки конденсатора 8 отключены от источников входного сигнала, Устройство находится в режиме хранения. Импульс выборки, поступающий на шину 12 управления, передним фронтом п)оизводит замыкание ключей 3,4,1 и 2 и размыкание ключей 5 и причем размыкание последних происходит с некоторой задержкой во времени по отношению к времени замыкания ключей 3,4,1 и 2, которая обеспечивается элементом 7 и равна задержке на распространение сигнал в ключах 1-6 (10-30 не). В момент импульса выборки напряжение на конденсаторе 8 следит за входным напряжением. Задним фронтом импульса выборки происходит ра мыкание ключей 3,4,1 и 2 и замыкание ключей 5 и 6. Аналоговое запоминающее устройство переходит в режим хранения. При этом ключи 3 и 4 предотвращают замыкание входно сигнала через открытые ключи 5 и 6 на шину 11. Напряжение с обкладок конденсатора В поступает на входы дифференциального усилителя Э с выхода которого снимается напряжение, которое запоминает конденсатор 8 в момент размыкания ключей 3,4,1 и 2. Наличие ключей Зи4, 5и6иих соединение с элементом 7 задержки и другими элементами позволяет улучщить помехозащищенность устройства. Действительно, при отсутствии ключей 3 и 4, 5 и 6 и разомкнутых ключаа 1 и 2 напряжение на конденса торе В подвержено не только влиянию токов утечки, обусловленных конечными значениями сопротивления диэлектрика конденсатора 8 и входного сопротивления дифференциального уси лителя 9, но и токов, обусловленных наличием паразитной емкости между входами и выходами разомкнутых ключей 1 и 2. Даже при незначительных паразитных емкостях, значения которых для полупроводниковых переключателей составляет несколько пикофарад, резкое изменение амплитуды напряжения на входе разомкнутого ключаS характерное для динамическкх процессов, ведет к просачива нию определенной части входного сиг нала на обкладку конденсатора 8, которое изменяет напряжения на нем Помеха от входного сигнала тем боль ще, чем въте скорость изменения и его динамичевходного напряжения ский диапазон. На фиг. 2а изображена эквивалентная схема одного ппеча известного устройства без входного операционного усилителя и выходного дифференциального каскада в режиме хранения напряжения (вторая обкладка конденсатора заземлена). На схеме обозначены паразитная емкость С между входом и выходом разомкнутого ключа; сопротивление (для полевых р разомкнутого ключ ); емкость контранзисторовС(з; сопротивление R,j , ранденсаторанее cy 4мapнoмy сопротивлению утечки и входного сопротивления дифференциального каскада. Простыми расчетами можно показать, что на частотах входного сигнала 2 .10, при Rp- 10 см иС Зпфток через паразитную емкость превышает ток через сопротивление разомкнутого ключа примерно на два порядка, поэтому можно считать, что ток через паразитную емкость является опреде- ляющим. При этом эквивалентная схема принимает вид, изображенный на фиг. Коэффициент передачи такой равен ивъ,х/и .). напряжение на конденсаторе в режиме хранения; напряжение на паразитной емкости разомкнутого ключа. Рассмотрим эквивалентную схему одного плеча предложенного устройства(фиг. 2в)5 также без входных и выходных цепей (вторая обкладка конденсатора 8 соединена с щиной нулевого потенциала), где гj - сопротивление замкнутого ключа (обычно 50 200 Ом для полупроводниковых переключателей) . Первая половина схемы фиг. 26 вдентична схеме фиг, 2а, поэтому рассмотрим левую половину этой схемы, которая с учетом того, что ток через паразитную емкость разомкнутого ключа является определяющим, принимает вид, представленный на фиг.2г. Коэффициент передачи этой схемы равен к uebis ЧГ Найдем отношение коэффициентов передачи схем, изображенных на фиг.26 и 2г, А Й ./MLLV к, Ug,; I ) Приняв, что входные напряжения равны для обеих схем, получим А l4t}L гз Э yJO Uftb.x UR Ъ Таким образомS наличие дополниteHbHbCc ключей 5 и 6, шунтирующих параэитн5по емкость (например, стокисток у полевых транзисторов), разомкнутых ключей 3,4, 1 и 2 на щину 11 уменьшает просачивание входного сигнала на конденсатор 8 на несколь ко порядков и исключает возможность влияния его на выходной сигнал устройства в режиме хранения. Кроме того, симметричная схема соединения ключей еще более улучшает его помехозащищенность. Наличие паразитной емкости между управляющим входом и цепью переключа

фг,1.

3AfX. емого сигнала почти у всех полупроводниковых переключателей приводит во время переключения к выбросам напряжения или тока. Однако в предложенном устройстве благодаря тому, что управляющие сигналы подаются на ключи 1 - 6 в противофазе, причем управляющий импульс, размь кающий ключи 5 и 6, поступает на них с определенной временной задержкой по отношению к времени прихода управляющего импульса, замыкающего ключи 1-4, образуются низкоомнЫе утечки на шину 115 в результате чего компенсируются емкостные токи, возникающие при переключение ключей, что уменьшает величину выбросов напряжения. При этом выбросы, возникающие в ключах 1-4 идентичны и поэтому еще более подавляются в дифференциальном усилителе 9, не пропускающим синфазные сигналы. Таким образом, введение дополнительных ключей и элемента задержки с соответствующими связями с другими элементами устройства позволяет улучшить его помехозащищенность.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1164788A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU968855A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU868839A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU936031A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU966750A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1185398A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU920843A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU920844A1 |

АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее дифференциальный усилитель, выход которого является выходом устройства, накопительный элемент на конденсаторе, одна из обкладок которого соединена с первым входом дифференциального усилителя и с выходом первого ключа, второй ключ, выход которого соединен с другой обкладкой конденсатора повторитель напряжения, шину управления и шину нулевого потенциала, отличающееся тем, что, с целью повышения его помехозащищенности, в него введены элемент задержки, третий, четвертый, пятый и шестой ключиц причем первые входы первого, второго, третьего и четвертого ключей соединены с шиной управления, первые входы пятого и шестого ключей соединены с выходом элемента задержки, вход повторителя напряжения является входом устройства и соединен с вторьм входом третьего ключа, выход которого соединен с вторыми входами первого и пятого i ключей, выход повторителя Напряжения соединен с входом четвертого ключа, выход которого соединен с вторыми входами второго и шестого ключей, выходы пятого и шестого ключей соединены с шиной нулевого потенциала, вход элемента задержки соединен с шиной управления, выход второго ключа соединен с вторым эо входом дифференциального ключа. 4 эо со 00

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дифференциальное аналоговое запоминающее устройство | 1974 |

|

SU549838A1 |

| G, 11 С 27/00, 1974 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аналоговое запоминающее устройство | 1976 |

|

SU639021A1 |

| G, 01 С 27/00, | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1984-04-07—Публикация

1982-12-13—Подача