I

Изобретение относится к автоматике, вычислительной, информационноизмерительной технике и может быть использовано для созд/ания аналогоцифровых преобразователей, дискретно-аналоговых анализаторов спектра в качестве запоминающих устройств.

Целью изобретения является повышение точности и быстродействия устройства.

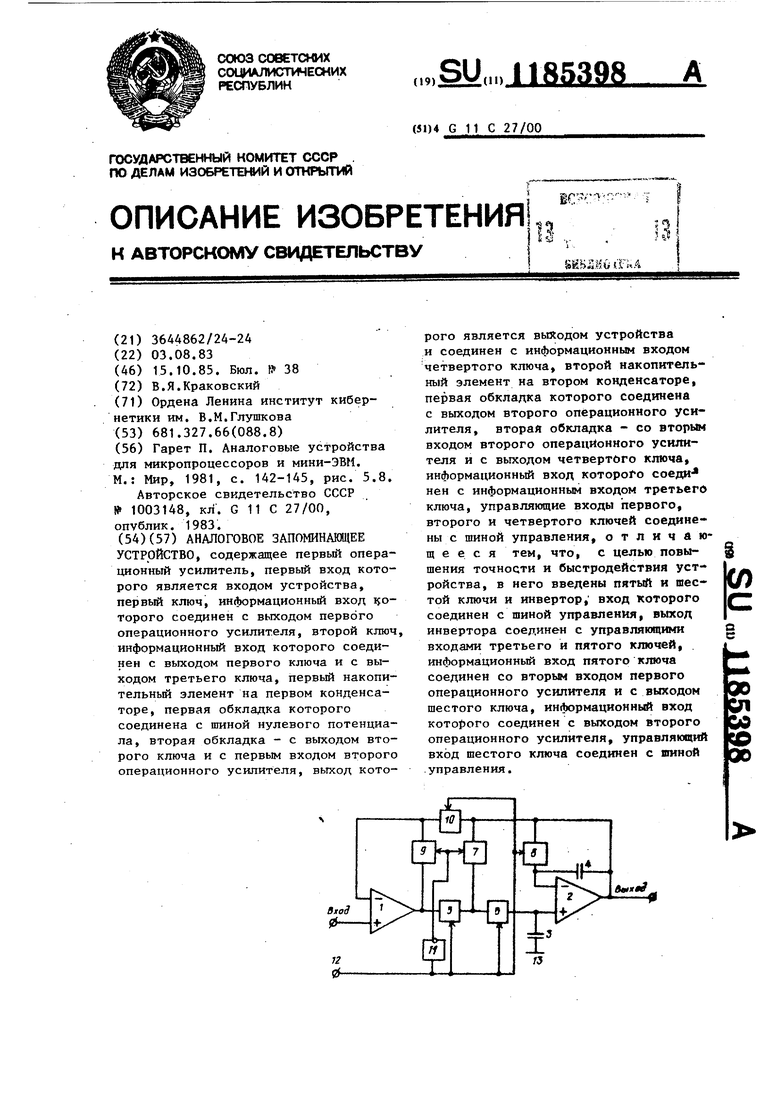

На чертеже приведена функциональная схема предложенного устройства.

Схема содержит операционные усилители 1 и 2, накопительные элементы на конденсаторах 3 и 4, клю-. чи 5-10, инвертор 11, шину 12 управления и шину 13 нулевого потенциала

Устройство работает следующим образом.

На шину 12 управления подается потенциал включения ключей 5-6 и 10 в режиме слежения и снимается этот потенциал при переходе в режим хранения. При замкнутых ключах 5, 6 и 10 устройство отслеживает входной сигнал. Услитель 2 работает как повторитель напряжения на конденсаторе 3.

Ключи 5 и 6 охвачены отрицательной обратной времени заряда конденсатора 3, которая, в основном, определяется допустимой скоростью нарастания выходного усилителя 1 и ограничивается предельным значением выходного тока этого усилителя. При размыкании ключей 5-7 и 10 устройство запоминает значение напряжения на конденсаторе 3. Инвертор 11 кроме инвертирования создает еще и необходимую задержку для замыкания ключей 7 и 9, после размыкания ключей 5. 6 и 10. Замыкание ключа 7

85398 . . 2

уравнивает потенциалы сигнального входа и выхода ключа 6, что исключает цепь разряда конденсатора 3 через этот ключ. Разряд конденсато5 ра 3 через первый вход усилителя 2 компенсируется подзарядом конденсатора 4 через второй вход этого усилителя. Размыкание ключа 10 и замыкание ключа 9 при переходе в режим хранения включает усилитель 1 по схеме повторителя входного сигнала, что при последующем обратно переходе в режим слежейия обеспечивает повышение точности записи входного сигнала за небольшой период времени, отведанный для выборки сигнала, так как в этом случае не, требуется времени навыход усилителя 1 из режима насьш1ения, как это имеет место в устройстве - прототипе..Этим же повьш1ается быстродействие, так как с той же точностью можно осуществить выборку входного сигнала за более короткое время. Снижается также энергопотребление и исключаются помехи на выходе устройства изза возможных частых перебросов усилителя 1 из одного внца насыщения в другой вид при нахождении значений входного сигнала вблизи значения хранимого отсчета сигнала. При этом снижения точности хранения не происходит, так как потенциалы сигнального входа и выхода ключа 6 У4)авниваются с помощью ключа 7.

В предложенном устройстве повышена точность и быстродействие за счет устранения разряда конденсатора 3 через конечную величину сопротивления разомкнутого ключа 6 и устранения режима насыщения операционного усилителя 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1980 |

|

SU966749A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU920843A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU841057A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU830583A1 |

| Аналоговое запоминающее устройство | 1984 |

|

SU1267484A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1003148A1 |

| Аналоговое запоминающее устройство | 1990 |

|

SU1734123A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1084898A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU847374A1 |

АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее первьв операционный усилитель, первый вход которого является входом устройства, первый ключ, информационный вход которого соединен с выходом первого операционного усилителя, второй ключ, информационный вход которого соединен с выходом первого ключа и с выходом третьего ключа, первый накопительный элемент на первом конденсаторе, первая обкладка которого соединена с шиной нулевого потенциала, вторая обкладка - с выходом второго ключа и с первым входом второго операционного усилителя, выход которого является выходом устройства и соединен с информационным входом четвертого ключа, второй накопительный элемент на втором конденсаторе, первая обкладка которого соединена с выходом второго операционного усилителя, вторая обкладка - со вторым входом второго операционного усилителя и с выходом четвертого ключа, информационный вход которого соеди- нен с информационным входом третьего ключа, управляющие входы первого, второго и четвертого ключей соединены с щиной управления, отличаюг щееся тем, что, с целью повышения точности и быстродействия устройства, в него введены пятый и шестой ключи и инвертор, вход которого соединен с шиной управления, выход инвертора соединен с управляющими входами третьего и пятого ключей, информационный вход пятого ключа соединен со вторым входом первого 90 операционного усилителя и с выходом сл шестого ключа, информационный вход 00 которого соединен с выходом второго ;о операционного усилителя, управляющий вход шестого ключа соединен с шиной эо управления.

| Гарет П | |||

| Аналоговые устройства для микропроцессоров и мини-ЭВМ | |||

| М.: Мир, 1981, с | |||

| Рогульчатое веретено | 1922 |

|

SU142A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1003148A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1985-10-15—Публикация

1983-08-03—Подача