Изобретение относится к вычислительной технике 5 в частности к запоминающим устройствам (ОЗУ), и может быть использовано в различных средствах вычислительной техники, которые критичны к потерям информации в электронной памяти при аварийном проподании или включении (выключении) сети переменного тока.

Известны устройства для защиты информации в блоке памяти Cl3 и C2J

Одно из известных устройств содержит основной источник питания, резервный источник питания, например батарею, ключевые элементы, реле С1

Недостатками этого устройства являются низкая надежность и сложность.

Наиболее близким техническим решением к изобретению является устройство для защиты информации в блоке памяти, содержащее детектор порогового уровня сетевого напряжения, соединенный с компаратором, основной 25 ° источник питания, выход которого соединен с другим входом компаратора входом первого одновибратора и через дкод - с выходом устройства, резервный ислчэчник питания батарею, соединенный через диод с выходом устройства, два одновибратора и два ключа, формирующие сигналы блокировки записи и считывания из ОЗУ и бло-кировкк микропроцессора (МП) С2, Недостатком известного устройства является то, что блок формирования сигналов блокировки МП и ОЗУ - одновибраторы и ключи - запитываются от батарейного источника питания, что вызывает нежелательный расход энергии батареи и сокращает срок ее использования 5 а следовательно, умен шает продолжительность хранения информац -1И о Кроме того, кгавесткое устройство формирует сигнал блокировки ОЗУ без временкой задержки по отношению л сигналу блокировки МПр что мопет зыз EiTb неправильную работу и потерю й:-1формо.дии в ОЗУ при аварии питания. Цель.о изобретения является повыше :-ше- надежности устройства Постазланная цель достигается уем, что в устройство для защиты инфпрмацки в блоке памяти« содержащее оеясвной и резервный исгочкики пита-ьля, разделительные эпементы, кокпапатор, одновибраторы, ключи и датчик

сетевого напряжения, выход которого соединен с входом элемента развязки и первьгм входом компаратора j выход которого подключен к первому входу первого одновибратора, выход которого соединен с первым входом первого ключа причем выход второго одновибратора подключен к первому входу второго ключа, выход основного источника питания подключен к вторым входам компаратора и первого одновибратора и входу первого разделительного элемента, выход резервного источника питания соединен с входом второго

разделительного элемента, выходы первого и второго разделительных элементов объединены и являются первым выходом устройства, управляющим выходом которого является выход первого ключа;

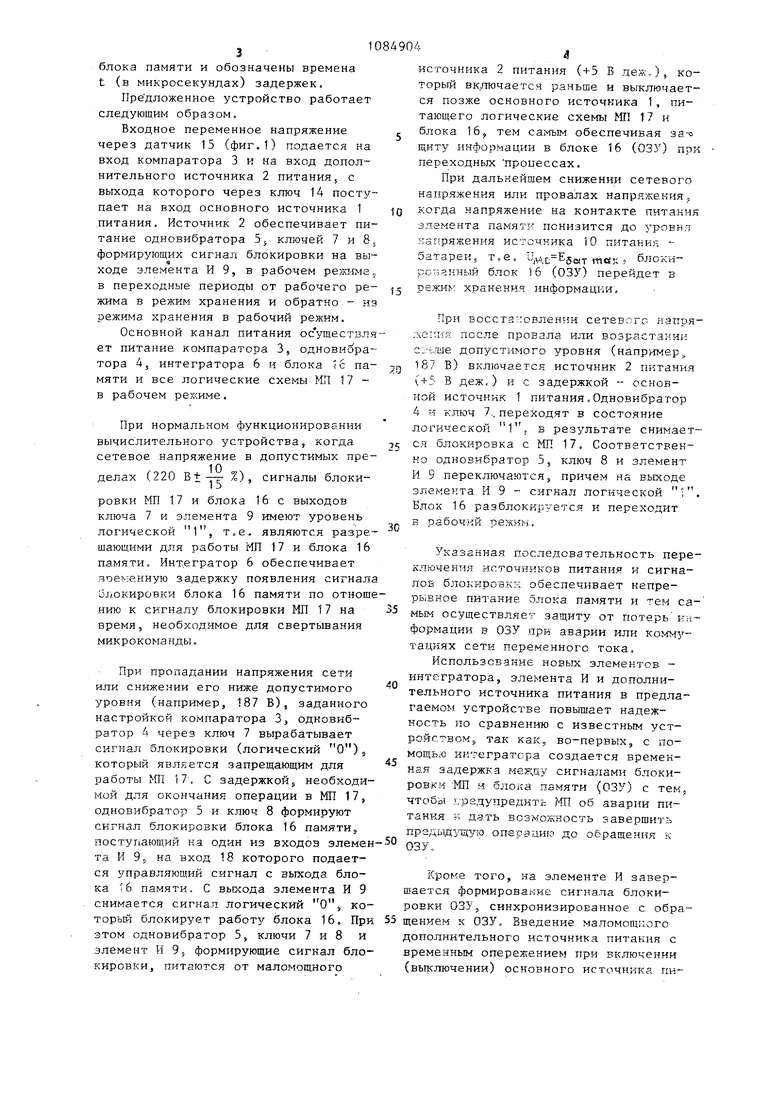

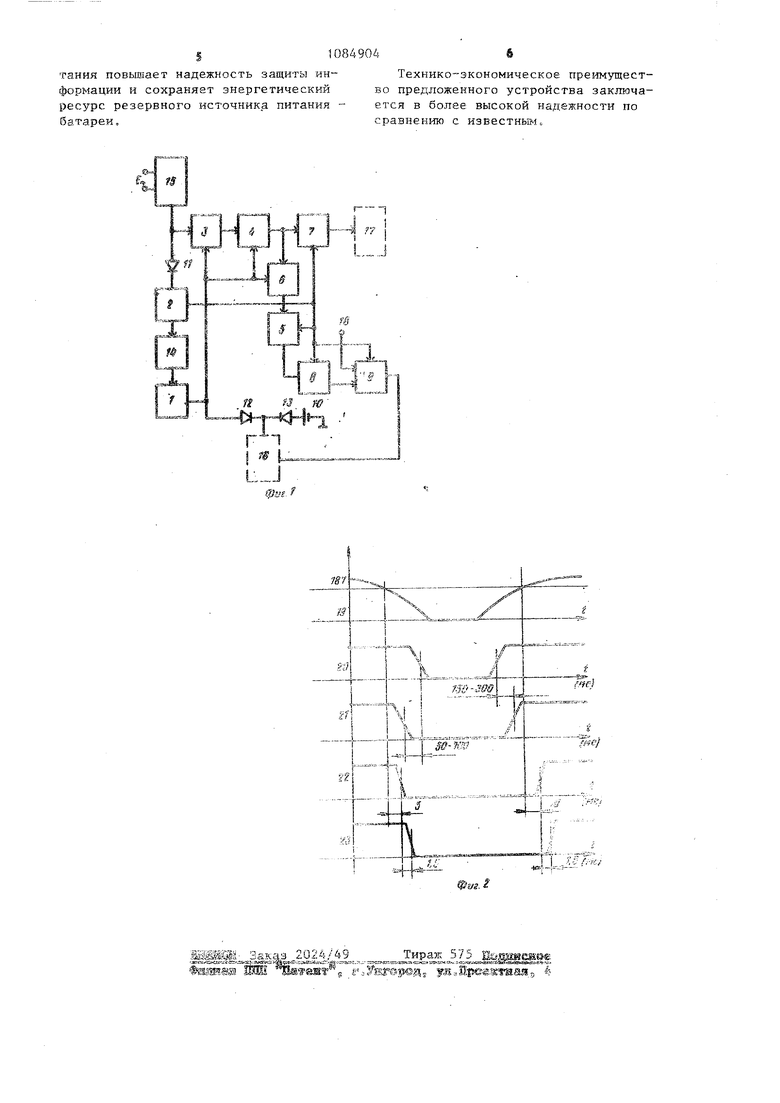

введены интегратор, элемент И. дополнительный источник питания 3 вход которого соединен с выходом элемента развязки, и третий ключ, выход которого соединен с входом основноисточника питания, причем выходы дополнительного источника питания подключены соответственно к входу третьего ключа и к вторым входам первого и второго ключей, второму входу второго одновибратора и ггерзому входу элемента И, второй вход которого соединен с выходом второго од ноЕибратораз а третий вход, и выход являются соответственно управляющим входом и вторым выходом устройства. На фиг. 1 изображена функциональная схема предложенного устройства: на фиг. 2 - временные д,иaгpa iмы, поясняющие работу устройства,П11едложенное устройство содер1; основной и дополнительный 2 источники питания, компаратор 3, первый 4 и второй 5 O,II;HOBHC ратсрЫз интегратор 6,. лервый 7 к второй 8 ключи, элемент М 9, резервный источник to питанлЯ; иапри:-;ер батарею, злемект И раавям- н, г-ерзый 2 и второй iS рК13делнтельи,.,1е элементы, третий ключ 14 и д сетевого напряжения, бло-с микропроцессор (МП) 1 ;эдш вхо,гг 18 устройства На фиг. /:. показаны зр.: . л:гаграммы сетевого напряжения пряжения 20 на выходе ,-дите го источника питания, идпряже ;-: на выходе основного исгочкик; НИН, сигналы 22 блокироБ:-;;: кк процессора и сигналы 23 б,;.эк блока памяти и обозначены времена t (в микросекундах) задержек. Предложенное устройство работает следующим образом. Входное переменное напряжение через датчик 15 (фиг,1) подается на вход компаратора 3 и на вход дополнительного источника 2 питания, с выхода которого через ключ 14 поступает на вход основного источника 1 .питания. Источник 2 обеспечивает питание одновибратора 5 ключей 7 и 8 формирующих сигнал блокировки на выходе элемента И 9, в рабочем в переходные периоды от рабочего режима в режим хранения и обратно - из режима хранения в рабочий режим. Основной канал питания осущестзля ет питание компаратора 3, одновибратора 4, интегратора 6 и блока 16 памяти и все логические схемы Ш 17 в рабочем режиме. При нормальном функционировании вычислительного устройства, когда сетевое напряжение в допустимых пределах (220 Бt уг %), сигналы блокировки МП 17 и блока 16 с выходов ключа 7 и элемента 9 имеют уровень логической 1, т.е. являются разре шающими для работы МП 17 и блока 16 памяти. Интегратор 6 обеспечивает з эеменную задержку появления сигнал блокировки блока 16 памяти по отнош нию к сигналу блокировки МП 17 на время, необходимое для свертывания микрокоманды. При пропадании напряжения сети или снижении его ниже допустимого уровня (например, 187 В), заданного настройкой компаратора 3, одковибратор 4 через ключ 7 вырабатывает сигнал блокировки (логический О)э который является запрещающим для работы МП 17. С задержкой; необходимой для окончания операции в МП 17, одновибратор 5 и ключ 8 формируют сигнал блокировки блока 16 памяти. поступающий на один из входов элемен та И 9,, на вход 18 которого подается управляющий сигнал с выхода блока 16 памяти, С выхода элемента И 9 снимается сигнал логический О, который блокирует работу блока 16, При

этом одновибратор 5, ключи 7 и 8 и элемент И 9, формирующие сигнал блокировки, питаются от маломощного

дополнительного источника питания с временным опережением при включении (выключении) основного источника пиисточника 2 питания (+5 Б деж%) который вк.лючается раньше и выключается позже основного источника 1, питающего логические схемы МП 17 и блока 16, тем самым обеспечивая за-о щиту информации в блоке 16 (033) при переходных пропессах. При дальнейшем снижении сетевого напряжения или провалах напряжения., когда напряжение на контакте питания элемента памят -: понизится до уровня яагфяження источника 10 питания батареи, т.е. той;; блокирсзанн :.1й блок 16 (ОЗУ) перейдет в режим хракени.ч информации. При восстановлении сетевого напрялспкя после провала или возрастании с::Ь.гше допустимого уровня (например,, 187 Б) включается источник 2 питания (-ь5 В деж,) и с задержкой -- основной источник 1 питания.Одновибратор 4 и ключ 7., переходят в состояние логической в результате снимается блокировка с МП 17. Соответственно одновибратор 5 j ключ 8 и элемент И 9 переключаются, причем на выходе злемекта И 9 - сигнал логической ;. Блок 16 разблокируется и переходит Е рабочз й режин. Указанная последовательность переключения источников питания и сигналов блокировки обеспечивает непрерывное питание блока памяти и тем самьм осуществляет защиту от потерь информации в ОЗУ при аварии или коммутациях сети переменного тока. Использование новых элементов интегратора, элемента И и дополнительного источника питания в предлагаемом устройстве повышает на.дежность по сравненито с известным устройством так как, во-первых, с помощью интегратс-ра создается временная задержка сигналами блокировки МП я блока памяти (ОЗУ) с тем чтобо ..редупредить МП об аварии питания к дать возможность завершить ирадыдутщпо операцию до обращения к y Кроме того, на элементе И заверается формирование сигнала блокиовки ОЗУ,, синхронизированное с обраением к ОЗУ, Введение маломощкого

тания повышает надежность защиты информации и сохраняет энергетический ресурс резервного источнику питания батареи.

Технико-экономическое преимущество предложенного устройства заключается в более высокой надежности по сравнению с известным.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синфазного автоматического включения резервного питания потребителей с двигательной нагрузкой | 1985 |

|

SU1305811A1 |

| Запоминающее устройство с сохранением информации при аварийном отключении питания | 1987 |

|

SU1434504A1 |

| Устройство для перезапуска и контроля электропитания микроЭВМ | 1989 |

|

SU1797122A1 |

| УСТРОЙСТВО ПРОГРАММНО-АППАРАТНОГО КОМПЛЕКСА ФОРМИРОВАНИЯ КЛЮЧЕВОЙ ИНФОРМАЦИИ И РАДИОДАННЫХ ДЛЯ РАДИОСТАНЦИИ | 2016 |

|

RU2634202C1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1986 |

|

SU1365133A1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| Устройство для сохранения информации в полупроводниковой памяти при аварийном отключении питания | 1985 |

|

SU1285537A1 |

| Устройство для тревожной сиг-НАлизАции | 1978 |

|

SU798931A1 |

| УСТРОЙСТВО ЗАЩИТЫ ПАМЯТИ | 1991 |

|

RU2006923C1 |

| УСТРОЙСТВО ДЛЯ ДИАГНОСТИРОВАНИЯ ТЕЛЕВИЗИОННОЙ АППАРАТУРЫ | 1989 |

|

RU2050700C1 |

УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ИНФОРМАЦИИ В БЛОКЕ ПАМЯТИ, содержащее основной и резервный источники питания, разделительные элементы, компаратор, одновибраторы, ключи и датчик сетевого напря:кения, выход которого соединен с входом элемента развязки и первым входом компаратора, выход которого подключен к первому входу первого одновибратора, выход которого соединен с первым входом первого ключа, причем выход второго одновибратора подключен к первому входу второго ключа, выход основного источника питания подключен к вторым входам компаратора и первого одновибратора и входу первого разделительного элемента, выход резервного источника питания соединен с входом второго разделительного элемента, выходы первого и второго разделительных элементов объединены и являются первым, выходом устройства, управляющим выходом которого является выход первого ключа, отличающееся тем, что, с целью повышения его на-, дежности, в него введены интегратор, элемент И; дополнительный источник питания, вход которого соединен с выходом элемента развязки, и третий ключ, выход которого соедис S нен с входом основного источника питания, причем выходы дополнительного источника питания подключены соответственно к входу третьего ключа и к вторым входам первого и второго ключей, второму входу второго одновибратора и первом г входу элеменваяА та И, второй вход которого соединен О 00 с выходом второго одновибратора, а третий вход и выход являются соот. ветственно управляющим входом и втоf рым выходом устройства.

yL

А

..,„..1

---П ( 1 i л

(4.-...,- f I sff-wa

.J::H-t -- I -ff

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ получения мыла | 1920 |

|

SU364A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1984-04-07—Публикация

1982-12-03—Подача