элемента И и.подключен к выходу первого разряда кольцевого регистра, выход последнего разряда которого объединен с первым входом второго триггера и является первым выходом блока защиты, выход второго разряда кольцевого регистра является вторым выходом блока защиты, вторые входы триггеров являются первым и вторым входами блока защиты/ а вход первого разряда кольцевого регистра является третьим входом блока защиты.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2008 |

|

RU2386208C1 |

| Стохастический аналого-цифровой преобразователь | 1985 |

|

SU1267615A1 |

| Устройство для сжатия цветовых сигналов телевизионных изображений | 1988 |

|

SU1607080A1 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2004 |

|

RU2269866C2 |

| Шифратор | 1987 |

|

SU1439748A1 |

| Устройство для магнитной записи измерительной информации | 1990 |

|

SU1727164A1 |

| Устройство для вычисления математического ожидания | 1986 |

|

SU1383398A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 2000 |

|

RU2170444C1 |

| Устройство для сжатия цифровых телевизионных сигналов цветного изображения | 1988 |

|

SU1529471A1 |

| КОРРЕЛЯЦИОННАЯ ИЗМЕРИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2007753C1 |

УСТРОЙСТВО СИНХРОНИЗАЦИИ, содержащее последовательно соединенные генератор тактовых импульсов и формирователь входного сигнала, выходы которого подключены соответственно к входам первого и второго блоков счетчиков, выходы которых через соответствующие первый и второй элементы задержки подключены к входам триггера, последовательно соединенные делитель и блок задержки, после- . довательно соединенные элемент И,первый счетчик, блок триггеров и выходной блок элементов И, последовательно соединенные второй счетчик и дешифратор, а также блок управления и блок фиксации, к входс1м которого подключены соответствующие выходы первого счетчика, а выходы блока фик:сации подключены к соответствующим входам выходного блока элементов И, другие входы которого объединены и подсоединены к первому входу элемента И, второй вход которого подключен к выходу генератора тактовых HMnyflbi сов, при этом соответствующие выходы первого и второго блоков счетчиков подключены к входЁ1м блока управления, выходы которого подключены к соответствуюпшм входам-формирователя входных сигналов, соответствующий выход которого подключен к входу второго счетчика, соответствующие выходы блока триггеров объединены и подключены к соответствующим входам Сброс первого и второго блока счетчиков, отличающееся тем, что, с целью повышения точности синхронизации путем устранения потерь информационных импульсов, в него введены дополнительный делитель, элемент задержки, блок защиты и блок управляемой задержки, выход которого подключен к первому входу элемента И, к первому и второму входу блока управляемой задержки подсоединены выходы триггера, а третий вход подсоединен к первому выходу блока защиты, первый, второй и третий выходы которого подключены к.соответствующим входам блока управления, к первому и второму входам блока защиты подключены другие выходил первого блока счетчиков , а третий вход подсоединен к выходу дополнительного делителя, вход которого подсоединен к выходу генератора тактовых импульсов, а выход к входу делителя, этом выходы дешифратора через элемент задержки подключены к входам блока фиксации. 00 2.Устройство ПОП.1, ОТЛИ.чающееся тем, 4to блок упраел вляемой задержки содержит два элемента И выходы которых подключены к входам триггера, выход которого является выходом блока управляемой задержки, первые входы элементов И объединены и являются третьим входом блока управляемой задержки, а вторые входы элементов И являются первым к вторым входами блока управляемой задержки. 3.Устройство по п.1, о т л и чающееся тем, что блок защиты содержит два триггера,.выходы которых через последовательно соединенные первый и вто{3ой элементы И подключены к третьему выходу блока защиты, первый вход первого триггера объединен с вторым входом второго

I .

Изобретение относится к технике связи и может использоваться в систе мах передачи дискретной информации.

Известно устройство дискретной фазовой синхронизации, содержащее последовательно соединенные опорный генератор, элемент НЕ, делитель на два, элемент И, делитель частоты на ш и фазовый дис криминатор, выход которого подсоединен к второму входу элемента И, а к второму входу под ключен выход входного блока, первый вход которюго является входом устройства, к второму входу подключен второй выход опорного генератора, к третьему входу подключен второй выход делителя на два, а второй выход входного блока подсоединен к второму входу элемента НЕ 1.

Однако данное устройство дискретной фазовой синхронизации имеет низкую точность синхронизации. I

Наиболее близким техническим решением к изобретению является устрой ство синхронизации, содержащее последовательно соединенные генератор тактовых импульсов и формирователь входного сигнала, выходы которого подключены соответственно к входам ггервого и второго блоков счетчиков, выходы которых через соответствующие первый и второй элементы задержки подключены ко входам триггера, последовательно соединенные делитель и блок задержки, последовательно соединенные элемент И, первый счетчик, блок триггеров и выходной блок элементов И, последовательно соединенные второй счетчик и дешифратор, а также блок управления и блок фиксации, к входам которого подключены со ответствуювдие выходы первого счетчика, а ВЫХОДЁ1 блока фиксации подключены к соответствующим входам выходного блока элементов И, другие входы которого объединены и подсоединены к первому входу элемента И,второй вход которого подключен к выходу генератора тактовых импульсов, при это сортветствующие выходы первого и второго блоков счетчиков подключены к входам блока управления, выходы которого подключены к соответствующим

входам формирователя входных сигналов, соответствующий выход которо1-О подключен ко входу второго счетчика, соответствующие выходы блока триггеров объединены и подключены к соответсгвующим входам Сброс первого и второго блока счетчиков, рри этом к третьему входу блока управления подключены объединенные выходы блока триггеров, а выхрды дешифратора подсоединены к входам блока фиксации С2.

Однако известное устройство синхронизации имеет низкую точность синхронизации за счет потерь информационных импульсов, попадающих в промежуток времени между стробирующими импульсами.

i Цель изобретения - повышение точ|ности синхронизации за счет устранения потерь информационных импульсов.

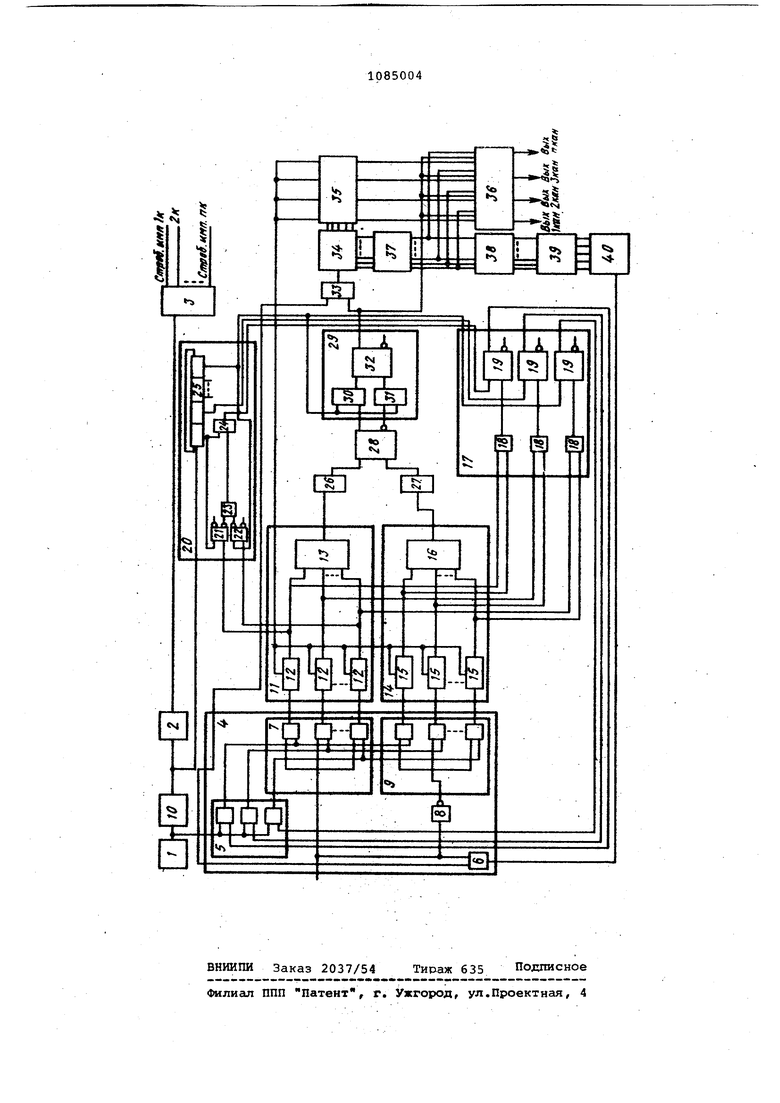

Поставленная цель достигается тем что в устройство синхронизации, содержащее последовательно соединенные генератор тактовых импульсов и формирователь входного сигн«ала, выходы которого подключены соответственно к входам первого и второго блоков счетчиков, выходы которых через соответствукхаие первый и второй элементы задержки подключены к входам триггера, последовательно соединенные делитель и блок задержки,, последовательно соединенные элемент И, первый счетчик, блок триггеров и выходной блок элементов И, последовательно соединенные второй счетчик и дещифратор, а также блок управления и блок фиксации, к входам которого подключены соответствующие выходы первого счетчика, а выходы блока фиксации подключены.к соответствующим входам выходного блока элементов И, другие входы которого объединены и подсоединены к первому входу элемента И, второй вхрд которого подключен к выходу генератора тактовых импульсов, при этом соответств тоцие выходы первого и второго блоков счетчиков подключены к входам блока управления выходы которого подключены к соответствующим входам формирователя входны сигналов, соответствующий выход которого подключен к входу второго счетчика, соответствующие выходы блока триггеров объединены и подключены к соответствующим входам Сброс первого и второго блока счетчиков, введены дополнительный делитель, элемен задержки, блок защиты и блок управля емой задержки, вь1ход которого подклю чен к первому входу элемента И, к первому и второму входу блока управляемой задержки подсоединены выходы триггера, а третий вход подсоединен к первому выходу блока защиты, первый, второй и третий выходы которого подключены к соответствующим входам блока управления, к первому и второму входам блока защиты подключены другие выходы первого блока счетчиков, а третий вход подсоединен к выходу дополнительного делителя, вход которого подсоединен к выгходу генератора тактовых импульсов, а выход - к входу делителя, при этом выходы дешифратора через элемент задержки подключены к входс1м блока фиксации,1 При этом блок управляемой задержки содержит два элемента И, выходы которых подключены к входам триггера, выход которого является, выходом блока управляемой задержки, первые входы элементов И объединены и являются третьим входом блока управляемой задержки, а вторые входы элементов И являются первым и вторым входа ми блока управляемой задержки. Кроме того, блок защиты содержит два триггера, выходил которых через последовательно соединенные первый и второй элементы И подключены к третьему выходу блока защиты, первый вход первого триггера объединен с вторым входом второго элемента И и подключен к выходу первого разряда кольцевого регистра, выход последнего разряда которого объединен с первквд входом второго триггера и является первым выходом блока защиты выход второго разряда кольцевого t eгистра является вторым выходом блока защиты, вторые входы триггеров являются первым и вторым входами блока защиты, а вход первого разряда кольцевого регистра является третьим входом блока защиты. На чертеже представлена структурно-электрическая схема- устройства синхронизации. Устройство синхронизации содержит генератор 1 тактовых импульсов (ГТИ делитель 2, блок 3 задержки, формирователь 4 входного сигнала, состоящий из блока 5 элементов И, элемента И 6, блока 7 элементов И, инвертора и блока 9 элементов И, дополнительный делитель 10, первый блок 11 чиков, содержащий счетчики 12 и элемент ИЛИ 13, второй блок 14 счетчиков, содержащий счетчики 15 и элемент ИЛИ 16, блок 17 управления, содержащий элементы ИЛИ 18 и триггеры 19, блок 20 защиты,содержащий триггеры 21 и 22, элементы И 23 и 24 и кольцевой регистр 25, элементы 26 и 27 задержки, триггер 28, блок 29 управляемой задержки, содержащий элементы И 3Q и 31 и триггер 32, элемент И 33, первый счетчик 34, блок 35 триггеров, выходной блок 36 элементов И, блок 37 фиксации, элемент 38 задержйи, дешифратор 39, второй счетчик 40, Устройство синхронизации работает следующим образом. Если на устройство поступает импульс Информационная единица, то он подготавливает к открытию блок 7 элементов И и элемент И 6. Импульсы с ГТИ 1 через дополнительный делитель 10 поступаетна кольцевой регистр 25 блока 20 защиты. Кольцевой регистр 25 поочередно устанавливает триггеры 19 блока 17 управления в единичное состояние, открывая тем самым блок 5 элементов И. В этом случае импульсы с ГТИ 1 с.частотой пг,,фпроходят через блок 7 элементов И на соответствующие счетчики 12 первого блока 11 счетчиков. Входной информационный импульс независимо от его длительности обязательно совпадает либо со стробируквдим импульсом (который формирует блок 5 элементов И и блок 7 элементов И), либо со стробирующим и одним или несколькими вспомогательными импульсами или только с одним или несколькими вспомогательными импульсами. На выходе соответствующих счетчиков 12 первого блока 11 счетчиков после т-го импульса появляется импульс, который, пройдя через элемент ИЛИ 13 и элемент 26 задержки через п тактов, устанавливает триггер 28 в единичное состояние, подготавливая тем самым элементы И 30 и 31 блока 29 управляемой задержки к открытию. i . Кроме того, импульсы ГТИ 1 с частотой nf, через элемент И. 6 поступают на вход счетчика 40, который производит измерение длительности входного импульса. Импульсом с последней ячейки кольцевого регистра 25 через элементы И 30 и 31 триггер 32 устанавливается в единичное состояние, подготавливая тем самым блок 35 триггеров к открытию. Через элемент И 33 на счетчик 34 начинают поступать импульсы с ГТИ 1, На одном из выходов дешифратора 39, соответствующем длительности поступаквдего импульса, появляется напряжение, которое через элемент 38 з.адержки открывает соответственно выходной блок 36 и производит остановку счетчика 34 на.It-ом такте, соответствующем длительности поступающе го импульса. На выходе выходного блока 36.появляется выходной импульс. Когда счетчик 34 досчитает д k-ro импульса, этот импульс устанавливает блок 35 триггеров в нулевое состояние, выходной блок 36 закрыва ется и выходной импульс прекращается. Длительность импульса на выходе таким образом, равна длительности BXOjAoro импульса и его фаза синхронна с фазой стробирующих импульсов, поступающих с блока 3 задержки обеспечивающего попадание стробирующих импульсов на середину информац онных импульсов. В случае, если .информационный им пульс совпадает с последним вспомогательным и стробируюадим импульсйм следующего периода, может быть зафиксирована единица в первом и во втором периодах, т.е. будет ложное срабатывание во втором периоде. Для устранения этого с помощью триггеров 21,22 и элементов И 23 и блока 20 зёвциты осуществляется запр записи единицы во втором периоде в триггер 28 по результатам совпадег ния информационного импульса и стро бирующего импульса второго периода. Это достигается тем, что во вторам периоде один из триггеров 19 блока 17 управления остается в нулевом состоянии, соответственно блок 5 элементов И закрыт и импульсы с ГТИ 1 не поступач т через блок 7 элементов И На один из счетчиков 12 первого блока 11 счетчиков. Элемент 38 задержки предназначен для временного согласовг1ния работы канала измерения длительности входных импульсов и канала синхронизации входного импульса. Технико-экономическая эффективность устройства синхронизации заключается в повышении точности синхронизации за счет устранения потерь информационных импульсов, при этом вспомогательные импульсы осуществляют только обнаружения информационных импульсов, ц по стробир зощим импульсам осуществляется как обнаружение, (так и синхронизация входных импульсов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДИСКРЕТНОЙ ФАЗОВОЙ СИНХРОНИЗАЦИИ | 0 |

|

SU391750A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство синхронизации | 1978 |

|

SU696622A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-04-07—Публикация

1983-01-25—Подача