Изобретение от юсится х технике передачи и хранения цветных изображений в системах с применением телевизионных дисплеев и видеотерминалов, может быть использовано в автоматизированных системах отображения, обработки данных и управления.

Целью изобретения является увеличение коэффициента сжатия.

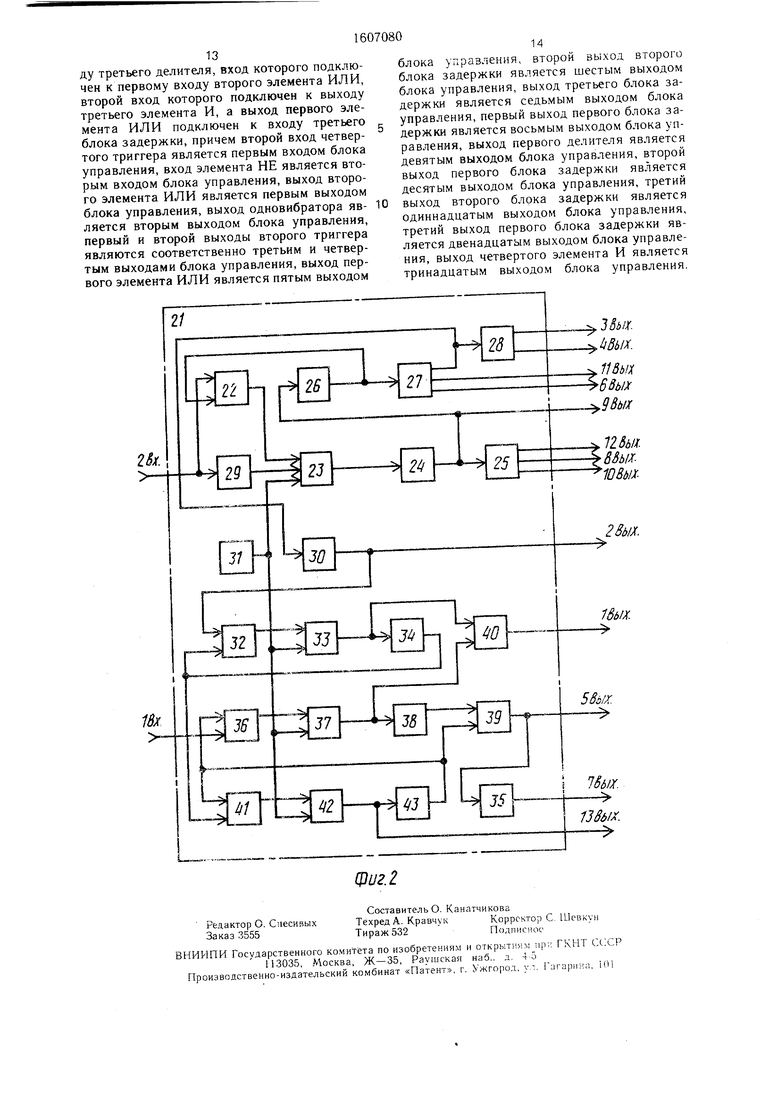

На фиг. 1 нредстазлена структурная электрическая схема устройства для ежа- тия цветовых сигналов телевизионных изображений; на фиг. 2 - структурная электрическая схема блока управления.

Устройство для сжатия цветовых сигналов телевизионных изображений содер жит аналого-цифровой преобразователь (АЦП) 1 блок 2 установки опорного уровня, перзый рсг:-ч-тр 3, П--ОПОЙ )егнстп 4 перргАИ OJiOK h з ;де;; клн, первый блок 6 -равненья, перьь и счетчик 7, йторой счетчик 8, третий регистр , втор.ой блок I O сравнения, первый комгу ута- тор 1, второй коммутатор 12, первый--четвертый 13---16 блоки памяти, блок 17 эле- MCiiTOB ИЛИ. формирователь i8 кода с-;:хро - низации, преобразователь кода (ПК) 19, элемент ИЛИ 20. блок 21 управления.

Блок 2 управления с-о держит первый триггер 22, первый элемент И 23, первый делитель 24, первый блок 25 задержки, вто- оой делитель 26, второй задержки, триггер 28 элемент НЕ 29. однонис- оатор 30, генератор 31 тактовых импуль- сов Г ГИ), третид триггер 32, второй элемент И 33, третий делитель 34, третий блок 35 задержки, четвертый триггер 36, третий элемент И 37, четвертый делитель 38, nei)- нын элемент ИЛИ 39, второй элемент ИЛИ 40, пятый триггер 41, четвертый элемент И 42, пятый ,.,елитель 43.

АЦП I преобразует а; алого 5Ый TCjieijii- : иониый сигнал в цифровой, где ка кдому элсггепту отображения соответстну; т т-раз- ичдпый код цветности.

Влок 2 установки опорного уровн прпд- илзчачен для формирова1:Иь импульсов, соCTB-TCTEVfOIJU-iX кадровым и СТрОЧ ЫМ ..)(;ил1иульсам а1-1алоговог; телсьизио;1иого с .

JleiiBijiA peгнl: p 3 предпазпачеп для запи t-H. хранения и выдачи кода цветности те- ;(уг,его элемента отображения.

Второй pei-истр 5 пред1;азначел для з::и1я- ;. чр 5нения и выдачи кода ц;;е лости г:ре ыдущего элемента отобргження.

Пепвый блок 5 задержки предназначен ;-.л5 задержки кода цветности

Первый блок 6 сравнения гм еднэзиачс . поразрядного сравнения г11-разряд|-)ы; i:o:;ob цветности текуп,его и (ре ыдущеи

сзоем выходе единич1Ю т: несовпадения KO,:IOB.

Первый счетчик 7 прг, -. иповаыия кода адреса кал 3 или i-i памяти.

о 5

,,

:

,

да1-;ном unKJie обработки инжиме записи в формации.

Второй счетчик 8 предназначен для q3Op- мированкя кода адреса обращения к блокам 1.3 или 14 памяти, работающим в данном цикле обработки в режиме считывания. Третий регистр 9 предназначен для записи, хранения к выдачи кода максимального а (т. е. адреса ячейки памяти блока П или 14 памяти, в которую записан код цветности последней полосы предыдущего кадра). Второй блок 10 сравнения предназначен для сравнения кода максимального адреса и кода текущего адреса (т е адреса ячейки памяти блока 13 или 14 памяти из которой осуществляется считывание кода цветности), а также для Формирова НИИ единичного импульса при совпадений э гнх кодов.

Перв1лй коммутатор 11 предназначен для по0 -:еоед ого подклрочения выходов первого, второго счетчиков 7, 8 к вторым входам черного второго .блоков 13, 14 памяти. Выбор блока памяти (13 или 14), к которому осуществляется подключение выхода того или ИНОГО счетчика (7 или 8), определяется комби.;1ацией сигналов, поступающих на третий, четвертый входы коммутатора 11.

Второй коммутатор 12 предназначен для поочерёдного подключения выходов 12 и 13 б.лока 21 управления к соответствующим плодам - -; етьего, четвертого блоков памяти () Выбор блока памяти (15 или 16), к которому подключается тот или иной выход б .ока 21 i2 или 13) управления, определяется комбинацией сигналов на третьем, четвертом входах второго коммутатора 2.

Первый блок 13 памяти предназначен для записи, хранения и выдачи списка ко- ;, цветности кадра изображения.

Итерой блок 14 памяти также предназ- иачеи для записи, хранения и выдачи списка ;о;зо|-. чветлости кадра изображения. Третий блок 15 памяти предназначен для ап лси, хранения и считывания битовой карты измёнени лветиости хадра изображения. Четвертый блок 16 памяти также пред- пазпачен для записи, хранения и считывания битовой карты изменения цветности кадра ; зобрах енйя.

17 элемектон ПЛИ предназначе:-; ii |я объединения выходов первого, второго блоков 3, 14 памяти, -ахода формирователя 8 кода синхронизации.

ФормиооБЗте 1ь i5 кода синхронизации иреапазначеи дл.: хранении и выдачи перед началом счигывания инфирмаиии о кадре ичображечв;; ко;ха синлро;-;изации.

Преобпаз /ватель кода (ГП;) 19 пред1 аз- ,ачен ;:. ;;, п зеобрнзования счит:7Ц ьемых в па- 5 .)аллел1,ном коде кодов цйетности а аосле- i,oB3.Te., ко.д.

:)npyi.,j-r 1 ;Л11 2С |редназиачен для объе .ми1-:пиия выходов ПАП 19, третьего б,пока 15 к -чЯ - : че веотого блока 16 памятл.

Блок 21 управления предназначен для обеспечения согласованной работы блоков устройства путем формирования и выдачи управляющих сигналов и тактовых импульсов на соответствующие входы блоков устройства.

Устройство работает следующим образом.

Поступающий на вход устройства ТВ- сигнал преобразуется АЦП 1 в цифровой массив, где каждому элементу отображения соответствует т-разрядный код цветности. Полученный массив подвергается преобразованию, в результате которого информация о кадре записывается в виде списка кодов цветности и битовой карты изменения цветности. С целью устранения потери информации блоки памяти для записи битовой карты изменения цветности и списка кодов цветности дублированы. Список кодов цветности записывается в первый или второй блоки 13, 14 памяти, а битовая карта изменения цветности - в третий или четвертый блоки 15, 16 памяти. Выбор блоков памяти (13, 15 или 14, 16), в которые записывается информация о кадре, осуществляется по сигналам с выходов блока 21 управления. При этом, если информация о j-м кадре была записана в блоки 13, 15 памяти, то информация о (j4-l)-M кадре запищется в блоки 14, 16 памяти. Одновременно с процессом записи информации о (j-f-l)-M кадре в блоки 14, 16 памяти из блоков 13, 15 памяти осуществляется считывание информации о J-M кадре на выход устройства. Информация о (j+2)-M кадре запишется в блоки 13, 15 памяти. Таким образом, запись информации о каждом новом кадре будет производиться в освободившиеся блоки памяти (13, 15 или 14, 16).

Рассмотрим работу устройства по структурной схеме (фиг. 1).

В исходном состоянии первый регистр 3, второй регистр 4, первый счетчик 7, второй счетчик 8 обнулены. В третий регистр 9 записан код максимального адреса предыдущего кадра (если на вход устройства поступает первый кадр, то регистр 9 обнулен). В один из блоков 13 или 14 памяти записан список кодов цветности предыдущего кадра. В один из блоков 15 или 16 памяти записана битовая карта изменения цветности предыдущего кадра. Для удобства рассмотрения работы устройства допустим, что список кодов цветности данного кадра будет записываться в первый блок 13 памяти, а битовая карта изменения цветности - в третий блок 15 памяти. В этом случае на выходе 4 блока 21 управления установлен единичный потенциал, а на выходе 3 - нулевой.

С поступлением на вход устройства аналогового ТВ-сигнала блок 2 установки опорного уровня формирует импульс, соответствующий кадровому синхроимпульсу, поступающий на вход 2 блока 21 управления, разрешая цикл работы блока 21 управления. АЦП 1 преобразует ТВ-сигнал в т-разрядный код цветности, который поступает на первый вход первого регистра 3. 5 Этот код соответствует текущему элементу отображения. С приходом тактового импульса с выхода 10 блока 21 управления на второй вход первого регистра 3 код за писы- вается в регистр. По приходу тактового им- 0 пульса с выхода 9 блока 21 управления на второй вход второго регистра 4 в этот регистр записывается код, поступающий с выхода первого регистра 3 на первый вход второго регистра 4. За счет того, что импульс с выхода 9 блока 21 управления опережает 5 импульс с выхода 10, во второй регистр 4 осуществится запись кода, соответствующего предыдущему элементу отображения (или, если начинается обработка нового кадра, - нулевой комбинации). Коды цветнос- 0 ти текущего и предыдущего элементов отображения, поступающее с выходов регистров 3, 4 на входы первого блока 6 сравнения поразрядно сравниваются. С приходом тактового импульса с выхода 8 блока 21 управления на третий вход первого блока 6 5 сравнения на его выходе формируется сигнал результата сравнения. Этот сигнал одновременно поступает на первые (информационные) входы третьего и четвертого блоков 15, 16 памяти и записывается в третий блок 15 памяти по приходу на его первый вход тактового импульса с первого выхода второго коммутатора 12. Этот импульс поступает с выхода 12 блока 21 управления на первый вход второго коммутатора 12, который коммутирует этот вход в данном цикле обработки на первый выход. Пос- лeдoвaтeJ ьнocть сигналов с выхода первого блока 6 сравнения образует битовую карту изменения цветности. Сигнал с выхода первого блока 6 сравнения поступает также на первый вход первого счетчика 7, фор- 0 мирующего адрес ячейки памяти первого блока 13 памяти, в которую производится запись кода цветности текущего и предыдущего элементов отображения. В случае, если коды цветности текущего и предыдущего элементов отображения совпадают, состоя- 5 ние счетчика 7 не изменяется и запись кода цветности текущего элемента отображения производится в ту же ячейку памяти, в которую до этого был записан код цветности предыдущего элемента отображения. В случае несовпадения этих кодов на выхо- 0 де первого блока 6 сравнения формируется .единичный импульс, поступающий на первый вход первого счетчика 7. Под воздействием этого импульса счетчик 7 увеличивает свое состояние на едини 1у, формируя новый 5 адрес. Этот адрес поступает на первый вход первого коммутатора 1, который коммутирует этот вход в данном цикле обработки на свой первый вььход. Код адреса с первого выхода первого коммутатора 11 поступает

0

5

хода ПК 19 через элемент ИЛИ 20 на выход устройства. По окончании выдачи и т-раз- рядного кода синхронизации на выход устройства формирование тактовых импульсов на выходе 1 блока 21 управления прекраща- 5 ется и начинается их выдача с выхода 13 блока 21 управления на второй вход второго коммутатора 12. В соответствии с комбинацией сигналов на выходах 4, 3 блока 21 управления второй коммутатор 12 коммутирует

IClliUBAn VJllV. pnWi - J -f ГГ

поступающий на вход 2 блока 21; управления. На время этого импульса прекращается выдача тактовых импульсов с выходов 10,

мент ИЛИ 20 на выход устройства. По окончании считывания битовой карты изменения цветности из третьего блока 15 памяти выдача тактовых импульсов с выхода 13 блока 21 управления прекращается и начинана второй вход первого блока 13 памяти. Так как в первый блок 3 памяти запись кода цветности каждого элемента отображения осуществляется асинхронно, то смена кода адреса поступающего на второй вход блока 13 памяти, должна опережать смену кода цветности, поступающего на первый вход этого блока памяти. Необходимую задержку кода цветности обеспечивает первый блок 5 заЙГ с ро К:го °сГр™Г„уГьсГблоГГу : ,„ гё„1 второй-.хс,. „а первый выход/Такто Говк7Гр;о.оуро в„„ф/р ируе.„.„ульо, « „„„ульсь,фор„„руе.-.е „а ,ходе,3

ствующий вход третьего блока 15 памяти, обеспечивая последовательный сдвиг битоГ8ГТГбло; а 2Т управления. Этим обеспе- вой карты изменения цветности через элеч ивается обработка только информационной

части поступающего на вход устройства

ТВ-сигнала. По окончании обработки кадра

изображения с выхода 6 блока 21 управлест па е иТу1Г1е7п17:в1 Т:пи сГв 0 с выхода 1 на второй вход

ступает /Г. оа-ПК 19. Одновременно начинается выдача имэтот регистр of 4 Г1;о1 Гтупает на пер-пульсов с вых)дов 7, 5 блока 21 управления,

ботанного « ; РИмпульсы с выхода 7 блока 21 управления

ГоТчТтчГа 7 Гза де жко йне пост упают на первый вход второго счетчиЕ г:др:сГ ™и™%-: г. .1- оГут1р 1Гп:рвГ кгмТг; тсоответствии с комбинацией сигналов, поступающих с выходов 4, 3 на его третий, четпоступает импульс который устанавливает вертый входы соответственно, коммутирует их в нулевое состояние Одновременно на 0 свой второй вход на первый выход. Код адре- вьгходе 3 блока 21 управления ус,танавлива- са с первого выхода первого коммутато- выходе о QjiuKd 1 уираJ. JJ поступает на второй вход первого

блока 13 памяти. При этом с выхода блока 13 памяти считывается код цветности.

ботки кадра изображения завершается. Этот код цветности через блок 17 элементов С поступлением кадрового синхроимпуль- 5 ИЛИ поступает на первый вход ПК 19, на са следующего Тадра на вход устройства второй вход которого поступают и мпульсь, с начинается цикл считывания из блоков 13, 15 памяти информации о предыдущем кал- ре и обработки поступающего кадра. Обработка поступающего кадра изображения осу- 40 1сствляется аналогично с той разницей, что запись битовой карты изменения цветности осуществляется в четвертый блок 16 памяти, а списка кодов цветности - во второй блок

гГитшание информации на выход уст- 45 м а ксима ль7ого адреса, которь Й поступает на пойства осуществляет ся следующим образом. второй вход второго блока 10 срвавнения с Г поступлением с выхода блока 2 установ- выхода третьего регистра 9. Если сравни JEEEn -r ГоГе с в$.ГкС: ,x ir rocpI ° Sa: . rrxST- . 1 чинают выдаваться такговые импульсы. Единичный потенциал с выхода 2 блока поступает на вход фор:;: ; ователя 18 кода синхронизации, ра.феп;::; выдачу кода синii С1 1 1 JV iVCl .t.1 jfii ijut i- -- -- -,-,---- jтретий вход первого регистра 3, третий вход второго регистра 4, второй вход первого счетчика 7, второй вход второго счетчика 8 поступает импульс, который устанавливает их в нулевое состояние. Одновременно на выходе 3 блока 21 управления устанавливается единичный потенциал, а на выходе 4 - нулевой, чем обеспечивается смена режимов работы пар блоков памяти. На этом цикл обработки кадра изображения завершается.

JikJLJVjn О., 1 ч/1 - чд1, iiv,.ij..

выхода 7 блока 21 управления, обеспечивая последоватетьную выдачу кода цветности с выхода ПК 19 через элемент ИЛИ 20 на выход устройства. По окончании выдачи кода цветности на выход устройства с выхода 5 блока 21 управления на третий вход второго блока 10 сравнения поступает импульс, обеспечивающий формирование сигнала результата сравнения кода адреса с кодом

j- 7И 1 k л, 1 /iv- iii i/jj .1-.--.. ..

пульса, формируемого на выходе блока 21 управления, с выхода 7 на первый вход счетчика 8 поступает очередной импульс, обеспечивая формирование нового кода адреса. В случае совпадения сравниваемых кодов адхронизации через бло

i I :;-. j J3 Ы Д ii Ч V - i-rint - -г

IK Г- элементов ИЛИ на „ ресов на выходе б.лока 10 сравнения фор ., . „ . .. - , - ,-.1 -f-.T- ft гл гг и ri I.I1I II ui rj r КР И М П hP

первый вход liK 1У. а.товые с выхода 1 21 управления ;; ;гт;..:ак , на второй вход ПК 19, (-ч.:;/и пи...-о.:.о- вательиую вы.и-;-. гии;.:р.ч и:5аци с УЬ,мируется единичный импульс. Этот импульс ;)бну.1яет третий регистр 9 и, поступая на 1 блока 21 управления, прекращает выдачу импульсов с выходов 7, 5, 1 блока 21

хода ПК 19 через элемент ИЛИ 20 на выход устройства. По окончании выдачи и т-раз- рядного кода синхронизации на выход устройства формирование тактовых импульсов на выходе 1 блока 21 управления прекраща- ется и начинается их выдача с выхода 13 блока 21 управления на второй вход второго коммутатора 12. В соответствии с комбинацией сигналов на выходах 4, 3 блока 21 управления второй коммутатор 12 коммутирует

гё„1 второй-.хс,. „а первый выход/Такто « „„„ульсь,фор„„руе.-.е „а ,ходе,3

мент ИЛИ 20 на выход устройства. По окончании считывания битовой карты изменения цветности из третьего блока 15 памяти выдача тактовых импульсов с выхода 13 блока 21 управления прекращается и начина вой карты изменения цветности через эле с выхода 1 на второй вход

Этот код цветности через блок 17 элементов ИЛИ поступает на первый вход ПК 19, на второй вход которого поступают и мпульсь, с

м а ксима ль7ого адреса, которь Й поступает на второй вход второго блока 10 срвавнения с выхода третьего регистра 9. Если сравни JikJLJVjn О., 1 ч/1 - чд1, iiv,.ij..

выхода 7 блока 21 управления, обеспечивая последоватетьную выдачу кода цветности с выхода ПК 19 через элемент ИЛИ 20 на выход устройства. По окончании выдачи кода цветности на выход устройства с выхода 5 блока 21 управления на третий вход второго блока 10 сравнения поступает импульс, обеспечивающий формирование сигнала результата сравнения кода адреса с кодом

,x ir rocpI ° Sa: . 7И 1 k л, 1 /iv- iii i/jj .1-.--.. ..

пульса, формируемого на выходе блока 21 управления, с выхода 7 на первый вход счетчика 8 поступает очередной импульс, обеспечивая формирование нового кода адреса. В случае совпадения сравниваемых кодов адt - -г

ресов на выходе б.лока 10 сравнения фор ресов на выходе б.лока 10 сравнения фор. - , - ,-.1 -f-.T- ft гл гг и ri I.I1I II ui rj r КР И М П hP

мируется единичный импульс. Этот импульс ;)бну.1яет третий регистр 9 и, поступая на 1 блока 21 управления, прекращает выдачу импульсов с выходов 7, 5, 1 блока 21

управления. По окончании обработки кадра импульс с выхода 11 блока 21 управления обнуляет второй счетчик 8. На этом цикл считывания информации о кадре изображения завершается.

Блок 21 управления работает следующим

образом.

В исходном состоянии первый-четвертый триггеры 22, 28, 32, 36, первый-пятый делители 24, 26, 34, 38, 43 обнулены.

Поступающий на вход 2 блока 21 управления импульс одновременно подается на первый вход первого триггера 22, вход элемента НЕ 29. По переднему фронту импуль са, соответствующего кадровому синхроим

10

Импульс, соответствующий кадровому синхроимпульсу очередного кадра, поступает на вход 2 блока 21 управления и обеспечивает работу первого триггера 22. элемента НЕ 29, ГТИ 31, второго делителя 26, первого элемента И 23, второго блока 27 задержки, первого делитачя 24, второго триггера 28, третьего блока 35; задержки по описанному алгоритму.

Импуль с, формируемый одновибрато- ром 30, одновременно поступает на выход 2 блока 21 управления, первый вход третьего триггера 32. По переднему фронту этого импульса третий триггер 22 переключается в единичное состояние. Единичный потенса, соответствующего кадровому синхроим- - выхода третьего триггера 32 пода y J : : : 15 ,-„: «:;вый вх од второг о эле мента И 33.

в единичное состояние. Единичный потенциал с его выхода подается на первый вход первого элемента И 23. Одновременно на второй вход элемента И 23 подается нулевой потенциал с выхода элемента НЕ 29, блокируя прохождение тактовых импульсов с выхода ГТИ 31 через элемент И 23. По окончании импульса, поступающего на вход 2 блока 21 управления, на выходе элемента НЕ 29 устанавливается единичный потенциал, разрешающий прохождение тактовых импульсов

ется на первый вход второго элемента И 33, разрещая прохождение через него тактовых импульсов с выхода ГТИ 31. Эти импульсы поступают на вход третьего делителя 34 и через второй элемент ИЛИ 40 на вы- 20 ход 1 блока 21 управления. После прохождения через элемент И 33 m импульсов на выходе делителя 34 формируется импульс, устанавливающий третий триггер 32 Е нулевое состояние, а пятый триггер 41 - в единичное. Блокируется прохождение тактовых

шающий прохождение тактовых импульсов ,, f р и зГи р;;. на выход первого элемента И 23. Эти им- их поохождение через четвертый

пульсы поступают на вход первого делителя 24, который осуществляет деление частоты входной последовательности на {ш+ -|-1), обеспечивая формирование импульсов с частотой, равной частоте обработки информации АЦП 1. Импульсы с выхода первого делителя 24 одновременно поступают на вход второго делителя 26, выход 9 блока 21 управления, а также через первый блок 25 задержки на выходы 12, 8, 10 блока 21 управления.

С поступлением 2 блока 21 управления импульса, соответствующего строчному синхроимпульсу, на выходе элемента НЕ 29 сформируется нулевой потенциал, который блокирует прохождение Гактовых импульсов через элемент И 23. По окончании строчного синхроимпульса прохождение тактовых импульсов через элемент И 23 возобновится.

После поступления на вход второго делителя 26 М импульсов на его выходе формируется импульс, который устанавливает первый триггер 22 в нулевое состояние, и, будучи задержанным во втором блоке 27 задержки, поступает на выходы И, 6 блока 21

30

рещается их прохождение через четвертый элемент И 42 одновременно на выход 13 блока 21 управления, вход пятого делителя 43. После прохождения через четвертый эле.мент И 42 М импульсов на выходе пятого делителя 43 формируется импульс, устанавливающий пятый триггер 41 в нулевое состояние, четвертый триггер 36 - в единичное и поступающий на второй вход первого э.емен- та ИЛИ 39. Блокируется прохождение импульсов через четвертый элемент И 42 i п;ачи нается их прохождение через третш - лте- мент И 37. Кроме того, импульс с выхода пятого делителя 43 через первый элемент ИЛИ 39 поступает на выход 5 блока 21 управления и через третий блок 35 задержки - 40 на выход 7. Этот импульс обеспечивает фор мирование вторым счетчиком 8 начального адреса. Импульсы с выхода третьего эле мента И 37 о дновременно поступают на вы ход четвертого делителя 38 и через второй элемент ИЛИ 40 - на выход 1 блока 21 уп

5 равления. Четвертый делитель 38 ос ществляет деление частоты входной пос. Ю доватальности импульсов на m и выдачу сформированных импульсов через периьп элемент ИЛИ 39 на выход о блока 21 управ

Деи/плИ, HUk, J Jiiav-i Ji я -, .

управления, a та кже на вход второго тригге- ления и через третий блок Зо задержка J . on ,- ,,.. - Duivnn 7 Пппупжприир имш .пьсов чео

ра 28, вход одновибратора 30. С приходом этого импульса второй триггер 28 переключается в противоположное состояние, обеспечивая смену управляющих сигналов на выходах 3, 4 блока 21 управления, а одноАида Л - , ;t чу 14J .

вибратор 30 формирует импульс, длитель- 55 вертыи триггер 6Ь

,,,, riTiT i. ( ппнупппм н;

tn 4VpVO IJ/Virtii wi I V./ IV - t - j,-. f--

выход 7. Йрохождение импульсов через тре тий элемент И 37 прекра1Цается с приходом на вход 1 блока 21 управления импульс окончания считывания информации о кадре устанавливающего в нулевое состояние чет

ность которого равна времени считывания синхрокода на выход 2 устройства, а задний фронт совпадает с задним фронтом кадрового синхроимпульса очередного кадра.

С приходом на вход одновибратора 3 очередного импульса работа третьего триг гера 32, четвертого триггера 36, пятого триг гера 41, одновибратора 30, второго элемен

Импульс, соответствующий кадровому синхроимпульсу очередного кадра, поступает на вход 2 блока 21 управления и обеспечивает работу первого триггера 22. элемента НЕ 29, ГТИ 31, второго делителя 26, первого элемента И 23, второго блока 27 задержки, первого делитачя 24, второго триггера 28, третьего блока 35; задержки по описанному алгоритму.

Импуль с, формируемый одновибрато- ром 30, одновременно поступает на выход 2 блока 21 управления, первый вход третьего триггера 32. По переднему фронту этого импульса третий триггер 22 переключается в единичное состояние. Единичный потен - выхода третьего триггера 32 пода - выхода третьего триггера 32 пода5 ,-„: «:;вый вх од второг о эле мента И 33.

ется на первый вход второго элемента И 33, разрещая прохождение через него тактовых импульсов с выхода ГТИ 31. Эти импульсы поступают на вход третьего делителя 34 и через второй элемент ИЛИ 40 на вы- 0 ход 1 блока 21 управления. После прохождения через элемент И 33 m импульсов на выходе делителя 34 формируется импульс, устанавливающий третий триггер 32 Е нулевое состояние, а пятый триггер 41 - в единичное. Блокируется прохождение тактовых

,, f р и зГи р;;. их поохождение через четвертый

,, f р и зГи р;;. их поохождение через четвертый

0

рещается их прохождение через четвертый элемент И 42 одновременно на выход 13 блока 21 управления, вход пятого делителя 43. После прохождения через четвертый эле.мент И 42 М импульсов на выходе пятого делителя 43 формируется импульс, устанавливающий пятый триггер 41 в нулевое состояние, четвертый триггер 36 - в единичное и поступающий на второй вход первого э.емен- та ИЛИ 39. Блокируется прохождение импульсов через четвертый элемент И 42 i п;ачи нается их прохождение через третш - лте- мент И 37. Кроме того, импульс с выхода пятого делителя 43 через первый элемент ИЛИ 39 поступает на выход 5 блока 21 управления и через третий блок 35 задержки - 40 на выход 7. Этот импульс обеспечивает фор мирование вторым счетчиком 8 начального адреса. Импульсы с выхода третьего элемента И 37 о дновременно поступают на выход четвертого делителя 38 и через второй элемент ИЛИ 40 - на выход 1 блока 21 равления. Четвертый делитель 38 ществляет деление частоты входной пос. Ю- доватальности импульсов на m и выдачу сформированных импульсов через периьп элемент ИЛИ 39 на выход о блока 21 управ.

ления и через третий блок Зо задержка - Duivnn 7 Пппупжприир имш .пьсов чео

ления и через третий блок Зо задержка Duivnn 7 Пппупжприир имш .пьсов чео

.

вертыи триггер 6Ь

tn 4VpVO IJ/Virtii wi I V./ IV - t - j,-. f--

выход 7. Йрохождение импульсов через третий элемент И 37 прекра1Цается с приходом на вход 1 блока 21 управления импульса окончания считывания информации о кадре, устанавливающего в нулевое состояние четвертыи триггер 6Ь

( ппнупппм н;

С приходом на вход одновибратора 30 очередного импульса работа третьего триггера 32, четвертого триггера 36, пятого триггера 41, одновибратора 30, второго элемента И 33, третьего элемента И 37, четвертого элемента И 42 третьего делит1 ля 34, четвертого делителя 38, пятого делителя 43, элемента ИЛИ, первого элемента ИЛИ 39, третьего блока 35 задержки повторяется по описанному алгоритму.

Формула изобретения

1. Устройство для сжатия цветовых сигналов телевизионных изображений, содержащее аналого-цифровой преобразователь (АЦП), блок установки опорного уровня, первый регистр, второй регистр, первый блок задержки, первый блок сравнения, первый счетчик, второй счетчик, третий регистр, пер вый коммутатор, второй блок сравнения, первый блок памяти, второй блок памяти, блок элементов ИЛИ, формирователь кода синхронизации, преобразователь кода (ПК), элемент ИЛИ, блок управления, первый выход которого подключен к второму входу ПК, первый вход которого подключен к выходу блока элементов ИЛИ, третий вход которого подключен к выходу формирователя кода синхронизации, вход которого подключен к второму выходу блока управления, третий выход которого подключен к четвертому входу первого коммутатора, четвертому входу первого блока памяти и третьему входу второго блока памяти, четвертый вход которого объединен с третьим входом первого блока памяти, третьим входом первого коммутатора и подключен к четвертому выходу блока управления, пятый выход которого подключен к третьему входу второго блока сравнения, выход которого подключен к третьему входу третьего регистра и первому входу блока управления, шестой выход которого подключен к второму входу третьего регистра, выход которого подключен к второму входу второго блока сравнения, первый вход которого объединен с вторым входом первого коммутатора и подключен к выходу второго счетчика, первый вход которого подключен к седьмому выходу блока управления, восьмой выход которого подключен к третьему входу первого блока сравнения, второй вход которого подключен к выходу второго регистра, второй вход которого подключен к девятому выходу блока управления, десятый выход которого подключен к второму входу первого регистра, третий вход которого объединен с третьим входом второго регистра, вторым входом первого счетчика, вторым входом второго счетчика и подключен к Одиннадцатому выходу блока управления, втор/ой вход которого подключен к выходу блока установки опорного уровня, вход которого объединен с входом ALJ,n и является входом устройства., выход АЦП подключен к первому входу первого регистра, выход которого подключен к первому входу второго регистра, первому входу первого блока сравнения,и входу первого блока задержки, выход которого подключен к первому входу первого блока памя0

О

ти, первому входу второго блока памяти, выход которого подключен к второму входу блока элементов ИЛИ, первый вход которого подключен к выходу первого блока памяти, второй вход которого подключен к первому выходу первого коммутатора, второй выход которого подключен к второму входу второго блока памяти, первый вход первого коммутатора объединен с первым входом третьего регистра и подключен к выходу первого счетчика, отличающееся тем, что, с целью увеличения коэффициента сжатия, введены второй коммутатор, элемент ИЛИ, третий блок памяти и четвертый блок памяти, выход которого подключен к первому входу элемента 5 ИЛИ, второй вход которого подключен к выходу третьего блока памяти, первый вход которого подключен к первому выходу второго коммутатора, первый вход которого подключен к двеннадцатому выходу блока управления, тринадцатый,выход которого под- - ключен к второму входу второго коммутатора, третий вход которого объединен с вторым входом, третьего блока памяти и подключен к четвертому выходу блока управления, третий выход которого подключен к первому входу четвертого блока памяти и четвертому входу второго коммутатора, второй выход, которого подключен к второму входу четвертого блока памяти, третий вход которого объединен с третьим входом третьего блока памяти и подключен к первому 0 входу первого счетчика, третий вход элемента ИЛИ подключен к выходу ,ПК, а выход элемента ИЛИ является выходом устройства. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит после- довате„|1ьно соединенные первый триггер, первый элемент И, первый делитель и первый блок задержки, последовательно соединенные второй делитель, второй блок задержки и второй триггер, последовательно соединенные одновибратор, третий триггер, второй элемент И и третий делите.ль, а также элемент НЕ, генератор тактовых импульсов (ГТИ) и третий блок задержки, при этом зход ,-;лемента НЕ соединен с первым вхо- ,цом первого триггера, второй вход которого подключен к выходу второго делит&пя, вход которого соединен с выходом первого делителя, выход элемента НЕ п-одключен к второму входу первого элемента И, третий вход которого соединен с вторым входом второго элемента И и выходом ГТИ, вход одновиб- ратора соединен с входом второго триггера, введены последовательно .инeнныe четвертый триггер, третий элемент И, четвертый делитель и первый элемент ИЛИ, после- ,a,OBaTejibHO соединенные пят,ый триггер, чеп - вертый элемент И и пятый делитель, а также второй элемент ИЛИ, при это.м первый вход четвертого триггера подключен к первому яходу пятого триггера, второ,му входу первого элемента ,ИЛИ и выходу пятого делите- ,Я, второй вход пятого триггера подключен :( второму входу третьего триггера и выхо5

0

5

0

3S& T llBblX.

65ЫХ : 9SblJ(

Шы1 В&ых- ЮВых28ш.

16ых.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия цифровых телевизионных сигналов цветного изображения | 1988 |

|

SU1529471A1 |

| Адаптивное устройство для сжатия цветовых сигналов телевизионных изображений | 1988 |

|

SU1631752A1 |

| Устройство для сжатия цветовых сигналов телевизионных изображений | 1987 |

|

SU1515400A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

| Устройство для сжатия телевизионных сигналов цветного изображения | 1989 |

|

SU1633523A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Устройство для воспроизведения видеосигнала | 1987 |

|

SU1555918A1 |

| Устройство для ввода информации | 1986 |

|

SU1397924A1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

Изобретение относится к телевидению. Цель изобретения - увеличение коэффициента сжатия. Телевизионный сигнал преобразуется АЦП 1 в M-разрядный код цветности. Список кодов цветности записывается в первый или второй блоки памяти 13, 14, а карта изменения цветности - в третий или четвертый блоки 4 памяти 15 и 16. Выбор блоков памяти осуществляется с помощью блока управления 21. Коды цветности текущего и предыдущего элементов изображения поступают с выходов регистров 3, 4 на входы первого блока сравнения 6, где поразрядно сравниваются. Если коды цветности текущего и предыдущего элементов совпадают, состояние счетчика 7 не меняется и запись кода цветности текущего элемента отображения производится в ту же ячейку памяти, в которую до этого был записан код цветности предыдущего элемента. В случае несовпадения кодов цветности счетчик 7 увеличивает свое состояние на единицу, формируя новый адрес. Цель изобретения достигается введением третьего и четвертого блоков памяти 15 и 16, второго коммутатора 12 и элемента ИЛИ 20. 1 з.п. ф-лы, 2 ил.

| Устройство для сжатия цифровых телевизионных сигналов цветного изображения | 1988 |

|

SU1529471A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-11-15—Публикация

1988-02-18—Подача