тыми входами блоков анализа основного байта состояния и приема уточненных байтов состояния, второй выход соединен с пять1м входом блока приема уточненных байтов состояния, третий выход соединен с пятым входом блока анализа основного байта состояния четвертый выход подключен к третьему входу блока управления регистрацией, выход блока анализа основного байта состояния соединен с пятым входом блока приема сигналов окончания операций вводавьгеода и с четвертым входом блока. управления регистрацией, Лятый, шестой, седьмой и восьмбй входа которого соединены соответственно с вторым и третьим выходами блока приема сигналов окончания операции ввода-выводй и с первым и вторым выходами блока вывода информации об ошибках, выходы блока управления регистрацией с первого по десятьй соединены соответственно с управляющими входами блока приема уточненных байтов состояния, блока памяти, блока счетчиков ошибок, блока вывода информации об ошибках, дешифратора и блока переполнения, информационный вход блока переполнения подключен к первому выходу блока счетчиков ошибок, первый и второй входы которого соединены соответственно с выходами блока памйти и блока приема уточненных байтов состояния, второй выход блока счетчиков ошибок соединен с вторым входом блока памяти и с информационным входом блока вывода информации об ошибках, причем блок приема сигналов установления связи содержит элементы И, ИЛИ, триггеры и генератор одиночных импульсов, вход которого соединен с выходом элемента ИЛИ, а выход является вторым выходом блока, выход элемента ИЛИ подключен к третьему выходу блока, входы элемента ИЛИ соединены соответственно с выходами первого и второго триггеров, выход первого триггера подключен к второму выходу

блока, первые входы первого и второго триггеров соединены соответственно с выходами первого и второго элементов И, вторые входы подключены к третьему входу блока, первьй и второй входы первого элемента И и первый вход второго элемента И соединены с первым входом блока, второй вход которого подключен к третьему входу первого элемента И и к второму и третьему входам второго элемента И, блок анализа команд канала содержит триггер, схему сравнения, узел набора кодов, элемент И, группу элементов И, причем первые входы элементов И группы подключены к третьему входу блока, вторые входы соединены с выходом элемента И, выходы группы элементов И и выходы узла набора кодов соединены соответственно с входами схемы сравнения, выход которой подключен к первому входу триггера, втрой вход которого является пятым входом блока, первый и второй выходы триггера являются соответственно первьм и вторьм выходами блока, входы элемента И являются соответственно первым, вторьм и четвертым входами блока, блок приема сигналов передачи абонентом байта состояния содержит элементы И, НЕ и элемент ИЛИ, причем выход элемента ИЛИ является третьим выходом блока, входы элемента ИЛИ подключены соответственно к выходам первого и второго элементов И и к третьему входу блока, выходы третьего и четвертого элементов И подключены соответственно к второму и первому выходам блока, входы пятого элемента И соединены соответственно с выходом третьего элемента И и с четвертым входом блока, выход пятого элемента И является четвертьм выходом блока, первый вход блока соединен с входами первого, второго и третьего элементов НЕ, с первыми входамипервого и третьего элементов И, с первым и вторым входами второго элемента И второй вход блока соединен с вторьм и третьим входами первого элемента И, с первьм и вторим входами четвертого элемента И, с третьим входом второго элемента И и с вторьм входом третьего э1пемента И, третий вход которого подключен к выходу третьего элемента НЕ, третий и ч трертый входы четвертого элемента И соединены соответственно с выходами первого и второго элементов НЕ, блок анализа основного байта состояния содержит два элемента И и триггер, причем выход триггера является выходом блока, первый вход первого элемента И является первым входом блока, второй.

третий и четвертьй входы которого соединены соответственно с входами второго элемента И, выход которого подключен к второму входу первого элемента И, выход которого соединен с первым входом триггера, второй вход которого является пятьм входом блока, блок приема сигналов окончания операции ввода-вывода содержит .элемент И, ИЛИ,НЕ, задержки, причем первый вход блока соединен с входом jnepBoro элемента НЕ с первыми входами первого, BTQporo и третьего элементов И, второй вход блока подключен к входу второго элемента НЕ, выход которого соединен с вторыми входами первого, второго и третьего элементов И, третьи входы которых подключены к выходу первого элемента НЕ, выход первого элемента И подключен к первым входам четвертого и пятого элементов И, выходы второго и третьего элементов И соединены соответственно с первым и вторь входайи первого элемента ИЛИ, второй вход четвертого элемента И соединен с третьим входом блока, выход четвертого элемента И соединен с третьим входом первого элемента ИЛИ и с первым входом шестого элемента И, второй вход которого соединен с пятым входом блока, второй вход пятого элемента И является четвертым входом блока, вькод шестого элемента И соединен с первым входом второго .элемента ИЛИ, выход которого .является вторым выходом блока, выход пятого элемента И подключен к третьему выходу блока, к второму входу второго элемента ИЛИ и к входу элемента задержки, выход которого подключен к четвертому входу первого элемента ИЛИ, вькод которого является первым выходом блока, блок управления регистрацией содержит элементы И, ИЛИ, НЕ, триггеры., группыэлементов И, регистр, сдвигающие регистры и генератор тактовых импульсов, причем вькод генератора тактовых импульсов подключен к входу элемента НЕ и к первым входаЛ. первого и второго элементов И, выход первого элемента И соединен с входом первого сдвигающего регистра, второй вход первого элемента И и первые входы элементов И первой группы соединены с выходом первого триггера, второй выход которого подключен к

второму входу второго элемента И, третий вход которого соединен с первым выходом второго триггера, выход второго элемента И подключен к вход второго сдвигающего регистра, второ выход второго триггера соединен с первым входом третьего элемента И, iвторой и третий входы которого подключены соответственно к вькоду элемента НЕ и к седьмому входу блока, входы второго триггера соединены соответственно с пятым входом блока и с первым выходом второго сдвигающего регистра, выходы которого с второго по шестой подключены соотвественно к входам первого элемента ИЛИ, выход которого подключен к первым входам элементов И второй группы, выходы которых и выходы элементов И первой группы являются десятым выходом блока, вторые входы элементов И первой группы :оединены с восьмым входом блока, первый и второй входы первого триггера соединены соответственно с первым вьжодом первого сдвигающего регистра и с выходом третьего элемента И, входы четвертого элемента И соединены с третьим и четвертым входами блока входы второго элемента ИЛИ соединены с третьим и шестьм входами блока, выход четвертого элемента И подключен к первому входу третьего триггера, второй вход третьего триггера и первая группа входов регистра соединены с выходом третьего элемента. ИЛИ, выход третьего триггера является пятым выходом блока, выход второго элемента ИЛИ подключен к первым входам элементов И третьей группы, вторые входы которых соединены с вторьм входом блока выходы элементов И третьей группы соединены с второй группой входов регистра, выходы которого подключены соответствейно к вторым входам элементов И второй группы, первый вход блока подключен к первому входу третьего элемента И, второй вход которого и первый выход блока соединены с седьмьм выходом второго сдвигающего регистра, второй, третий, четвертый, пятый и шестой выходы которого соединены соответственно с первыми входами четвертого и пятого элементов ИЛИ, с седьмым, третьим и четвертым выходами блока, второй выход первого сдвигающего регистра соединен с восьмым выI ходом блока и с вторым входом четi вертого элемента ИЛИ, вькод которого является шестым выходом блока, третий и четвертый выходы первого сдвигающего регистра соединены соответственно с девятым выходом блока и с вторым входом пятого элемента ИЛИ, выход которого Является вторым выходом блока, блок переполнения содержит триггер, усилитель, звуковой сигнализатор, группу элементов И, регистры, индикатор и Элемент коммутации, причем выход элемента коммутации подключен к первому входу триггера и к первым входам регистров вторые входы кото;рых соединены соответственно с выходами группы элементов И, первые входы которых соединены с управляющим входом блока, а вторые входы подключены к информационному входу блока, выходы регистров подключены соответственно к входам дешифратора, выходы которого подключены соответственно к входам .индикатора, второй вход триггера соединен с информационным входом блока, выход триггера через усилитель .подключен к входу звукового сигнализатора, блок приема уточненного байта состояния содержит группы элементов И, регистры, элементы ИЛИ,

элемент И, сдвигающий регистр и генератор одиночных импульсов, причем выход генератора одиночных импульсов подключен к первому входу элемета ИЛИ и к первому входу сдвигающего регистра, второй вход которого соединен с выходом элемента И, вход генератора одиночных импульсов и певый вход элемента И подключены к второму входу блока, второй вход элемента И соединен с пятым входом блока, второй вход элемента ИЛИ является управляющим входом блока, группа входов сдвигающего регистра соединена с первым входом блока, выходы сдвигающего регистра соединены соответственно с первыми входами Элементов И первой группы, вторые входы которых подключены к четвертому входу блока, первые входы элементов И каждой группы, начиная с второй, соединены с третьим входом блока, вторые входы подключены к выходу сооответствующего элемента И первой группы, выходы элементов И каждой группы, начиная с второй, подключены к первой - группе входов соответствующего регистра, вторая группа входов каждого регистра соединена с выходом.элемента ИЛИ выходы регистров являются выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения канала ввода-вывода с абонентом | 1989 |

|

SU1695312A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения вычислительных машин | 1982 |

|

SU1065852A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Многоканальный адаптер | 1987 |

|

SU1495806A1 |

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СТАТИСТИЧЕСКИХ ДАННЫХ О PABOTO АИПАР АТУШ ВЫЧИСЛИТЕЛЬНЫХ МАШИН И СИСТЕМ, содержащее блок приема сигналов установления связи, блок ана.лиза команд канала, блок приема адреса, блок приема сигналов передачи абонентом байта состояния, блок приема .сигналов окончания операции ввода - вывода, первые и вторые входы которых соединены соответственно с первым и вторым управляющими входами устройства, третий вход блока анализа команд канала соединен с первым информационным входом устройства, третий вход блока приема адреса и первый вход блокаанализа основного байта состояния соединены с вторым информационным входом устройства, выход дешифратора соединен с первьм входом блока памяти, отличающее с я тем, что, с целью сокращения затрат обо- : рудования, оно содержит блок приема уточненных байтов состояния, блок управления регистрацией, блок счетчиков ошибок, блок переполнения и блок вьшода информации об ,i2Ci :, ошибках, причем первый выход блока прИ1ема сигналов установления связи соединен с четвёртым входом блока анализа команд канала, пятый вход которого, третий вход блока приема сигналов установления связи, четвертьй вход блока приема адреса и первьй вход блока приема уточненных байтов состояния соединены с первьм выходом блока приема сигналов окончания операций вводавывода, второй выход блока приема сигналов установления связи соединен с пятым входом блока приема адреса, с третьим входом блока приема сигналов передачи абонентом байш та состояния, с первьм входом блока управления регистрацией, третий выход блока приема сигналов установления связи соединен с шестым входом блока приема адреса и с вторым входом блока анализа основного байVa состояния, первый выход блока анализа Команд канала соединен с чето вертым входом блока приема сигналов 00 О) передачи абонентом байта состояния и с третьими входами блока анализа 4аь основного байта состояния и блока СО СР приема сигналов окончания операции ввода-вывода, а второй выход соединен с четвертым входом блока приема сигналов окончания операций ввода-вывода и с вторым входом блока приема уточненных байтов состояния, третий вход ifOToporo соединен с вторым информационным входом устройства, выход блока приёма адреса соединен с вторым входом ,блока управления регистрацией, первый выход блока приема сигналов передачи абонентом байта состояния соединен с четвер

Изобретение относится к вычислительной технике и может быть использовано для сбора и первичной обработки статистических данных о работе периферийных устройств электронно-вычислительных машин (ЭВМ), информационно-вычислительных систем, автоматизированных систем управления, вычислительных центров в процессе их эксплуатации и испытаний.

Известно устройство, содержащее .блок ввода данных, узел регистрации временной диаграммы, блок управления, блок приема, блок буферной памяти и блок коммутации. Данное устройство позволяет собирать и обрабатывать данные о работе аппаратуры вычислительных мащин Cl

Недостатком этого устройства является необходимость создания в электрических цепях контролируемых устройств специальных контрольных точек и установки при необходимости в Этих точках специальных датчиков, а также прокладки дополнительных измерительных кабелей от этих контрольных точек и датчиков к устройству контроля, что усложняет аппаратурную реализацию устройств.

Наиболее близким к изобретению по технической сущности и достигаемому результату является система контроля вычислительных машин, содержащая последовательно соединенные модуль сопряжения с каналом ввода-вывода, модуль сбора информации и счетно-решающее устройство. Модуль сопряжения с каналом пред назначен для приема из канала ввода-вывода данных, адресов, команд и информации о состоянии и содержит шесть входных детекторов (блоки приема) последовательностей этапов прохождения операций ввода-вьгоода, селектор данных, входной регистр и генератор кодов событий. Модуль сбора информации осуществляет селек цию информации, относящейся к конкретному периферийному устройству и формирование по каждому периферийному устройству информационных паке тов и содержит восемь приемных регистров, буферньм регистр данных, счетчик байтов данных, блок контрол четности, запоминаняцее устройство для хранения информационных пакетов регистры адресов считывания и записи, блок контроля запоминающего устройства, регистры адреса, комавд и состояния, дешифратор команд, входной транслятор, блок сравнения и управления, выходной блок со схемой управления и контроля, счетчик выходных записей, регистры адреса и состояния модуля сбора информации Кроме того, модуль сбора информации содержит блоки управления, с помощь которых задаются адреса контролируе мьк периферийных устройств, а также типа контролируемых параметров и/шга зоны регистрируемых данных. Счетнорешающее устройство ведет обработку полученных данных. В качестве после него может быть использована ЭВМ или микропроцессор. Рассмотренная, система может осуществлять сбор и обработку статистических данных о работе периферийных устройств, не затрачивая на их выполнение ни ресурсов оборудования, ни рабочего времени контролируемой ЭВМ С2 . Недостатком данной системы явля ется некоторая сложность аппаратурных решений, возникаемая из-за многоцелевого назначения системы контроля и разрыва во времени процессов регистрации и обработки информации. Цель изобретения - сокращение затрат оборудования. Поставленная цель достигается тем, что устройство, содержащее блок приема сигналов установления связи, блок анализа команд канала. 394 . блок приема адреса, блок приема сигналов передачи абонентом байта состояния, блок приема сигналов окончания операции ввода-вывода, первые и вторые входы которых соединены соответственно с первым и вторым управлякяцими входами устройства, третий вход блока анализа команд канала соединен с первым информационным входом устройства, тре-Гий вход блока приема адреса и первый вход блока анализа основного байта состояния соединены с вторым информационным входом устройства, выход дешифратора соединен с первым входом блока памяти, содержит блок приема уточненных байтов состояния, блок Iуправления регистрацией, блок счетчиков ошибок, блок переполнения и блок вывода информации об ошибках, причем первый выход блока приема сигналов установления связи соединен с четвертым входом блока анализа команд канала, пятый вход которо го, третий вход блока приема сигна,пов установления связи, четвертый вход блока приема адреса и первый вход блока приема уточненньпс байтов состояния соединены с первым |Выходом блока приема сигналов окон(чания операцией ввода-вывода, второй выход блока приема сигналов установления связи соединен с пятым входом блока приема адреса, с третьим входом блока приема сигналов передачи абонентом байта состояния, с первьм входом блока управления регистрацией, третий выход блока приема сигналов установления связи соединен с шестым входом блока приема адреса и с вторым входом блока анализа основного байта состояния, первый выход блока анализа команд канала соединен с четвертым входом блока приема сигналов передачи абонентом байта состояния и с третьими входами блока анализа основного байта состояния и блока приема сигналов окончания операции ввода-вывода, а второй выход соединен с четверым входом блока приема сигналов окончания операций ввода-вывода и с вторым входом блока приема уточненных байтов состояния, третий вход которого соединен с вторым информационным входом устройства, выход блока приема адреса соединен с вторым входом блока управления регистрацией, первый выход блока приема сигналов передачи абонентом байта состояния соединен с четвертыми входами блоков анализа основного байта состояния и приема уточненных байто состояния, второй выход соединен с пятым входом блока приема уточнен ных байтов состояния, третий выход соединен с пятым входом блока анали за основного байта состояния, четвертый выход подключен к третьему входу блока управления регистрацией выкод блока анализа основного байта состояния соединен с пятым входом блока приема сигналов окончания операций ввода-вывода и с четвертым входом блока управления регистрацие пятый, шестой, седьмой и восьмой входы которого соединены Соответственно с вторым и третьим выходами блока приема сиУ-налов окончания операции ввода-вывода и с первым и вторым выходами блока вьюода информации об ошибках, выхода блока управления регистрацией с первого по десятый соединены соответственно с управляющими входами блока прие ма уточненных байтов состс яния, блока памяти, блока счетчиков ошибок, блока вьюода информации об ошибках,. дешифратора и блока переполнения, информационный вход блока переполнения подключен к первому выходу блока счетчиков ошибок, первый и второй входы которого соединены соответственно с выходами блока памяти и блока приема уточненны байтов состояния, второй выход блока счетчиков ошибок соединен с вторьнч входом блока памяти и с информационным входом блока,вьюода ин формации об ошибках, причем блок приема сигналов установления связи содержит элементы И, ИЛИ, триггеры и генератор одиночных импульсов, вход которого соединен с выходом элемента ИЛИ, а выход является вторьы выходом блока, выход элемента ИЛИ подключен к третьему выходу блока, входы элемента ИЛИ соединены соответственно с выходами первого и второго триггеров, выход перво го триггера подключен к второму выходу блока, первые входы первого и второго триггеров соединены соответ ственно с выходами первого и второг элементов И, вторые входы подключены к третьему входу блока, первый и второй входы первого элемента И и первый вход второго элемента И соед 39 С первым вхчодом , второй которого П(щкл1в4:в № к v iPfbetty входу первого в и« второму и третьему входам второго элемента И, блок анализа команд канала содержит триггер, схему сравнения, узел набора кодов, элемент И, группу элементов.И, причем перв1ле юсоды элементов И группы подк вочены к третьему входу блока, вторые «aojof соединены с выходом элемента И, выходы группы элементов И и вькоды узла набора кодов соединены соответственно с входами схемы сравнения, выход которой подключен к первому входу триггера, второй вход которого является пятьв4 входом блока, первый и второй выкоды триггера являются соответственно первым и вторым выходами блока, входы элемента И являются соответственно первым, вторьи и четвертым входами блока, блок приема сигналов передачи абонеитЬм байта состояния содержит элемёйты И, НЕ и элемент ШШ, прич вьиод элемента ИЛИ является третьим выходом блока, входы элемента ИЛИподключв ны соответственно к первбго и второго элементов И и к третьему входу блока, выходы третьего и четвертого элементов И подключены соответственно к второму и первому выходам блока, входы пятого элемента И соединены соответственно с выходом третьего элемента И и с четвертин ВХОДОМ блока, выход пятого элемента И является четвертым выходом блока, первый вход блока соединен с входами первого, второго и третьего элементов НЕ, в первыми входами первого и третьего элементов И, с первым и BTopbiM входами второго элемента И, второй вход блока соединен с вторым и третьим входами первого элемента И, с первьм и вторым входами четвертого элемента И, с третью входом второго элемента И и с вторым входом третьего элемента И, третий вход которого подключен к выходу третьего элемента НЕ, трет и четвертый входы четвертого элемента И соединены соответственно с выходами первого и второго элементов НЕ, блок анализа основного байта состояния в устройстве соде1йкит два элемента И и триггер, причем выход триггера является выходом бjfока, первый ВХ0Д первого элемента И является первьм входом блока, второй, третий

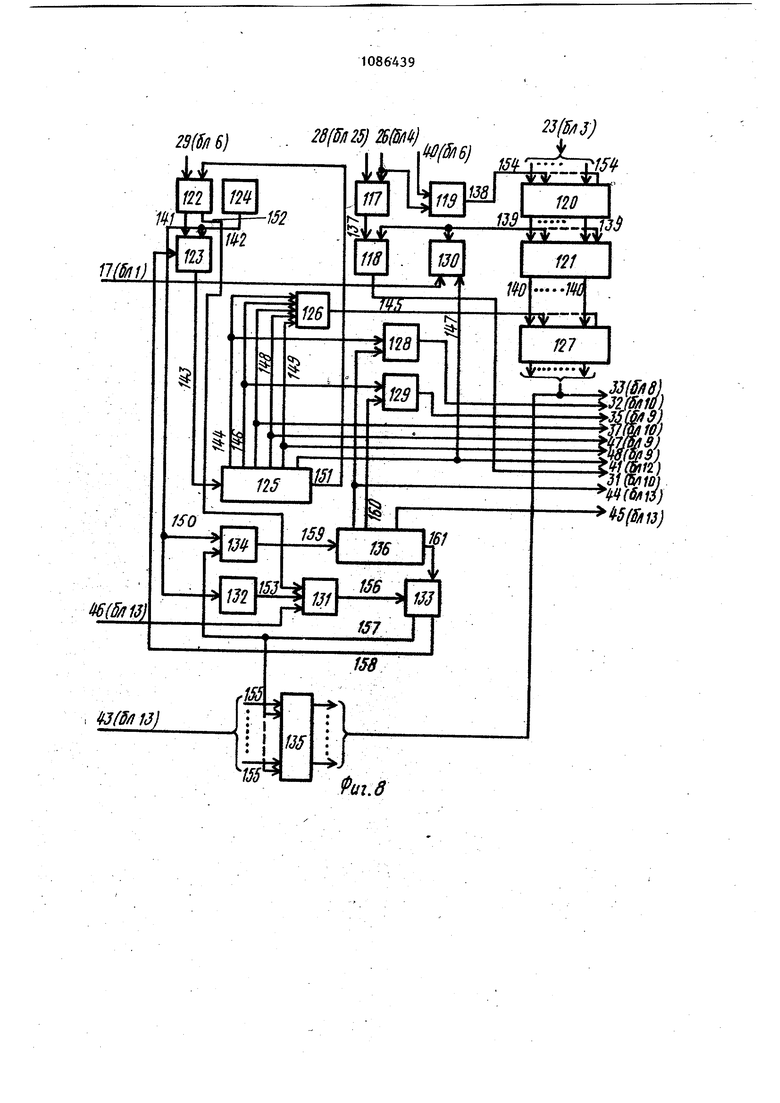

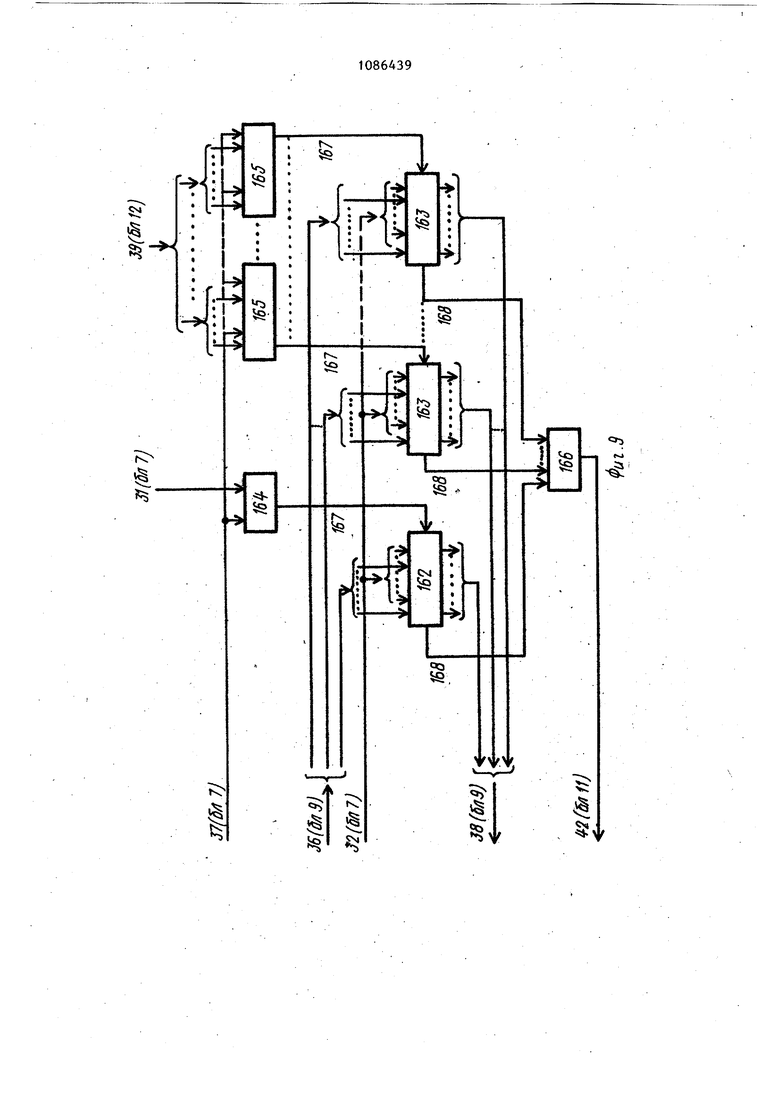

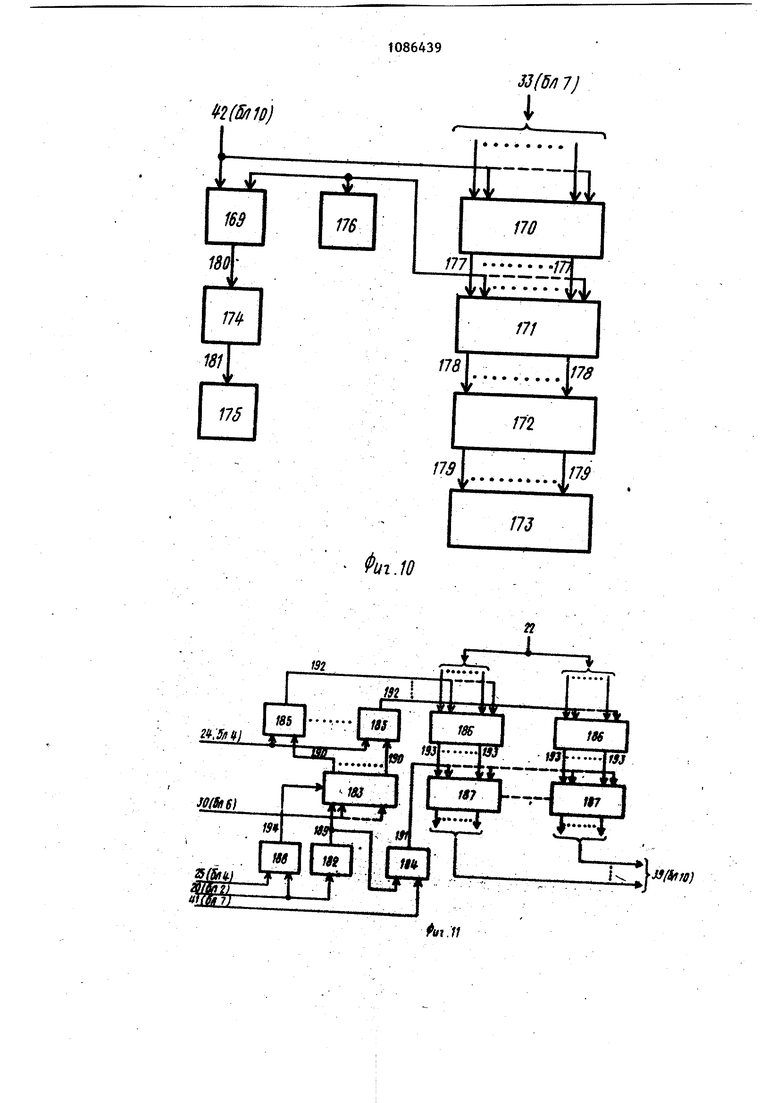

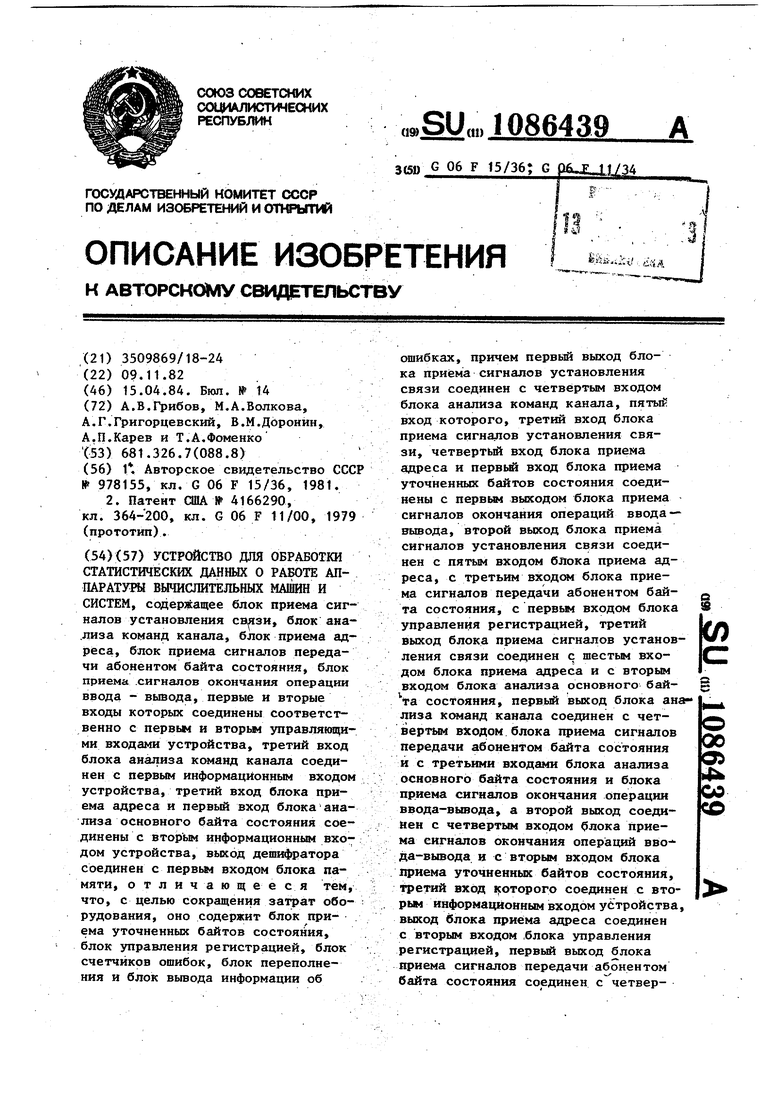

и четвертый входы которого соединены соответственно с входамц второго элемента И, выход которого подключен к второму входу первого элемента И, выход которого соединен с первым входом триггера, второй вход которого является пятьм входом блока, блок приема сигналов окончания операций ввода-вьтода содержит элементы И, ИЛИ, НЕ, iзадержки. Причем первый вход Ьлока соединен с входом первого элемента НЕ, с первыми входами первого, второго и третьего элeмёнtoв И, второй вход блока подключен к входу второго элемента НЕ, выход которого соединен с вторыми входами первого, второго и третьего элементов И, третьи входы которых подключены к выходу первого элемента НЕ, выход первого элемента И подключен к первым входам четвертого и пятого элементов И выходы второго и третьего элементов И соединены соответственно с певым и «зторьм входами первого элемента ИЛИ, второй вход четвертогр элемента И соединен с третьим вхо-г дом блока, выход четвертого элемента И соединен с третьим входом первого элемента ИЛИ и с первым входом шестого элемента И, второй вход которого соединен с пятым входом блока, второй вход пятого элемента И является четвертым входом блока, выход шестого элемента И соединен с. первьм -входом второго элемента ИЛИ, выход которого является вторым выходом блока, выход пятого элемента И подключен к третьему выходу блока, к второму входу второ го элемента ИЛИ и к входу элемента задержки, вьпсод которого подключен к четвертому входу первого элемента RIffi, выход которого является первым. выходс, блока, блок управления регистрацией содержит И, ИЛИ, НЕ, триггеры, группы элементов И, регистр, сдвигаю1ф1е регистры и генератор тактовых импульсов, причем выход генератора тактовых им- ; пульсов подключен к входу элемента НЕ и к первым входам первого и второго элементов И, в.ыход первого элемента И соединен с входом первого сдвигающего регистра, второй вход первого элемента И и первые входы элементов И первой группы сое динены с выходом первого триггера, второй выход которого подключен к

первому входу второго элемента И, TpeTirii вход которого соединен с первым выходом второго триггера, выход второго элемента И подключен к входу второго сдвигающего регистра, второй выход второго триггера соединен с первым входом третьего элемента И, второй и третий входы которого подключены соответственно к выходу элемента НЕ и к седьмому

0 входу блока, входы второго триггера соединены соответственно с пятым входом блока и с первым выходом второго сдвигакщего регистра, выходы которого с второго по шестой

5 подключены соответственно к входам первого элемента ИЛИ, выход которого подключен к первым входам элементов И второй группы, выходы которых и выходы элементов И первой

0 группы являются десятым выходом блока, вторые входы элементов И первой группы являются десятым выходом блока, вторые входы элементов И первой Группы соедине5ны с восьмым входом блока, первь и второй входы первого триггера соединены соответственно «с первым выходом первого сдвигакнцего регистра и с выходом третьего элемента И,

0 входы четвертого элемента И соединены с третьим и четвертым входами блока, входы второго элемента ИЛИ соединены с третьим и шестым входами блока, выход четвертого элемента И подключен к первому входу третьего триггера, второй вход третьего триггера и первая группа входов регистра соединены с выходом третьего элемента ИЛИ, выход третьего триггера является пятым выходом блока, выход второго элемента ИЛИ подключен к первым входам элементов И третьей группы, вторые входы которых соединены с вторым входом блока, выходы элементов И третьей группы соединены с второй группой входов регистра, выходы которого подключены соответственно к вторым входам элементов И

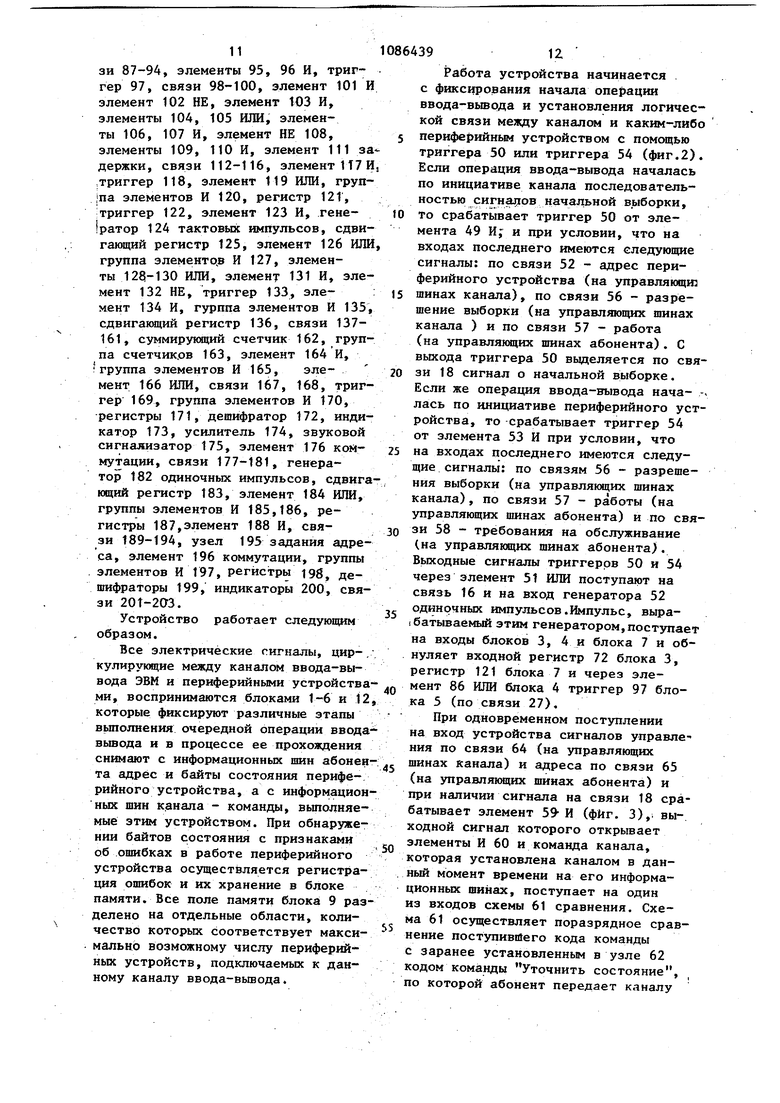

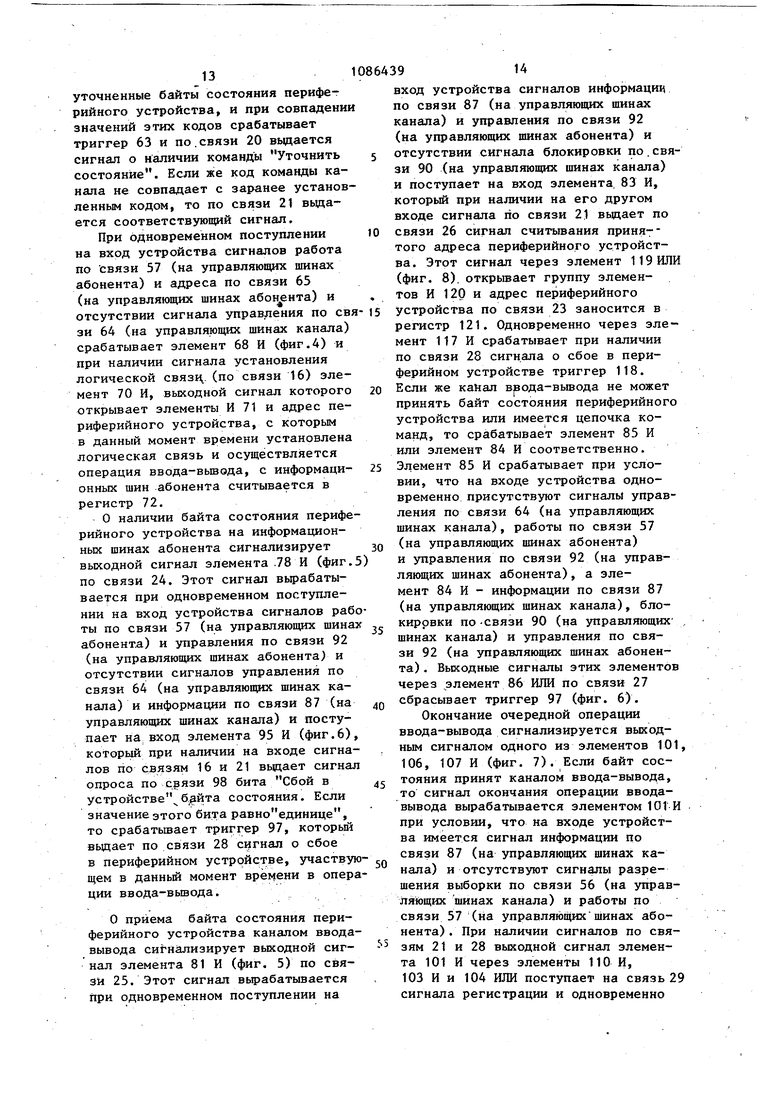

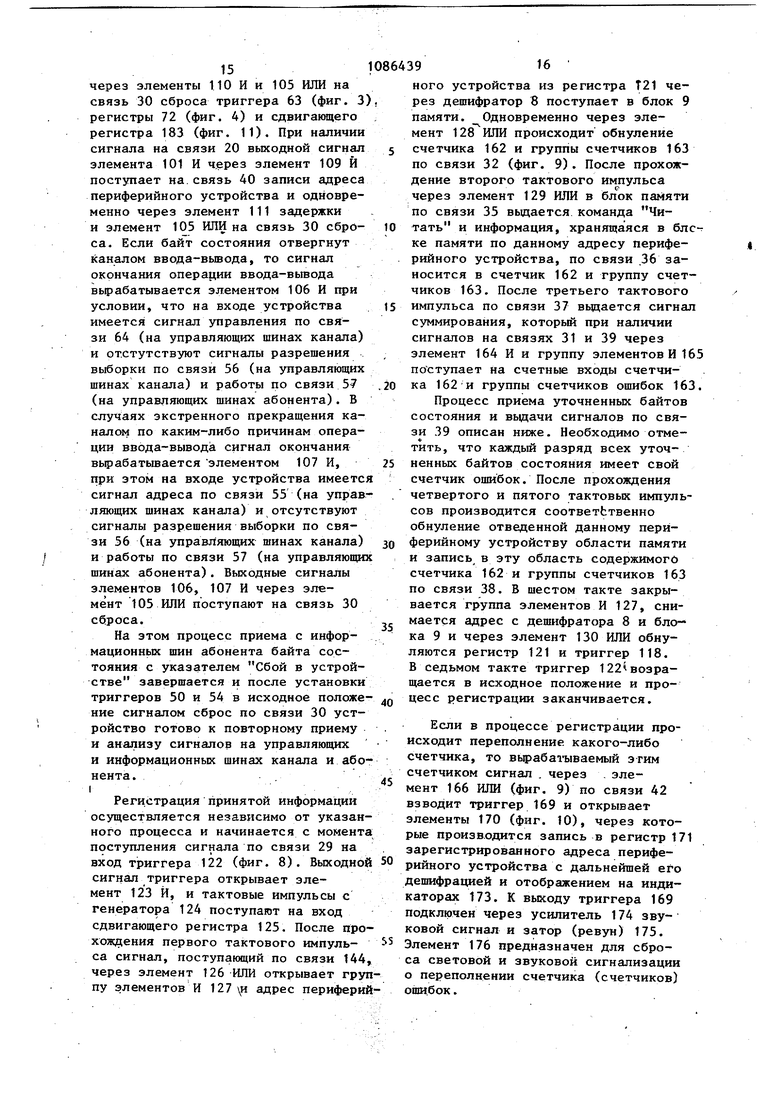

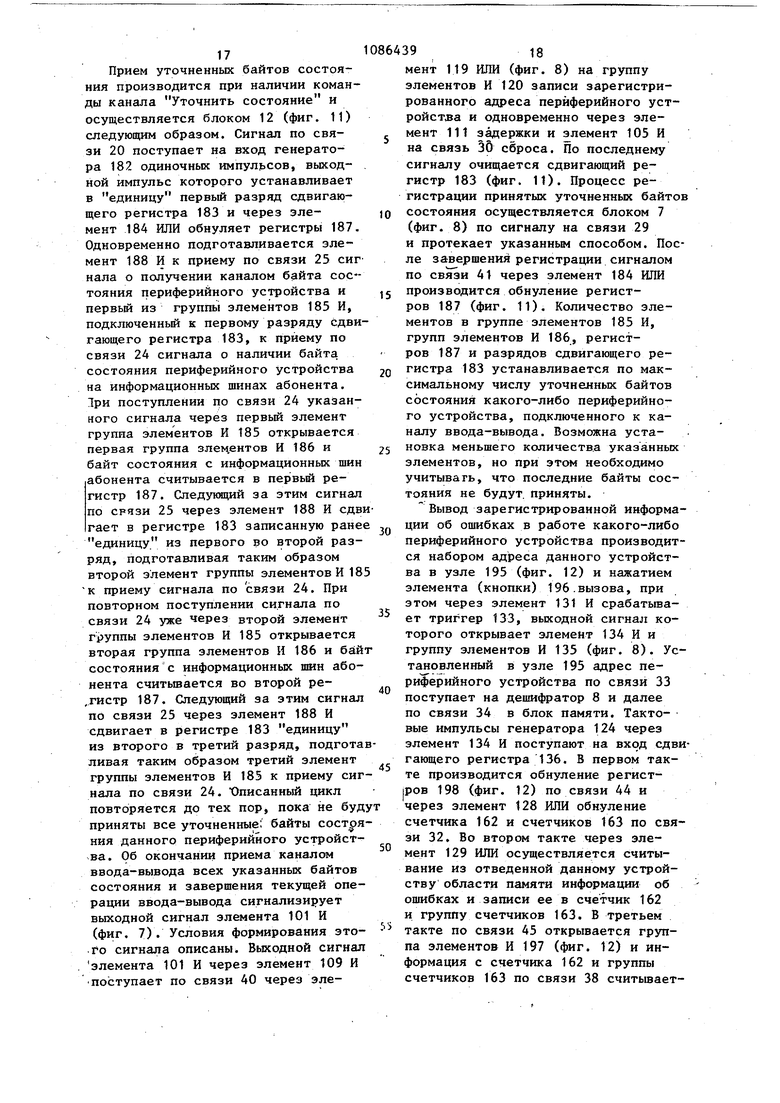

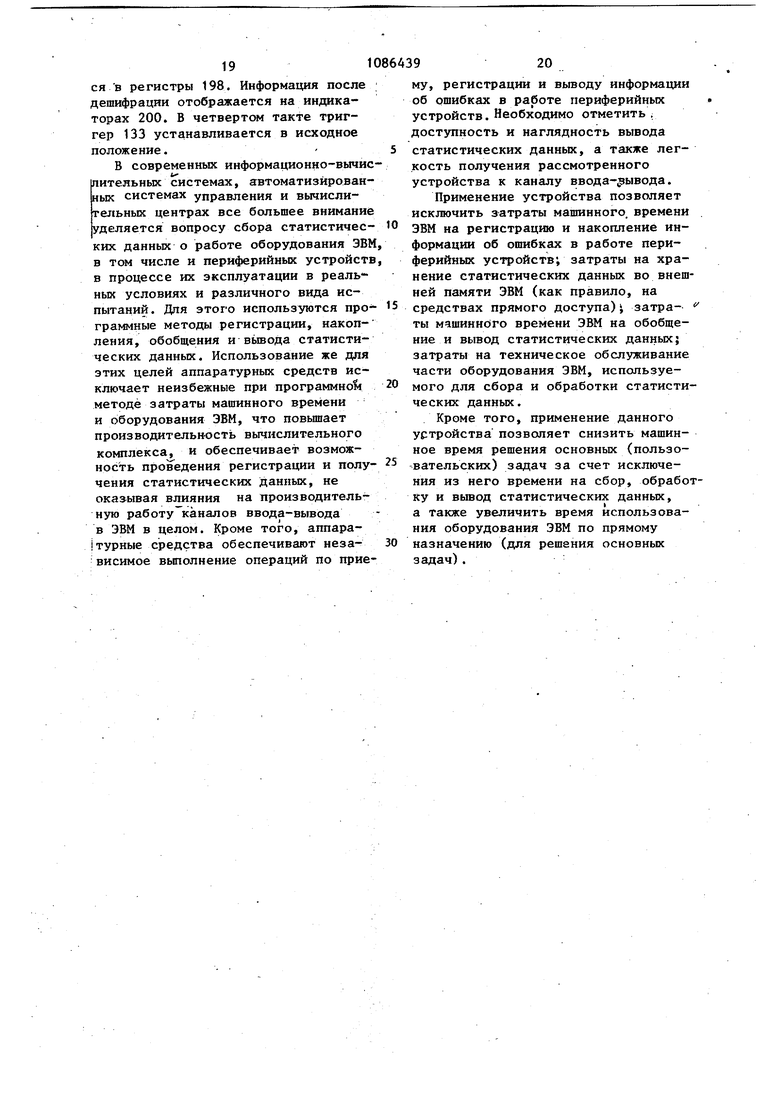

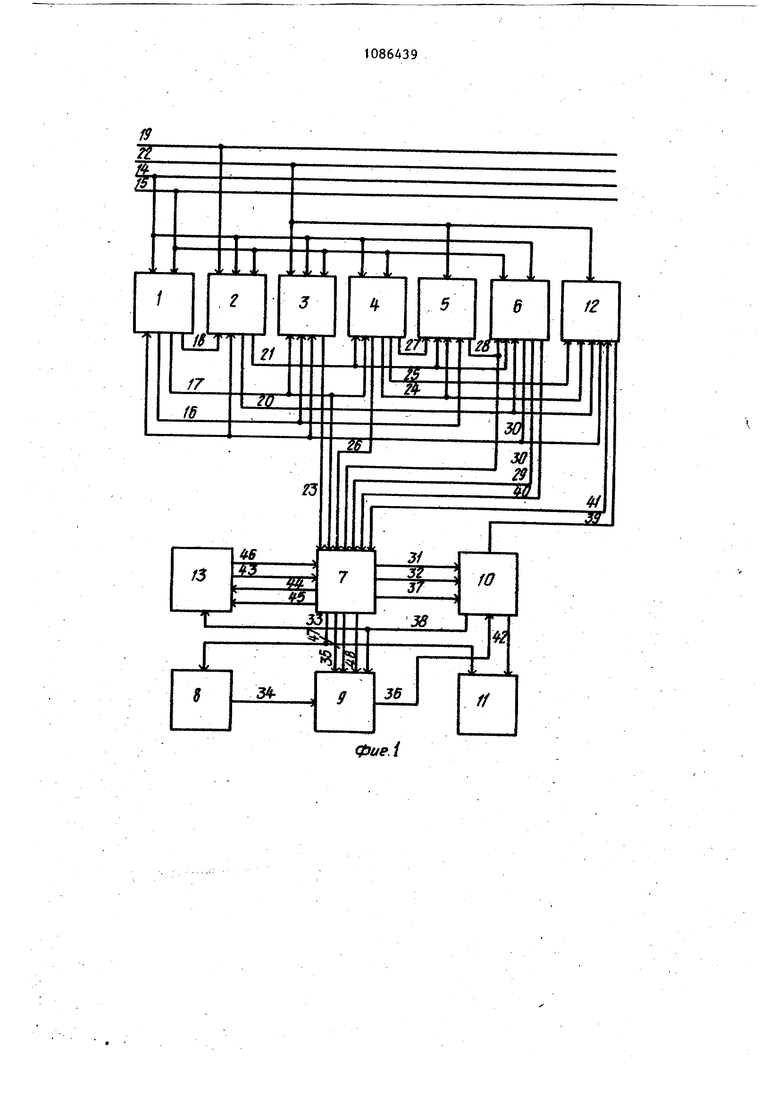

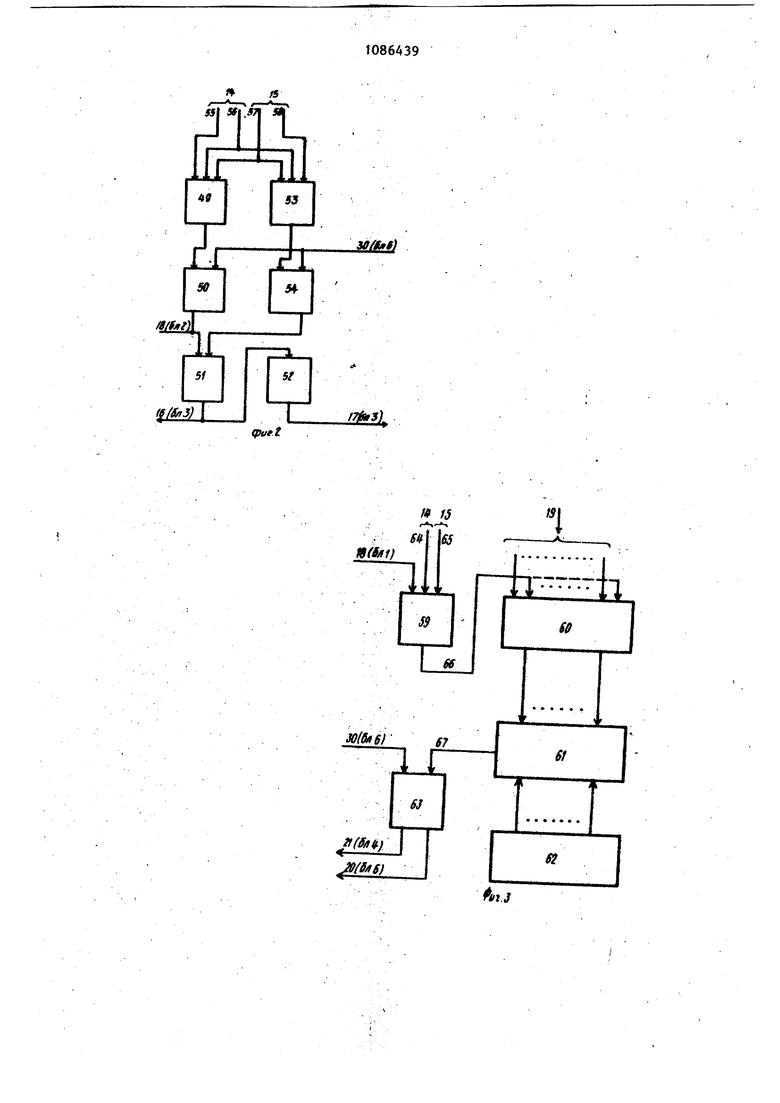

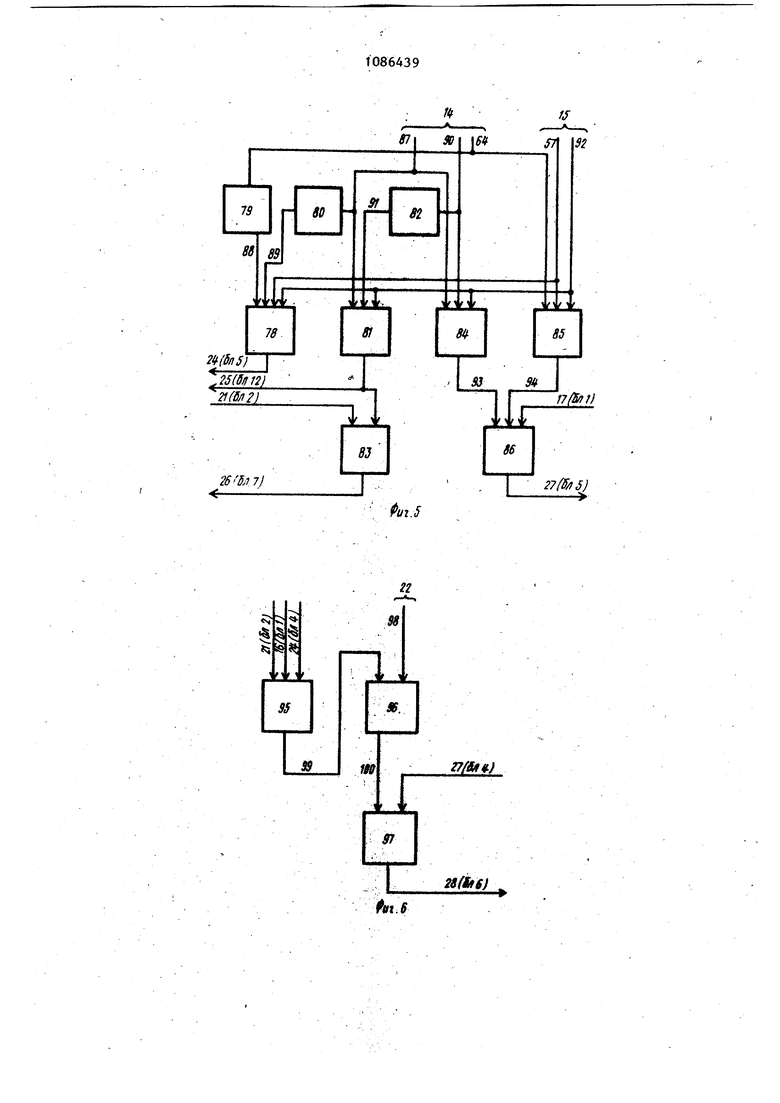

I торой группы, первый вход -блока подключен к первому входу третьего элемента И, второй вход которого и первьй выход блока соединены с Седьмым выходом второго сдвигакщего регистра, второй, третий, четвертьй, пятый и шестой вых.оды которого соединены соответственно с первыми входами четвертого и пятого эле.ментов ИЛИ, с седьмым, третьим и четвертьм выходами блока, второй выход первого сдвигающего регистра соединен с восьмым выходом блока и с вторым входом четвертого элемен та ИЛИ, выход которого является шестым выходом блока, третий и четвертый выходы первого сдвигающего регистра соединены соответственно с ц. выходом блока и с вторым 1ВХОДОМ Питого элемента ИЛИ, выход которого является вторым выходе блока, блок переполнения содержит триггер, усилитель, звуковой сигнализатор, группу элементов И, регист ры, индикатор и элемент коммутации, причем выход элемента коммутации по ключен к первому входу триггера и к первым входам регистров, вторые входы которых сбёдинены соответственно с выходами группы элементов И Первые входы которых соединены с управляющим входом блока, а вторые входы подключены к информационному входу блока, выходы регистров подключены соответственно к входам дешифратора, выходы которого подклю чены соответственно к входам индика тора,, второй вход триггера соединен с информадионным входом блока, выход триггера через усилитель подключен к входу звукового сигнализатора, блок приема уточненного байта состояния содержит группы элементов И, регистры, элемент ИЛИ элемент И, сдвигающий регистр и генератор одиночных импульсов, причем выход генератора одиночньт импульсов подключен к первому входу элемента ИЛИ и к первому входу сдви гающего регистра, второй вход;которого соединен с выходом элемента И вход генератора одиночньпс импульсов и первьй вход элемента И подключены к второму входу блока, второй вход элемента И соединен с пятым входом блока, второй вход элемента ИЛИ является управляющим входом блока, группа входов сдвигающего регистра соединена с первым входом блока, выходы сдвигающего регистра соедине ны соответственно с первыми входами элементов И первой группы, вторые входы которых подключены к четверто му входу блока, первые входы элемен тов И каждой rpynnbi, начиная с второй, соединены с третьим входом бл ка , вторые входы подключены к выходу Соответствукщего элемента И 910 первой группы, выходы элементов И каждой группы, начиная с второй, подключены к первой группе входов соответствующего регистра, вторая группа входов каждого регистра соединена с выходом элемента ИЛИ, выходы регистров являются выходом блока. На фиг, 1 приведена структурная схема устройства на фиг. 2 - функциональная схема блока приема сигналов установления связи на фиг. 3функциональная схема блока анализа команд канала на фиг. 4 - функциональная схема блока приема адреса на фиг. 5 - функциональная схема блока приема сигналов передачи абонентом байта состоянияi на фиг.бфункциональная схема блока анализа основного байта состоянияj на фиг. 7 - функциональная схема блока приема сигналов окончания операции ввода-выводаi на фиг. 8 - функциональная схема блока управления регистрацией j на фиг. 9 - функциональная схема блока счетчиков ошибок; на фиг. 10 - функциональная схема блока переполнения; на фиг. 11 функциональная схема блока приема уточненных байтов состояния; на фиг. 12 - функциональная схема блока вывода информации об ошибках. На фиг. 1-12 обозначены: блок 1 приема сигналов установления связи, блок 2 анализа команд канала, блок 3 приема адреса, блок 4 приема сигналов передачи абонентом байта состояния, блок 5 анализа основного байта состояния, блок 6 приема сигналов окончания операции вводавывода, блок 7 управления регистрацией, дешифратор 8, блок 9 памяти, блок 10 счетчиков ошибок, блок 11 переполнения, блок 12 приема уточненных байтов состояния, блок 13 вьюода информации об ошибках, связи 14-48, элемент 49 И, триггер 50, элемент 51 ИЛИ, генератор 52 одиночных импульсов, элемент 53 И, триггер 54, связи 55-58, элемент 59 И, группа элементов И 60, схема 61 .сравнения, узел 62 набора кодов, триггер 63, связи 64-67, элемент 68 И, элемент 69 НЕ,элемент И70, группа элементов И 71, регистр 72, элемент 73 ИЛИ, связи 74-77, элемент И 78, элементы 79, 80 НЕ, элемент 81 И, элемент 82 НЕ, элементы 83-85 И, элемент 86 ШШ, связи 87-94, элементы 95, 96 И, триггер 97, связи 98-100, элемент 101 И элемент 102 НЕ, элемент 103 И, элементы 104, 105 ШШ, элементы 106, 107 И, элемент НЕ 108, элементы 109, 110 И, элемент 111 за держки, связи 112-116, элемент 1Т7 И триггер 118, элемент 119 ИЛИ, групjna элементов И 120, регистр 121, триггер 122, элемент 123 И, гене ратор 124 тактовых импульсов, сдвиганиций регистр 125, элемент 126 ШШ группа элементо.в И 127, элементы 128-130 ИЛИ, элемент 131 И, элемент 132 НЕ, триггер 133, элемент 134 И, гурппа элементов И 135, сдвигающий регистр 136, связи 137161, суммирукщий счетчик 162, группа счетчик.ов 163, элемент 164 И, группа элементов И 165, элемент 166 ИЛИ, связи 167, 168, триггер 169, группа элементов И 170, регистры 171, дешифратор 172, индикатор 173, усилитель 174, звуковой сигнализатор 175, элемент 176 коммутации, связи 177-181, генератор 182 одиночных импульсов, сдвига ющий регистр 183, элемент 184 ИЛИ, группы элементов И 185,186, регистры 187,элемент 188 И, связи 189-194, узел 195 задания адреса, элемент 196 коммутации, группы элементов И 197, регистры igg, дешифраторы 199, индикаторы 200, связи 20Т-203. Устройство работает следующим образом. Все электрические сигналы, цир-. кулирующие между каналом ввода-вывода ЭВМ и периферийными устройства ми, воспринимаются блоками 1-6 и 12 которые фиксируют различные этапы выполнения очередной операции ввода вьшода и в процессе ее прохождения снимают с информационных шин абонеи та адрес и байты состояния периферийного устройства, а с информацион ных шин канала - команды, выполняемые этим устройством. При обнаружении байтов состояния с признаками об ошибках в работе периферийного устройства осуществляется регистрация ошибок и их хранение в блоке памяти. Все поле памяти блока 9 раз делено на отдельные области, количество которых соответствует максимально возможному числу периферийных устройств, подключаемых к данному каналу ввода-вьшода. 3912 Работа устройства начинается с фиксирования начала операции ввода-вывода и установления логической связи между каналом и каким-либо периферийным устройством с помощью триггера 50 или триггера 54 (фиг.2). Если операция ввода-вывода началась по инициативе канала последовательностью сигналов начальной выборки, то срабатывает триггер 50 от элемента 49 И; и при условии, что на входах последнего имеются следующие сигналы: по связи 52 - адрес периферийного устройства (на управляющие шинах канала), по связи 56 - разрешение выборки (на управляющих шинах канала ) и по связи 57 - работа (на управлякицих шинах абонента). С выхода триггера 50 вьзделяется по связи 18 сигнал о начальной выборке. Если же операция ввода-вывода нача- -, лась по инициативе периферийного устройства, то срабатывает триггер 54 от злемента 53 И при условии, что на входах последнего имеются следущие сигналы: по связям 56 - разрешения выборки (на управляющих шинах канала), по связи 57 - работы (на управляющих шинах абонента) и по связи 58 - требования на обслуживание (на управляющих шинах абонента). Вьпсодные сигналы триггеров 50 и 54 через элемент 51 ШШ поступают на связь 16 и на вход генератора 52 одиночных импульсов.Импульс, выра|батываёмый этим генератором, постзшает на входы блоков 3, 4 и блока 7 и обнуляет входной регистр 72 блока 3, регистр 121 блока 7 и через элемент 86 ИЖ блока 4 триггер 97 блока 5 (по связи 27). При одновременном поступлении на вход устройства сигналов управления по связи 64 (на управляющих шинах канала) и адреса по связи 65 (на управляющих шинах абонента) и при наличии сигнала на связи 18 срабатывает элемент 59-И (фиг. 3), выходной сигнал которого открывает элементы И 60 и команда канала, которая установлена каналом в данный момент времени на его информационных шинах, поступает на один из входов схемы 61 сравнения. Схема 61 осуществляет поразрядное сравнение поступившего кода команды с заранее установленным в узле 62 кодом команды Уточнить состояние, по которой абонент передает каналу уточненные байты состояния периферийного устройства, и при совпадени значений этих кодов срабатывает триггер 63 и по.связи 20 вьщается сигнал о наличии команды Уточнить состояние. Если же код команды канааа не совпадает с заранее установ ленным кодом, то по связи 21 вьщается соответствующий сигнал. При одновременном поступлении на вход устройства сигналов работа по связи 57 (на управляющих шинах абонента) и адреса по связи 65 (на управляющих шинах ) и отсутствии сигнала управления по св зи 64 (на управляющих шинах канала) срабатывает элемент 68 И (фиг.4) и при наличии сигнала установления логической связи (по связи 16) злемент 70 И, выходной сигнал которого открывает элементы И 71 и адрес периферийного устройства, с которым в данный момент времени установлена логическая связь и осуществляется операция ввода-вьшода, с информационных шин абонента считывается в регистр 72, О наличии байта состояния перифе рийного устройства на информационных шинах абонента сигнализирует выходной сигнал элемента .78 И (фиг по связи 24. Этот сигнал вырабатывается при одновременном поступлении на вход устройства сигналов раб ты по связи 57 (на управляющих шина абонента) и управления по связи 92 (на управляющих шинах абонента) и отсутствии сигналов управления по связи 64 (на управляющих шинах канала) и информации по связи 87 (на управляющих шинах канала) и поступает на вход элемента 95 И (фиг.6) который при наличии на входе сигна лов по связям 16 и 21 выдает сигна опроса по связи 98 бита Сбой в ус тройстве состояния. Если значение этого бита равно единице, то срабатьюает триггер 97, которьй вьдает по связи 28 сигнал о сбое в периферийном устройстве, участву щем в данньй момент времени в опер ции ввода-вьшода. О приема байта состояния периферийного устройства каналом ввода вывода сигнализирует выходной сигнал элемента 81 И (фиг. 5) по связи 25. Этот сигнап вырабатывается при одновременном поступлении на 3914 вход устройства сигналов информации по связи 87 (на управляющих шинах канала) и управления по связи 92 (на управляющих шинах абонента) и отсутствии сигнала блокировки по.связи 90 (на управляющих шинах канала) и поступает на вход элемента. 83 И, который при наличии на его другом входе сигнала lio связи 21 вьщает по связи 26 сигнап считывания приня-того адреса периферийного устройства. Этот сигнал через элемент 119 ИЛИ (фиг. 8). открывает группу элементов И 120 и адрес периферийного устройства по связи 23 заносится в регистр 121. Одновременно через элемент 117 И срабатывает при наличии по связи 28 сигнала о сбое в периферийном устройстве триггер 118. Если же канал ввода-вьшода не может принять байт состояния периферийного устройства или имеется цепочка команд, то срабатывает элемент 85 И или элемент 84 И соответственно. Элемент 85 И срабатывает при условии, что на входе устройства одновременно присутствуют сигналы управления по связи 64 (на управляющих шинах канала), работы по связи 57 (на управляющих шинах абонента) и управления по связи 92 (на управляющих шинах абонента), а элемент 84 И - информации по связи 87 (на управляющих шинах канала), блокировки по -связи 90 (на управляющих , шинах канала) и управления по связи 92 (на управляющих шинах абонента) . Выходные Сигналы этих элементов через элемент 86 ИЛИ по связи 27 сбрасывает триггер 97 (фиг. 6). Окончание очередной операции ввода-вывода сигнализируется выходным сигналом одного из элементов 101, 106, 107 И (фиг. 7). Если байт состояния принят каналом ввода-вывода, то сигнал окончания операции вводавывода вырабатывается элементом 101 И при условии, что на входе устройства имеется сигнал информации по связи 87 (на управляющих шинах канала) и отсутствуют сигналы разрешения выборки по связи 56 (на управляющих шинах канала) и работы по связи 57 (на управляющих шинах абонента). При наличии сигналов по связям 21 и 28 выходной сигнал элемента 101 И через элементы 110И 103 И и 104 ИЛИ поступает на связь 29 сигнала регистрации и одновременно через элементы 110 И и 105 ИЛИ на связь 30 сброса триггера 63 (фиг. 3 регистры 72 (фиг. 4) и сдвигающего регистра 183 (фиг. 11). При наличии сигнала на связи 20 выходной сигнал элемента 101 И ч,ерез элемент 109 И поступает на.связь 40 записи адреса периферийного устройства и одновременно через элемент 111 задержки и элемент 105 ИЛИ на связь 30 сброса. Если байт состояния отвергнут каналом ввода-вьюода, то сигнал окончания операции ввода-вывода вырабатывается элементом 106 И при условии, что на входе устройства имеется сигнал управления по связи 64 (на управляющих шинах канала) и отстутствуют сигналы разрешения выборки по связи 56 (на управляющих шинах канала) и работы по связи 57 (на управляющих шинах абонента). В случаях экстренного прекращения каналом по каким-либо причинам операции ввода-вывода сигнал окончания вырабатьшается элементом 107 И, при этом на входе устройства имеетс сигнал адреса по связи 55 (на управ ляющих шинах канала) и отсутствуют сигналы разрешения выборки по связи 56 (на управляющих шинах канала) и работы по связи 57 (на управляющи шинах абонента). Выходные сигналы элементов 106, 107 И через элемент 105 ИЛИ поступают на связь 30 сброса. На этом процесс приема с информационньБС шин абонента байта состояния с указателем Сбой в устройстве завершается и после установки триггеров 50 и 54 в исходное положе ние сигналом сброс по связи 30 устройство готово к повторному приему и анализу сигналов на управляющих и информационных шинах канала и або нента. Регистрация принятой информации осуществляется независимо от указан ного процесса и начинается с момент поступления сигнала по связи 29 на вход триггера 122 (фиг. 8). Вькодно сигнал триггера открывает элемент 123 И, и тактовые импульсы с генератора 124 поступают на вход сдвигающего регистра 125. После про хождения первого тактового импульса сигнал, поступающий по связи 144 через элемент 126 ИЛИ открывает гру пу элементов И адрес перифери 916 ного устройства из регистра Т21 через дешифратор В поступает в блок 9 памяти. Одновременно через элемент 128 ИЛИ происходит обнуление счетчика 162 и группы счетчиков 163 по связи 32 (фиг. 9). После прохождение второго тактового импульса через элемент 129 ИЛИ в блок памяти по связи 35 вьщается команда Читать и информация, хранящаяся в блоке памяти по данному адресу периферийного устройства, по связи .36 заносится в счетчик 162 и группу счетчиков 163. После третьего тактового импульса по связи 37 вьщается сигнал суммирования, который при наличии сигналов на связях 31 и 39 через элемент 164 И и группу элементов И 165 поступает на счетные входы счетчика 162 и группы счетчиков ошибок 163. Процесс приема уточненных байтов состояния и вьдачи сигналов по связи 39 описан ниже. Необходимо отметить, что каждый разряд всех уточненных байтов состояния имеет свой счетчик ошибок. После прохождения четвертого и пятого тактовых импульсов производится соответЬтвенно обнуление отведенной данному периферийному устройству области памяти и запись, в эту область содержимого счетчика 162 и группы счетчиков 163 по связи 38. В шестом такте закрывается группа элементов И 127, снимается адрес с дешифратора 8 и блока 9 и через элемент 130 ИЛИ обнуляются регистр 121 и триггер 118. В седьмом такте триггер 122 возращается в исходное положение и процесс регистрации заканчивается. Если в процессе регистрации происходит переполнение какого-либо счетчика, то вырабатываемый этим счетчиком сигнал . через . элемент 166 ИЛИ (фиг. 9) по связи 42 взводит триггер 169 и открывает элементы 170 (фиг. 10), через которые производится запись в регистр 171 зарегистрированного адреса периферийного устройства с дальнейшей eto ешифрацией и отображением на индикаторах 173. К выходу триггера 169 подключен через усилитель 174 звуовой сигнал и затор (ревун) 175. лемент 176 предназначен для сброса световой и звуковой сигнализации переполнении счетчика (счетчиков) шибок. Прием уточненных байтов состояния производится при наличии команды канала Уточнить состояние и осуществляется блоком 12 (фиг. 11) следующим образом. Сигнал по связи 20 поступает на вход генератора 182 одиночных импул ьсов, выходной импульс которого устанавливает в единицу первый разряд сдвигающего регистра 183 и через элемент 184 ИЛИ обнуляет регистры 187. Одновременно подготавливается элемент 188 И к приему по связи 25 сиг нала о получении каналом байта состояния периферийного устройства и первый из группы элементов 185 И, подключенный к первому разряду сдви гающего регистра 183, к приему по связи 24 сигнала о наличии байта состояния периферийного устройства на информационных шинах абонента. 1ри поступлении по связи 24 указанного сигнала через первый элемент группа элементов И 185 открывается первая группа элем.ентов И 186 и байт состояния с информационных шин абонента считывается в регистр 187. Следукмций за этим сигнал по срязи 25 через элемент 188 И сда гает в регистре 183 записанную ране единицу из первого во второй разряд, подготавливая таким образом второй элемент группы элементов И 18 к приему сигнала по связи 24. При повторном поступлении сигнала по связи 24 уже через второй элемент группы элементов И 185 открывается вторая группа элементов И 186 и бай состояния с информационных шин абонента считьшается во второй ре,гистр 187. Следующий за этим сигнал по связи 25 через элемент 188 И сдвигает в регистре 183 единицу из второго в третий разряд, подгота ливая таким образом третий элемент группы элементов И 185 к приему сиг нала по связи 24. Описанный цикл повторяется до тех пор, пока не буд приняты все уточненные байты сост|)Я ния данного периферийного устройства. Об окончании приема каналом ввода-вывода всех указанных байтов состояния и завершения текущей операции ввода-вывода сигнализирует выходной сигнал элемента 101 И (фиг. 7). Условия формирования этого сигнала описаны. Выходной сигнал элемента 101 И через элемент 109 И поступает по связи 40 через эле3918мент 119 ИЛИ (фиг. 8) на группу элементов И 120 записи зарегистрированного адреса периферийного устройства и одновременно через элемент 111 задержки и элемент 105 И на связь 3D сброса. По последнему сигналу очищается сдвигающий регистр 183 (фиг. 11). Процесс регистрации принятых уточненных байтов состояния осуществляется блоком 7 (фиг. 8) по сигналу на связи 29 и протекает указанным способом. После завершения регистрации сигналом по связи 41 через элемент 184 ИЛИ производится обнуление регистров 187 (фиг. 11). Количество элементов в группе элементов 185 И, групп элементов И 186, регистров 187 и разрядов сдвигающего регистра 183 устанавливается по максимальному числу уточненных байтов состояния какого-либо периферийного устройства, подключенного к каналу ввода-вывода. Возможна установка меньшего количества указанных элементов, но при этом необходимо учитывать, что последние байты состояния не будут, приняты. Вывод зарегистрированной информации об ошибках в работе какого-либо периферийного устройства производится набором адреса данного устройства в узле 195 (фиг. 12) и нажатием элемента (кнопки) 196.вызова, при этом через элемент 131 И срабатьшает триггер 133, выходной сигнал которого открывает элемент 134 И и группу элементов И 135 (фиг. 8). Установленный в узле 195 адрес периферийного устройства по связи 33 поступает на дешифратор 8 и далее по связи 34 в блок памяти. Тактовые импульсы генератора 124 через элемент 134 И поступают на вход сдвигающего регистра 136. В первом такте производится обнуление регистpoB 198 (фиг. 12) по связи 44 и через элемент 128 ИЛИ обнуление счетчика 162 и счетчиков 163 по связи 32. Во втором такте через элемент 129 ИЛИ осуществляется считывание из отведенной данному устройству области памяти информации об ошибках и записи ее в счетчик 162 и группу счетчиков 163. В третьем такте по связи 45 открывается группа элементов И 197 (фиг. 12) и информация с счетчика 162 и группы счетчиков 163 по связи 38 считьшается в регистры 198. Информация после дешифрации отображается на индикаторах 200. В четвертом такте триггер 133 устанавливается в исходное положение.В современных информационно-вычислительных системах, автоматизированных системах управления и вьиислигельных центрах все большее внимание уделяется вопросу сбора статистических данньк о работе оборудования ЭВМ в том числе и периферийных устройств в процессе их эксплуатации в реальных условиях и различного вида испытаний. Для этого используются программные методы регистрации, накопления, обобщения и вывода статистических данных. Использование же для этих целей аппаратурных средств исключает неизбежные при программно методе затраты машинного времени и оборудования ЭВМ, что повьшает производительность вычислительного комплекса, и обеспечивает воэможность про;в едения регистрации и получения статистических данных, не оказывая влияния на производительную работу каналов ввода-вывода в ЭВМ в целом. Кроме того, аппараIтурные средства обеспечивают независимое выполнение операций по приему, регистрации и выводу информации об ошибках в работе периферийных устройств. Необходимо отметить.

доступность и наглядность вывода статистических данньк, а также легкость получения рассмотренного устройства к каналу ввода-вывода.

Применение устройства позволяет исключить затраты машинного, времени ЭВМ на регистрацию и накопление информации об ошибках в работе периферийных устройств; затраты на хранение статистических данных во внешней памяти ЭВМ (как правило, на средствах прямого доступа) затраты машинного времени ЭВМ на обобщение и вывод статистических данных; затраты на техническое обслуживание части оборудования ЭВМ, используемого для сбора и обработки статистических данных.

Кроме того, применение данного устройства позволяет снизить машинное время решения основных (пользовательских) задач за счет исключения из него времени на сбор, обрабоку и вьшод статистических данных, а также увеличить время использования оборудования ЭВМ по прямому назначению (для решения основных задач).

фие.{

sti.sr

fS

Ш

2ЬЗ

зе/М)

n

ЗО(бЯб)-67

и

6t

f(

62

15

S7

М

69

16 (5/} V

70

J0(5n 6}

nWi)

22

J у

JUL

71

f fj f f

72

- Jfff/77

Фаг Л

ч«N

Й

M p V

99

//

.S

,

7/ tf4t;

28fii f)

Фиг1 28(Sfi25) 2SM 23{Sn 6) ж ML t17 23ft/iS) т-Ц( Ф П

2()

192

}

Ш

Т т L т fTfar-tr--- --

33 (дл 7

Л

Фиг.Ю

п

......

.di L

т

I

т

WI-IW

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США 4166290, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-15—Публикация

1982-11-09—Подача