1

Изобретение относится к вычислительной технике и может быть использовано, в качестве системы ввода-вы рзода вычислительной системь с распределенной обработкой и распределе ным вводом-выводом данных.

Целью изобретения является повышение быстродействия устройства.

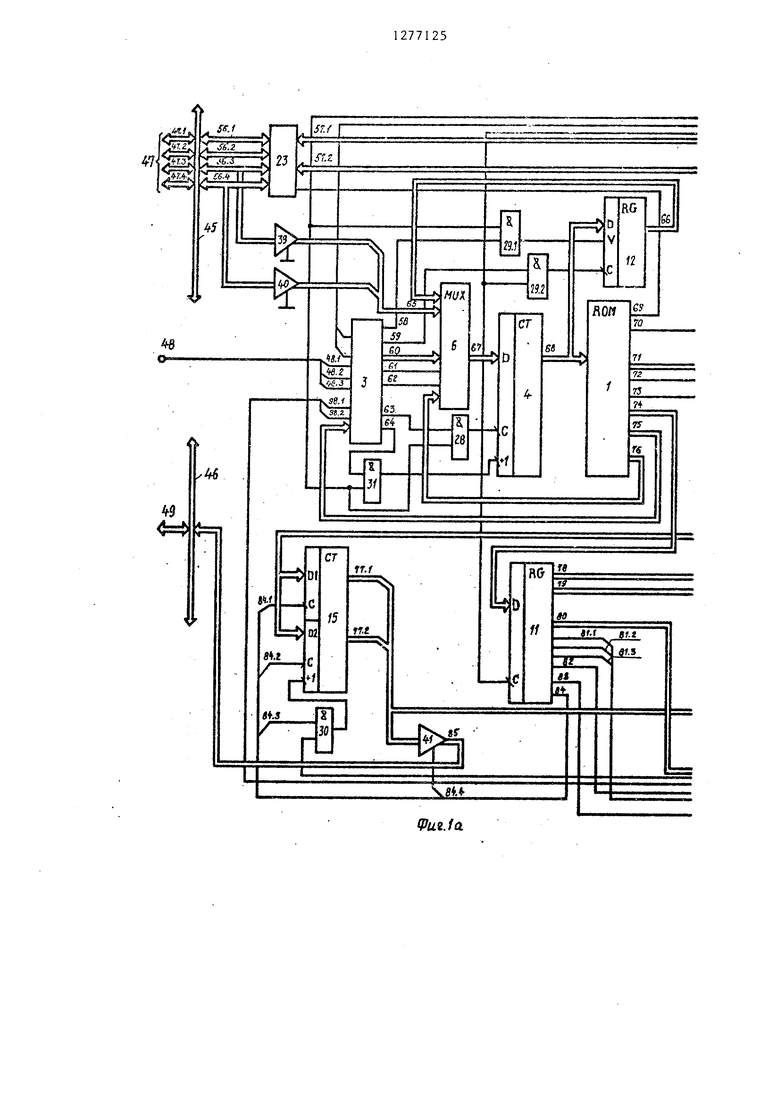

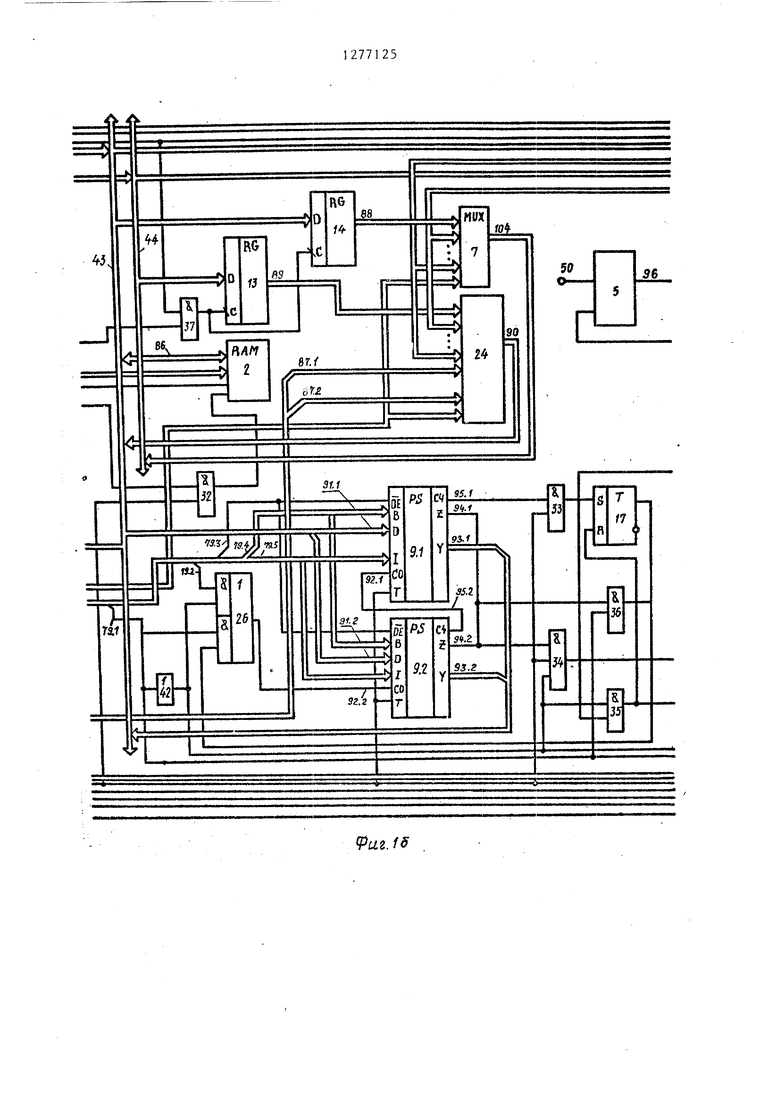

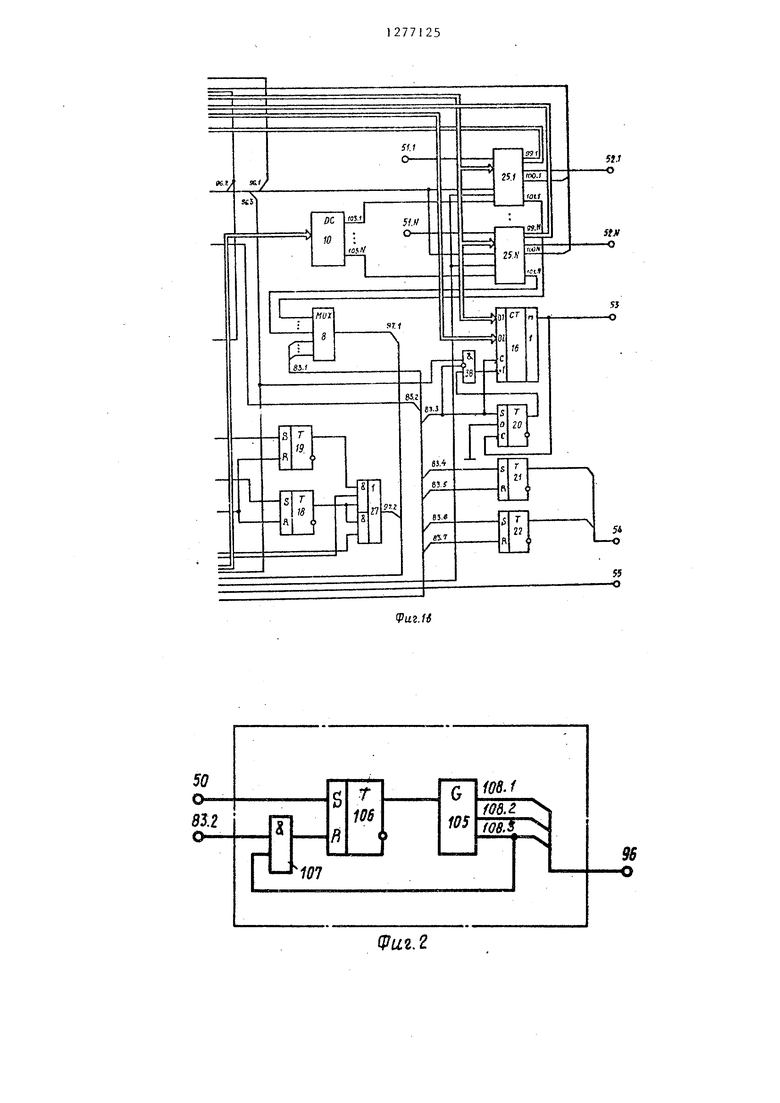

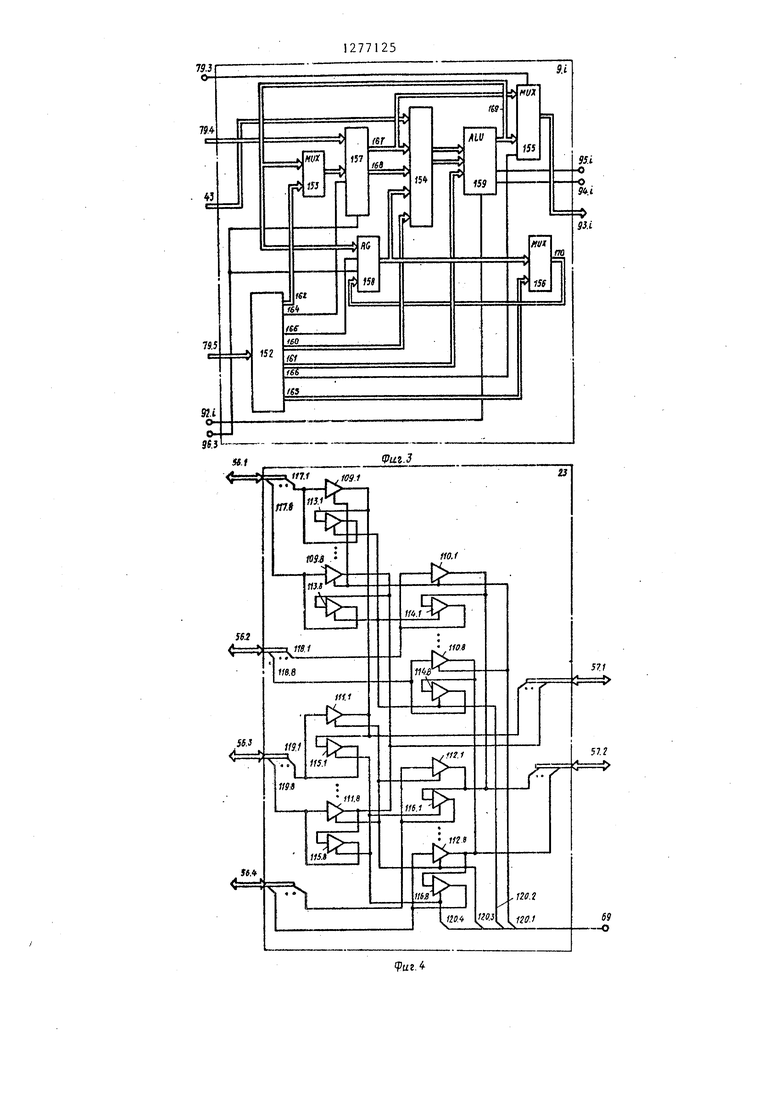

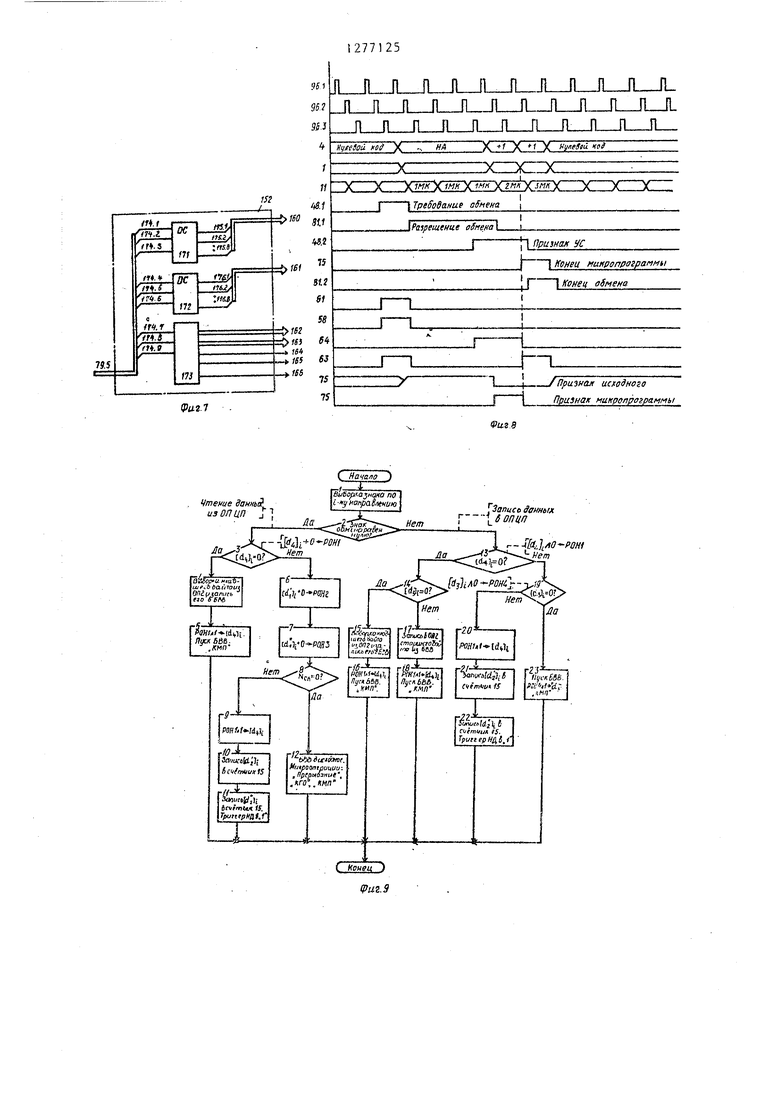

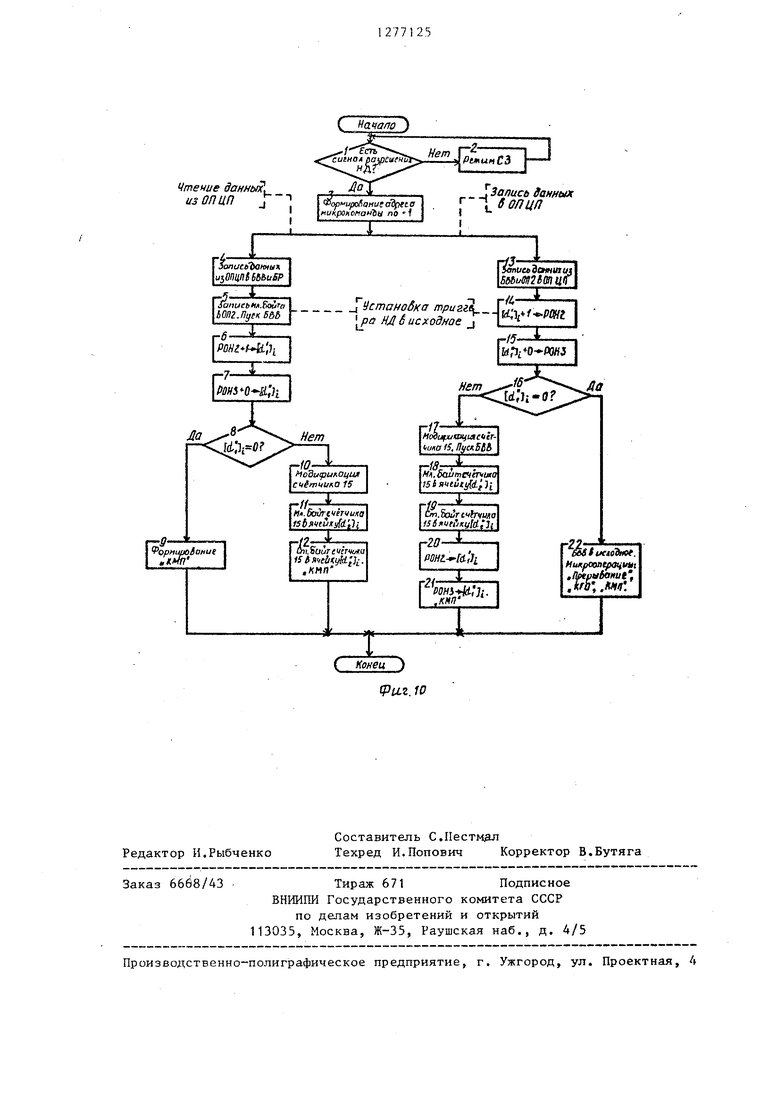

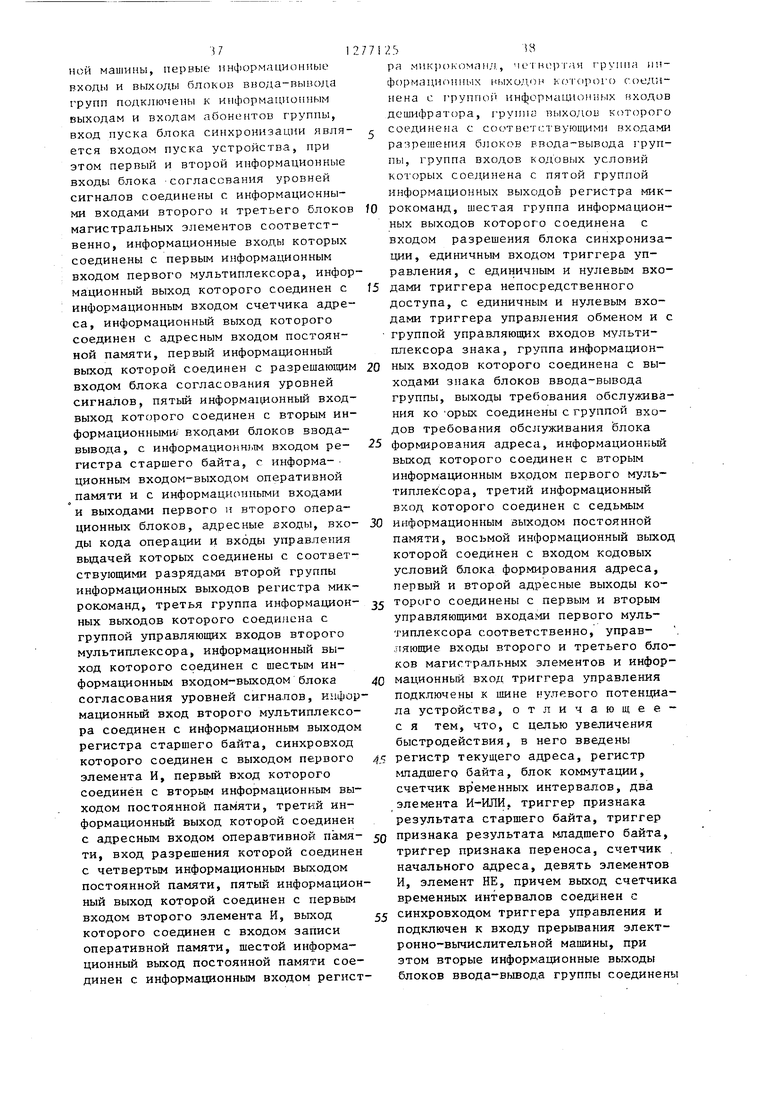

На фиг. 1а, б, в приведена функциональная схема устройства; на фиг, 2 - функциональная схема блока синхронизацииi на фиг. 3 - функциональная схема операционного блока (ОБ), на фиг. 4 - функциональная схема блока согласования уровней си налов; на фиг. 5 - функциональная схема блока коммутации; на фиг. 6 - функциональная схема блока ввода- вывода; на фиг. 7 - функциональная схема блока дешифраторов управления операционного блока; на фиг, 8 - временная диаграмма работы устройства при выполнении команд обмена (ОБМ1-ОБМ4); на фиг. 9 - структурная схема алгоритма микропрограммы обслуживания абонента; на фиг. 10 - структурная схема алгоритма микро- опрограммы непосредственного доступа

Устройство для обмена данными между электронно-вычислительной машиной и абонентами (фиг. 1а, б, в) содержит постоянную память (ПП) 1, оперативную память (СП) 2, блок 3 формирования адреса, счетчик 4 адреса, -блок 5 синхронизации, первый мультиплексор 6, второй мультиплек сор 7, мультиплексор 8 знака (направления обмена), операционные блоки (ОБ) 9.1 и 9.2, дешифратор 10, регистр 11 микрокоманд, регистр 12 текущего адреса, регистр 13 младшего байта, регистр 14 старшего байта, счетчик 15 начального адреса, счетчик 16 временных интервалов, триггер 17 признака переноса, триггеры 18 и 19 признаков результата мпадшего и старшего байтов, триггер 20 управления, триггер 21 .непосредственного доступа (НД), триггер 22 управления обменом, блок 23 согласования уровней сигналов, блок 24 коммутации, блоки 25.1-25.N ввода- вывода, второй элемент И-ИЛИ 26, первьй элемент И-ИЛИ 27, пятый: элемент И 28, четвертый элемент И 29.1 седьмой элемент И 29.2, третий эле- .мент И 30, шестой элемент И 31, второй элемент И 32, десятый элемент

O

0

25

71

55

30

35

40

45

50

252

И 33, девятый элемент И 34, восьмой элемент И 35, двенадцатый элемент И 36, первый элемент И 37, одиннадцатый элемент И 38, иторой, третий, первый блоки 39-41 магистральных элементов, элемент НЕ 42, шину 43 старшего байта данных, шину 44 младшего байта данных, шину 45 данных, шину 46 адреса, информационный вход- выход 47 устройства, вход-выход 47.1 старшего байта второго полуслова, вход-выход 47.2 младшего байта второго полуслова, вход-выход 47.3 старшего байта первого полуслова, вход-выход 47,4 младшего байта первого полуслова, группу 48 управляющих входов устройства, вход 48.1 требования обмена, вход 48.2 признака управляющего слова (УС), вход 48.3 разрешения непосредственного доступа (НД), вход-выход 49 адреса устройства, вход 50 пуска устройства, входы 51.1-51.N абонентов устройства, выходы 52. абонентов устройства, выход 53 прерывания устройства, первую группу управляющих выходов 54 устройства, вторую группу управляющих выходов 55 устройства, третий 56,1, четвертый 56.2, первый , второй 56.4, пятый 57,1 и шестой 57.2 информационные входы-выходы блока 23 согласования уровней сигналов, управляющие выходы 58 и 59 блока 3 формирования адреса соответственно записи и признака модификации, информационный выход 60 блока 3, управляющие выходы 61 и 62 блока 3 формирования адреса, управляющие выходы 63 и 64 блока 3 соответственно записи-счета и блокировки счета, вход 65 мультиплексора 6, выход 66 регистра 12, выход 67 мультиплексора 6, выход 68 счетчика 4 адреса, выходы 69-76 соответственно управления блоком 23 согласования, управления регистрами, 13 и 14,, адреса, обращения, записи, микроопераций, признаков перехода, адресов перехода ПП 1, выходы 77.1 и 77.2 счетчика 15 соответственно старшего и младшего байтов, выходы 78-80, 81.1-81.3, 82-84 соответственно управления блоком 24 коммутации, операционными блоками, дешифратором 10, разрешения обмена, требования НД, прерывания, управления блоками ввода-вывода, внутренних микроопераций, управления счетчиком регистра 11 микрокоманд,выход 85

31

блока 41 магистральных элементов, вход-выход 86 ОП 2, информационные входы 87.1 и 87.2 блока 24 коммутаци выход 88 регистра 14, выход 89 регистра 13, выход 90 блока 24 комму- тации, четырехразрядные входы 91.1 и 91.2 данных соответственно ОБ 9.1 и 9.2, входы 92.1 и 92.2 входных переносов соответственно ОБ 9.1 и 9.2, четырехразрядные выходы 93.1 и 93.2 данных ОБ 9.1 и 9.2 соответственно, выходы 94.1 и 94.2 признаков результата соответственно ОБ 9.1 и 9.2, выходы 95.1 и 95.2 распространения переноса соответственно ОБ 9.1 и 9.2, группа выходов 96 блока 5 синхронизации, выход 97.1 мультиплексора 8 знака, выход 97.2 первого элемента И-ИЛИ 27, вход 98.1 знака блока 3, вход 98.2 признака результата блока 3, информационный 99.1 и управляющий 100.1 выходы 25.1 ввода-вывода, где 1 1, N, выход

101.1знака блока 25.1, вход 102.1 требования обслуживания блока 3, вы- ход 103.1 дешифратора 10, выход 104 второго мультиплексора 7.

Блок 5 синхронизации (фиг. 2) содержит генератор 105 тактовых импульсов, триггер 106 и элемент И 107 группу выходов 108.

Блок 23 согласования (фиг. 4) содержит первую 109.1-109.8, вторую 110.1-110.8, третью 111.1-111.8, четвертую 112.1-112.8, пятую 113.1- 113.8, шестую 114.1-114.8;седьмую 115.1-115.8, восьмую 116.1-116.8 группы магистральных элементов, входы и выход 117-120 магистральных элементов.

Блок 25.1 ввода-вывода (фиг. 6) содержит счетчик 121, регистр 122 ввода-вывода, регистр 123 управления, второй триггер 124 режима, пер- вьй триггер 125 режима, триггер 126 признака начала обмена (ПНО), триггер 127 знака, триггеры 128 и 129 управления, восьмой элемент И 130, первый элемент И 131, второй элемент И 132, третий элемент И 133, шестой элемент И 134, седьмой элемент И 135, девятый элемент И 136, четвертый элемент И 137, пятый элемент И 138, одиннадцатый элемент И 139, десятый элемент И 140, первый эле- мент ИЛИ 141, второй элемент ИЛИ 142 элемент НЕ 143, первый 144.1, второй

144.2и третий 144.3 входы группы

254

входов 96 блока 25.1 ввода-вывода, первый 145.1, второй 145.2, третий 145.3, четвертый 145.4, пятый 145.5 входы группы входов 82 микроопераций блока 25.1 ввода-вывода, выход 146 N-ro разряда регистра 123 управления, выход 147 инверсного (п+О-го разряда счетчика 121, выход 148 элемента И 133, первый 149.1, второй

149.2,третий 149.3 выходы группы вькодов 52.1 блока 25.1 ввода-вывода информационные входы 150.1 - 150.N регистра 122 ввода-вывода, выходы 151.1 - 151.N регистра 122 ввода-вывода,о

Операционный блок 9.1 (фиг. 3) содержит блок 152 дешифраторов управления, первый мультиплексор 153, коммутатор 154, второй и третий мультиплексоры 155 и 156, блок 157 регистров общего назначения, буферный регистр 158, арифметико-логический блок 159, первый - седьмой выходы 160-166 блока 152 дешифраторов управления, первый 167 и второй 168 выходы блока 157 регистров общего назначения, выход 169 арифметико-логического блока 159, выход 170 треть .его мультиплексора 156.

Блок 152 дешифраторов управления (фиг. 7) операционного блока 9.1 содержит дешифратор 171 источников операндов блока 159, дешифратор 172 функции блока 159, преобразователь 173 кодов. Входы разрядов 174.1174.3,174.4-174.6, 174.7-174.9 входа 79,5 блока 152 образуют соответственно группы информационных входов дешифраторов 171, 172 и преобразователя 173.

Блок 24 коммутации (фиг. 5) содержит дешифратор 175, первый 176.1 восьмой 176.8 коммутаторы.

На временной диаграмме работы устройства при выполнении команд обмена (фиг. 8) показаны номера тех элементов, входов и выходов устройства, которые необходимы для пояснения функционирования устройства. Кроме того, состояние счетчика 4 адреса на временной диаграмме поясняется следующими обозначениями: НА - в счетчике 4 записан начальный адрес микропрограммы, соответствующий выборке из ГШ 1 первой микрокоманды (1 МК){ +1 - исполнительный адрес второй (2МК) и третьей (3 МК) микро5 1 команды форьшруется путем увеличения содержимого счетчика 4 на единицу.

На фиг, 9 и 10 приведены структурные схемы микропрограмм, которые содержат символы, определяющие порядок выполнения микропрограмм. Кроме того, на фигурах использованы следующие обозначения: i.,; , ci , фиксированные ячейки ОН 2, в которых хранится информация соответственно ;о младшем и старшем байтах счетчика :длины массива слов данных по 1-му :направлению обмена, где i 4,N, N - количество абонентов .oi.j . , о(.1- фиксированные ячейки ОП 2, в которых хранится информагщя соответственно о младшем и старшем байтах счетчика начального адреса ОП

центрального процессора ( ) i фиксированная ячейка ОП 2, в которой хранится информация о факте выдачи абоненту управляющего слова; Гы,- фиксированная ячейка ОП 2, в которой хранится информация о признаке байта (старшего или младшего) передаваемого слова данных абоненту.

Рассмотрим назначение элементов, дзлов и связей данного устройства.

Постоянная память 1 предназначена

для хранения микропрограмм, реализуе- 30 ставляет собой комбинационное дискмых устройством. На вход ПИ 1 подается адрес микрокоманды с выхода 68 счетчика 4 адреса„ ПП 1 представляет собой блок памяти статического типа и может быть построена на типовых интегральных элементах.

На выходе 69 ПП 1 формируются микрооперации, управляющие блоком 23. На выходе 70 ПП 1 формируется сигнал управления (записи), который, поступая на вход элемента И 37, разрешает поступление тактовых импульсо с выхода 96.2 группы выходов 96 блок 5 синхронизации на входы синхронизации регистров 13 и 14. На выходе 71 ПП 1 формируются адреса ячеек ОП 2, к которым происходит обращение На выходе 72 ПП 1 выдается сигнал обращения к ячейкам ОП 2. На выходе 73 ПП 1 формируется сигнал микрооперации, который поступает на вход элемента И 32, управляя записью дант ных в ОП 2j на выходе 74 ПП 1 сигналы внешних и внутренних микроопераций; на выходе 75 ПП 1 - микроопе- 55 0) на выходах блока 3 формируютрации признаков перехода имеющие

следующие коды:

Признак результат (Z)100

Анализ знака011

Признак исходного 000 Признак микропрограммы 001 Конец микропрограммы 010

На выходе 76 ПИ 1 формируется ад

рес перехода А

пер

при выполнении мик

ропрограмм.

ОП 2 предназначена для временного хранения информации в процессе функционирования устройства. Она преде- тавляет собой запоминающее устройство статического типа, которое может быть построено на типовых интегральных микросхемах. Информационный

вход-выход ОП 2 подключен к шине 43 старшего байта данных, откуда поступает в ОП 2 и куда выдается из ОП 2 информация по командам, поступающим на адресные и управляющие входы

ОП 2 из ПП Ь

Блок 3 формирования адреса предназначен для формирования начальных адресов микропрограмм, модификации адреса очередной микрокоманды, а также для формирования управляющих сигналов на мультиплексор 6 (выходы 61 и 62). на счетчик 4 адреса (выходы 61, 63 и 64).

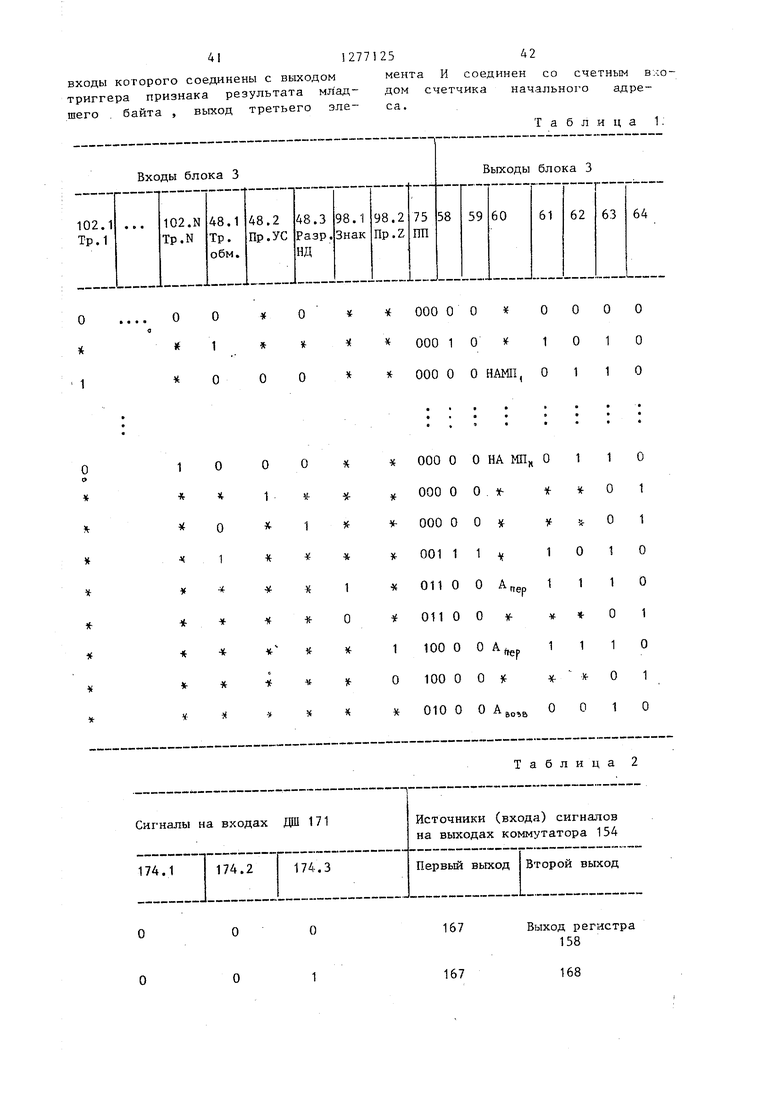

Блок 3 формирования адреса предретное устройство, закон функционирования которого определяется таблицей соответствия.

В табл. 1 показаны состояния хо35 дов и выходов блока 3 формирования адреса, где обозначает безразличное состояние соответствующего входа устройства; Тр. обм. - сигнал., Требование обмена, формируе1-{ый на вхо40 де 48.1 блока 3,- Тр. 1 - сигнал Требование обслуживания, от 1-го абонента; Пр. УС - сигнал признак управляющего слова ; Разр. НД - сигнал разрешения непосредственного досту-.

45.,па, Пр. Z - сигнал Признак резуль- тата (Z), ПП - трехразрядные микрооперации признаков перехода, коды и наименования которых приведены вьше.

50 Как следует из табл. 1, блок 3 формирования адреса микрокома Зд функционирует следующим образом. При воздействии на вход 75 блока 3 микрооперации Пр изнак исходного (код

ся нулевые сигналы. -Если на входы блока 3 формирования адреса поступает сигнал Требование обмена, то на своих управляющих выходах 58, 59,

71277

61-64 блок 3 формирует управляющие сигналы (соответственно 1,0,1,0,1,0) по которым код начального адреса (первой микрокоманды)-микропрограммы

обмена (НА МП

06М.

) с выходов блоков

39 и 40 магистральных элементов через мультиплексор 6 записывается в счетчик 4 адреса.

Если на входы блока 3 поступает сигнал Требование обслуживания то на своем выходе 60 блок 3 формирует код начального адреса микропрограммы обслуживания i-ro абонента (НА МП-), который по управляюпщм синалам записывается в счетчик 4 ад- реса. Более высокий приоритет имеет сигнал Требование обмена. Если в момент выполнения микропрограммы поступает сигнал Требование обслуживания, то данный сигнал не воспри нимается до окончания микропрограммы

При поступлении на вход блока 3 сигнала Признак УС блок 3 на выходе 64 формирует единичный сигнал, который разрешает формирование адре- са очередной (второй) микрокоманды путем увеличения содержимого счетчика 5 адреса на единицу по тактовому импульсу , .

С приходом на вход блока 3 сигнал Разрешение НД блок 3 формирует на выходе 64 единичный сигнал, который по тактовому импульсу с, в счетчике , формирует лод начального адреса микропрограммы непосредственного доступа.

Если на входы блока 3 поступает микрооперация Признак микропрограммы и сигнал Требование обмена, то на выходах 58 и 59 формируются еди- ничные сигналы, которые производят запись и модификацию текущего адреса микропрограммы в регистре 12„

При поступлении на входы блока 3 микрооперации Анализ знака и еди- ничного сигнала Знак блок 3 формирует на своих выходах управляющие, сигналы, по которым адрес перехода Angp с выхода 76 ПП 1 через мультиплексор 6 записывается в счетчик 4 адреса. Если поступает нулевой сигнал Знак, то блок 3 формирует на выходах управляющие сигналы, осуществляющие формирование адреса микрокоманды путем увеличения содержи- мого счетчика 4 на единицу.

При поступлении на входы блока 3 микрооперации Признак результата

8

н единичного сигнала Признак Z блок 3 формирует на :. входах yIIpaвJlяюlIЦ e сигналы, по которым адрес перехода с выхода 76 ПП 1 через мультиплексор 6 записывается в счетчик 4 адреса. Если же поступает нулевой сигнал Признак Z, to блок 3 формирует на выходах управляющие сигналы, осуществляющие формирование адреса очередной микрокоманды путем увеличения содержимого счетчика 4 на единицу.

Если на вход блока 3 поступает микрооперация Конец микропрограммы на выходе последнего формируются управляющие сигналы, осуществляющие прохождение и запись кода адреса возврата Аво,врС выхода регистра 12 текущего адреса через мультиплексор f 6 в счетчик 4 адреса.

Как гсомбинационное устройство, усповит функционирования которого показаны в табл. 1, блок 3 формирования адреса может быть реализован на программируемой логической матрице.

Счетчик 4 адреса предназначен для запоминания, увеличения на единицу и ВЫДАЧИ адреса очередной микрокоманды. Он имеет вход D параллельной записи кода Адреса, счетный вход (+1) и вход синхронизации С. Код адреса, поступающий на вход D, записывается в счетчик, если на его вход синхронизации поступает тактовый импульс. Содержимое счетчика увеличивается, если импульс поступает на его счетный вход (+1). Счетчик 4 адреса работает в двух режимах. Если следующий адрес формируется путем увеличения на единицу текущего адрес, то на вход синхронизации поступает нуевой сигнал с выхода элемента И 28, а на счетный вход счетчика 4 адреса - очередной тактовый импульс с выхода элемента И 31. Если следующий адрес формируется путем параллельной записи кода адреса с входа D, то на счетный вход счетчика 4 поступает нулевой сигнал с вь)хода элемента И 31, а на вход синхронизации - тактовый импульс с выхода элемента И 28.

Блок 5 синхронизации (фиг.2) предазначен для формирования на своих ыходах 96.1-96.3 трех последовательостей тактовых импульсов, сдвинутых руг относительно друга, которые

912771

обеспечивают синхронизацию работы устройства.

Триггер 106 служит для управления работой блока 5 синхронизации. Исходное состояние триггера 106 - 5 нулевое. При этом нулевой сигнал с его выхода поступает на вход управления генератора 105. Генератор 105 формирует на своих выходах последовательности импульсов только при на- Ю личии единичного сигнала на его управляющем входе. Элемент И 107 служит для формирования сигнала на нулевом входе триггера 106 после поступления управляющего сигнала . 5 Конец работы с входа 83.2 блока 5с Запуск блока 5 синхронизации осуществляется по сигналу Пуск, который поступает на вход 50. Он подает- ся на единичный вход триггера 106 к 20 устанавливает его в единичное состояние. Единичным сигналом на своем выходе триггер 106 запускает генератор 105, который начинает фop iиpoвaниe последовательностей синхросигнгшов, Формирование синхросигналов продолжается до тех пор 5 пока на первый вход элемента И 107 не поступит управляющий сигнал Конец работы. После этого при поступлении на второй 30 вход элемента И 107 очередного тактового импульса с выхода 108.3 формируется управляющий сигнал на нулевом входе триггера 106, который возвращается в исходное состояние и снимает 35 управляющий сигнал с входа генератора 105. В результате генератор 105 прекращает выдачу посдедоватепьностей тактовых импульсов.

Мультиплексор 6 реализует следую- 40 щую логическую функцию:

25

Yea + АбЛб- Y,, -ь + А,. Y,

Мб -б 1

де A „их адрес на выходе мультиплексора 6;

45

А

60

50

адрес, сформированный блоком 3 форм11рования адреса;

А - адрес, поступающий с выхода шины 45 данных через блоки 39, 40 магистральных элементовJ

А(, - адрес, поступающий с выхода 66 регистра 12 текущего адреса;

А16 - адрес, поступающий с выхода 76 ПП Г,

2510

61 S 67 управляющие сигналы, формируемые на выходах 61 и 62 блока 3 формировани адреса соответственно. Мультиплексор 7 предназначен для .;управления прохождением младшего байта слова данных, поступающего с выходов 99.1-99.N блоков 25.1-25.N ввода-вывода соответственно, и старшего байта слова данных с выходов 88 регистра 14 в зависимости от управляющего кода с выхода 78 регистра 11 микрокоманд. Мультиплексор 7 реализует следующую систему логических фукций:

У, V, a;,k;; у, .V a.k;;

н V

где а;, -а.

значение первого - восьмого разрядов соответственно байта слова данных i-ro абонента

5 5 0 0 5

0

k;

-.Z

iV,.

1

L )

5

0

если в соответствующем разряде; выхода 78 регистра 11 присутствует 1, если в соответствующем разряде выхода 78 регистра 11 присутствует О,- у - число разрядов выхода 78 регистра 11, причем 2- Ы - П

N - число абонентов. Мультиплексор 8 знака служит для выбора знака, поступающего с выходов 101,1-101.N соответственно блоков 25.1-25.N ввода-вывода, в зависимости от управляющего кода на его выходе 83.1t Мультиплексор 8 реализует следующую логическую функцию: к

М V x-k:, ;,

где х- - значение сигнала с вькода

lOKi блока 25,1 ввода-вывода..

ОБ 9,1 и 9,2 (фиг. 3) предназначены для обработки восьмиразрядных дан- нык и представляют собой операционный блок, который может быть подстроен по типовой схеме, например на микропроцессорных секциях К1804ВС1. На функциональной схеме

Ч.

(фиг. 3) типового ОБ вход 79.3 ОБ соответствует 40-му выводу микросхемы К1804ВС1, вход 79.4 - 17-20-му выводу вход 43 - 22 25-му выводам, вход 79.5 - 5-7, 12-14, 26-28-м вы- водам, выходы 92.1 и 96.3 - 29-му и 15-му выводам, выходы 94.1 и 95.1 МПС - 11-му и 33-му выводам, выход 93.1 МПС - 36-39-м выводам. Выходы 94.1 и 94.2 соединяются в общей точ- ке, подключаемой через резистор к источнику питания (не показан).

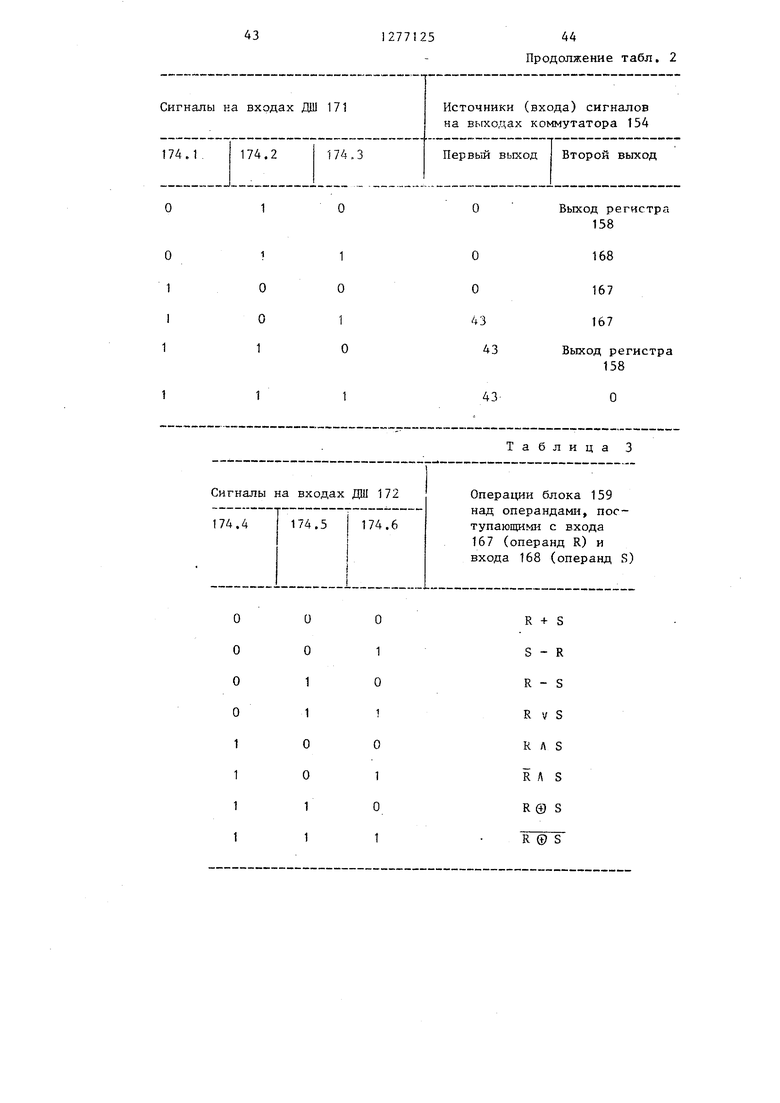

Блок 152 дешифраторов управления (фиг. 7) предназначен для управления работой ОБ 9.1, Структура блока 152 отражена в табл. 2-4.

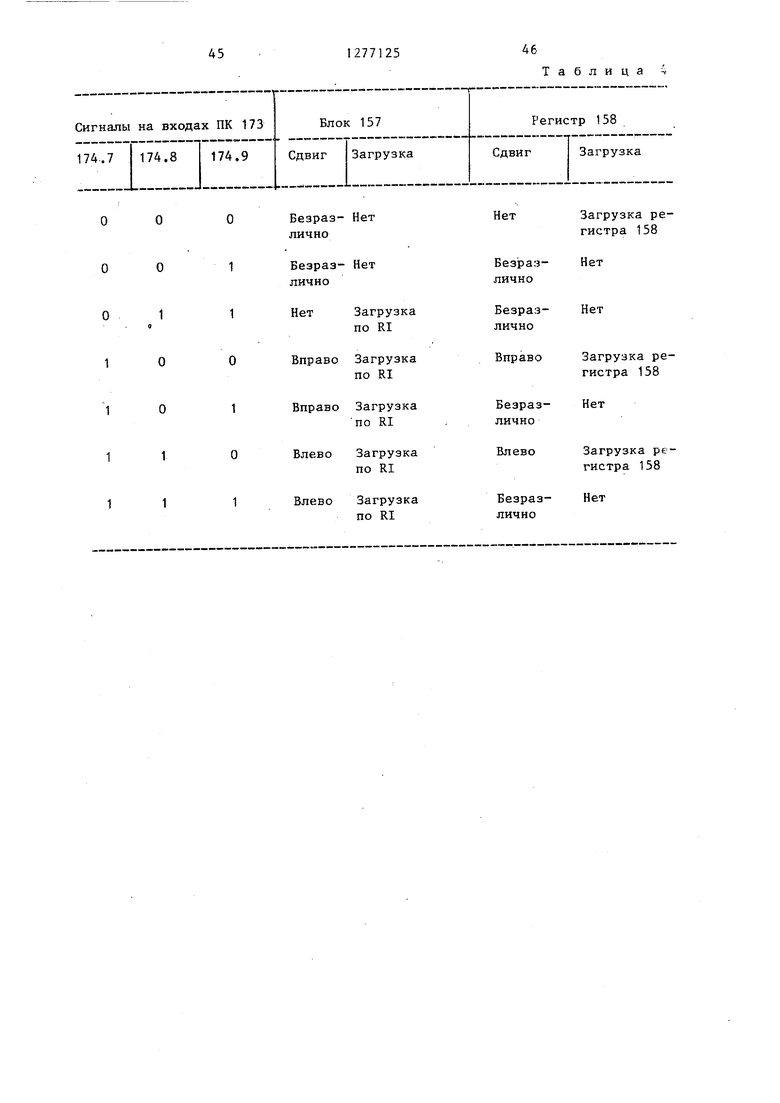

Мультиплексор 153 предназначен для прямой передачи, сдвига данных вправо или влево на один разряд и передачи их на входы блока 157. Управление мультиплексором 153 осуществляется с выхода 162 блока 152.

Коммутатор 154 предназначен для коммутации операндов на первый и вто рой входы блока 159 от четырех источников: входа 43 данных, двух источников блока 157 и регистра 158. Управление коммутатором 154 осуществляется сигналами с выхода 160 дешифратора (ДИ) 151 (фиг. 7).

Структура коммутатора 154 и ДШ 171 показана в табл. 2.

Мультиплексор 155 (фиг. 3) представляет собой мультиплексор с третьим состоянием и предназначен для коммутации данных от двух источников: выхода 169 бло.ка 159 и выхода

167 блока 157. Управление этим мультиплексором осуществляется по сигна-

лу с выхода 166 блока 152 и по сигналу с входа 79.3.

Мультиплексор 156 предназначен для прямой передачи, сдвига содержимого буферного регистра 158 впра- во или влево на один разряд и передачи его на первый информационный вход регистра 158. Управление мультиплексором 156 осуществляется с выхода 163 блока 152.

Блок 157 регистров общего назначения (фиг. 3) содержит регистры общего назначения, используемые для хранения адресов, данных или констан Адрес первого (второго) операнда задается сигналами с входа 79.4 (вход второго операнда условно не по показан). С выходов 167 и 168 блока

25

12

5

0

5

П

0

5

0

157 на коммутатор 154 выдается содержимое регистров, адреса которых заданы на выходе 79.4. С выхода мультиплексора 153 на блок 157 поступает информация, предназначенная для записи в соответствующие регистры блока 157. Управление блоком 157 осуществляется с выхода 164 блока 152 и с входа 96,3.

Буферный регистр 158 (фиг. 3) предназначен для промежуточного хранения данных и может быть использован в качестве аккумулятора. Запись информации в регистр 158 может производиться с выхода 170 м льтиплексо- ра 156 и с выхода 169 блока 159. Управление регистром 158 осуществляется по управляющим сигналам с выхода 156 блока 152 и с выхода 96.3 ОБ. При этом с двухразрядного выхода 165 блока 152 поступает сигнал разрешения записи с выхода 169 или вьпсода мультиплексора 170, а с входа 96.3 ОБ - строб записи.

Арифметико-логический блок 159 (фиг. 3) предназначен для вьшолнения арифметических и логических операций в соответствии с управляющими сигналами, которые поступают с выхода 161. Операции блок 159 выполняет за один такт. Управление этим блоком осуществляет дешифратор 172 (фиг. 7) в соответствии с табл. 3.

Табл. 3 показывает соответствие между сигналами на входах 174.4-174.6 и функцией блока 159 и, следовательно, отражает структуру дешифратора 172 и блока 159 (фиг. 3)

, ОБ 9.1 (фиг. 3) выполняет широкий набор операций. За один такт его работы реализуются операции, перечисленные в табл. 3. Длинные операции, например деление, умножение и т.д., выполняются по микропрограммам, составленным из коротких операций, аналогично микропрограммам, употребляемым в известных устройствах.

Операции загрузки и сдвига содержимого регистров блока 157 и регистра 158 определяются сигналами на входах 174.6-174.9 (фиг. 3) в соответствии с табл. 4, в которой описана работа преобразователя 173 кодов (ПК).

Дешифратор 10 (фиг. 1в) предназначен для формирования на выходах

103.1-103.n сигналов, управляющих соответственно блоками 25.1-25,N ввода-вывода.

Регистр 11 микрокоманд (фиг. 1а) предназначен для записи сигналов микрооперап 1Й, поступающих с вьссода 74 ПП 1.

Регистр 12 текущего адреса предназначен для записи и модификации адреса выполняемой микрокоманды при поступлении сигнала Требование обмена от центрального процессора. Регистр 12 имеет информационный вход D, управляющий вход V и вход синхро низации С. Код текущего адреса, поступающий на информационный вход, записывается в регистр 12 по тактовому импульсу t, , поступающему на V-вход регистра с выхода элемента И 29.1. Модификация кода текущего адреса осуществляется путем увеличения содержимого регистра 12 на единицу по тактовому импульсу ь с выхода элемента И 29.2. Управляющий вход и вход синхронизации регистра 12 Текущего адреса соответствуют вхду синхронизации и счетному входу интегральной микросхемы 533 ИЕ 7 соответственно.

Регистры 13 и 14 соответсФвенно младшего и старшего байтов апова данных служат для временного хранения слова данных. Устройство может обеспечивать чтение содержимого сче чик а 16 временных интервалов командами обмена в ЦП. При чтении содержимого счетчика 16 командами обмена с ЦП возможно наложение команды обмена на импульс модификации счетчика, что приводит к искахсению считываемой информации. Для устранения этого явления чтение содержимого счетчика 16 производится через регистры 13 и 14, в которые содержимое счетчика записывается по тактовму импульсу, не совпадающему с импульсом модификации счетчика 16.

Счетчик 15 начального адреса преназначен для записи по информационному входу адресов ячеек ОП ЦП, из которых считывается или записывается информация с входа-выхода 47 усройства. Кроме того, по тактовому импульсу, поступающему на счетный вход счетчика 15 начального адреса, происходит модификация начального адреса.

Если на входе синхронизации счетчика 15 присутствует единичный сиг-- нал, то счетчик 15 работает в режиме параллельной записи, если на входе

синхронизации присутствует нулевой сигнал, то счетчик работает в режиме модификации путем увеличения содержимого счетчика на единицу по тактовому импульсу t, , поступающему

на счетный вход счетчика 15.

Счетчик 16 временных интервалов осуществляет формирование длительности такта работы ЦП, а также формирование различных временных интервалов, определяющих время сигнала прерывания ЦП. ЦП ведет обмен данными с абонен ами в реальном масштабе времени. Организация службы времени осуществляется счетчиком 16 временных интервалов, который работает . в тех же режимах и может быть выполнен на тех же интегральных микросхемах, что и счетчик 15 начального адреса и счетчик 4 адреса.

Триггер 17 признака переноса (фиг. 16) служат для записи переноса с выхода 95.1 старшего ОБ 9.1. Триггеры 18 и 19 признаков результата соответственно этадшего и старшего байтов предназначены для записи сигнала признака результата при обработке младшего и старшего байтов слова данных. Триггер 20 управления предназначен для управления работой

счетчика 16. Триггер 21 НД предназначен для формирования сигнала НД центральному процессору. Триггер 22 управления обменом служит для записи информации, извещающей ЦП о направлении передачи данных с i-м абонентом.

Блок 23 (фиг. 4) предназначен для согласования работы устройства с центральным процессором при записи

(чтении) данных в ОП ЦП.

ПерваяИ09.1-109.8 и вторая 110.1- 110.8 группы магистральных элементов служат для формирования соответственно старшего (16-23-й разряды) и младшего (24-31-й разряды) байтов четного полуслова данных, поступаюгцих с входов 56.1 и 56.2 блока 23 через первую и вторую группы магистральных элементов на входы 57.1 и 57,2 блока 23 соответственно по управляющему сигналу на входе 120.1 группы входов при чтении данных из ОП ЦП. Третья 111.1-111.8и четвертая 112.1-112.8

15-

группы магистральных элементов предназначены для формирования соответственно старшего (0-7-й разряды) и младшего (8-15-й разряды) байтов нечетного полуслова данных, поступающих с входов 56.3 и 56.4 блока 23 при чтении данных из ОП ЦП через третью и четвертую группы магистраль ных элементов на выхЬды 57.1 и 57.2 блока 23 соответственно по управляющему сигналу на входе 120.3 блока 23. Пятая 113.1-113.8 и шестая 114. 114.8 группы магистральных элементов предназначены для формирования соответственно старшего и младшего байтов четного полуслова данных, поступающих с входов 57.1 и 57.2 . блока 23 при записи данных в ОП ЦП по управляющему сигналу на входе 120.2 блока 23. Седьмая 115.1-115.8 и восьмая 116.1-116.8 группы магистральных элементов служат для формирования старшего и младшего байтов нечетного полуслова данных, поступающих с входов 57.1 и 57.2 блока 23 при записи данных в ОП ЦП по управляющему сигналу на входе 120.4 блока 23.

Блок 24 коммутации (фиг. 5) предназначен для коммутации восьмиразрядных данных с выходов 99.1-99.N соответственно блоков 25.1-25.N ввода-вывода, с выходов 87.1-87.2 счетчика 15 начального адреса, а также с выхода 89 регистра 13 младшего бай .та. По управляющему сигналу с выхода

дешифратора 175 первый - восьмой разряды слова данных с соответствующего блока 24 проходят на выход 90 блока 24 через коммутаторы 176.1- 176.8 соответственно.

Блок 25 ввода-вывода (фиг. 6) предназначен для управления выдачей и приемом слов данных от абонентов, а также автономно осуществляет формирование частоты (темпа) обмена битов слова.

Счетчик 121 предназначен для записи кода количества переданных битов слова при вьздаче и приеме его от абонента. Разрядность счетчика 121 определяется выражением п log N + 1, где N - количество разрядов регистра 122,

Регистр 122 ввода-вывода предназначен для записи слов данных, поступающих в параллельном коде на вход 83 блока 25 от центрального процес27712516

сора и выдачи их абоненту последовательным кодом с выхода 151.N регистра 122. Кроме того, в регистр

122 по входу DI

записываются

слова данных в последовательном коде от абонента и вьщаются с выхода 99.i центральному процессору в fta- раллельном коде.

Регистр 123 управления предназначен для формирования темпа обмена битами слов данных при приеме (передаче) их от абонента. Регистры 122 и 123 могут работать в режиме записи и сдвига. Если на V-вход регистров

поступает единичный сигнал, то регистры работают в режиме записи, в противном случае - в режиме сдвига. Триггер 124 режима предназначен для управления режимом работы (записи

или сдвига) регистра 122 ввода-выво- да триггер 125 режима - для управления работой триггера 124 и регистра 123. Триггер 126 признака начала обмена формирует сигнал требования обмена словами данных мажду ЦП и абонентом. Триггер 127 знака предназначен для хранения информации о направлении обмена данными между ЦП и абонентом; триггер 128 управления ля временного хранения битов слов анных, поступаю1цих от абонента с входа 51.1 блока 25.1. Триггер 129 управления служит для управления выачей битов слов данных абоненту.

Элемент И 130 предназначен для орми{1ования сигнала установки в нулевое (исходное) состояние триггера 128 перед приемом одного бита слова от абонента, элементы И 131-133 - для

ормирования управляющих сигналов при поступлении на их входы сигналов микроопераций с группы входов 82 блока 25.1, управляющего сигнала с входа 103.1 и очередного тактового

импульса с группы входов 96 блока 25.1 ввода-вывода. Элемент И 135 предназначен для формирования сигнала установки в исходное состояние триггера 125 в момент выдачи (приема) последнего бита слова данных

элемент И 136 - для формирования сигналов синхронизации, управляющих работой абонента, при вьщаче (приеме) одного бита слова. Элемент И 137

ормирует управляющий сигнал при поступлении на его входы сигналов с входов 145.5 и 103.1 блока 25.1 ввоа-вывода, элемент И 138 - сигнал.

являющийся сигналом синхронизации регистра 122, элемент И 139 - биты слова, передаваемые абоненту элемент И 140 - сигнал установки в исходное состояние триггера 129 управ- ления в момент вьщачи или приема последнего бита слова , элемент ИЛИ 141 - сигнал установки в исходное (нулевое) состояние счетчика 121. Элемент ИЛИ 142 предназначен для формирования сигналов синхронизации регистра 122; элемент НЕ 143 - ,для формирования единичного сигнала $ I необходимого для автономного формирования темпа обмена битами слов данных.

Входы 144,1 144.3 группы входов 95 блока 25.1 предназначены для подачи трех последовательностей тактовых импульсов сдвинутых друг относи- тельно друга, соответственно t t - Г3 j входы 145.1-145о5 группы входов 82 блока 25.1 - для подачи сигн,алов микроопераций, управляющих работой блока 25.1, выход 146 регистра 123 - для выдачи сигнала, управляющего работой предлагаемого канала ввода- вывода при выдаче (приеме) бита слова.

Выход 147 счетчика 121 предназ- начен для вьщачи единичного при пе- тздаче (приеме) слова данных и нулевого сигнала после окончания передачи (ирие -la) слова данньзс, вьжод 148 jjitMeHTa И 133 - для выдачи сиг- нало1в синхронизации триггера 127 знака, т.ыходы 149.1-149.3 группы выходов 52,1 блока 25.1.являются соответственно выходами признака начала обмена, синхронизации и информации. Выходы 150,1-150.N регистра 122 предназначены для подачи на регистр 122 слова данных от ЦГ1 в параллельном коде. По входу 150.N подается знак (направление) обмена информацией.

Выходы 151,1--151.N предназначены для вьщачи слова данных в параллельном коде от абонента 1Д1, Выход 151.и служит для выдачи слова данных абоненту от ЦП в последовательном коде 1

Блок 25.1 ввода-вывода функционирует в следующих режимах: выдачи информации абоненту и приема информации от абонента.

Режим вьщачи информации абоненту

В исходном состоянии регистры, триггеры и счетчик находятся в исходном (нулевом) состоянии. Работа

начинается с момента прихода на вход блока 25.1 управляющего сигнала с выхода дешифратора 10 (фиг.1) С этого момента с группы входов 96 и 82 блока 25.1 ввода-вывода поступают сигналы синхронизации и микрооперации, управляющие работой блока 25.1 ввода-вывода. Перед вьща- чей слов данных абоненту всегда выдается управляющее слово, в котором обязательно содержится знак, извещающий абонент о направлении обмена информацией. Управляющее слово поступает на входы 150,1-150,N регистра

122и записывается в него по заднему фронту тактового импульса j , кото- рьй с входа 144,3 через элементы

И 138 и ИЛИ 142 поступает на вход, синхронизации регистра 122. Знак с входа 150.N поступает на D-вход триггера 127 знака и записывается в него по заднему фронту тактового импульса э 5 который через элемент И 133 поступает на вход синхронизации триггера 127. Разрешающими сигналами для прохожде 1ия тактового импульса (3 через элементы И 133 и 138 являются еоот)зетственно микрооперации, поступающие на входы 145.3 и 145.4.

После этого по тактовому импульсу , и микрооперации, поступающей с входа 145.2, происходит установка триггера 126 ОНО в единичное состояние. На выход 149.1 группы выходов 52.1 блока 25,1 выдается сигнал признака начала обмена абоненту. Кроме того, тактовый импульс с, с выхода элемента И 132 устанавливает триггеры 129 и 125 в единичное состояние, а такжеs пройдя через элемент ИЛИ 141, подтверждает исходное (нулевое) состояние счетчика 121. Единичный сигнал с выхода триггера . 125 переводит триггер 1-24 в единичное состояние и устанавливает регистр 122 в режим сдвига ранее запк- санног о управляющего слова.

По тактовому импульсу Tj в регист

123записывается в младший разряд елчница с выхода элемента НЕ 143. Пареное единицы в старшие разряды регистра 123 осуществляется по очередному Тактовому импульсу j после установки триггера 125 в исходное (нулевое) состояние.

По второму тактовому 1-1Мпульсу Сз триггеры 125 и 126 уста 191

навливаются в исходное нулевое состояние.

При записи единицы в старший разряд регистра 123 по очередному тактовому импульсу tj единичный сигна с выхода 146 регистра 123 поступает на вход элемента И 136 и по очередному тактовому импульсу Г поступает на выход 149.2 группы выходов 52.1 блока 25.1. Кроме того, единичный сигнал с выхода элементов И 136 через элемент ИЛИ 142 поступает на вход синхронизации регистра 122 и производит сдвиг записанного управляющего слова. Информационный сиг- нал с выхода 151.N регистра 122 через элемент И 139 поступает на выход 149.3 группы выходов 52.1.

Единичный сигнал с выхода элемента И 136 поступает также на счетный вход счетчика 121, который производит счет числа переданных битов слова данных.

Единичный сигнал с выхода 146 регистра 123, пройдя через элемент И 135, по тактовому импульсу Т, (с выхода 147 счетчика 121 на вход элемента И 135 поступает единичный разрешающий сигнал) поступает на единичный вход триггера 125 режима, пе- реводя последний в единичное состояние . Единичный сигнал с выхода триггера 125 разрешает запись единицы в младший разряд регистра 123 с выхода элемента НЕ 143. Блок 25.1 готов к выдаче очередного бита слова данных. Вьщача очередных битов с выхода 151.N происходит аналогично.

При выдаче последнего бита слов данных из регистра 122 на единичном выходе (п + 1)-го разряда счетчика 121 появляется единичный сигнал, который поступает на выход 100.1 блока 25.1, сигнализируя об окончании вы- дачи управляющего слова абоненту. Кроме того, единичный сигнал с единичного выхода (п + 1)-го разряда счетчика 121 по тактовому импульсу f, проходит через элемент И 134 и переводит в исходное (нулевое) состояние триггер 124, а также через элемент И 140 - триггер 129 управления .

Выдача сигнала конца обмена слово на выход 100.1 блока 25.1 сигнализирует о том, что слово данных вьздано абоненту и блок 25.1 готов к записи и выдаче очередного слова.

2520

После выдачи управляющего слова передаются слова данных, нлн информационные слова (ИС). Запись и выдач ИС имеет некоторые особенности. При записи ИС по тактовому импульсу , на выходе 145.3 отсутствует микрооперация, управляющая записью знака ;в триггер 127. По тактовому импульсу 6, отсутствует микрооперация на входе 145.2 признака начала обмена, но присутствует микрооперация на входе 144.1, переводящая через элемент И 131 триггер 125 в единичное состояние, а также через элемент ИЛИ 14 устанавливающая счетчик 123 в исходное (нулевое) состояние. В дальнейшем запись ИС в регистр 122 и вьщача его абоненту происходит аналогично записи и выдаче абоненту управляющего слова. После окончания выдачи массива ИС на вход 145.5 поступает микрооперация конца группового обмена, которая, пройдя через элемент Ш1И14 устанавливает счетчик 121 в исходное (нулевое) состояние.

Режим приема информагуш от або нента.

В режим приема информации блрк 25.1 ввода-вывода переходит после вьщачи абоненту управлякицего слова, которое настраивает абонент на вьща- чу информации на вход 51.1 блока 25.1 ввода-вывода.

На вход 144.1 поступает микрооперация, которая по тактовому импульсу t, устанарливает триггер 125 режима в единичное состояние. Сигнал с выхода триггера 125 устанавливает триггер 124 в единичное состояние. Нулевой сигнал с выхода триггера 124 разрешает запись информации (бита слова данных), поступающей на вход регистра 122 с выхода триггера 128. Частота приема битов определяется блоком 25,1 ввода-вывода аналогично частоте при вьщаче битов слова данных путем сдвига единицы в регистре 123. При появлении единицы на (N - 1)-м выходе регистра 123 единичный сигнал с данного выхода по тактовому .импульсу f проходит через элемент И 130 на нулевой вход триггера 123 и подтверждает его исходное (нулевое) состояние, подготавливая триггер 128 к приему бит.а слова данных.

По очередному тактовому импульсу (2 единица появляется на N-M выходе 146 регистра 123 и по тактовому

импульсу

2112771

через элемент И 136 поступает на выход 149,2, синхронизируя поступление бита слова от абонента на вход 51.1. блока 25.1. Одновременно единичный сигнал с выхода элемента И 136 поступает на счетный вход счетчика 121 и через элемент ИЛИ 142- на вход синхронизации регистра 122. В результате бит информации (нзшь или единица) записывается в младший разряд регистра 122 с выхода триггера 128.

Прием последующих битов слова данных происходит аналогично. Биты слова последовательно записываются в младший разряд регистра 122 с выхода тригг ера 128, а ранее записанные биты сдвигаются в более старшие разряды регистра 122 до тех nopj пока на единичном выходе (п + 1)-го разряда счетчика 121 не появится единичный сигнал, поступающий на выход 100,1 блока 25,1.

Прием следующих ИС происходит аналогичным образом. При приеме последнего ИС в массиве информационных слов на вход 145.5 поступает микрооперация конца группового обмена, которая, пройдя через элементы И 137 и или 141, устанавливает счетчик 121 в исходное (нулевое) состояние, подготавливая его к дальнейшей работе.

Коммутатор 26 предназначен для коммутации сигналов с выходов 79.2 и 79.1 регистра 11 микрокоманд и формирования на своем выходе сигнатга входного переноса младшего ОВ 9.2, Коммутатор 27 служит для коммутации сигналов признака результата при обработке данных MilC 9.1 и 9.2.

Элементы И 28-38 предназначены для формирования управляющих сигналов, обеспечивающих синхронизацию работы устройства.

Второй 39 и третий 40 блоки магистральных элементов предназначены щГя выдачи с шины 45 данных ЦП начальных адресов микропрограмм, KOTOрые поступают на вход 65 мультиплексора 6. Первый блок 41 магистральных элементов служит для выдачи на шину 46 адреса ячейки СП ЦП, к которой производится обращение. Шина 43 старшего байта данных служит для передачи старшего (0-7-й разряд) байта слова данньЕХ, передаваемого между Щ1 и абонентом.

25

22

5

0

5

0

0

5

0

5

Шина 44 младшего байта данных х.ред- назначена для передачи младшего (8- i 15-й разряд) байта слова данных, передаваемого между ЦП и абонентом.

Информационная шина 45 данных (0 31 разряд) служит для приема-передачи данных из ОП ЦП, 0-7-й разряды i 8-15-й разряды шины используются для передачи соответственно старшего и младшего байтов первого (нечетного) полуслова данных. 16-23-й разряды и 24-31-й разряды используются для пере дачи соответственно старшего и младшего байтов второго (четного) полуслова данных. Формат слова данных ОП центрального процессора равен двум форматам слов данных абонента. Шина 46 адреса служит для передачи кода адреса ячеек ОП ЦП,

Предлагаемое устройство состоит из двух частей: блоков ввода-вывода 25.1-25.N,, которые автономно осуществляют формирование темпа обмена битов слова, прием (вьщачу) слова . гиных, и процессора ввода-вывода ..микропрограммное устройство управления, ОП, операционный блок, блоки коммутации и согласования и т.д.), который осуществляет организацию счетчика начального адреса и счетчи;- ка длины массивов, организацию пре- рьшания, обработку (в случае необходимости) информации, управление блоками ввода-вывода после приема (выдачи) ими слова данных, организацию связи с ЦП.

Устройство работает следующим образом.

В исходном состоянии все триггеры, регистры и счетчики устройства находятся в нулевом состоянии, ОП 2 находится в произвольном состоянии, в нулевой ячейке ПП 1 хранится микрокоманда, которая с выхода 75 ПП Г вьщает на вход блока 3 формирования адреса микрооперацию Признак исходного и устанавливает на выходе 63 записи-счета и выходе 64 блокировки счета блока 3 формирования адреса нулевые управляющие сигналы.

Фунционирование устройства начинается с приходом на вход 50 устройства сигнала пуска. В результате блок 5 синхронизации начинает формировать на выходах 96.1-96,3 группы выходов 96 три последовательности тактовых импульсов, сдвинутых друг относительно друга, соответственно , - (з.

ilyjioHhip с .иг налы с: ньгходов б З и Ь4 блока 3 формирования адреса поступают соотпетственно на входы элементов И 28 и 31. В результате тактгшый импульс Г, не поступает на счетный вход и вход синхронизации счетчика 4 адреса. Таким образом, организуется режим статического зависания (СЗ), выходом из которого является появление на входе 48.1 группы входов 48 уст- ройства сигнал Требование обмена.

Процессор ввода-вывода (ПВВ) наст- .раивается на обмен данными с соответствующим абонентом тремя командами обмена ОБМ1-ОБМЗ. Кроме команд обмена

1

2

3

HAi,(0-15р) HAi ОЗУ ЦП (16-31р) HAij(0-15p) Ы сл (16-31р) HAi,(0-15p) УС i (16-31р)

N

ел

ОБМ 4 НА4 (0-15 где НА i ОЗУ ЦП - начальный адрес массива слов данных, передаваемых по i-му направлени обмена и хранящихся в ОП центрально го процессора, где i 1,N,- N - количество абонен. TOBJ

количество слов данных, передаваемых по i-му направлению обмена; УС; - управляющее слово,

передаваемое i-му абоненту; начальные адреса соответствующих

микропрограмм, выполняемых процессо ром ввода-вывода j-й командой обмена по i-му направ- лению обмена,Де i 1,N, j 1,4. Рассмотрим функционирование устройства при г ьтапнении команд обмена ОБМ1 и ОБМ2 (см. фиг. 8).

Обмен данными с ЦП асинхронный. При поступлении на вход 48.1 блока 3 формирования адреса сигнала Требование обмена на выходах 58, 63 и 6.1 блока 3 формируются единичные уп- равляюгцие сигналы. Управляющий едиНА

ОНМ1-0 -;М 3, ГК1 каждому направлению обмена в счетчик 16 временных интервалов устройства командой обмена ОНМ4 записывается уставка, котора определяет длительность временного интервала, окончание которого фиксируется сигналом прерывания, являющегося импульсным сигналом счетчика и поступающего на выход 53 устройства. После переполнения счетчик 16 устанавливается в исходное (нулевое) состояние и для его нового запуска необходима новая команда ОБМ 4 по записи кода соответствующей уставки. Команды обмена имеют следующий формат:

Код уставки (16-31рХ яичный сигнал на выходе 58 записывает содержимое счетчика 4 адреса (нулевой код) в регистр 12 текущег,о адреса по тактовому импульсу с, . Начальный адрес микропрограммы, поступающий с входов-выходов 47.3 и 47.4 устройства через шину 45 данных входы-выходы 56.3 и 56.4, блоки 39 и 40 магистральных элементов, проходит на вход 65 мультиплексора 6. В результате присутствия на управляющих входах мультиплексора 6 кода 1,0 (на выходах 61 и 62 блока 3 формирования адреса сформированы соответственно единичный и нулевой сигналы) начальный адрес микропрограммы проходит через мультиплексор 6 и поступает на информационный вход счетчика 4 адреса. Тактовый импульс

t с выхода 96.1 блока 5 синхронизации, пройдя через элемент И 28 и поступая на вход синхронизации счетчика 4 адреса, записывает начальный адрес микропрограммы с выхода 67 мультиплексора 6 в счетчик 4 адреса. Из ПП 1 выбирается первая микрокоманда команды обмена, которая по тактовому импульсу Г запишется в регистр 11 микрокоманд. В результате на выход 81.1 группы выходов 55 устройства ЦП вьщается сигнал Разрешение обмена. Кроме того, с выхода 75 признаков перехода ПП 1 на вход блока 3 формирования вьща- ется микрооперация Признак исход25

ного, которая устанавливает на вы- ходах 58, 63 и 64 формирователя 3 адреса нулевые сигналы после снятия сигнала Требование обмена от ЦП. Таким образом, происходит переход в режим СЗ ожидания сигнала от центрального процессора Признак УС.

С приходом сигнала Признак УС на вход 48,2 группы входов 48 устройства на выходе 64 блока 3 формирова- НИН адреса формируется единичный управляюпщй сигнал, который разрешает прохождение тактового импульса , через элемент И 31 на счетный вход счетчика 4 адреса. Счетчик 4 адреса по тактовому импульсу , формирует исполнительный адрес второй микрокоманды команды обмена.С выхода 69 ПП ,1 на вход блока 23 поступает

микрооперация, которая разрешает

.-

прохождение содержимого 16-31-го разряда команды обмена с входов-выходов 47.1 и 47.2 устройства через шину 45 данных, входы-выходы 56.1 и 56.2 блока 23 на выходы 57.1 и 57,2 бло 23.

На выходе 70 ПП 1 присутствует микрооперация, разрешающая запись по тактовому импульсу содержимого 16-23-го разрядов и 24-31-го разря- дов команды обмена соответственно в регистр 14 старшего байта и в регист 13 младшего байта. Одновременно на выходах ;1, 72, 73 ПП 1 присутствуют управляюище сигналы, предназначенные для записи по тактовому импульсу 1 старшего байта (16-23-й разряды команды обмена) с шины 43 старш:ей части данных в соответствующую ячейку СП 2.

По очередному iктoвo гy импульсу . в счетчик 4 записывается исполнительный адрес третьей микрокоманды, по которой осуш,ествлявтся прохождение байта (24-31-й разряды команды обмена) с выхода 89 регистра 13 через блок 24 коммутац1-1И на шину 43 старшей части данных по тактовому

импульсу

и последующая запись

младшего байта в соответствующ ю ячейку СП 2 по тактовому импульсу Tj. Прохождение младшего байта чере блок 24 коммутации обеспечивается микрооперациями с выхода 78 регистра 11 икpoкoмaнд, поступающими на управляюшрй вход блока 24 коммутации. Одновременно с выдачей микроопераций на выход 78 регистра 11

771

5

15

20

25

р 35 40

45

50

55

2526

с выхода 81.2 регистра 11 на группу выходов 55 устройства поступает сигнал Конец обмена, сигнализируя ЦП об окончании обмена. Кроме того, с выхода 75 ПП 1 на вход блока 3 формирования адреса поступает микрооперация Конец микропрограммы (КМП)J по которой осуществляется прохождение нулевого кода из регистра 12 текущего адреса через мультиплексор 6 адреса и его запись в счетчик 4 по очередному тактовому импульсу 2, , По нулевому коду выбирается нулевая ячейка Ш1 1 и формируется на выходе 75 признаков перехода микрооперация Признак исходного, блокирующая счетчик 4 адреса (см. фиг, 8), Таким образом, происходит переход в режим СЗ, Устройство готово к выполнению очередной команды обмена.

Функционирование устройства при выполнении команд обмена ОБМЗ и ОБМ4 происходит аналогично. Рассмотрим особенности вьтолнения команды ОБМЗ.

С приходом сигнала Признак УС от центрального процессора разрешается модифик:ация кода адреса счетчика 4 адреса по тактовому импульсу D, , а также открывается блок 23, Кроме того, по тактовому импульсу Г, формируется микрооперация записи старшего и младшего байтов соответственно в регистры 14 и 13, По тактовому импульсу t j на выход 82 регистра 11 вьщаются микрооперации выбора определенного блока 25.1 ввода-вывода ,

По тактовому импуль су Tj микрооперации Запись знака и Запись УС с группы выходов 82 регистра 11 микрокоманд производят запись старшего байта и знака обмена в регистр 122 ввода-вывода и триггер 127 знака блока 25.1 ввода-вывода соответственно (см, фиг, 5).

По очередному тактовому импульсу L, микрооперация Признак начала обмена с входа 145.2 группы входов 83 блока 25.1 устанавливается в единичное состояние триггер 126 ПНО блока 25.1 ввода-вывода, а также форми руются микрооперации на выходах 71, 72 и 73 ПП 1 для записи мх;адшего байта в ОП2. По очереднрму тактовому импульсу осуществляется запись единицы в регистр 123 блока 25.1 ввода-вывода, С этого момента блок

271

25. i ввода-вывода начинает работать автономно по выдаче (приему) слова данных абоненту. Кроме того, в этом же такте работы устройства формируются следующие микрооперации: мик- рооперации с выхода 78 регистра 11, управляющие прохождением младшего байта с выхода 89 регистра 13 через блок 24 коммутации на вход-выход 86 ОП2; микрооперации Конец обме- на и КМП.

Рассмотрим особенности функционирования устройства при выполнении команды ОБМ4.

Код уставки с входа-выхода 57.1 (16-23 разряд) с входа-выхода 57.2 (24-31 разряд) через шины 43 и 44 данных соответственно поступает на информационные входы счетчика 16 временных интервалов.

По тактовому импульсу f в регист

11записывается вторая микрокоманда, которая с выхода 83.3 группы выходов 83 формирует микрооперацию, которая, поступая на вход синхронизации счетчика 16, записывает код уставки в счетчик 16. Одновременно триггер 20 устанавливается в единичное состояни

По следующему тактовому импульсу 2 в регистр 11 записывается третья микрокоманда, которая на выходе 83.3 формирует нулевой сигнал. С выхода 81.2-регистра 11 на группу выходов 55 устройства поступает сигнал Конец обмена, сигнализируя ЦП об окончании обмена. В момент формирования исполнительного адреса третьей микрокоманды с выхода 75 ПП 1 на вход блока 5 формирования адреса поступает микрооперация КМП , которая формирует на выходах 61 и 62 блока 3 формирования адреса нулевые управляющие сигналы, позволяющие пройти коду содержимого регистра

12текущего адреса через мультиплексор 6, и единичный управляющий сигнал на выходе 63 формирователя 3, который по тактовому импульсу , записывает содержимое регистра 12 текущего адреса (нулевой код) в счетчик 4 адреса. Нулевой сигнал на выходе 83.3 разрешает прохождение тактового импульса через элемент И 38

на вход синхронизации счетчика 16,

увеличивая его содержимое на едини цу. По очередным тактовьм импульсам Т содержимое счетчика 16 продвигается до тех пор, пока счетчик не пе

125

28

25

5.

р

е.

30

55

реполнится. Сигнал переполнения поступает на выход 53 устройства и одновременно на вход синхронизации триггера 20, переводя последний в ..исходное (нулевое) сосстояние. Нулевой сигнал с единичного выхода триггера 20 запрещает прохождение тактового импульса через злемент И 38 на вход синхронизации счетчика 16.

Для нового запуска счетчика 16 необходима очередная команда ОБМ 4.

Рассмотрим функционирование устройства после вьщачи (приема) слова данных абоненту (см. фиг. 9).

Сигналы конца обмена словом с выходов 100.1-100.N блоков 25.1-25.N поступают соответственно на входы 102.1-102.N блока 3 формирования адреса. Данные сигналы возникают асинхронно по отношению к ЦП и друг к другу. При этом в одно и то же время может иметь место более чем один сигнал конца обмена словом. Процессор ввода-вывода (ПВВ) устанавливает приоритет между этими сигналами так, что в любой момент времени обрабатывается только одно требование на обслуживание. До тех пор, пока сигналы конца обмена словом не будут учтены ПВВ, они сохраняются в блоках ввода-вывода. Если ПВВ занят вьшолнением команды обмена или микропрограммы обслуживания i-ro блока ввода-вьшода, где , N-1, то сигнал требования обслуживания от блока ввода-вывода не воспринимается до тех пор, пока не будет выполнена текущая микропрограмма. Если ПВВ находится в режиме €3, то сигнал конца обмена словом с выхода 100.1, воздействуя на вход блока 3 формирования адреса, формирует на выходе 60 последнего начальный адрес микропрограммы обслуживания 1-го абонента, где 1 1,N. Кроме того, на выходах 61, 62 и 63 блока 3 формирования адреса формируются соответственно нулевой и единичные управляющие сигналы, разрешающие прохождение НА МП через мультиплексор 6 и последующую запись его по тактовому импульсу в счетчик 4 адреса. На выходе 75 Ш1 1 формируется микрооперация Анализ знака, по тактовому импульсу Г. на выходе 83,1 группы выходов 83 регистра 11 формируются управляющие сигналы, поступающие на управляющие входы мультиплексора 8 знака и разрешающие

. 29. 1

прохождение знака обмена с выхода 101.1 блока 25.1 через мупьтиплерссор 8 на выход 97.1. Сигнал знака обмена с выхода 96.1 поступает на вход 98.1 блока 3 формирования адреса к в зави симости от своего значения (нуль Ш1и: единица) формирует адрес следующей микрокоманды либо путем увеличения содержимого счетчика 4 адреса на единицу, либо путем записи ядре- са перехода с выходов 76 ПИ 1 (символ 2, фиг. 9). Если сигнал знака равен нулю (налравление передачи соответствует передаче данных из ОЗУ Ьп ЦП к абоненту), то на выходах 63 и 64 блока 3 формирования адреса появляются соответственно нулевой и единичный управляющие сигналы и формирование исполнительного адреса микрокоманды происходит путем продвиже- НИН содержимого счетчика 4 адреса на единицу по тактовому импульсу t, . Если сигнал знака обмена равен единице (направление .передачи соответствует передаче данных в СП ЦП), то исполнительный адрес микрокоманда формируется путем записи адреса с выхода 76 -ПП 1, по тактовому импульсу J, при этом на выходах 63 и 64 блока 3 формирования присутствуют соответственно единичный и нулевой управляюпще сигналы.

Рассмотрим функционирование устройства при чтении данных из ОП ЦП.

По второй микрокоманде микропрог- -раммы обслуживания i-ro абонента (символ 3) формируются микрооперации на выходах 71 и 72 ЦП 1 для обращения к фиксированной ячейке , в которой хранится информауоря о выда че старшего ( 0) или малдше- го ( 1) байта слова данных; Кроме того, в этой же микрокоманде формируются следующие микрооперации: кода операции логического умножения О содержимого ячейки выходе 79.5 группы выходов 79 регистра 11 микрокоманд; кода адреса регистра общего назначения (например РОН1), в который записывается резуль тат сложения содержимого О по тактовом:, импульсу с i микрооперация Признак Z на выходе 75 ПП 1.

Если результат вьшолнения опера- ции логического умножения нуль равен нулю (признак. байта 0) триггер 18 устанавливается в единичное состояние по так530

товому импульсу Zj е,;иничными сигналом с выхода 94 о i признака разульт;;;-. та ОБ 9.1 и 9 о2 через элемент И 34. Единичный сигнал с выхода триггера 18 проходит через коммутатор 27 на выход 97.2 и поступает на вход 98.2 блока 3, формируя на выходах 61, 62 и 63 блока 3 единичные сигналы (код Ijljl) для прохождения и записи адреса перехода с выхода 76 ПП 1 через мультиплексор 6 в счетчик 4 адреса. азрешающим сигналом для прохождения единичного сигнала признака результата через элемент И 34 и атор 27 является нулевой сигнал на ыходе 79.1 признака байта группы, выходов 79 регистра 11 микрокоманд.

ри выполнении арифметических операций над данными обычной разрядности (восемь разрядов) на выходе 79.1 всегда присутствует нулевой сигнал, который с выхода элемента НЕ 42. производит запись признака результата в триггер 18.

По третьей микрокоманде (символ 4) формируются следующие микрооперации: на выходах 7,1 и 72 ПП t, на выходе 80 регистра 11 микрокоманд для выбора блока ввода-вывода, закончившего вьщачу абоненту старшего байта слова данных;микрооперации Запись УС, Запись канала соответственно на входах 145.4 и 145.1 группы входов 83 блока 25.1 ввода- вывода (см. фиг 5),

Данные микрооперации осуществляют выборку младшего байта слова данных из фиксированной ячейки ОП 2 и последующую запись его. в блок 25.1 ввода-вывода.

Четвертая микрокоманда (символ 5) производит операцию логического умножения содержимого РОН 1 (нулевого кода) с единицей и последующую запись результата умножения (единицы) в фиксированную ячейку ОП 2. Для этого формируются микрооперации на выходах 79.2, 79.3, 79.4 и 79,5 группы выходов 79 регистра 11 микрокоманд, на выходах 71, 72 и 73 ПП Ij а также на выходе 75 ПП 1 микрооперация КМП.

Если результат (символ 3) вьшолнения операции Логического утлнотае- ния на нуль не равен нулю (признак байта ; 1)« то формирование адреса очередной третьей микрокоманды происходит путем увели311277

чения содержимого счетчика 4 адреса на единицу, В результате выполнения третьей микрокоманды (символ 6) производится выборка младшего байта счетчика длины массива () oi ,3 5 из фиксированной ячейки 01Г2, выполнение арифметической операции сложа- ния содержимого Ы,- с нулем и запоминание результата сложения в РОН 2, Для этого формируются микро- О операции на выходах 71 и 72 ПП 1, на выходах 79.5 и 79.4 группы выходов 79 регистра 11 микрокоманд.

Четвертая микрокомавда (символ 7) осуществляет выборку старшего байта 5 из фиксированной ячейки Со(, 1;; вьшолнение арифметической операции сложения содержимого данной ячейки с нулем и запись результата в РОНЗ.

При выполнении арифметических one- 20 раций микропрограммы микропроцессорными секциями 9.1 и 9.2 с младшим байтом (символ 6) признак пераноса вьтолнения результата арифметической операции записывается с выхода 95.1 ОБ 9.1 в триггер 17 признака переноса, одновременно признак результата записывается в триггер 18 признака результата младшего байта и поступает на вход блока 3 без поступления микрооперации Признак Z с выхода 75 ПП 1.

При обработке микрокоманд с признаком (символы 7 и 8, фиг. 9) старшего байта (на выходе 79.. 1 присутству- 35 ет единичный сигнал) переключается коммутатор 26 для передачи на в: .од 9.2 ОБ 9.2 признака переноса результата выполнения микрокоманды над младшим байтом с выхода 17, одновре- менно переключается коммутатор 27, на выход 97.2 которого передается результат логического умножения сигналов с триггеров 18 и 19 признаков результатов младшего и старшего бай- тов соответственно. Сигнал с выхода 97.2 коммутатора 27 поступает на вход 98.2 блока 3 одновременно с поступлением микрооперации Признак Z с выхода 75 ПП 1. Таким образом, ее- 50 ли счетчик длины массива данных об нулился (Njj 0), то по пятой микрокоманде, адрес которой формируется с выхода 75 ПП 1, осуществляется установка счетчика 123 блока 25.1 вво- 55 да-вывода в исходное (нулевое) состояние по микрооперации Конец группового обмена на входе 145.5 группы

30

О

5

0

5 0 5

0

2532

входов 83 блока 25.1 ввода-вывода (символ 12). Кроме того, на выход 81,3 группы выходов 55 устройства выдается микрооперация Прерывание, а на выход 75 ПП 1 - микрооперация КШ,

Если содержимое ячейки счетчика длины массива не равно нулю (N 0) то адрес пятой микрокоманды формируется путем увеличения содержимого счетчика 4 на единицу. Пятая микрокоманда (символ 9) в этом случае производит сложение содержимого РОН 1 с единицей и помещает результат сложения в фиксированную ячейку ОП 2 ° шестой Микрокоманде (символ 10) производится запись из фиксированной ячейки I ОП 2 младшего байта начального адреса ОП центрального процессора (НА ОП ЦП) в счетчик 15. Для этого формируются микрооперации на выходах 71 и 72 ПП t и на выходе 84.2 группы выходов 84 регистра 11 микрокоманд.

Седьмая микрокоманда (символ 11) записывается из фиксированной ячейки ОП2 старший байт НА ОП ЦП в счетчик 15 по микрооперациям на выходах 71 и 72 ПП 1 и выходе 84.1 регистра 11 микрокоманд. Кроме того, микрооперацией на выходе 83.4 регистра 11 устанавливается в единичное состояние триггер 21 непосредственного доступа, извещающий ЦП с группы управляющих выходов 54 устройства о том, что ПВВ готов к приему слова данных из ОП ЦП. Формируется микрооперация Признак исходного , по которой устройство переходит в режим СЗ.

Рассмотрим особенности функционирования устройства при записи данных в ОП ЦП от абонента.

При записи данных в ОИ ЦП (см. фиг. 9) во второй микрокоманде (символ 13) осуществляется проверка признака байта аналогично проверке признака байта при чтении данных из ОП ЦП (символ 3).

При записи данных в ОП ЦП от абонента приему информационных слов в блок ввода-вьшода устройства всегда предшествует вьщача управляющего слова абоненту. Поэтому по третьей микрокоманде (символ 14 или 19) осуществляется проверка содержимого фиксированной ячейки oi,. ОП 2 на факт выдачи управляющего слова абоненту.

3312771

сли ячейка признака передаваемого айта равна нулю и результат огического умножения содержимого чейки ( признака выдачи управяющего слова на нуль равен нулю (абоненту выдан старший байт), то по четвертой микрокоманде (символ 15) осуществляется выборка мгшдшего байта УС из ОП 2 и запись его в, БВВ. о пятой микрокоманде (символ 16) fO роизводится запуск блока ввода-вывода на автономную выдачу байта слова данных абоненту 4, логическое умножение содержимого РОН 1 (признака передаваемого байта) на единицу и 15 запоь&1нание результата сложения в иксированную ячейку Oil 2. Кроме того, формируется микрооперация КМП, которая осуществляет выход в исходное состояние.20

Если оказалось, что управляющее слово уже быпо выдано абоненту оС ; О, 0) , то по четвертой микрокоманде (символ 17) осуществляется запись в ОП2 старшего байта ело-25 на данных из блока ввода-вывода.

По пятой микрокоманде (символ 18) производится логическое умножение содержимого РОН 1 на единицу, запоминание результата в ячейке .(/41; ОП 2, запуск блока ввода-вывода на автономный прием младшего байта слова данных от абонента. В этой же микрокоманде формируется микрооперация КМП.35

Если абоненту, бып вьщан младший байт управляющего слова (oL j 5 О, oi i ,- 0), то четвертая микрокоман- да (символ 23) осуществляет запуск блока ввода-вывода на автономный при-40 ем старшего байта слова данных от абонента и производит логическое умножение содержимого РОН 4 на единицу и запоминание результата в ячейке ыЛ; Результат выполнения предыду- щей третьей микрокоманды (символ 19) запоминается в РОН 4.

Если от абонента был принят младший байт слова данных(с()1 ; t 0) то осуществляется уста- 50 новка признака байта в ячейку , запись младшего и старшего байтов НА ОП ЦП .соответственно из ячеек установка триггера 21 НД и триггера 22 знака в единичные состоя-55 ния и формирование микрооперации Признак исходного, которая переводит устройство в режим СЗ (символы

2534

20-22) . Выход из режима СЗ осуществляется по сигналу от ЦП Разрешение ИД.

Рассмотрим функционирование устройства при записи данных в ОП ЦП (см. фиг. 10).

При поступлении сигнала Разрешение НД на вход 48.3 блока 3 происходит формирование на выходах 63 и 64 последнего соответственно нулевого и единичного сигналов. По тактовому импульсу о, формируется исполнительный адрес первой микрокоманды (символ 13) микропрограммы прямого доступа в память при записи данных в ОП ЦП.

Первая микрокоманда осуществляет одновременную выдачу на шину 45 данных старшего и младшего байтов слова данньпс. Старший байт выбирается из ячейки ОП2 на выход 56.1 блока 23 через шину 43 старшего байта. Младший байт с выхода 99.1 блока 25.1 ввода-вывода через мультиплексор 7 поступает на шину 44 младшего байта и далее через блок 23 - на выход 56.2 блока 23. Таким образом, осуществляется выд,ача 16-разрядного слова данных в шину 45 данных и последующая его запись в ОП 1Щ по адресу, записанному в счетчике 15 и выдаваемому в шину 46 адреса по микрооперации на выходе 84,4 группы выходов 84 регистра 11 микрокоманд.

По второй (символ 14) и третьей (символ 15, 16) микрокомандам произ водится проверка счетчика длины массива (ячейки oi., ОП2) на переполнение и установка триггера НД в исходное состояние. Если все слова по 1-му направлению обмена оказались переданными - О, то блок ввода-вьшода переводится в .исходное состояние микроопераций Конец группового обмена на входе 145.5 группы входов 82 блока 25.1 ввода-вывода. Кроме того, формируется микрооперация Прерывание на вы ходе 81.3 регистра 11 микрокоманд и КМП на выходе 75 ПИ 1. Результат сложения ot il; с единицей запоминается в РОН 2, а результат сложения с нулем- в РОН 3 (символ 22).

Если оказапось, что не все слова переданы 1 О, то по четвертой микрокоманде осуществляется модификация счетчика 15 по тактовому импульсу 1/3 и микрооперации на вы35

ходе 84.3 группы выходов 84 регистра 11, а также запуск блока ввода- вывода (символ 17).

По пятой и шестой микрокомандам (соответственно сомволы 18 и 19) осуществляется запись младшего байта и старшего байта счетчика 15 через блок 24 коммутации в соответствующие фиксированные ячейки ОП2.

По седьмой микрокоманде (символ

20)содержимое РОН 2 помещается в ячейку foi i младшего байта счетчика длины массива ОП 2.

По восьмой микрокоманде (символ

21)содержимое РОНЗ помещается в ячейку Сы J старшего байта счетчика длины массива ОП2 и формируется микрооперация КМП.

Адрес ячейки ОП ЦП определяется счетчиком 15. Разрядность счетчика определена таким образом, что младший разряд счетчика 15 не поступает .на адресный вход ОП ЦП. Это позволяет сохранять адрес ячейки ОП ЦП в течение выдачи (приема) двух 16-раз- рядных слов данных абоненту. Формат слова данных ОП ЦП равен двум форматам слов данных абоненту. Два cjfoBa данных от абонента или к абоненту записьшаются (считываются) по од- ному адресу четному или нечетному в зависимости от того, какой бьш загружен первоначальный адрес в счетчик 15. Например, первоначальный адрес, записанный в счетчик 15, равен 00000000. Увеличение содержимого счетчика 15 не приводит к изменению адреса ячейки ОП ЦП, так как код адреса равен 0000000t. Первый разряд равен 1 остальные семь разрядов сохраняют значение О. Таким образом, по адресу 0000000 будет записан (считано) два слова данных от абонента. В последующем код счетчика 15 будет равен 00000010 и слова данных от абонента будут записываться по адресу 0000001.

Чтение данных из ОП ЦП при вьшол- нении микропрограммы прямого доступа в память осуществляется аналогично

(

записи данных в ОП ЦП (см. символы 4-12, фиг. 10).

В коде вьшолнения микропрограммы обслуживания абонента возможно поступление сигнала Требование обмена на вход 48.1 блока 3 формирования адреса. В этом случае на выходах 58 и 59 блока 3 формируются единичные

12536

управляющие сигналы, которые осуществляют запись Р модификацию адреса текущей микрокоманды соответственно по тактовым импульсам б, и с , После выполнения команды по микрооперации КМП тскущи; ; адр прерванной микропрограммы через мультиплексор 6 записывается в счетчик 4 адреса и выполнение прерванной микропрограммы продолжается.

Функционирование устройства прекращается после вьщачи микрооперации Конец работы с выхода 83.2 группы выходов 83 регистра 11 микрокоманд по тактовому импульсу Г . а

Формула изобретения

Устройство для обмена данными между электронно-вычислительной машиной и абонентами, содержащее два мультиплексора, мультиплексор знака, счетчик адреса, постоянную память, регистр микрокоманд, регистр старшего байта, два операционных блока, оперативную память, блок согласования уровней сигналов, блок синхронизации блок формирования адреса, дешифратор группу блоков ввода-вывода, триггер непосредственного доступа, триггер управления обменом, триггер управления, три блока магистральных элементов, три элемента И, причем входы требования обмена, признака управляющего слова и разрешения непосредственного доступа блока формирования ад1)еса подключены к управляющей шине электронно-вычислительной мащины, первый и второй информационные взводы выходы блока согласования уровней сигналов подключены к информационным входам-выходам старшего и младшего байтов первого полуслова электронно-вычислительной машины, третий и четвертый информационные входы-выходы блока согласования уровней сигналов подключены к информационным входам-выходам старшего и младшего байтов второго полуслова электронно- вычислительной машины, выход первого блока магистральных элементов подключен к адресной шине электронно-вычислительной маошны, первая группа информационных выходов регистра микрокоманд, выход триггера непосредственного доступа, выход триггера управления обменом подключен к управляющей шине злектронно-вычислитель 71

ной машины, первые информационные входы и выходы блоков ввода-вывода групп подключены к информационным выходам и входам абонентов г руппы, вход пуска блока синхронизации явля- ется входом пуска устройства, при этом первый и второй информационные входы блока согласования уровней сигналов соединены с информационными входами второго и третьего блоков магистральных элементов соответственно, информационные входы которых соединены с первым информа1щонным входом первого мультиплексора, информационный выход которого соединен с информационным входом счетчика адреса, информационный выход которого соединен с адресным входом постоянной памяти, первый информационный выход которой соединен с разрешаю1а;им входом блока согласования уровней сигналов, пятьм информап юнный вход- выход которого соединен с вторым ин- формационнымИ входами блоков ввода- вывода, с информационным входом ре- гистра старшего байта, с информа- ционным входом-выходом оперативной памяти и с информационными входами и выходами первого и второго операционных блоков, адресные входы, вхо- ды кода операции и входы управления вьщачей которых соединены с соответствующими разрядами второй группы информационных выходов регистра микрокоманд, третья группа информацион- ных выходов которого соединена с группой управляющих входов второго мультиплексора, информационный выход которого соединен с шестым информационным входом-выходом блока согласования уровней сигналов, информационный вход второго мультиплексора соединен с информационным выходом регистра старшего байта, синхровход которого соединен с выходом первого элемента И, первый вход которого соединен с вторым информационным выходом постоянной памяти, третий информационный выход которой соединен с адресным входом операвтивной памя- ти, вход разрешения которой соединен с четвертым информационным выходом постоянной памяти, пятый информационный выход которой соединен с первым входом второго элемента И, вьжод которого соединен с входом записи оперативной памяти, шестой информационный выход постоянной памяти соединен с информационным входом регист23 8

ра микрокоманд, чочнергая грунна информационных ныходом ксугорого с.оеди- нена с т рупцоГ информационных входов дешифратора, группа выходов которого соединена с соответ(;.твуюиц- ми входами разрешения блоков ввода-вывода группы, группа входов кодовых условий ко1 орых соединена с пятой группой информационных выходов регистра микрокоманд, шестая группа информационных выходов которого соединена с входом разрешения блока синхронизации, единичным входом триггера управления, с единичным и нулевым входами триггера непосредственного доступа, с единичным и нулевым входами триггера управления обменом и с группой управляющих входов мультиплексора знака, группа информационных входов которого соединена с выходами знака блоков ввода-вывода группы, выходы требования обслуживания ко орых соединены с группой входов требования обсл живания ёлока формирования адреса, информационный выход которого соединен с вторым информационным входом первого мультиплексора, третий информационный вход которого соединен с седьмым информационным выходом постоянной памяти, восьмой информационный выход которой соединен с входом кодовых условий блока формирования адреса, первый и второй адресные выходы которого соединены с первым и вторым управляющими входами первого мультиплексора соответственно, управляющие входы второго и третьего блоков магистральных элементов и информационный вход триггера управления подключены к шине нулевого потенциала устройства, отличающее- с я тем, что, с целью увеличения быстродействия, в него введены регистр текущего адреса, регистр младшего байта, блок коммутации, счетчик вр еменных интервалов, два элемента И-ИЛИ. триггер признака результата старшего байта, триггер признака результата младшего байта, триггер признака переноса, счетчик начального адреса, девять элементов И, элемент НЕ, причем выход счетчика временных интервалов соединен с синхровходом триггера управления и подключен к входу прерывания электронно-вычислительной машины, при этом вторые информационные выходы блоков ввода вывода группы соединены

39

с группой инф(зрмапионных входов второго мультиплексора и группой информационных входов блока коммутации, первый информационный вход которого соединен с информационным выходом регистра нпадшего байта, информационный вход которого соединен с информационным выходом второго мультиплексора и с первым информационным входом счетчика временных интервалов, второй информационный вход которого соединен с информационным входом- выходом оперативной па мяти, с информационным выходом блока коммутации, с первым и вторым информационными входами счетчика начального адреса, второй и третий информационные входы которого соединены с первым и вторым информационными выходами счетчика начального адреса соответ- ственно и с информационным входом первого блока магистральных элементов, управляющий вход которого, первый вход третьего элемента И, первый и второй синхровходы счетчика начального адреса соединены с седьмой группой информационных выходов регистра микрокоманд, третья группа информационных выходов которого соединена с группой управлякнцих вхо- дов блока коммутации, группа синхро- входов блоков ввода-вывода группы соединена с .первым, вторым и третьим выходами блока синхронизации, первый выход которого соединен с первыми входами четвертого, пятого и шее го- го элементов И, второй выход блока синхронизации соединен с синхровходо регистра микрокоманд с первыми входами седьмого и восьмого элементов И, с вторым входом первого элемента И, выход которого соединен с синхровходом регистра младшего байта, третий выход блока синхронизации соединен с тактовыми входами первого и второго операционных блоков, с вторыми входами второго и третьего элементов И, с первыми входами девятого и десятого элементов И, с первым входом одиннадцатого элемента И, вы- ход которого соединен со счетным входом счетчика временньпс интервалов синхровход которого соединен со вторым входом одиннадцатого элемента И и с единичным входом триггера уп- равления, выход которого соединен с третьим входом одиннадцатого элемента И, третий и четвертый адресные

s

5.

71

5 0 5

2540

выходы блока формирования адреса соединены с вторыми входами пятого и шестого элементов И соответственно, выходы которых соединены с синхровходом и счетным входом счетчика адреса соответственно, информационный выход которого соединен с информационным входом регистра текущего адреса, информационный выход которого соединен с четвертым информационным входом первого мультиплексора, синхровход и разрешающий вход регистра текущего адреса соединены с выходами седьмого и четвертого элементов И соответственно, вторые входы KOTopbiXi соединены с пятым и шестым адресными выходами блока формирования адреса соответственно, входы знака и признака результата которого соединены с выходами мультиплексора знака и первого элемента И-ИПИ соответственно, вторая группа информационных выходов регистра микрокоманд соединена с первым и вторым входами второго элемента И-ИЛИ, второй вход второго элемента И-ИЛИ соединен с первыми входами первого элемента И-ИЛИ, двенадцатого элемента И и с входом элемента НЕ, выход которого соединен с вторыми входами первого элемента И-ИЛИ, восьмого и девятого элементов И и с третьим входом второго элемента И-ШШ, выход которого соединен с входом переноса второго операционного блока, выход переноса которого соединен с входом переноса первого операционного блока, выход переноса которого соединен с вторым входом десятого элемента И, выход которого соединен с единичным входом триггера признака переноса, выход которого соединен с четвертым входом второго элемента И-ИЛИ, выходы признака результата первого и второго операционных блоков соединены с третьим входом девятого элемента И и с вторым входом двенадцатого элемента И, выходы которых соединены с единичными входами соответственно триггера признака результата младшего байта и триггера признака результата старшего байта, нулевые входы которых соединены с нулевым входом триггера признака переноса и с выходом восьмого элемента И, выход триггера признака результата старшего байта соединен с третьим входом первого элемента И-ИЛИ, четвертый и пятый

411277125А2

входы которого соединены с выходом мента И соединен со счетным вло- триггера признака результата мл ад- дом счетчика начального адре- шего . байта , выход третьего эле- са.

Таблица 1.

Сигналы на входах ДШ 171

Источники (входа) сигналов на выходах коммутатора 154

167

Выход регистра 158

167

168

Таблица 4

lpU2.fu

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммный модуль | 1986 |

|

SU1427366A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |