иЕстой ВЫХОД которого соединен с третьим входом блока адресации памя ти, второй и третий выходы которого подключены соответственно к управляющему и второму информационному входам блока памяти.

2,Устройство по п, 1, отличающееся тем, что блок синхронизации передачи содержит два элемента И, два элемента И-НЕ, два триггера, элемент ЙЕ, элемент И-ИЛИ-НЕ и элемент ИЛИ, причем первый вход первого элемента И соедине

с третьим входом блока, второй вход - с первым входом первого элемента И-НЕ, а выход - с первыми вхо дами вторых элемента И и элемента И-НЕ, выход которого является третьим выходом блока, а второй.вход соединен с первым входом элемента И-ИЛИ-НЕ и через элемент НЕ с вторыми входами первого элемента И-НЕ и второго элемента И, выходом и третьим входом подключенногр- соответственно к счетному входу.и нулевому выходу первого триггера, единичный вход которого соединен с выходом первого элемента И-НЕ, а единичный выход - с вторым входом элемента И-ИЛИ-НЕ и первым входом элемента ИЛИ, выход которого является вторым выходом блока, третий и четвертый входы элемента И-ИЛИ-НЕ образуют второй вход блока, а выход соединен с нулевыми входами первого и второго триггеров, третий вход первого элемента И-НЕ соединен с единичным выходом второго триггера, нулевой выход и единичный вход кото.рого являются соответственно первыми выходом и входом блока, второй и третий входы первого элемента И, вход элемента НЕ, четвертый вход первого элемента И-НЕ и второй вход элемента ИЛИ образуют четвёртый вхо блока.

3.Устройство по п, 1, о т л ичающееся тем, что блок адресации памяти содержит два элемента НЕ, два элемента И, три счетчика

и мультиплексор, причем первый вход первого элемента И соединен с вторьа входом блока, второй вход через первый элемент НЕ - с первым выходом первого счетчика, а выход - с первым управляющим входом мультиплек - сора и суммирукядими входами первого и второго счетчиков, второй выход первого счечика соединен через второй элемент НЕ с первым входом второго элемента И, вторым входом соединенного с первым входом блока, а выходом - с вычитающими входами первого и третьего счетчиков, первы выходом блока и вторым управляющим входом мультиплексора, первый и вторбй информационные входы которого

подключены соответственно к выходам второго и третьего счетчиков, а выход является третьим выходом блока, выходы первого и второго элементов И образуют второй выход блока, а третий вход второго элемента И и информационные входы второго и третьего счетчиков образуют третий вход блока

4. Устройство по п. 1 отличающееся тем, что блок управления связью с основной машиной содержит десять триггеров, четыре элемента И, восемь элементов И-НЕ, три элемента И-ИЛИ-НЕ, пять элементов НЕ, два элемента ИЛИ и два элемента задержки, причем выход п-ервого элемента И-НЕ соединен с первым входом первого триггера, выход которого подключен к первым входам второго триггера и первого и второго элементов И, второй вход - к выходувторого триггера, вторым входом соединенного с выходом второго элемента И-НЕ и первыми входами третьего и четвертого триггеров, вторые входы которых подключены к третьему входу второго триггера и первым входам первого элемента ИЛИ и пятого триггера, выход которого соединен с первыми входами шестого триггера, третьего и первого элементов И-НЕ, а второй вход - с первыми входами четвертого, пятого и шестого элементов И-НЕ, вторым входом второго элемента И и выходом шестого триггера, вторым входом подключенного к выходу седьмого элемента И-НЕ, вход которого соединен с выходом первого триггера, второй вход - с вторым входом третьего элемента И-НЕ, третьим входом подключенного к выходу второго триггера, а выходом к второму входу первого элемента И-НЕ, входу первого элемента НЕ и первому входу третьего элемента И, первый вход первого элемента И-ИЛИ-НЕ соединен с П6ФВЫМ входом второго элемента И-НЕ, третьим входом второго элеменkra И и первым входом четвертого элемента И, второй вход.которого подключен к третьему входу четвертого триггера и вторым входам икстого элемента И-НЕ и первого элемента И-ИЛИ-НЕ, третий вход которого соединен с выходом седьмого триггера, первыми входг1ми восьмых триггера и элемента И-НЕ и входом второго элемента НЕ, а выход - с вторым входом восьмого триггера, выходом подключенного к первому входу седьмого триггера, второй вход которого соединен с выходом второго элемента И-ИЛИ-НЕ, первый вход которого подключен к второму входу восьмого элемента И-НЕ, к первым входам второго элемента ИЛИ и третьего элемента И-ИЛИ-НЕ и входу третьего элемента

НЕ, а второй вход - к второму входу второго элемента ИЛИ, и входу чет.вертого элемента НЕ, третий вход шестого элемента И-НЕ соединен с выходом второго элемента ИЛИ, первый и-второй входы.девятого триггера подключены соответственно к выходам шестого и восьмого элементов И-НЕ,

третий вход - к выходу третьего триггера и второму входу четвертого элемента И-НЕ, а выход - к третьему входу третьего триггера и второму входутретьего элемента И-ИЛИ-НЕ, третьим входом соединенного с входом первого элемента задержки и вторым входом второго элемента И-НЕ, выходом с четвертым выходом блока, а четвертым входом с входом второго элемента задержки, вторым выходом блока и выходом второго элемента И, ёыход и третий вход четвертого триггера подключены соответственно к первому входу и выходу десятого триггера, второй и третий входы которого соединены соответственно с выходом пятого и четвертого элементов И-НЕ, выход и второй вход первого элемента ИЛИ соединены соответственно с входом пятого элемента НЕ и выходом четвертого элемента И-НЕ,

третьим входом подключенного к четвертому входу первого элемента И-ИЛИ-НЕ, вторые входы первого и четвертого элементов И, третьи входы первого элемента И-НЕ и вто|5ого Триггера и вторые входы второго и третьего элементов И-НЕ образуют первый вход блока, первый и второй входы второго элемента ИЛИ образуют второй вход блока, третьи входы четвертого и восьмого элементов И-НЕ, четвертый вход uiecToto элемента И-НЕ, третий и четвертый входы второго элемента И-ИЛИ-НЕ-и второй вход третьего элемента -И образуют третий вход блока, выходы первого, третьего и четвертого элементов И, шестого триггера и первого элемента НЕ образуют первый выход блока, выходы третьего и седьмого триггеров, соответствующая шина второго входа бло1ка и выходы второго элемента задержки и третьего и пятого элементов НЕ образуют третий выход блока, выходы седьмого триггера и первого элемента ИЛИ образуют шестой выход блока, выходы десятого триггера, первого элемента задержки, второго и четвертого элементов НЕ . и соответствующая шина второго входа блока образуют пятый выход блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения для вычислительных комплексов | 1983 |

|

SU1104499A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство ввода-вывода | 1976 |

|

SU781803A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Устройство для обмена данными | 1988 |

|

SU1599863A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ МАШИН, содержащее группу блоков усилителей связи с линией, первый буферный регистр данных, информационный вход которого соединен с информационным входом первого регистра команд и информационным входом устройства, а выход через магистраль - с первыми информационными входами блоков усилителей связи с линией группы, первые информационные выходы которых подключены через магистраль к информационному входу второго регистра команд, приоритетные входы и выходы соответственно к группе выходов и входов регистра приоритетов, а первые управляющие входы и выходы через магистраль - соответственно к первому выходу и входу блока управления линиями связи, вторые вход и выход которого соединены соответственно с управл5«о1дим входом и выходом второго регистра команд, первые вход и выход блока управления связью с основной машиной соединены соответственно с управлякидоми входотл и выходом устройства, вторые вьххоя и вход - соответственно с управлятвим входом и выходом -первого регистра команд, третьи вход и выход - соответственно с третьими выходом и входом блока управления линиями связи, а четвертый выход - с управляющим входом первого буферного регистра данных, -четвертые вход и выход блока управления линиями связи соединены соответственно с выходом и входом регистра приоритетов, а пятый выход с управляющим входом второго буферного регистра данных, выход которого является информационным выходом устройства, вторые информационные входы и выходы блоков усилителей связи с линией группы являются информационными группами входов и выходов устройства, а вторые управляющие входы и выходы блоков усилителей свя § ;3и с линией группы являются соответствующими управляющими группами вхо0 дов и выходов устройства, о т л ичающееся тем, что, с целью расширения области применения устройства, в него введены блок памяти, блок адресации памяти и блок синхронизации передачи, причем первый информационный вход блока памяти соединен через магистраль с первьп«ш информационны ж выходами блоков усилителей связи с линией группы, а выход с информационным входом второго буферного регистра, первые вход и выход блока синхронизации передачи подключены соответственно к первым входу и выходу блока адресации памяти, вторые вход и выход - соответственно к второму выходу блока управления линиями связи и к выходу синхронизации устройства, а третий выход через магистраль - к первым управляющим входам блоков усилителей связи линии группы, первые управляющие выходы которых соединены с вторым входом блока адресации памяти и третьим входом блока синхронизации передачи, четвертым входом под-: ключенного к пятому выходу блока управления связью с основной машиной,

Изобретение относится к вычислительным машинам и может найти применение в многомашинных вычислительных комплексах и сетях ЭВМ.

Известны устройства для содержаНИН вычислительных машин, содержащие узел синхронизации, два узла фиксации состояния, два информационных регистра, регистр состояния, регистр команд, кoм Iyтaтop, узел готовности и узлы формирователей приемников Щ

Недостаток данных устройств со- стоит в ограниченной области применения, так как они не позволяют сопрягать удаленные друг от друга ЭВМ,

Наиболее близким к предлагаемому по технической сущности являетсй устройство для сопряжения вычислительных машин, содержащее два буфер-ных регистра данных, два регистра команд, регистр приоритетов, блок ;управления с основной-маЕциной, соединенный двухсторонними связями с входом-выходом устройства, первым регистром команд и блоком управлеНИН линиями связи, соединенного двухсторонними связями с регистром при оритетов, вторым регистром команд

и через магистраль с группой блоков усилителей связи с линией, инфомационные входы и выходы которых соединены соответственно через магистраль с выходом первого и входом второго буферных регистров, приоритетный вход-выход - с входом-выходом регистра приоритетов, информационные входы регистров команд соединены соответственно с входами первого и второго буферных регистров , управляющие входы которых подключены к выходам блока управления связью с основной вычислительной машиной и блоком управления линиями связи 2 .

Недостатком известного устройства является ограниченная область применения.

Цель изобретения - расширение рбласти применения устройства.

Поставленная цель достигается тем, что в устройство, содержащее группу блоков усилителей связи с линией, первый буферный регистр данных, информационнь й вход которого соединен, с информационным входом первого регистра команд и информационным входом устройства, а выход через магистраль - с первыми информационными входами блоков усилителей связи с линией группы, первые информационные выходы которых подключены через магистраль к информационному входу второго регистра команд, приоритетные входы и выходы соответственно к группе выходов и входов регистра приоритетов, а первые управляющие входы и выходы через магистраль - соответственно к первому выходу и входу блока уп.равления линиями связи, вторые вход и выход которого соединены соответственно с управляющим Входом и выхйдом второго регистра команд, первые вход и выход блока управления связью с основной машиной соединены соответственно, с управляющими входом и выходом устройства, вторые выход -и вход - соответственнос управляющими входом и выходом первого регистра команд, -треть - вход и выход - соответственно с третьими выходом и входом блока управления линиями связи,. а четве этый выход - с управляющим входом первого буферного регистра данных, четвертые вход и выход блока управления линиями связи соединены соответственно с выходом и входом регистра приоритетов, а пятый выход - с управляющим входом второго буферного регистра данных, выход которого является информационным выходом устройства, вторые информационные входы и выходы блоков усилителей йвязи с линией: группы являются информационными группами входов и выходов устройства, а вторь:е управляющие входы и выходы блоков усилителей связи с линией группы являются соответствующими управляющими группами входов и выходов устройства, введены блок памяти, блок адресации памяти и блок синхронизации передачи, причен первыйинформационный вход блока памяти соединен через магистраль с первыми информационными выходами блоков усилителей связи с линией группы, а выход - с информационным входом второго буферного регистра, первые вход и выход блока синхронизации передачи подключены соответственно к первому входу и выходу блока адресации памяти, .вторые вход и выход - соответственно к второму выходу блока управления линиями связи и к выходу синхронизации устройства, а третий выход через магистраль - к первым управляющим входам блоков усилителей связи линии группы, первые управляющие выходы которых соединены с вторым входом блока адресации памяти и третьим входом

блока синхронизации передачи, четвертым входом подключенного к пятому выходу Тлока управления связью с основной машиной, шестой выход которого соединен с третьим входом 5 блока адресации памяти, второй и - третий выходы которого подключены соответственно к управляющему и второму информационному входам блока памяти.

0 Блок синхронизации передачи содержит два элемента И, два элемента И-НЕ, два триггера, элемент НЕ, элемент Й-ИЛИ-НЕ и элемент ИЛИ, причем первый вход первого элемента И

5 соединен с третьим входом блока, второй вход - с первым входом первох-о элемента И-НЕ, а выход - с первыми входами вторых элемента И и элемента И-НЕ, выход которого явQ ляется третьим выходом блока, а второй вход соединен с первым входом элемента И-ИЛИ-НЕ и через элемент НЕ с вторыми входами первого элемента И-НЕ и второго элемента И, выходом

5 и третьим входом подключенного соответственно к счетному входу и нулевому выходу первого триггера, еди- . ничный вход которого соединен с выходом первого элемента И-НЕ, а единичный выход с вторым входом эле мента И-ИЛИ-НЕ и первым входом элемента ИЛИ, выход которого является вторым выходом блока, третий и четвертый входы элемента И-ИЛИ-НЕ образуют второй вход блока, а выход

5 соединен с нулевыми входами первого и второго триггеров, третий вход первого элемента И-НЕ соединен с единичным выходом второго триггера, нулевой выход и единичный вход кото0 рого язвляются соответственно первыми выходом и входом блока, второй и третий входы первого элемента И, вход элемента НЕ, четвертый вход первого элемента И-НЕ и второй вход

5 элемента ИЛИ образуют четвертый вход блока.

Ёлок адресации памяти содержит два элемента НЕ, два элемента И, три счетчика и мультиплексор, причем первый вход первого элемента И соединен с вторым входом блока, второй вход через первый элемент НЕ - с первым выходом первого счетчика, а выход - с первым управля5 ющим входом мультиплексора и суммирующими входами первого и второго счетчиков, второй выход первого счетчика соединен через второй элемент НЕ с первым входом второго элемен

0 та И, вторым входом соединенного с первым входом блока, а выходом :с вычитающими входами первого и третьего счетчиков, первым выходом блока и вторым управляющим входом

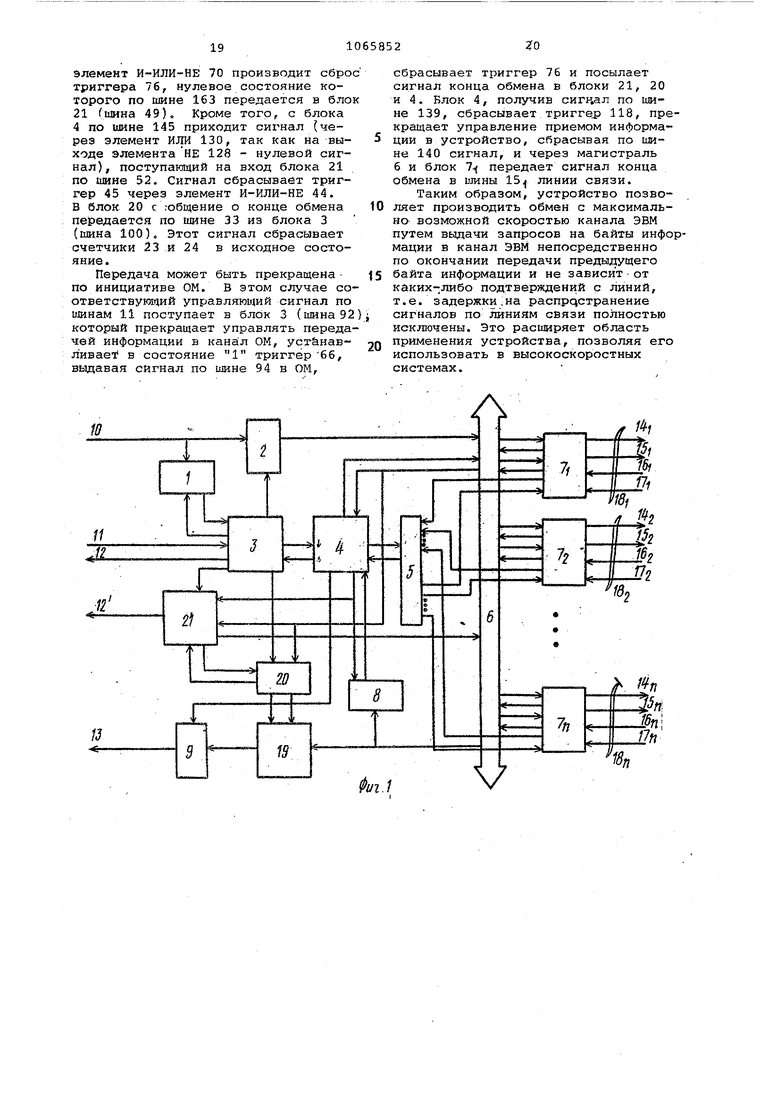

5 мультиплексора, первый и второй информационные входы которого подключены соответственно невыходам второ го и третьего счетчиков, а выход является третьим выходом блока, вы ходы первого и второго элементов И образуют второй выход блока, а тре .тий вход второго элемента И и инфо мационные входы второго и третьего счетчиков образуют третий вход бло I Блок управления связью с основной машиной содержит десять триггеров, четыре элемента И, восемь элементов И-НЕ, три элемента И-ИЛИ-НЕ пять элементов НЕ, два элемента ИЛИ и два элемента задержки, причем выход первого элемента И-НЕ соединен с первым входом первого тржггера, выход которого подключен к первым входам второго триггера и первого и второго элементов И, второй вход - к выходу второго триггера, вторым входом соединенного с выходом второго элемента И-НЕ и первыми входами третьего и четвертого триггеров, вторые входы которлх под ключены к третьему входу второго триггера и первым входам первого элементаИЛИ и пятого триггера, выход которого соединен с первыми входс1ми шестого триггера, третьего и первого элементов И-НЕ, а второй вход - с первыми входами четвертоГО-, пятого и икстого элементов И-НЕ вторым входом второго элемента И и выходом шестого триггера, вторым входом подключенного к выходу седьмого элемента И-НБ, первый вход которого соединен с выходом первого триггера, второй вход - с вторым входом третьего элемента И-НЕ, трет им входом подключенного к выходу второго триггера, а выходом - к вто рому входу первого элемента И-НЕ, входу первого элемента НЕ и первому входу третьего элемента И, первый вход первого элемента И-ИЛИ-НЕ соединен с первым входом второго элемента И-НЕ, вторым входом пятого элемента И-НЕ, третьи1м входом второго элемента И и первым входом четвертого элемента И, второй вход которого.подключен к третьему входу четвертого триггера и вторым входам шестого элемента И-НЕ и первого элемента И-ИЛИ-НЕ, третий вход которого соединен с выходом седьмого триггера, первыми входами восьмых триггера и элемента И-НЕ и входом второго элемента НЕ, а выход - с вт .рым входом восьмого триггера, выходом подключенного к первому входу седьмого триггера, второй вход, кото рого соединен с .выходом второго элемента И-ИЛИ-НЕ, первый вход кото рого подключен к второму входу вось мого элемента И-НЕ, к первым входам второго элемента ИЛИ и третьего эле мента И-ИЛИ-НЕ и входу TpeTfjero эле мента НЕ, а второй вход - к второму входу второго Элемента ИЛИ и входу четвертого элемента НЕ, третий вход шестого элемента И-НЕ соединен с выходом второго элемента ИЛИ, первый и второй входы девятого триггера подключены соответственно к выходам шестого и восьмого элементов И-НЕ, третий вход - к выходу третьего триггера и второму входу четвертого элемента И-НЕ, а выход- к третьему входу третьего триггера и второму входу третьего элемента И-ИЛИ-НЕ, третьим входом соединенного с входом первого элемента задержки и вторым входом второго элемента И-НЕ, выходом с четвертым выходом блока, а четвертым входом с входом второго элемента задержки, вторым выходом блока и выходом второго элемента И, выход и третий вход четвертого триггера подключены .соответственно к первому входу и выходу десятого триггера, второй и третий входы которого соединены соответственно с выходами пятого и четвертого элементов И-НЕ, выход и второй вход первого элемента ИЛИ соединены соответственно с входом пятого элемента НЕ и выходом четвертого элемента И-НЕ, третьим входом подключенного к четвертому входу первого элемента И-ИЛИ-НЕ, вторые входы первого и четвертого элементов И, третьи входы первого элемента И-НЕ и второго триггера и вторые входы второго и третьего элементов И-НВ образуют первый вход блока, первый и второй входы второго элемента ИЛИ образуют второй вход блока, третьи входы четвертого и восьмого элементов И-НЕ, четвертый вход шестого элемента И-НЕ, третий и четвертый входы второго элемента И-ИЛИ-НЕ и второй вход третьего элемента И образуют третий вход блока, выходы первого, третьего и четвертого элементов И, шестого триггера и первого элемента НЕ образуют первый выход блока, выходы третьего и седьмого триггеров, соответствующая шина второго входа блока и выходы второго элемента задержки и тр етьего и пятого элементов НЕ образуют третий выход блока, выходы седьмого триггера и первого элемента ИЛИ образуют шестой выход блока, выходы десятого триггера, первого элемента задержки, второго и четвертого элементов НЕ и соответствующая шина второго входа блока образуют Пятый выход блока. На фиг. 1 представлена блок-схема устройства; на фиг. 2-5 - функциональные, схемы блоков адресации памяти, синхронизации передачи, уп-:

равления связью с основной машиной управления линиями связи.

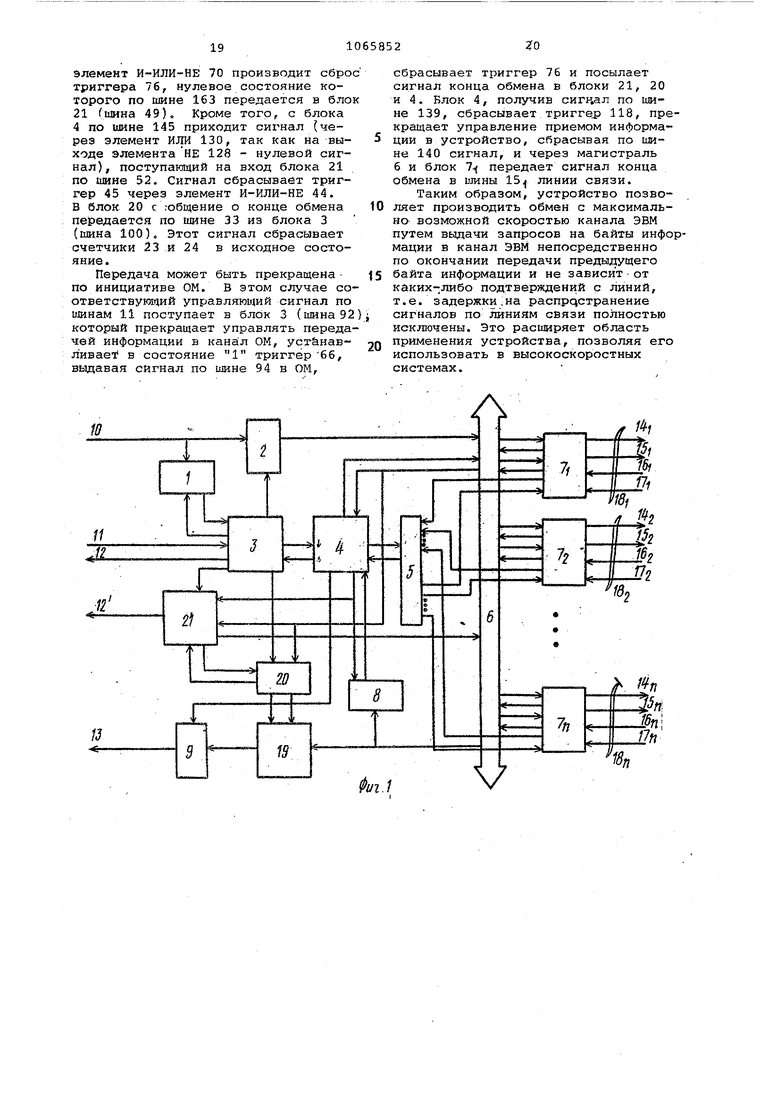

Устройство (фиг. 1) содержит первый регистр 1 команд, первый буферный регистр 2 данных, блок 3 управления связью с основной машиной, блока 4 управления линиями связи, регистр 5 приоритетов, магистраль 6 устройства, блоки 7 усилителей связи с линией группы, второй регистр команд, второй буферный регистр.9 данных, шины 10 информационного входа устройства, шины 11 и 12 - .управлянхшх входа и выхода устройства, ядана 12 выхода синхронизации устройства, шины 13 информационного вы хода устройства, шины 14 группы информационных выходов устройства, шины 15 группы управляющих выходов устройства, шины 16 группы информационных входов устройства, шины 17 группы управляющих входов устройства, шины 18 связи устройства с отдельным каналом связи, блок19 памяти, блок 20 адресации памяти и блок 21 синхронизации передачи.

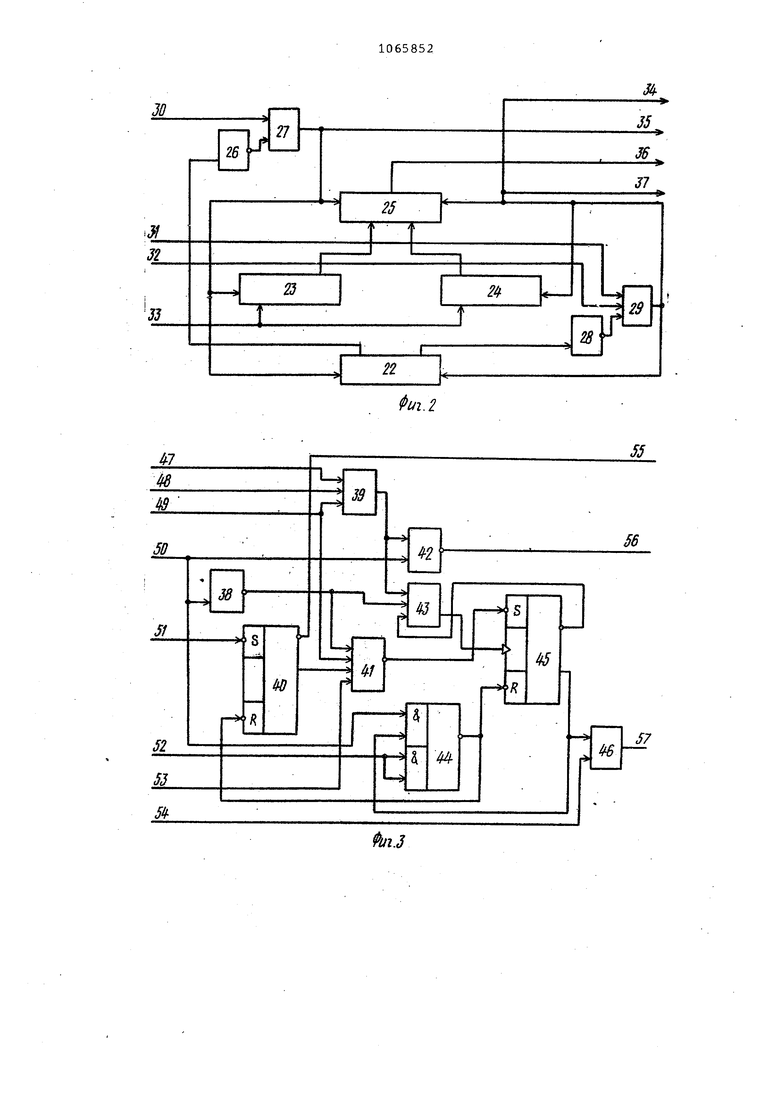

BJIOK 20 адресации памяти (фиг. 2) содержит счетчики 22-24, мультиплексор 25, первые элементы НЕ 26 и И 27 вторые элементы НЕ 28 и И 29, шину 30 второго входа, шину 31 третьего входа, шину 32 Первого входа и шину 33 третьего входа блока, шины 34 и 35 второго выхода, шину 36 третьего выхода и шину 37 первого выхода блока.

Блок 21 синхронизации передачи (фиг. 3) содержит элемент НЕ 38, первые элемент- И 39, триггер 40 и элемент И-НЕ 41, вторые элемеь гы И-НЕ 42 и элемент И 43, элемент И-ИЛИ-НЕ 44, второй триггер 45 и элемент. ИЛИ 46, шину 47 чет вертого входа,, шину 48 третьего входа, шины 49 и 50 четвертого вхо-; да, шины 51 и 52 первого и второго входов и шины 53 и 54 четвертого входа блока, шины 55-57 первого, третьего и второго выходов блока.

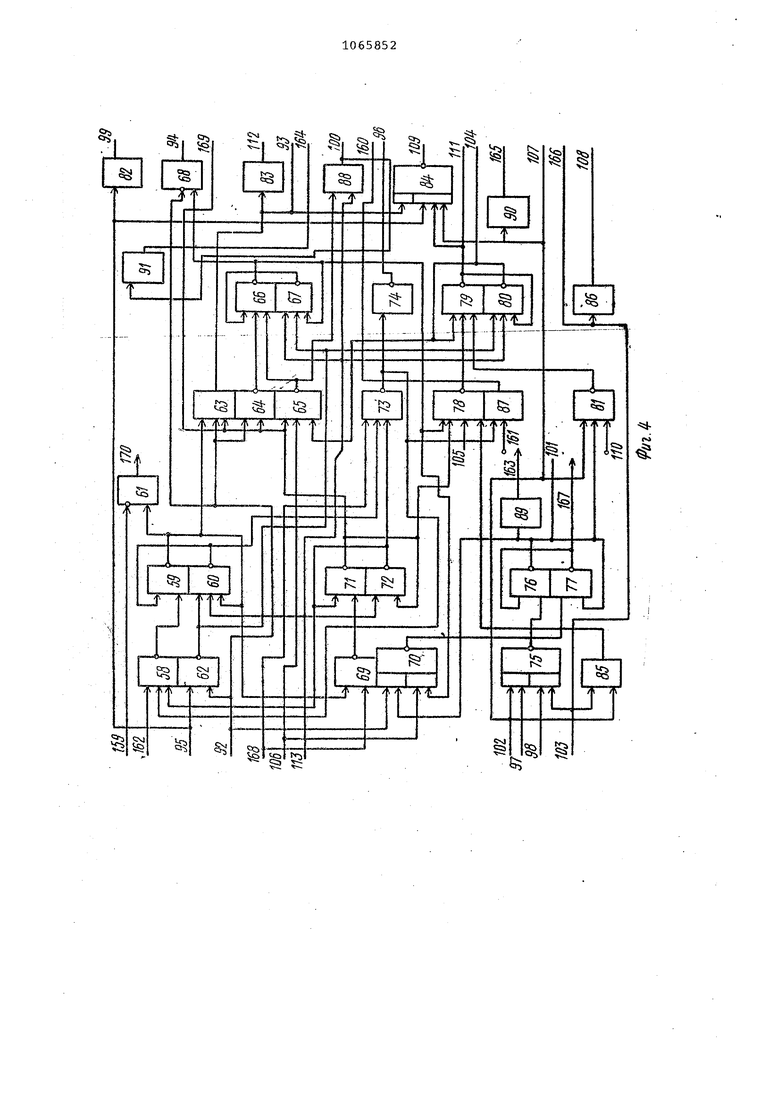

Блок 3 управления связью с основной машиной (фиг. 4) содержит первый элемент И-НЕ 58, первый и второй триггеры 59 и 60, первый элемент И 61, вторые элементы И-НЕ 62 и И 63, пятый и четвертый элементы И-НЕ 64 и 65, десятый и четвертый триггеры 66 и 67, четвертый эл(змент И 68, седьмой элемент И-НЕ 69, первый элемент И-ИЛИ-НЕ 70, шестой и пятый триггеры 71 и 72, третий элемент И-НЕ 73, первый элемент НЕ 74, второй элемент И-ИЛИ-НЕ 75 седь мой и восьмой триггеры 76 и 77, шестой элемент И-НЕ 78, девятый и третий триггеры 79 и 80, восьмой элемент И-НЕ 81, первый и второй элементы 82 и 83 задержки, третий элемент И-ИЛИ-НБ 84, второй элемент ИЛ 85, четвертый элемент НЕ 86, третий элемент И 87, первый элемент ИЛИ 88 второй, третий и пятый элементы НЕ 89-91, шину 92 первого входа, шину 93 второго выхода, шину 94 первого выхода, шину 95 первого входа, шину 96 первого выхода, шины 97 и 98 третьего входа, шину 99 пятого выхода, шины 100 и 101 шестого выхода шины 102 и 103 второго выхода, шину 104 третьего выхода, шины 105 и 106 третьего входа, шины 107 и 108 пятого выхода, шину 109 четвертого выхода, шину 110 третьего выхода, шину 111 пятого выхода, шину 112 третьего выхода, шину 11.3 первого выхода.

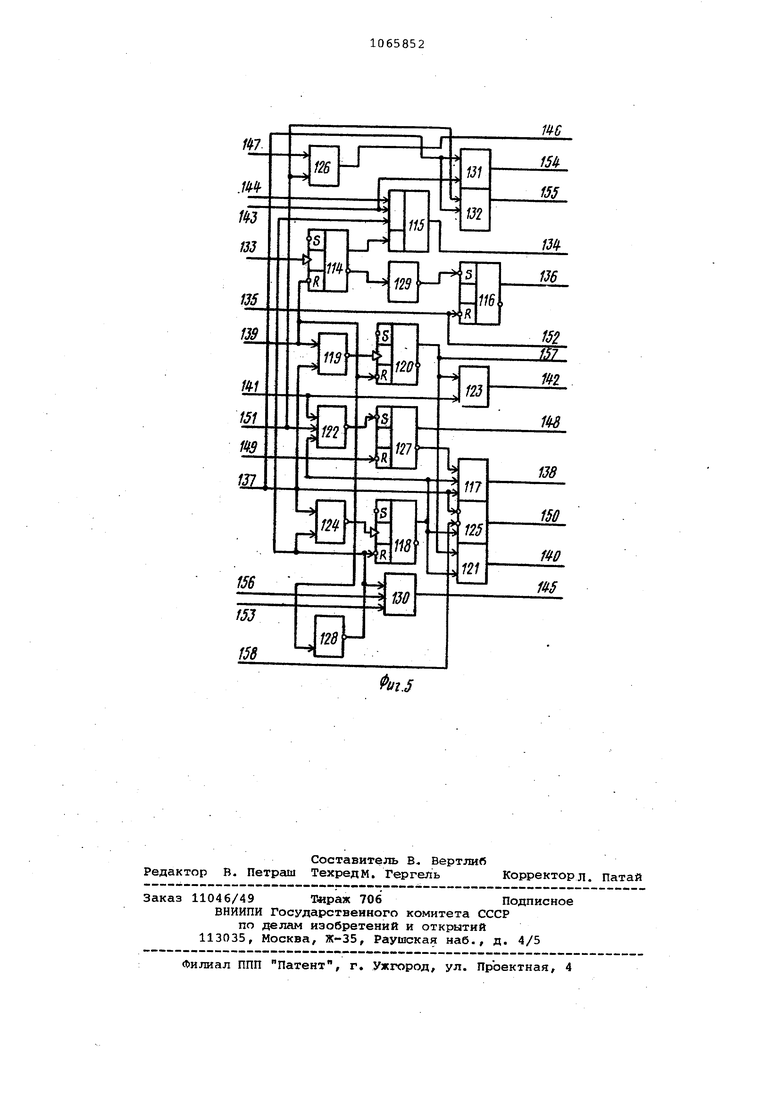

Блок 4 управления линиями связи (фиг. 5) содержит первый триггер 114 элемент И-ИЛИ 115, второй триггер 116, первый элемент И 117, третий триггер 118, первый элемент И-НЕ 119 четвертый триггер 120, первый элемент ИЛИ 121, вторые элементы И-НЕ 122 и И 123, третий элемент И-НЕ 124, третий и четвертые элементы ,И 125 и 126, пятый триггер 127, первый и второй элементы НЕ 128 и 129, второй элемент ИЛИ 130, пятый и шестой элементы И 131 и 132, шину 133 третьего входа, шину 134 четвертого выхода, шину 135 первого входа, шину 136 первого выхода, шину 137 четвертого входа, гиину 138 первого выхода, кЯну 139 третьего входа, шину 140 первого выхода, шину 141 первого входа, шину 142 второго выхода, шины 143 и 144 второго и третьего входов, шины 145 и 146 второго.и пятого выходов, шину 147 третьего входа, шину 148 третьего выхода;, шину 149 третьего входа, шину 150 третьего выхода, шину 151 второго входа, шину 152 третьего выхода, шину 153 первого входа, шины 154 и 155 третьего выхода, шину 156 третьего входа, Ш1 ну 157 третьего выхода и шину 158 первого входа.

Кроме того, на фиг. 4 дополнительно обоэначе ны следующие шины блока 3: шины 159 и 160 первых входа и выхода, шины 161 и 162 третьего и первого входов, шина 163 пятого выхода, шины 164-167 третьего выхода, шина 1§8 первого входа и шины 169 и 170 первого выхода блока

Регистр 1 команд предназначен для расшифровки и хранения команды, поступившей из основно.: магиины (ОМ); в соответствии с принятой командой он задает режим работы устройства.

Буферный регистр 2 данных предназначен для буферизации (временного Х|э анения) кодов команд и данных,

которое необходимо передать из ОМ в одну из линий связи

, Блок 3 управления связью с ОМ принимает, интерпретирует и формирует управляющие сигналы ОМ, а также управляет работой регистра 1 команд и буферного регистра 2 данных.

Блок 4 управления линиями связи служит для интерпретации и формирования управляющих сигналов линий связи, а также управляет работой регистра 8 команд и буферного регисра 9 данных.

Регистр 5 приоритетов предназначен для обеспечения коммутации основной машины с одной из линий связ в-соответствии с принятыми в устройстве приоритетами.

Внутренняя магистраль устройства предназначена для передачи к любому из блоков: усилителей связи с информации из буферного регистра 2 данных и управляющих сиг налов из блока 4 управления линиями связи и из блока 21 синхронизации передачи, а также для передачи от любого из блоков 7 усилителей связи с линией информации в регистр 8 команд и в блоке 19 памяти и управляющих сигналов в блок 4 управления линиями связи и в блок 21 сиихронизации передачи.

Блоки 7 усилителей связи с линией предназначены для формирования (усиления) информационных и управляющих сигналов, передаваемых в ли« НИИ связи и принимаемых из линий связи по шинам 18.

Регистр 8 команд предназначен для расшифровки и хранения команды, поступившей по шинам 18 из любой линии связи; в соответствии с принятой командой он задает режим работы устройства.

Буферный регистр 9 данных предназначен для буферизации (временного хранения) кодов команд и данных, которые необходимо передать в основную машину.

Блок 19 памяти предназначен для хранения данных, поступивших из линий связи.

Блок 20 адресации памяти служит для выработки адреса ячейки памяти, в которую должна быть произведена запись информации, поступившей из линий связи, или из которой должно быть осуществлено считывание информации в основную машину, а также управляющих сигналов записи или считывания.

Блок 21 синхронизации передачи формирует управляющие сигналы, необходимые для реализации синхронной передачи.

По шинам передаются следукнцие сигналы: шины 30 и 141 - управляющие

сигналы, поступающие в устройство по шинам 17 при выдаче из линий связи и сопровождающие байт информации, передаваемый по ищнам 16; 111ины 31 и 101 - сигналы, свидетельствующие о том, что процедура установления связи между ОМ и какой-либо линией связи завершена и может быть начата передача данных; шины 32 и 55 - сигнал о том, что очередной байт данных из линии связи в устройство сопряжения еще не поступил) шины 33 и 100 сигнал сброса счетчиков.23 и 24 блока 20, сообщающий о выполнении уст- . ройством сопряжения любого вида сброса, а также сброса по окончании обмена данными; шина 34 -сигнал, управляющий считыванием очередного байта информации из блока 19 памяти, шина 35 - сигнал, управляющий записью очередного байта информации в блок 19 памяти; шина 36 - сигнал, содержащий адрес ячейки памяти блока 19; шины 37 и 51 - сигнал установки триггера 40 при поступлении рчередного байта данных из линии связи, шины 47 и 107 - сигнал о том, что ОМ вьщала команду Запись (передача .1); шины 48 и 158 - сигнал, поступающий от линий связи и говорящий о готовности абонента к приему (СП1-И); шины 49 и 163 - сигнал о том, что процедура установления связи между ОМ и какой-либо линией связи завершена и может быть начата передача данных; шины 50 и 99 задержанный сигнал Информация от канала, шины 52 и 145. - сигнал, сообщающий о выполнении устройством любого вида сброса; шины 53 и 108 сигнал, свидетельствующий о том, что ОМ выдала команду Читать ; шины 54 и 111 - сигнал Информация от абонента, вырабатываемый блоком 3 в режиме работы устройства без синхронизации передачи; шина 56 управляющий сигнал, сопровождающий выдаваемый в линию байт информации; шина 57 - сигнал Информация от абонента } шина 159 - сигнал Адрес от канала, поступающий из ОМ по шинам 11; шина 162 - сигнал Адрес опознан, поступающий по шинам 11; шина 168 - сигнал Выборка от канала, поступающий по шинам 11 из ОМ, шина 169 - сигнал Работа абонента, поступакмций в ОМ; шина 170 - сигнал Адрес абонента, поступающий в ОМ по шинам 12; шина 92 - сигнал Управление от канала, поступающий из ОМ шина 93 - сигнал занесения в регистр команд; шина 94 - сигнал Управление от абонента, выдаваемый в ОМ; шина 95 - сигнал Информация от канала, поступающий из ОМ, шина 96 - сигнал, поступающий в ОМ в случае, если устройство не опознало свой адрес; шины 97 и 154 сигнал Прием шина 98 и 155 сигнал Передача шина 102 - сигнал Записать шина 103 - сигнал Чтение 1, шины 104 и 149 - сигнал Информация от абонента ИНФ-А (обратная полярность); шины 105 и 148 сигнал запроса на байт информации; шины 106 и 150 - сигнал Конец обмена ; шина 109 - сигнал занесения информации в регистр 1 данных; пины 110 и 152 - сигнал запроса на байт информации; шины 112 и 133 - сигнал занесения в регистр 1 команд, шина 113 - сигнал Сброс общий, поступающий из ОМ по шинам 11; шина 134 сигнал запроса на передачу устройством ГИ-И; шина 135 - Запрос на байт информации (ЗП-И), шина 136 стробирующий сигнал, сопровождающий байт информации; шина 137 - запроса на передачу со стороны лиНИИ; шина 138 - сигнал запроса на байт информации (ЗП-П) шины .139 и 167 - сигнал нулевое состояние триггера 77 блока 3, определяющего начало обменаj шина 140 - сигнал, внщаваемый в ответ на запрос на начало передачи, приходящий с линий связи (СП1-П); шина 142 - сигнал Прием команды, по которому происходит занесение кода команды в регистр 8 команду шина 143 - код команды Прием шины 144 и 165 команда Передача шина 146 прием РД2 - сигнал, по которому производится занесение данных в буферный регистр 9- данных, шины 147 и 166 - сигнал Прием 1 - команда в ОМ; шины 156 и 164 - сигнал общего сброса или прекращения передачи; шины 157 и 161 - сигнал, снимаемый с единичного выхода триггера 120 блока 4 Приме команды шина 160сигнал запроса на установление связи с ОМ по инициативе линий связи (Запрос ТрВ-А); шина 153 - сигнал общей готовности линий связи, шина 151 - сигнал Передача 2 (код команды Запись),,

Устройство работает следующим

образом.

Обмен информацией осуществляется между каналом основной ЭВМ (не пока зан) и одной из линий связи. Вводя последовательность начальной выборки (НВ), канал на шинах 10 выставляет адрес устройства в сопровождении сигнала идентификации, который поступает из канала ОМ по шине 159 в блок 3. При опознавании своего адреса на вход элемента И-НЕ 58 приходит сигнал по шине 162 и, если устройство не было подключено К каналу (триггер 72 находится в нулево состоянии) и опознало себя (на выходе элемента И-НЕ 73 сигнал имеет единичныйуровень), то триггер 59 переходит в единичное состояние.

После прихода из канала ОМ сигнала по шине 168 происходит переход в единичное состояние триггера 71 через элемент И-НЕ 69 (триггер 59 находится в состоянии 1) и в канал ОМ выдается сигнал по -мне 169. В ответ на это канал ОМ сбрасывает сигнал на шине 159, что позволяет передавать в канал ОМ через элемент И 61 по шине 170 единичное состояни триггера 59. Получив сигнал по шине 170, канал вьщает по шине 92 сигнал, при помощи которого на выходе элемента И 63 формируется сигнал по шине 93 (триггеры 59 и 71 находятся в 1), поступающий на регистр 1 и являющийся стробом для занесения кода команды по цинам 10 из ОМ. По сигналу на шине 92 производится сброс триггера 60 через элемент И-НЕ 62, а также установка в единичное состояние через элемент И-НЕ 64 триггера 66. Однако выдача в канал этого сигнала не производится до тех пор, пока канал не сбросит сиг нал на. шине 92. После сброса этого сигнала по шине 94 (через элемент И 68) в канал ОМ передается сигнал, а затем при поступлении сигнала по шине 95 производится сброс триггера 67 через элемент И-НЕ 62. Проце-дура НВ заканчивается сбросом каналом сигнала на шине 95.

Если при выполнении процедуры НВ устройство не опознало свой адрес (триггеры 60 и 72 находятся в О), то ПОЛ5ГЧИВ сигнал по иине 168, оно выдает в канал ОМ сигнал через элементы И-НЕ 73 и НЕ 74 по шине 96. В режиме передачи информации из основной машины в одну из линий связи когда в оперативной памяти ОМ имеется массив информации, подготовленной для передачи, ОМ вьщает команду Записать. Полученная из канала ОМ по шинам 10 выдачи в сопровождении соответствующих управляющих сигналов по шинам 11 выдачи команда Записать заносится в регистр 1 команд для задания режима работы устройства и в буферный регистр 2 для передачи кода команд в .шины выбранной линии связи, например шины 18. В результате дешифрации команд сигналы режима работ из блока 1 передаются в блок 3 (шины 102 - передача - для команды Записать и шины 103 прием - для команды Читать). Блок 3 задает режим работы всего устройства, выдавая в блок 4 сиглал по шинам 165 и 144 при передаче, информа ции или по шинам 166 ч 147 при приеме и;нформацни.

Код команды Записать из буферного регистра 2 через магистраль 6 устройства и включенный регистром 5 приоритетов блок 7 передается в шины 18{ линии связи.

Передача происходит следующим образом. Блок 4, получив по шине 133 из блока 3 задержанный сигнал, устанавливйет в единичное состояние триггер 114, который через элемент И-ИЛИ 115 формирует на шине 134 за- 5 прос на установление связи с линией связи. Этот запрос через магистраль б и включенный регистром 5 блок 7 передается в шины 18. Если линия связи готовак работе, то она от- 10 вечает сигналом, который через блок 7 магистраль б поступает в блок 4 по шине 135 и устанавливает триггер 116 в единичное состояние, что приводит к выдаче из блока 4 по шине 5

136сигнала. Этот сигнал аналогичным образом чере-з магистраль 6, блок 7| передается в шины.18, сопровождая передаваемый из буферного регистра 2 код команды.20

Нормальное выполнение процедуры передачи даннвах во.зможно лишь при соответствии команд, поступивших с одной стороны из канала ОМ и с другой т из шины 18 соответствующей линии связи.

Встречная команда Читать поступает по шинам 184 через включенный блок 7 , магистраль 6 в регистр 8 команд.

Процедура приема встречного кода команды осуществляется под управлением блока 4, .который принимает и посылает соответствующие сигналы через магистраль б в блок 7 с шин 35

17 и по шинам 15 линии связи. Запросом на передачу кода команды от. абонента является сигнал, который

поступает из блока 5 по -шине 137. При получении этого сигнала в блоке 40 4 вырабатывается сигнал на шине 138, который является запросом на байт

команды и передается через блоки 6 и 7 .в шины 15|. По сигналу на шине

137устанавливается в 1 триггер лс 120 через элемент И-НЕ 119, так как обмена еще нет и сигнал, приходящий

по шине 139 из блока 3, находится в единице. Установка триггера 120 в единичное состояние приводит к выдаче сигнала по шине 140 через элемент ИЛИ 121. Сигнал по шине 140 через блок 6, блок 7 передается в линию связи. На это линия отвечает выдачей сигнала в шину 141, который ерез блок 7 и магистраль 6 передается в блок 4 и, поступая на элемент И 123, вырабатывает сигнал При ем команды 2, который по шине 142 ередается в блок 8, разрешая прием кода команды. После дешифрации кода 60 в блоке 8 вырабатывается сигнал Прим 2 (шина 143), если из линий свяи была получена команда Читать, ли сигнал Передача 2 (шина 151), сли из линии связи была получена 5

команда Записать. Сигналы по шинам 143 или 151 при условии готовности устройства к обмену (на шине 137 единичный сигнал) переформируются элементами И 131 или 132 в сигналы Прием 2 (шина 154) или Передача 2 (шина 155) и поступают по шинам 97 и 98 в блок 3, в котором по признаку совпадения кодов команд на элементе И-ИЛИ-НЕ 75 устанавливается в 1 триггер 76. Сигнал по шинам 167 и 139 передается в блок 4, сбрасывая там триггер 120, инвертируется элементом НЕ 128-и устанавливает в 1 триггер 118, определяющий режим обмена данными.

После процедуры установления связи (обмена кодами команд) устройство переходит непосредственно к передаче данных. Приемом информации из канала ОМ в устройство по шинам 10 управляет блок 3 и блок 21 синхронизации передачи. Сама информаци с шин 10 поступает в первыйбуферны регистр 2.

Пе-)едачей информации из-устройства в шийы 18| управляет блок 4 и блок 21. Информация из буферного регистра 2 через магистраль 6 и блок 7 поступает на шины 14.

Передача данных начинается непосредственно после процедуры установления связи (обмена кодами команд). После обмена кодами команд при их соответствии в блоке 3 устанавливается в единичное состояние триггер 76, единичное состояние которого -передается по шинам 163 и 49 в блок 21, разрешая начать передачу данных. Передача данных начинается с выдачи блоком 4 по шине 134, через магистраль 6, блок 7 , по шинам 15 запроса на передачу ГИ-И. Этот запрос выдается с выхода элемента И-ИЛИ 115 и вырабатывается при условии наличия единичных сигналов на шинах 143 и 144, так как на шине 139 находится сигнал логического О. Полученный от абонента по шинам 17 ответный сигнал, говорящий о готовности абонента к приему, через блок 7vj и магистраль 6 поступает по шине 48 в блок 21, подготавливая начало передачи данных. В блок 21 также поступает команда Передача 1 (шина 47) из блока 3 (шина 107)о По шине 135 ответный сигнал, полученный из линий связи в блок 4, передается по шинам 152 и 110 на вход блока 3 и устанавливает в 1 триггер 79 через элемент И-НЕ 81. Сигнал по шинам 111 из блока 3 поступает на вход блока 21 (шина 54) и через элемент ИЛИ 46 выдается в канал ОМ (-шина 57), являясь запросом на первый байт. ОМ отвечает сигналом на шине 95, который

выдается из блока 3 (цшна 99) в блок 21 (шина 50), в совокупности с сигналами по шинам 47 (107), 48 и 49 (1бЗ)„ .

Блок 21 вырабатывает стробирующи сигнална шине 56, который через ма гистраль б и блок 7 передается по шинам 15j и сопровождает байт информации, передаваемый из буферного регистра 2 через магистраль 6 и блок 7 по шинам 14j| в линию связи. Эта же совокупность сигналов на шинах 47-50 используется для установки в единичное состояние триггера 4 блока 21, вырабатывающего управляющий сигнал по 57, который выдается по шинам 12 в ОМ. Сигнал на шине 57 формируется либо по единичному состоянию Триггера 45, либо по сигналу в шине 54, сформированному в блоке 3.

Триггер 45 сбрасывается при получении из блока 3 (шина 99) сигнала по шине 50 или при выполнеШШ устройством любого вида сброса. Сообщение о выполнении устройством сбро са (шина 52) а блок 21 выдается блоком 4. Блок 4 сигнал сброса вы -дает по шине 145 после формирования его по.сигналу прекращения передачи или общему сбросу, поступающему по шине 156 (элемент ИЛИ 130) из блока 3 (шина 164). Таким образом, передача информации в линию производится с максимально возможной скоростью канала ОМ, так как не требуется подтверждения на получение каждого байта от линии,

Таким образом, при выводе информации блок 21 синхронизации передачи вырабатывает запросы информации в канал ОМ непосредственно по окоН чании передачи каналом предыдущего байта информации, чем обеспечивает-СИ максимально возможная скорость считывания информации из канала ОМ и передачи ее в линию. При этом выдача информации продолжается только в течение времени, когда из канала выдается сигнал ее идентификации, и не зависит от каких-либо подтверждений от линии.

Блок 20 адресации памяти обеспечивает одновременность процедур заполнения памяти информацией, поступающей с линии, и освобождения ее при передаче принятой информации в канал ОМ, что приводит к умень;шению необходимого объема памяти и ускорению процесса передачи данны

Передача информации прекращается после поступления от ОМ соответствующего сигнала по шине 92 в блок 3 Останов обмена сбрасывает в О триггер 77 (через элемент И-ИЛИ-НЕ 70.) , которь1й прекращает прием информации и канала-ОМ (шина 163) и посылает сигнал конца обмена в блок 2 (нулевой уровень сигнала в шине 49 Одновременно по шине 167«этот сигнал поступает в блок 4 (шина 139) и сбрасывает сигнал ГИ-И, прекращая управление передг чей информации из устройства в линию связи и через магистраль 6 и блок 7 передает синал конца в шины 16 линии связи. Передача информации может быть также прекращена по инициативе линии связи, В этом случае сигнал конца обмена по шинам 174 через блок 7 и магистраль 6 поступает в блок 21, запрещая дальнейшую устновку, триггера 45 (нулевой уровень на шине 48), а также в блок 4 (шина 158), Блок.4 прекращает управление передачей информации в линию связи и посылает соответствующий сигнал в блок 3 {шина 106). При получении сигнала конца обмена через элемент И-ИЛИ-НЕ 70 сбрасывается триггер 77 и блок 3 прекращает управлять приемом. информации из ка.нала ОМ в устройство, ие посылая запросов на байт по шине 11 (триггер 72 находится в О), и по шинам 12 посылает в ОМ сигнал конца обмена данными, переводя в состояние 1 триггер 66 через элемент И-НЕ 65 и выдавая сигнал 1 в шину 94 через элемент .И 68с

В режиме передачи информации ид какой-либо линии связи в основную машину, например из первой линии связи, по шинам 16 через блок 7 выдаётся код команды Записать (в сопровождении соответствующих управляющий сигналов на шинах 17 ) По.пученная из линии связи команда Записать заносится в регистр 8 для задания режима работы устройства. Прием кода команды в регистр команд производится под управлением блока 5, При получении по шинам 137 и 141 сигналов элемент И 123 вырс1батывает сигнал на шине 142, Сброс триггера 120 - прием команды происходит после получения сигнала по шине 139, В остальном все процедуры установления связи аналогичным изложенным выше. Блок 4 по шине 157 посылает сигнал об инициализации процедуры обмена со стороны первой линии связи в блок который, в своюочередь, по шинам 12 сообщает ОМ о поступлении по шинам 18 команды, инициирующей обмен информации (шина 160)„ Нормальное выполнение процедуры передачи данных возможно лишь при соответствии команд, поступивших с Од;ной стороны из линии связи, с другой - из канала ОМ, Встречная команда Читать поступает из ОМ по шинам 10 в буферный регистр 2 данных и регистр 1 команд. При этом блок 3 управляет приёмом команды из ОМ, а блок пер-;дачей кода этой команды в шины 18 линии связи аналогично описанному ранее. После процедуры установления связи устройство переходит к передаче данных. Приемом информации из шин 18 линии связи управляет блок 4, а также блоки 21 и 20. Информация с шин 16 через магистраль б поступает в блок 19 памяти. Запись осуществляется блоками. Скорость записи определяется скоростью поступления информации с шин 1& и не зависит от скорости работы канала ОМ. Память необходима, чтобы избежать потерь информации в случае, если скорость канала ОМ меньше скорости, с которой поступает информация с линии. Скорость считывания из блока 19 определяется скоростью работы канала ОМ. Считываемая информация поступает в буферный регистр 9 данных, а затем по шинам 13 в ОМ. Передача информации в ОМ происходит под управлением блоков 3, 21 и 20. Передача данных начинается с .получения запроса со стороны линии связи по шинам 17 . Полученный запрос на передачу через блок 7 и магистраль б поступает по шине 137 4, который в ответ на это п редает по шине 140 через магистраль б и блок 7 по шинам 15 сигнал го товности к приему.информации. Одновременно с этим передается запрос за байт информации (ишна 138). В от вет на это из линии связи по шинам 16 через блок 7 , магистраль б про ходит байт информации в сопровождении соответствующего управляющего сигнала на шинах 17. Этот сигнал (шина 30) поступает в блок 20, где по нему происходит выдача содекжи(Мого счетчика 23 через мультиплексор 25 на шину 36 Содержимое счетчика 23 представляет собой адрес ячейки памяти, по которому будет производиться запись байта информации , поступающего по магистрали б на вход блока 19 памяти. Выдача адреса сопровождается стробируювщм сигналом по шине 35, который поступает на управляющий вход блока 19. Этим же сигналом по его окончании производится модификация содержимого счетчика 23 для получения ад реса ячейки памяти, в которую будет записан следующий байт. Сигналомвышине 30, кроме того (по его окончании), производится и модификация содержимого счетчика 22 Этот счетчик необходим для того, чтобы при считывании информации из блока 19 всегда иметь информацию о том, произведена ли запись в блок 19. Этот же счетчик позволяет следить за тем, чтобы не было переполнения в блоке 19. В случае переполнения с выхода счетчика 22 снимается сигнал +15, запрещающий прием сигнала с шины 30. Так производится последовательный прием информации и запись в блок 19, Считыванием-информации из блока 19 в буферный регистр 9 данных управляют блоки 21 и 20. Если содержимое счетчика 22 отлично от нуля, т.е. в. блок 19 произведена запись, а также если каналом ОМ была выдана команда Читать, а из линии связи принята команда Записать, т.е. триггер 76 находится в единичном состоянии и выдает в шину 31 единичный сигнал, то при нулевом состоянии триггера 40 в блоке 21 содержимое счетчика 24 через мультиплексор 25 выдается из блока 20 на второй информационный вход блока 19 в сопровождении стробирующего сигнала на шине 34 с выхода элементаИ 29. Содержимое счетчика 24 представляет собой адрес ячейки памяти блока 19, из которой Д6Л5ЧНО быть осуществлено считывание информации. Сигналом на 34 (по его окончании) производится модификация счетчика 24, а из содержимого счетчика 22 вычитается единица. Сигнал по шине 37 подается на вход блока 21 (шина 51) и устанавливает там в единичное состояние триггер 40. -Одновременно производится считывание по указанному адресу байта информации из блока,19 в буферный регистр 9 данных. По единичному состоянию триггера 40, при наличин сигналов на шинах 49 и 53 и отсутствии сигнала на шине 50, устанавливается в единичное состояние триггер 45 и из блока 21 по шине 57 в шины 12 выдается сигнал, сопровождающий информацию, считываемую из буферного регистра 9 данных, по шинам 13 в ОМ. Приняв байт информации, ОМ втдаeT ответный сигнал по шичам 11 в блок 3, из которого сигнал поступает в блок 21 (шина 50) и переводит в нулевое состояние триггеры 40 и 45. Передача информации прекращается после поступления соответствующего сигнала по шинам 17 линии связи в блок 4 (вина 137), который прекращает управлять приемом информации из линии связи и посылает по шине 150 сигнал конца обмена в блок 3 (шина 106). Блок 3 через элемент И-НЕ 65 устанавливает в 1 триггер 66 и по шинам 12 передает сигнал конца обмена в ОМ (шина 93), а также через

элемент И-ИЛИ-НЕ 70 производит сброс триггера 76, нулевое состояние которого по шине 163 передается в блок 21 Сшина 49). Кроме того, с блока 4 по иине 145 приходит сигнал (через элемент ИЛИ 130, так как на выходе элемента НЕ 128 - нулевой сигнал), поступающий на вход блока 21 по шине 52. Сигнал сбрасывает триггер 45 через элемент И-ИЛИ-НЕ 44. В блок 20 с юбщение о конце обмена передается по шине 33 из блока 3 (шина 100), Этот сигнал сбрасывает счетчики 23 и 24 в исходное состояние .

Передача может быть прекращенапо инициативе ОМ. В этом случае соответствую1ций управляющий сигнал по шинам 11 поступает в блок 3 (ащна92 который прекращает управлять передачей информации в кана:л ОМ, уст&навливает в состояние 1 триггер 66, выдавая сигнал по шине 94 в ОМ,

сбрасывает триггер 76 и посылает сигнал конца обмена в блоки 21, 20 и 4. Блок 4, получив сигнал по шине 139, сбрасывает триггер 118, прекращает управление приемом информации в устройство, сбрасывая по шине 140 сигнал, и через магистраль б и блок 7 передает сигнал конца обмена в илины 15 линии связи.

Таким образом, устройство позволяет производить обмен с максимально возможной скоростью канала ЭВМ путем выдачи запросов на байты инфомации в канал ЭВМ непосредственно по окончании передачи предыдущего байта информации и не зависит от каких-либо подтверждений с линий, т.е. задержки на pacпpqcтpaнeниe сигналов по линиям связи полностью исключены. Это расширяет область применения устройства, позволяя его использовать в высокоскоростных системах.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР, № 754403, кл | |||

| с, 06 F 3/04, 1978 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения вычислительных машин | 1977 |

|

SU732845A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-07—Публикация

1982-03-24—Подача