Изобретение относится к вычислительной технике и может быть использовано в качестве буферной памяти процессора ЭВМ.

Целью изобретения является повышение быстродействия устройства.

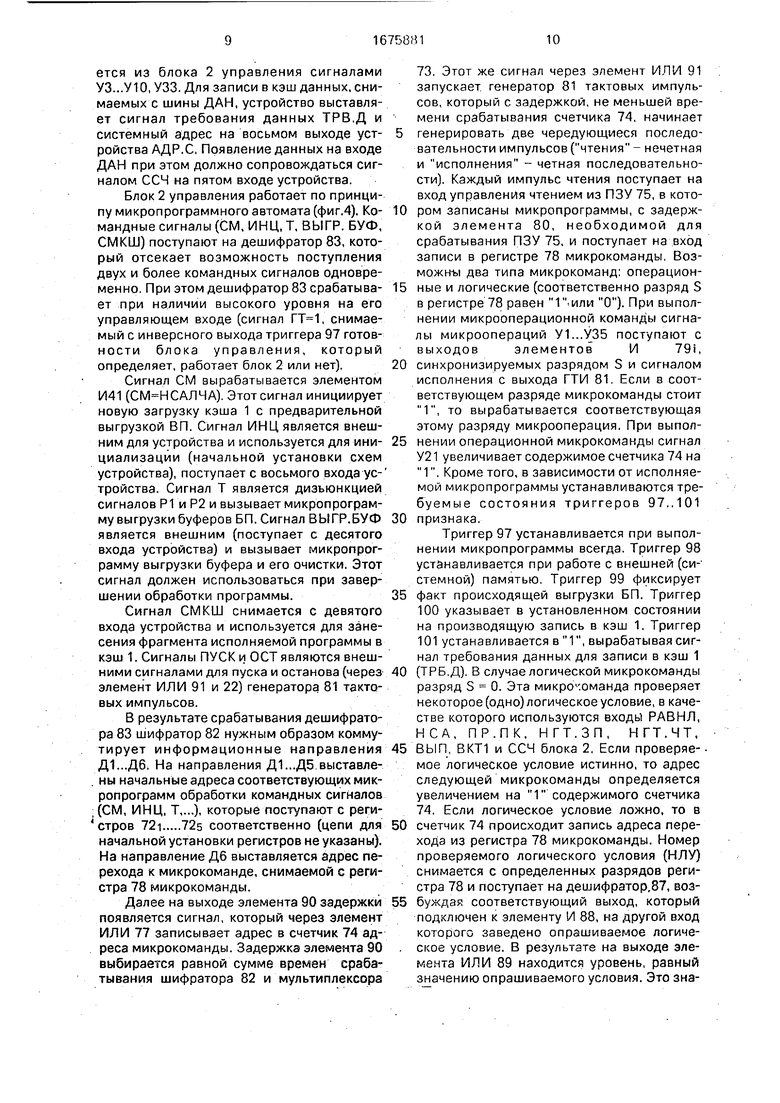

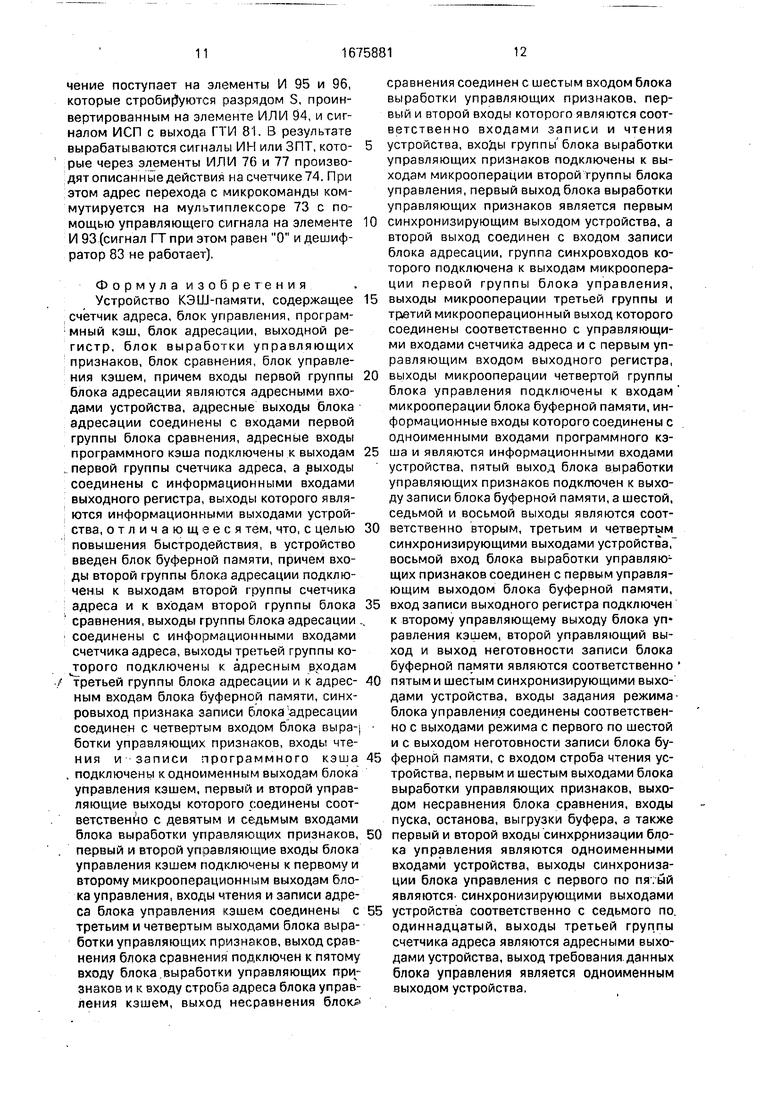

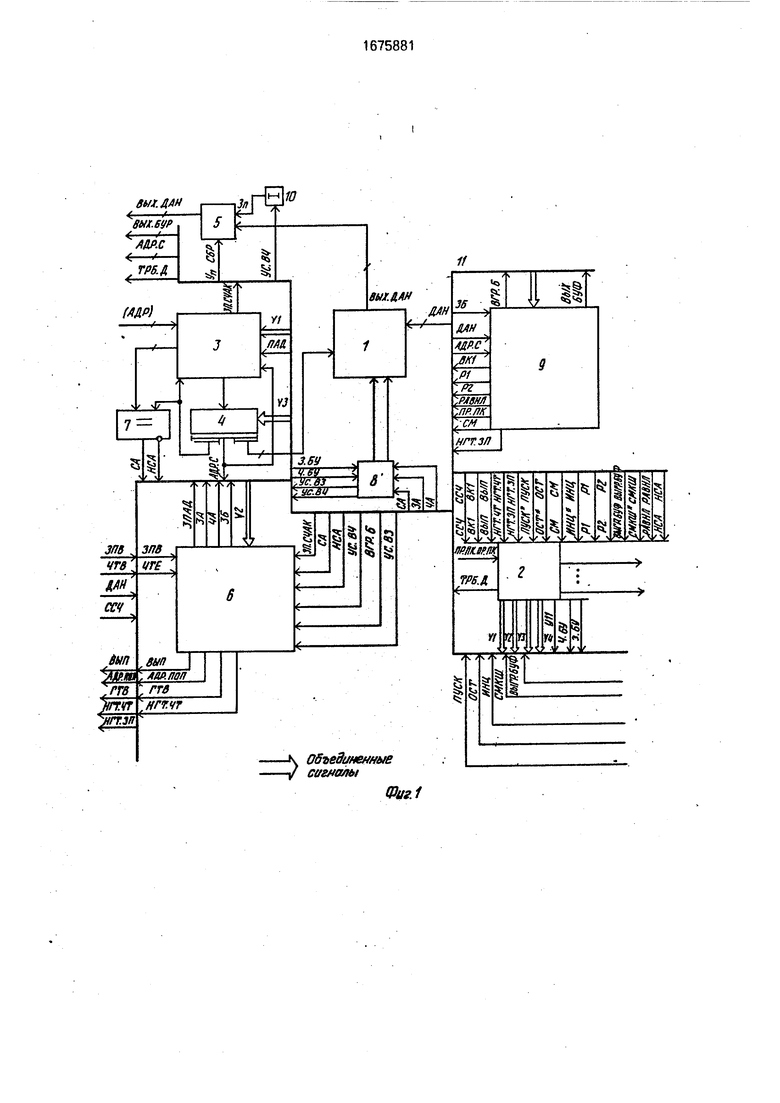

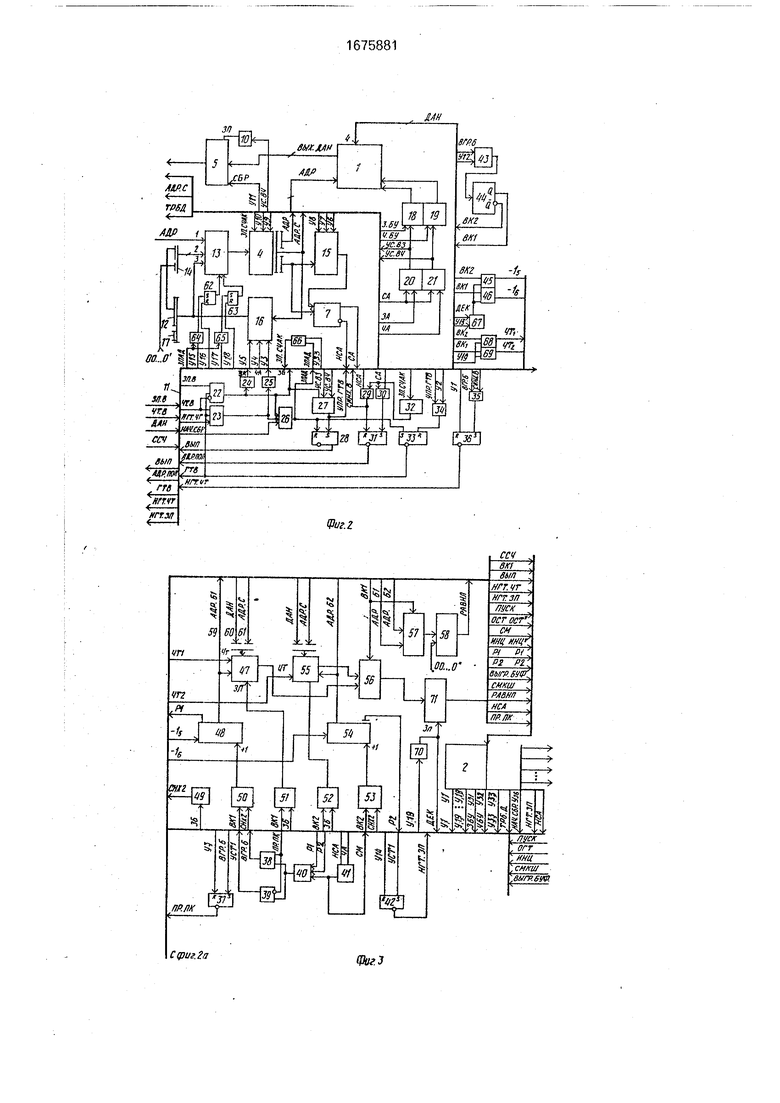

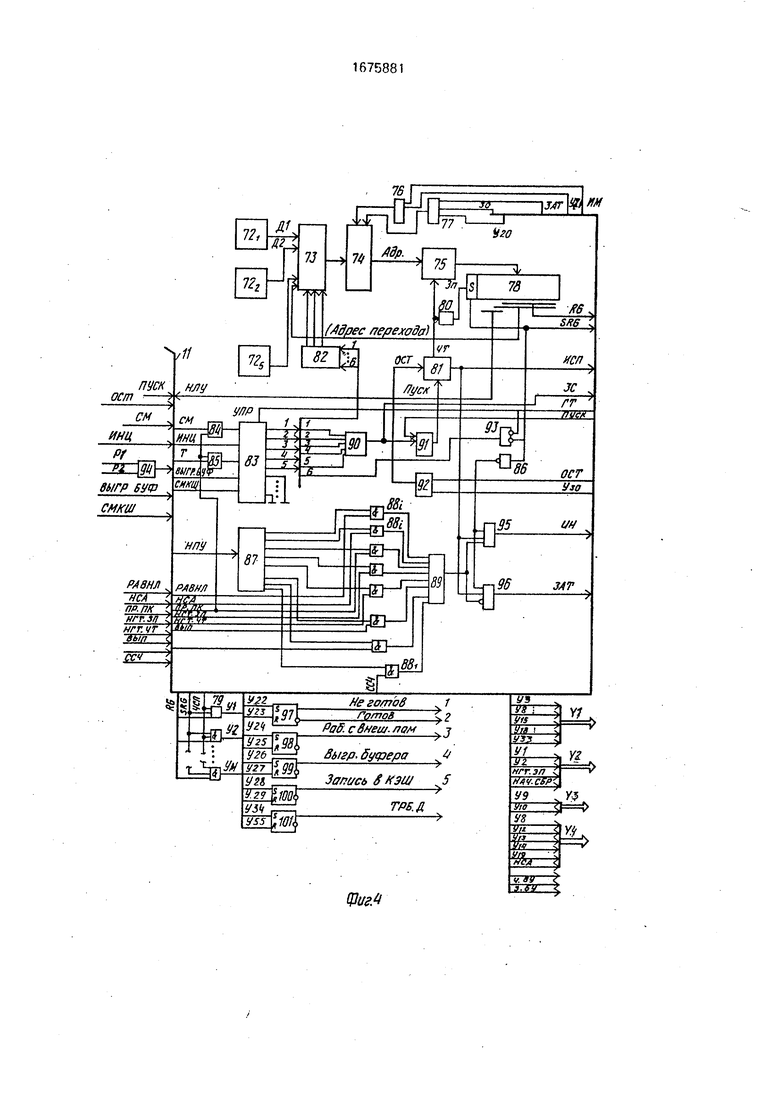

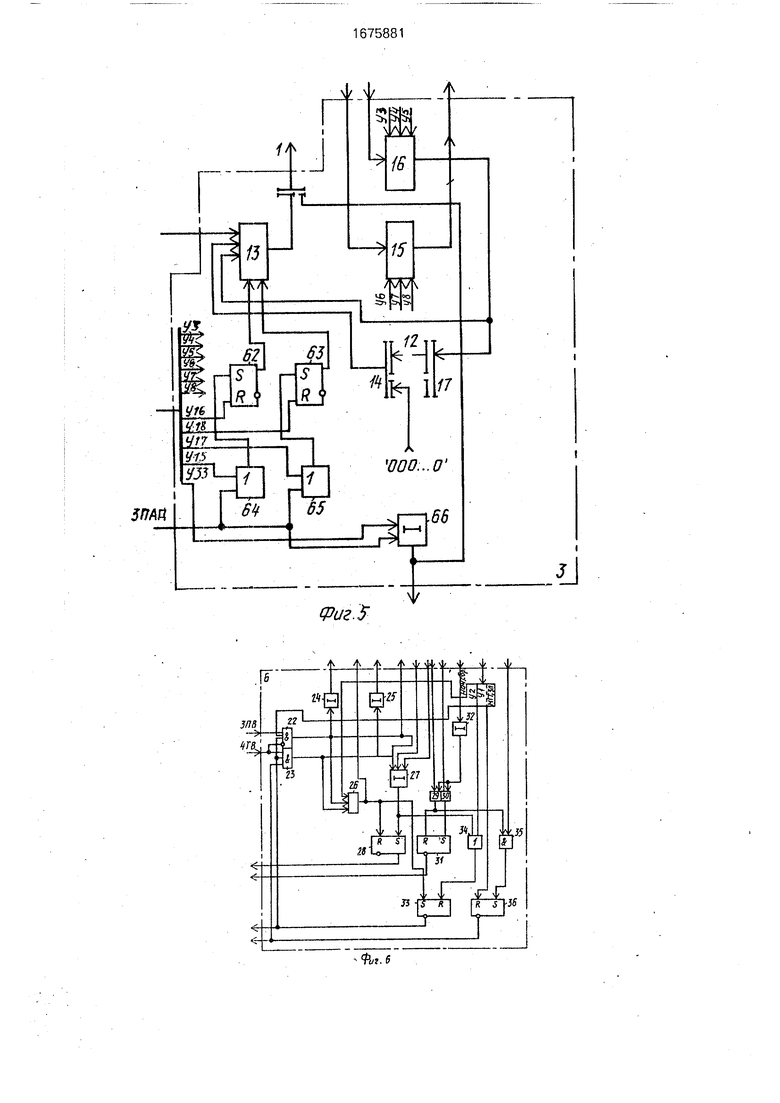

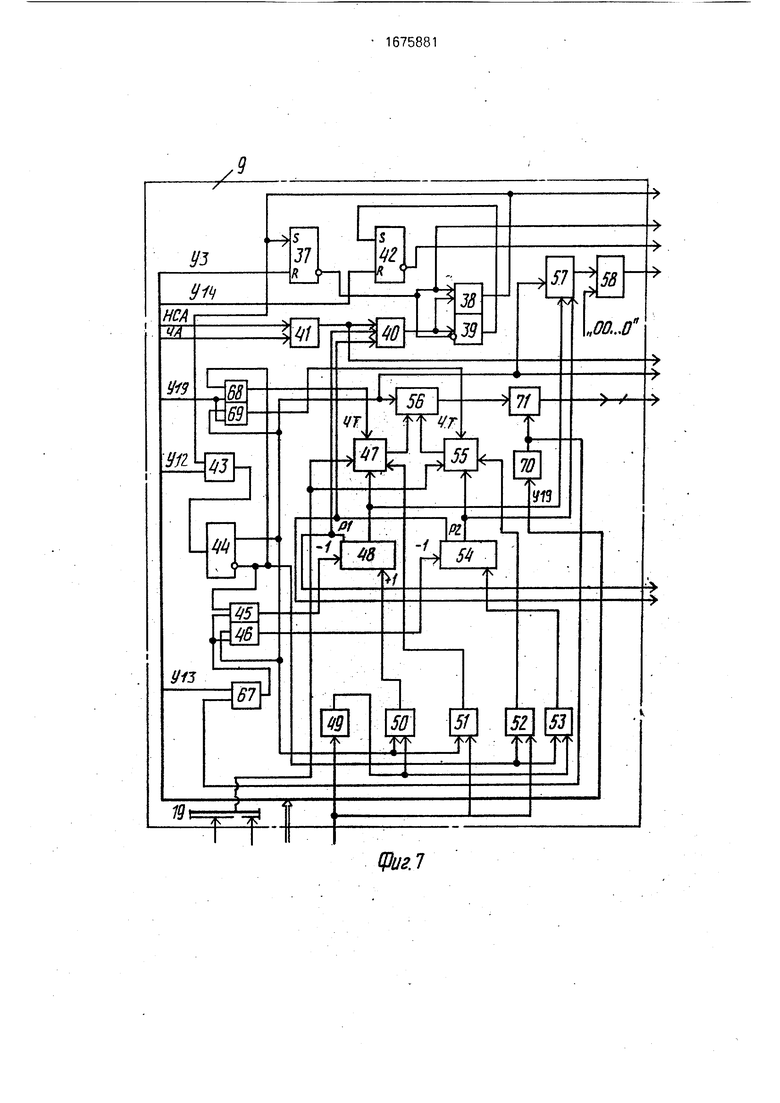

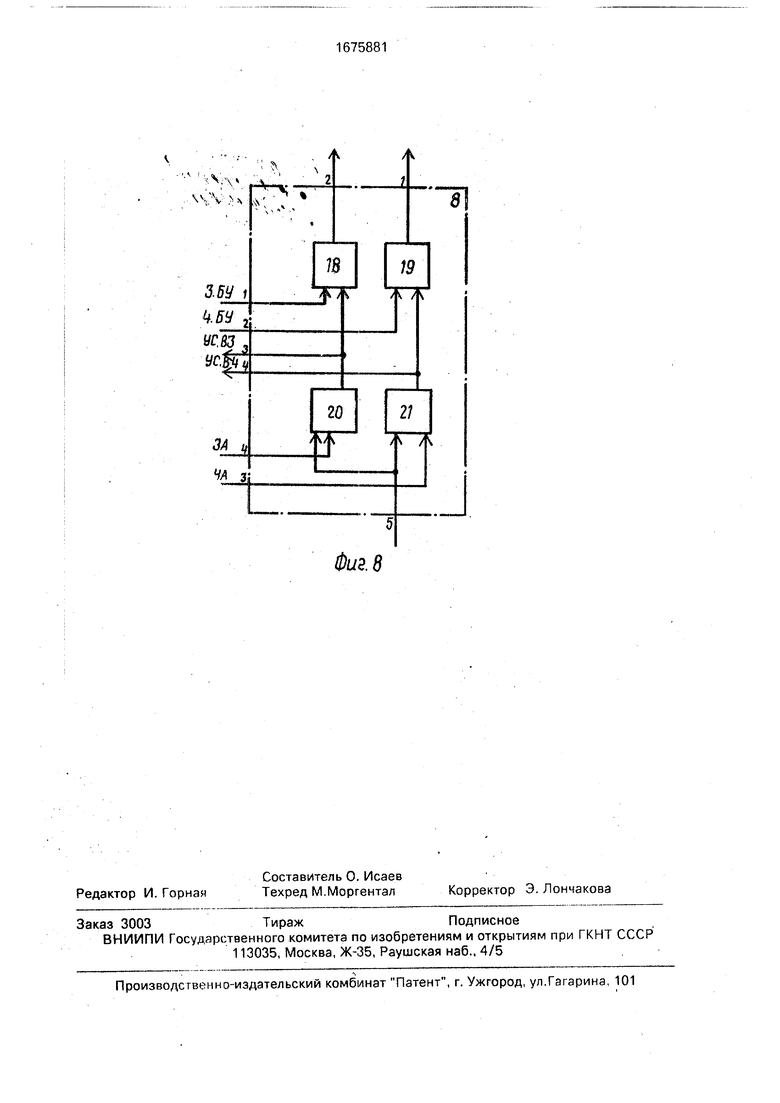

На фиг.1 представлена структурная схема устройства КЭШ-памяти; на фиг.2 и 3 - функциональная схема устройства КЭШ-па- на фиг.4 - пример реализации блока управления; на фиг.5 - пример реализации блока адресации; на фиг.6 - пример реализации блока выработки управляющих признаков; на фиг.7- пример реализации блока буферов записи; на фиг.8 - пример реализации блока управления кэшем.

Устройство (фиг.2 и 3) содержит программный кэш 1, блоки управления 2 и адресации 3, счетчик 4 адреса, выходной регистр 5, блоки выработки управляющих признаков 6, сравнения 7, управления кэшем 8 и буферной памяти 9, элемент 10 задержки и линию 11 связи.

Устройство также содержит входы 12 и 14 мультиплексора 13, счетчики 15 и 16, входы 17 мультиплексора 13, элементы ИЛИ 18 и 19, элементы И 20 - 23, элементы 24 и 25 задержки, элемент ИЛИ 26, элемент 27 задержки, триггер 28, элементы И 29 и 30, триггер31, элемент32 задержки,триггер 33, элемент ИЛИ 34, элемент И35, триггеры 36 и 37, элементы И 38 и 39, ИЛИ 40 и И 41, триггер 42, элемент ИЛИ 43, триггер 44, элементы И 45 и 46, первую буферную память 47, счетчик 48, элемент 49 задержки, элементы И 50 - 53, счетчик 54, вторую буферную память 55, мультиплексоры 56 и 57, узел 58 сравнения, связи 59-61, триггеры 62 и 63, элементы ИЛИ 64 и 65, элемент 66 задержки, элемент ИЛИ 67, элементы И 68 и 69, элемент 70 задержки и регистр 71.

Блок управления (фиг.З) содержит группу 72 регистров, мультиплексор 73, счетчик 74, ПЗУ 75, элементы ИЛИ 76 и 77, регистр 78, первую группу элементов И 79, элемент 80 задержки, генератор 81 тактовых импульсов, шифратор 82, дешифратор 83, элеменсл С

о

XJ

сл

00 00

ты И 84 и 85, элемент НЕ 86, дешифраторе, вторую группу элемент И 88, элемент ИЛИ 89, элемент 90 задержки, элементы ИЛИ 91 и 92, И 93, ИЛИ 94 и И 95 и 96 и триггеры 97 -101.

Устройство предназначено для функционирования в качестве программного кэша, например в высокопроизводительной ЭВМ в качестве оперативной памяти процессора мультипроцессорной системы, в качестве блока быстрой памяти в системах с общей шиной и т.п. Рассмотрим вариант работы устройства в мультипроцессорной системе с общей шиной, в которой имеется общая системная память, хранящая программы и данные, исполняемые процессорами системы. Каждый процессор такой системы в качестве собственной оперативной памяти использует предлагаемое устройство. Работа системы состоит в подкачке программ (фрагментов) из системной памяти в программные кэши процессоров, их исполнении, повторной подкачке .п.

Устройство в статическом режиме (фиг.1) работает следующим образом.

Основными действиями устройства являются запись слова данных в кэш 1 и чтение слова данных из кэш 1. Данные при этом подаются на четвертый вход устройства. Параллельно выставляется адрес на первом входе устройства (АДР) и выдается сигнал управления чтением (НТВ) или записью (ЗПВ). Блок выработки управляющих признаков СА и НСА, вырабатываемых блоком 7 сравнения,сравнивает старшую часть поступающего адреса с адресом отобража-, емого адресного окна. При попадании адреса вырабатывается сигнал СА, который стробирует сигналы записи ЗА или чтения ЧА, поступающие с выхода блока 6 выработки-управляющих признаков, в блоке 8 управления кэш.ем. При чтении данных выработанное слово данных из программного кэша 1 записывается в выходной регистр 5 под управлением сигнала записи УС.ВЧ от блока 8 управления кэшем, задержанного на задержке 10, что необходимо для совмещения сигнала з.аписм и информационного слова на входе регистра 5.

Если при записи выставленный на первом входе устройства адрес не попадает в адресное окно, то запись производится только в буферную память в блоке 9, на первый вход которого поступают данные, а на второй - адрес. Запись в блок 9 выполняется всегда, т е. как в случае попадания адреса в адресное окно, так и в случае непопадания. При переполнении буферной памяти вырабатывается признак НГТ. при переполнении обеих буферных памятей

в блоке 9 и НГТ.ЧТ, которые связаны соответственно с седьмым и шестым выходами устройства. Запись в блок 9 инициируется сигналом ЗБ, вырабатываемым в блоке 6

выработки управляющих признаков. При разгрузке блока 9 информационные слова поступают на его вторые выходы и далее на вторые выходы устройства. Процесс разгрузки блока 9 осуществляется без прерыва0 ния работы устройства: когда одна буферная память разгружается, вторая буферная память работает на запись, и наоборот. Исключение составляет лишь случай, когда обе буферные памяти потребуют вы5 грузки, что подробно рассматривается на функциональном уровне.

Если выполняется чтение из кэша 1 и вырабатывается признак непопадания адреса (НСА) на блоке 7 сравнения, то в блоке

0 2 управления инициируется микропрограмма, осуществляющая выгрузку буферной памяти в общесистемную память, после чего осуществляется смена адресного окна в кэше 1. Это выполняется следующим образом.

5 Старшая часть адреса из счетчика 4 адреса запоминается в блоке 3 адресации в качестве нового базового адреса. После этого мла д- шая адресная часть в счётчике 4 обнуляется (это выполняется за счет коммутации нуле0 вого поля при описании динамики работы в блоке 3j. При этом формируется системный адрес АДР.С, начиная с которого выполняется заполнение кэша. Под управлением блока 2 выполняется последовательная за5 грузка слов в кэш с одновременным увеличением содержимого счетчика 4 на 1 по входам УЗ. После заполнения программного кэша в счетчик 4 из блока 3 восстанавливается первоначальный адрес и

0 выполняется чтение данных в выходной регистр 5.

Блок 2 управления реализован как микропрограммный автомат и осуществляет уп- равление устройством, связанное с

5 выгрузкой буферов из блока 9.

Все другие сигналы и детали взаимодействия схем устройства раскрываются на уровне функционального описания по фиг.2 иЗ.

0 Динамика работы устройства (фиг.2 и 3) состоит в следующем. Полный адрес, поступающий на первый вход устройства, содержит старшую Ас и младшую Ам адресные части. Адрес поступает через мультиплек5 сор 13 на счетчик 4 адреса Группа разрядов Ам счетчика 4 адресует кэш 1. Количество разрядов Ам (обозначим I Ам I) определяется из соотношения (Ам logaM, где М - число ячеек кэша 1,

Требуемое соотношение является жестким и не может быть нарушено. Группа старших разрядов Ас поступает на второй вход блока 7 сравнения, на первый вход которого поступает базовый адрес из счетчика 15. Базовый адрес задает ячейку в системной памяти (не показано), начиная с которой в кэш 1 отображается программный фрагмент длиной Ам. Сигнал ЗПВ (ЧТВ) поступает на первый вход элемента И 22 (23) и проходит через него при готовности устройства, т.е. наличии сигнала ГТВ на втором входе элемента И 22(23), и сигнала НГТ. (НГТ.), подтверждающего готовность записи (чтения), причем одновременные запись и чтение взаимоисключены.

Задержки элементов 24 и 25 должны быть подобраны так, чтобы сигналы ЗА и ЧА, появляющиеся на их выходах, были не раньше выработки блоком 7 сравнения сигналов СА (Н СА). Далее сигнал ЗА (Ч А) поступает на второй вход элемента И 20 (21) и проходит через него при условиях, что блок 7 сравнения выработал сигнал совпадения (СА), попадает через элемент ИЛИ 18 (19) на вход управления записью (чтением) в кэше 1. В результате данные на четвертом входе кэша 1 записываются в кэш или попадают при чтении в выходной регистр 5 по сигналу записи УС.ВЧ, который поступает с выхода элемента И 21. При выполнении этих действий устройство определенным образом формирует выходные признаки. А именно, триггер 28 при прохождении сигнала через элемент И 22 (23) и далее элементы ИЛИ 26 сбрасывается, устанавливая признак выполнения команды Вып.-О. Сигналы 3В (УС.ВЧ), снимаемые с выходов элемента И 22(21), по которым производится запись (чтение), поступают через задержку элемента 27, необходимую для того, чтобы кэш 1 успел произвести операцию чтения (записи), на вход установки триггера 28, вырабатывая тем самым признак Вып.-1.

Триггер 31 формирует признак попадания или непопадания выставленного адреса в адресное окно. Этот триггер управляется сигналами СА и НСА, поступающими на входы соответствующих элементов И 30 и 29, которые стробируются сигналом ЗП.СЧАК.

Триггер 33 вырабатывает признак готовности устройства и устанавливается тем же сигналом, которым сбрасывается триггер 28. При установке триггера 33 его инвер- сный выход сбрасывается в О, сигнализируя о неготовности устройства. Триггер 33 сбрасывается сигналом УПР.ГТВ, вырабатываемым на выходе элемента 27 задержки, или сигналом У2 из блока 2 управления.

Триггер 36 вырабатывает сигнал НГТ.ЧТ, определяющий готовность (НГТ.) или неготовность (НГТ.ЧТЮ) выполнить операцию чтения в кэше 1. Состоя- ние НГТ. устанавливается сигналом микрооперации У1 (в исходном состоянии триггер 36 сброшен, что обеспечивается командой начальной установки на БУ 2). Приведение триггера 36 в состояние

0 неготовности чтения обеспечивается сигналами ВГР.В и СИНХ.В на входе элемента И35, выход которого заведен на вход установки триггера 36. Роль, аналогичную триггеру 36, по записи играет триггер 42, формирующий

5 НГТ.ЗП. Управление триггером 42 осуществляется сигналом микрооперации У14 и сигналом УСТ.1, вырабатываемыми на выходе элемента И 39.

Рассмотрим отдельно операции записи

0 и чтения, инициируемые сигналами ЗПВ и ЧТВ. При выполнении операции записи дополнительно к описанному происходит следующее. Информационный вход буферных памятей БП1 и БП2 - 47 и 55 образует объе5 единенные в шине разряды ДАН и АДР. С (АДР.С - выход счетчика 4). Адресация БП1 И БП2 выполняется счетчиками 48 и 54Д Размерность буферных памятей 47 и 55 одинакова и должна выбираться из соотношения

0 1/2к(Ам), где k 1,2- целое число, округляемое в зависимости от технических характеристик системы.

Выбор буферной памяти 47 или 55 для записи осуществляется Т-триггером 44, вы5 ходы которого ВК1 и ВК2 задают требуемую коммутацию. Буферные памяти хранят данные вместе с их полными адресами. Смена буферов для записи происходит, когда один из буферов, работающих на запись, полно0 стью заполняется, и когда при чтении из кэша 1 выставленный гдрес не попадает в диапазон адресов, соответствующих хранимому в кэше фрагменту программы, этот факт фиксируется элементом И 41, на входы

5 которого поступают сигналы НСА (несрав-. нения адресов) и ЧА (чтения).

При возникновении первого события один их счетчиков 48 и 54 (работающий на запись) переполняется, возникает сигнал

0 Р1 или Р2 на выходе переполнения соответствующего счетчика, который через элемент ИЛИ 40 далее поступает на вход элементов И 38 и 39. При наличии разрешающего признака ПР.ПК вырабатывается сигнал ВГР.Б

5 на выходе элемента И 38, который через элемент ИЛИ 43 поступает на счетный вход Т-триггера 44 и переключает его. В результате значения выходов ВК1 и ВК2 триггера 44 изменяются на противоположные, что обеспечивает новую требуемую коммутацию для разводки управляющих сигналов. Сигналы ВК1 и ВК2 стробируют элементы И 45, 46, 50 - 53, 68 и 69 и управляют коммутацией мультиплексоров 56 и 57. Перечисленные элементы и схемы обеспечивают следующее. Элементы И 50 (53) управляют поступлением сигналов инкрементирова- ния счетчиков 48 (54), Общим входом счетчиков 48 и 54 является вход СИНХ2, снимаемый с элемента 49 задержки, входом которого является вход ЗБ - сигнал записи в буферную память. Задержка элемента 49 должна быть не меньше времени для записи в БП1 и БП2. Элементы И 41 и 52 управляют записью в БП1 и БП2 соответственно. Сигнал для записи ЗБ поступает на И 51 и 52 незадержанным, Мультиплексор 56 коммутирует информационный выход одного из буферов БП1 или БП2 через регистр 71 на второй выход устройства. Этот выход используется для перезаписи содержимого буферных памятей в системную память.

Мультиплексор 57 используется для коммутации содержимого адресных счетчиков 48 и 54 на узел 58 сравнения с нулем. Процесс сравнения с нулем имеет место при разгрузке БП, в этот момент содержимое счетчиков 54 и 48 управляется сигналами декрементирования от блока 2 управления. Момент прекращения декрементирования определяется появлением высокого уровня на выходе РАВНЛ узла сравнения. Управление декрементированием осуществляется сигналом У13 из блока 2 который поступает на вход элементов И 45 и 46, на другие входы которых заведены соответственно ВК1 и ВК2.

Второе событие фиксируется элементом И 41 и далее через элементы ИЛИ 40, И 38 и ИЛИ 43 переключает триггер 44. В начале работы устройства буферные памяти должны быть очищены (нулевое содержимое ячейки БП интерпретируется как мусор, что должно использоваться при перезаписи содержимого разгрузочного буфера). Разгрузка буферной памяти БП1 или БП2 осуществляется под управлением бло- ка 2 управления сигналами У19, обеспечивающими чтение информации из БП1 через мультиплексор 56 в выходной регистр 71, сигналом записи в который служит задержанный сигнал У19 на элементе 70 задержки, что необходимо для учета срабатывания БП и времени задержки на мультиплексоре 56. Сигнал записи в регистр 71 (ДЭК) поступает затем через элемент ИЛИ 67 на элементы И 45 и 46 для декрементирования содержимого соответствующего счетчика 48 (54). Перед первым считыванием из БП в регистр 71 блок управления сигналом У13

уменьшает на 1 содержимое соответствующего счетчика 48 (54), так как это содержимое всегда указывает на следующую ячейку, в которую нужн.о производить запись. Узел

58 сравнения с нулем определяет момент прекращения чтения.

Сигналом для переключения Т-триггера 44 является сигнал ВГР.В, Этот же сигнал устанавливается триггером 37, который

0 сбрасывает признак ПР.ПК (ПР.), тем самым блокирует вход элемента И 38, запрещая на время выгрузки информации из БП переключение Т-триггера. При этом запись в БП продолжается до тех пор, пока не сформи5 руется сигнал переполнения счетчика 48 или 54, который через элемент ИЛИ 40 и далее через элемент И 39 устанавливает триггер 42. Низкий уровень триггера 42 (сигнал НГТ.ЗП) блокирует поступление сигна0 лов для чтения/записи в устройство по второму и третьему входам устройства до завершения выгрузки обоих блоков 47 и 55 памяти. Счетчик 16 используется для копирования содержимого счетчика 4. Старшие

5 разряды счетчика 16 используются в качестве нового значения базового адреса.

Для обращения к кэш 1 выставляется адрес на первом входе устройства. Если сигнал ЗПВ или НТВ воспринимается (т.е., по0 является на выходе элемента И 22 или 23), то на выходе элемента ИЛИ 26 появляется сигнал ЗПАД, который через задержку элемента 66, равную времени срабатывания мультиплексора 13, поступает на вход уп5 равления записью в счетчик 4 (сигнал ЗП.СЧАК). При этом сигнал ЗПАД устанавливает через элементы ИЛИ 64 и 65 триггеры 62 и 63, т.е., предполагается, что коммутация первого информационного вхо0 да на мультиплексоре 13 осуществляется значениями прямых выходов триггеров 62 и 63, равными1. Счетчик 15 базового адреса используется для базирования отображаемого в кэше 1 фрагмента памяти. Новое со5 держимое в счетчике 15 устанавливается путем переписывания содержимого счетчика 4 адреса по следующему тракту: счетчик 4 - счетчик 16 - замена младшей адресной части счетчика 16 нулями. После этого со0 держимое счетчика 16 переписывается в счетчик 4. Пусть, например, при чтении из кэша 1 выставлен адрес 1010010, который выходит за пределы отображаемого фрагмента. При этом в результате переписыва5 ния нового фрагмента в кэш 1 новый базовый адрес, выставленный в счетчике 15, равен 1010000 в предположении, что младшая адресная часть, адресующая кэш 1, представляет четыре младшие разряда. Управление счетчиками 16, 15 и 4 осуществляется из блока 2 управления сигналами УЗ...У10, УЗЗ. Для записи в кэш данных, снимаемых с шины ДАН, устройство выставляет сигнал требования данных ТРВ.Д и системный адрес на восьмом выходе устройства АДР.С. Появление данных на входе ДАН при этом должно сопровождаться сигналом ССЧ на пятом входе устройства.

Блок 2 управления работает по принципу микропрограммного автомата (фиг.4). Командные сигналы (СМ, ИНЦ, Т, ВЫГР. БУФ, СМКШ) поступают на дешифратор 83, который отсекает возможность поступления двух и более командных сигналов одновременно. При этом дешифратор 83 срабатывает при наличии высокого уровня на его управляющем входе (сигнал , снимаемый с инверсного выхода триггера 97 готовности блока управления, который определяет, работает блок 2 или нет).

Сигнал СМ вырабатывается элементом И41 (СМ НСАЛЧА). Этот сигнал инициирует новую загрузку кэша 1 с предварительной выгрузкой ВП. Сигнал ИНЦ является внешним для устройства и используется для инициализации (начальной установки схем устройства), поступает с восьмого входа ус- тройства. Сигнал Т является дизъюнкцией сигналов Р1 и Р2 и вызывает микропрограмму выгрузки буферов БП. Сигнал ВЫГР.БУФ является внешним (поступает с десятого входа устройства) и вызывает микропрограмму выгрузки буфера и его очистки. Этот сигнал должен использоваться при завершении обработки программы.

Сигнал СМКШ снимается с девятого входа устройства и используется для занесения фрагмента исполняемой программы в кэш 1. Сигналы ПУСК и ОСТ являются внешними сигналами для пуска и останова (через элемент ИЛИ 91 и 22) генератора 81 тактовых импульсов.

В результате срабатывания дешифратора 83 шифратор 82 нужным образом коммутирует информационные направления Д1...Д6, На направления Д1...Д5 выставле- ны начальные адреса соответствующих микропрограмм обработки командных сигналов (СМ, ИНЦ, Т,...), которые поступают с регистрое 72i72s соответственно (цепи для

начальной установки регистров не указаны). На направление Д6 выставляется адрес перехода к микрокоманде, снимаемой с регистра 78 микрокоманды.

Далее на выходе элемента 90 задержки появляется сигнал, который через элемент ИЛИ 77 записывает адрес в счетчик 74 адреса микрокоманды. Задержка элемента 90 выбирается равной сумме времен срабатывания шифратора 82 и мультиплексора

73.Этот же сигнал через элемент ИЛИ 91 запускает, генератор 81 тактовых импульсов, который с задержкой, не меньшей времени срабатывания счетчика 74, начинает

генерировать две чередующиеся последовательности импульсов (чтения - нечетная и исполнения - четная последовательности). Каждый импульс чтения поступает на вход управления чтением из ПЗУ 75, в кото0 ром записаны микропрограммы, с задержкой элемента 80, необходимой для срабатывания ПЗУ 75, и поступает на вход записи в регистре 78 микрокоманды. Воз- можн-ы два типа микрокоманд: операцион5 ные и логические (соответственно разряд S в регистре 78 равен О). При выполнении микрооперационной команды сигналы микроопераций У1...У35 поступают с выходов элементовИ 791,

0 синхронизируемых разрядом S и сигналом исполнения с выхода ГТИ 81. Если в соответствующем разряде микрокоманды стоит 1, то вырабатывается соответствующая этому разряду микрооперация. При выпол5 нении операционной микрокоманды сигнал У21 увеличивает содержимое счетчика 74 на 1. Кроме того, в зависимости от исполняемой микропрограммы устанавливаются требуемые состояния триггеров 97..101

0 признака.

Триггер 97 устанавливается при выполнении микропрограммы всегда. Триггер 98 устанавливается при работе с внешней (системной) памятью. Триггер 99 фиксирует

5 факт происходящей выгрузки БП. Триггер

100указывает в установленном состоянии на производящую запись в кэш 1. Триггер

101устанавливается , вырабатывая сигнал требования данных для записи в кэш 1

0 (ТРБ.Д). В случае логической микрокоманды разряд 3 0. Эта микрокоманда проверяет некоторое (одно) логическое условие, в качестве которого используются входы РАВНЛ, НСА, ПР.ПК, НГТ.ЗП, НГТ.ЧТ,

5 ВЫП, ВКТ1 и ССЧ блока 2, Если проверяв- мое логическое условие истинно, то адрес следующей микрокоманды определяется увеличением на 1 содержимого счетчика

74.Если логическое условие ложно, то в 0 счетчик 74 происходит запись адреса перехода из регистра 78 микрокоманды. Номер проверяемого логического условия (НЛУ) снимается с определенных разрядов регистра 78 и поступает на дешифратор,87, воз5 буждая соответствующий выход, который подключен к элементу И 88, на другой вход которого заведено опрашиваемое логиче- . ское условие. В результате на выходе элемента ИЛИ 89 находится уровень, равный значению опрашиваемого условия. Это значение поступает на элементы И 95 и 96, которые стробир ются разрядом S, проин- вертированным на элементе ИЛИ 94, и сигналом ИСП с выхода ГТИ 81. В результате вырабатываются сигналы ИН или ЗПТ, кото- 5 рые через эл ементы ИЛИ 76 и 77 производят описанные действия на счетчике 74. При этом адрес перехода с микрокоманды коммутируется на мультиплексоре 73 с помощью управляющего сигнала на элементе 10 И 93 (сигнал ГТ при этом равен О и дешифратор 83 не работает).

Формула изобретения Устройство КЭШ-памяти, содержащее 15 счетчик адреса, блок управления, программный кэш, блок адресации, выходной регистр, блок выработки управляющих признаков, блок сравнения, блок управления кэшем, причем входы первой группы 20 блока адресации являются адресными входами устройства, адресные выходы блока адресации соединены с входами первой группы блока сравнения, адресные входы программного кэша подключены к выходам 25 первой группы счетчика адреса, а выходы соединены с информационными входами выходного регистра, выходы которого являются информационными выходами устройства, отличающееся тем, что, с целью 30 повышения быстродействия, в устройство введен блок буферной памяти, причем входы второй группы блока адресации подключены к выходам второй группы счетчика адреса и к входам второй группы блока 35 сравнения, выходы группы блока адресации ., соединены с информационными входами счетчика адреса, выходы третьей группы которого подключены к адресным входам третьей группы блока адресации и к адрес- 40 ным входам блока буферной памяти, синх- ровыход признака записи блока адресации соединен с четвертым входом блока выра-| ботки управляющих признаков, входы чтения и записи программного кэша 45 . подключены к одноименным выходам блока управления кэшем, первый и второй управляющие выходы которого соединены соответственно с девятым и седьмым входами блока выработки управляющих признаков, 50 первый и второй управляющие входы блока управления кэшем подключены к первому и второму микрооперационным выходам блока управления, входы чтения и записи адреса блока управления кэшем соединены с 55 третьим и четвертым выходами блока выработки управляющих признаков, выход сравнения блока сравнения подключен к пятому входу блока,выработки управляющих признаков и к входу строба адреса блока управления кзшем, выход несравнения блокр

сравнения соединен с шестым входом блока выработки управляющих признаков, первый и второй входы которого являются соответственно входами записи и чтения устройства, входы группы блока выработки управляющих признаков подключены к выходам микрооперации второй группы блока управления, первый выход блока выработки управляющих признаков является первым синхронизирующим выходом устройства, а второй выход соединен с входом записи блока адресации, группа синхровходов которого подключена к выходам микрооперации первой группы блока управления, выходы микрооперации третьей группы и третий микрооперационный выход которого соединены соответственно с управляющими входами счетчика адреса и с первым управляющим входом выходного регистра, выходы микрооперации четвертой группы блока управления подключены к входам микрооперации блока буферной памяти, информационные входы которого соединены с одноименными входами программного кэша и являются информационными входами устройства, пятый выход блока выработки управляющих признаков подключен к выходу записи блока буферной памяти, а шестой, седьмой и восьмой выходы являются соответственно вторым, третьим и четвертым синхронизирующими выходами устройства, восьмой вход блока выработки управляющих признаков соединен с первым управляющим выходом блока буферной памяти, вход записи выходного регистра подключен к второму управляющему выходу блока уп равления кэшем, второй управляющий выход и выход неготовности записи блока буферной памяти являются соответственно пятым и шестым синхронизирующими выходами устройства, входы задания режима блока управления соединены соответственно с выходами режима с первого по шестой и с выходом неготовности записи блока буферной памяти, с входом строба чтения устройства, первым и шестым выходами блока выработки управляющих признаков, выходом несравнения блока сравнения, входы пуска, останова, выгрузки буфера, а также первый и второй входы синхррнизации блока управления являются одноименными входами устройства, выходы синхронизации блока управления с первого по пя-. ый являются синхронизирующими выходами устройства соответственно с седьмого по. одиннадцатый, выходы третьей группы счетчика адреса являются адресными выходами устройства, выход требования данных блока управления является одноименным выходом устройства.

вых. ДАН

Ю

}

Объединенные сигналы

Фиг.1

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для моделирования конечных автоматов | 1988 |

|

SU1520534A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1091158A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Устройство для программного управления | 1991 |

|

SU1800445A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве буферной памяти процессора ЭВМ. Целью изобретения является повышение быстродействия устройства. Устройство содержит программный кэш, блок управления, блок адресации, счетчик адреса, выходной регистр, блок выработки управляющих признаков, блок сравнения, блок управления кэшем и блок буферной памяти. Цель изобретения достигается тем, что в случае выставления процессором адреса записи, не принадлежащего кэшу, информация записывается предварительно в блок буферов записи, а затем автономно перекачивается в оперативную память, при этом работа кэша не прерывается. 8 ил.

Сфиг.га

сеч

ФигЗ

ЩигЯ

R

.11

4-гп&

L889A9L

фигЛ

Фиг. 8

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Химический огнетушитель | 1925 |

|

SU2361A1 |

| Способ обработки грубых шерстей на различных аппаратах для мериносовой шерсти | 1920 |

|

SU113A1 |

Авторы

Даты

1991-09-07—Публикация

1988-12-19—Подача