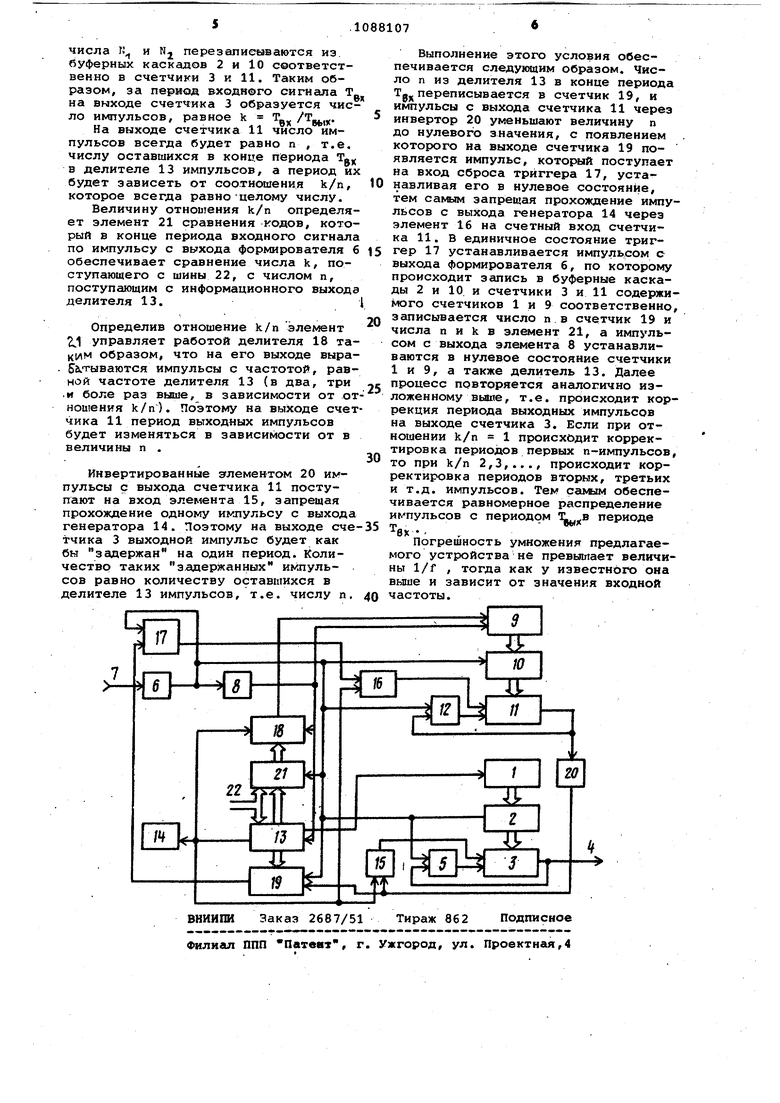

1 Изобретение относится к икэтульсной технике и может быть использова но в измерительных устройствах, например, при измерении частоты, фазы : формы низкочастотных периодических сигналов. . , Известен цифровой умножитель час тоты , содержащий последовательно соединенные счетчик импульсов, буфе ный каскад и счетчик обратного счет выход которого соединен с первьм .входом первого элемента ИЛИ, выход которого соединен с входом записи счетчика обратного счета, а второй вход - с входом записи буферного каскада, первым входом второго элемента ИЛИ, выходом формирователя им пульсов и входом элемента задержки, выход которого соединен с входом ус установки счетчика импульсов, счетный вход которого соединен с выходом второго элемента ИЛИ,второй вход ; которого через последовательно соединенные формирователь прямоугольны импульсов и делитель частоты соеди нен с выходом генератора тактовых импульсов и счетным входом счетчика обратного счета С1Q. Недостатком этого устройства явл ется низкая точность умножения, про являющаяся, в нарушении периодичност выходного сигнала. Наиболее близким по технической сущности и достигаемому результату к изобретению яйляется цифровой умно житель частоты, содержащий последовательно соединенные первый счетчик импульсов, первый буферный каскад, первый счетчик обратного счета, выход которого соединен с выходной шиНой умножителя и с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом формирователя импульсов, вход которого подключен к входной шине умножителя, с входом элемента задержки и входом записи первого буферного каскада, а выход - с входом записи первого счет чика обра,тного счета, последовательно Соединенные ВТОРОЙ счетчик импульсов, второй буферный каскад и второй счетчик обратного счета, выхо которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединён с выходом формирователя импульсов и входом записи вто рого буферного каскада, а выход с входом записи второго счетчика обратного счета, выход элемента задержки подключен к входам установки первого и второго счетчиков импульсов, счетный вход первого делителя частоты соединен с выходом генератора тактовых импульсов, первый выход со счетным входом первого счетчика импульсов, а второй выход - со счетным входом второго счетчика импульсов,выход второго счетчика обратного 107 счета соединен с третьим входом. первого элемента ИЛИ С22, Недостатком известного устройства является недостаточная точность умножения, проявляющаяся в нарушении периодичности выходного сигнала при больших значениях коэффициента Умножения. Цель изобретения - повышение точности умножения, Поставленная цель достигается тем, что в цифровой умножитель частоты, содержай1ий последовательно соединенные первый счетчик импульсов, первый буферный каскад, первый счетчик обратного счета, выход которого соединен с выходной шиной умножителя и с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом формирователя импульсов, вход которого подключен к входной шине умножителя, с входом элемента задержки и входом записи первого буферного каскада, а выход с входом записи первого счетчика обратного счета, последовательно соединеннь е второй счетчик импульсов, второй буферный каскад и второй счет чик обратного счета, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом формирователя импульсов и входом записи второго буферного каскада, а выход - с входом записи второго счетчика об ратного счета, выход элемента зiaдepжки подключен к входам установки вто.рого счетчикд импульсов и первого делителя частоты, счетный вход которого соединен с выходом генератора тактовых импульсов, а первый выход со счетным входом первого счетчика импульсов, введены инвертор, перйый и второй элементы И, триггер, второй делитель частоты, третий счетчик обратного счета и элемент сравнения кодов, вход установки которого соединен с выходом формирователя импульсов, запуска триггера и входом записи третьего счетчика обрат- , нОго счёта, информационный вход кот рого соединен с первым информационным выходом первого делителя частбты, счетный вход - с выходом инвертора , вход которого подключен к выходу второго счетчика обратного Счета, и с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика обратного счета, а второй вход - с выходом генератора тактовых импульсов, счетным входом второго делителя частоты и первым входом второго элемента И, выход которого соединен со счетным входом второго счетчика обратного счета, второй вход - с выходом триггера, вход сброса которого соединен с выходом третьего счетчика обратного счета, причем шина установки коэффициента деления соединена с кодовыми входами первого делителя частоты и элемента срав нения кодов, информационный вход которого соединен с вторым информациОННШ4 выходом первого делителя частоты, информационный выход - с информационным входом второго делителя частоты, выход которого соединен со счетным входом второго счетчика импульсов, а вход установки с выходом элемента задержки. На чертеже представлена структурная электрическая схема устройства. Цифровой умножитель частоты содержит последовательно соединенные первый счетчик 1 импульсов, первый буферный каскад 2, первый счетчик 3 обратного счета. выход которого сое динен с выходной шиной 4 умножителя и с первымвходЬм первого элемента 5 ИЛИ, второй вход которого соединен с выходом формирователя б импульсов, вход которого, подключен входной шине 7 умножителя, с входом элемента 8 задержки и входом записи первого буферного каскада 2, а выход - с входом записи первого счетчи ка 3 обратного счета, последователь но соединенные второй счетчик 9 импульсов, второй буферный каскад 10 и второй счетчик 11 обратного счета выход которого подключен к первому входу второго элемента 12 ИЛИ, второй вход которого соединен с выходо формирователя б импульсов и входом записи второго буферного каскада 10, а выход - с входом записи второ го счетчика 11 обратного счета, выхо элемента 8 задержки подключен к вхо дам установки второго счетчика 9 им пульсов и первого делителя 13 часто ты,- счетный вход которого соединен с выходом генератора 14 тактовых им пульсов, а первый выход - со счетны входом первого счетчика 1 импульсов первый 15 и второй 16 элементы И, триггер 17, вторйй делитель 18 частоты, третий счетчик 19 обратного счета, инвертор 20 и элемент 21 сра нения, кодов, вход установки которог соединен с выходом формирователя 6 импульсов, входом запуска триггера 17 и входом записи третьего счетчика 19 обратного счета, информационны вход которого соединен с первым информационным выходом первого делите ля 13 частоты, счетный вход - с выхо дом Инвертора 20, вход которого под ключен к выходу второго счётчика 11 обратного счета и с первым входом первого элемента 15 И, выход которог соединен со счетным входом первого счетчика 3 обратного счета, а второй вход - с выходом зтенератора 14 тактовых импульсов, счетным входом второго делителя 18 частоты и первым входом второго элемента 16 И, выход которого соединен со счетным входом второго счетчика 11 обратного счета, второй вход - с выходом триггера 17, вход сброса которого соединен с выходом третьего счетчика 19 обратного счета, причем шина 22 установки коэффициента деления соединена с кодовыми входами первого делителя 13 частоты и элемента 21 сравнения кодов, информационный вход которого соединен с вторым информационным выходом первого делителя.13 частоты, инфррмационный выход - с информационным входом второго делителя 18 частоты, выход которого соединен со счетным входом .второго счетчика 9 импульсов, а вход установки - с выходом элемента 8 задержки. Цифровой умножитель частоты работает следукчцим образом. , Формирователь б из входного периодического сигнала формирует короткие прямоугольные импульсы,-период повторения которнх равен периоду входного сигнала Т. Эти импульсы поступают на вход элемента 8, на входы записи буферных каскадов 2 и10, счетчика 19, установочные входы делителей 13 и 18 и элемента 21, а также запуска триггера 17. На счетный вход счетчика 1 поступают импульсы с выхода делителя 13 с часторой , на счетный вход счетчика 9 поступают импульсы с выхода делителя 18 с частотой f ./n, где k - коэффициент деления делителя 13 или коэффициент умножения устройства, - 1,2,3,.. - коэффициент увеличения частоты делИтеля 18 по сравнению с делителем 13,fт частота повторения импульсов генератора 14,- п - остаточное импульсов в конце периода входного сигнала в делителе 13. За период входного сигнала счетчике 1 поступает число импульсов, равное Н Тц)5, а в счетчик 9 - N f /k-k/n-Тех . В конце периода входного сигнала импульсом с В1ыхода формирователя 6 эти числа перезаписываются соответственно в буферный каскад 2, счетчик 3 и в буферный каскад 10 и счетчик 11. На счётные входы счетчиков 3 и 11 поступают импульсы с частотой f с выхода генератора 14. В результате этого чибло N считывается со счетчика 3 после перезаписи через промежуток времени, равный Te,,x Tgjf/k а счетчика 11 через промежуток времени, равный k/n. . На выходах счетчиков 3 и 11 через промежутки времени, равные соответственно Тр,и Тд,.,образуются импульсы, которые через элементы 5 и 12 поступают на входы записи счетчиков 3 и 11 соответственно, благодаря чему.

числа к и Nj перезаписываются из буферных каскадов 2 и 10 соответственно в счетчики 3 к 11. Таким образом, за период входного сигнсша Т„ на выходе счетчика 3 образуется число импульсов, равное k Т /Тд,.

На выходе счетчика 11 число импульсов всегда будет равно п , т.е. числу оставшихся в конце периода Т« в делителе 13 импульсов, а период их будет зависеть от соотношения k/n, которое всегда равно-целому числу.

Величину отношения k/n определяет элемент 21 сравнения Кодов, который в конце периода входного сигнала по импульсу с выхода формирователя б обеспечивает сравнение числа k, поступающего с шины 22, с числом п, поступающим с информационного выхода делителя 13.

Определив отношение k/n элемент 2 управляет работой делителя 18 та«им образом, что на его выходе выра- 5а.тываются импульсы с частотой, равной частоте делителя 13 (в два, три

и боле раз выше, в зависимости от отношения k/n). Поэтому на выходе счетчика 11 период выходных импульсов будет изменяться в зависимости от в величины п .

Инвертированные зглементом 20 импульсы с выхода счетчика 11 поступают на вход элемента 15, запрещая прохождение одному импульсу с выхода генератора 14. Поэтому на выходе сче тчика 3 выходной импульс будет как бы задержан на один период. Количество таких з.адержанных импульсов равно количеству оставшихся в делителе 13 импульсов, т.е. числу п.

Выполнение этого условия обеспечивается следующим образом. Число п из делителя 13 в конце периода TPJJ переписывается в счетчик 19, и импульсы с выхода счетчика 11 через инвертор 20 уменьшают величину п до нулевого значения, с появлением которого на выходе счетчика 19 появляется импульс, который поступает на вход сброса триггера 17, устанавливая его в нулевое состояние, тем самым запрещая прохождение импульсов с выхода генератора 14 через элемент 16 на счетный вход счетчика 11. В единичное состояние триггер 17 устанавливается импульсом с выхода формирователя 6, по которому происходит запись в буферные каскады 2 и 10 и счетчики 3 и 11 содержимого счетчиков 1 и 9 соответственно записывается число п в счетчик 19 и числа п и k в элемент 21, а импульсом с выхода элемента 8 устанавливаются в нулевое состояние счетчики 1 и 9, а также делитель 13. Далее процесс повторяется аналогично изложенному выше, т.е. происходит коррекция периода выходных импульсов на выходе счетчика 3. Если при отношении k/n 1 происходит корректировка периодов первых п-импульсов то при k/n 2,3,..., происходит корректировка периодов вторых, третьих и т.д. импульсов. Тем самым обеспечивается равномерное распределение илпульсов с периодом IJ-y периоде

вх - .

Погрешность умножения предлагаемого устройства не превышает величины 1/f , тогда как у известного она выше и зависит от значения входной частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1982 |

|

SU1095381A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU976482A1 |

| Цифровой умножитель частоты | 1979 |

|

SU843201A1 |

| Умножитель частоты | 1978 |

|

SU765818A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

| Цифровой умножитель частоты | 1979 |

|

SU799146A1 |

| Устройство определения временного положения импульсных сигналов | 1988 |

|

SU1596301A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

| Умножитель частоты с дробным коэффициентом умножения | 1987 |

|

SU1492475A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1290313A1 |

и11ФРОВОЙ УМНОЖИТЕЛЬ ЧАСТОТЫ, содержащий последовательно соединенные первый счетчик импульсов, первый буферный каскад, первый счетчик обратного счета, выход которого соединен с выходной шиной умножителя и с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом формирователя им- . пульсов, вход которого подключен к входной шине умножителя с входом элемента задержки и входом записи первого буферного каскада, а выход с входом записи первого летчика об-, ратного счета, последовательно соединенные второй счетчик импульсов, второй буферный каскад и второй счетчик обратного счета, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом формирователя импульсов и входом записи второго буферного каскада, а выход - с входом записи второго счетчика обратного счета, выход элемента задержки подключен к входам установки второго счетчика импульсов и первого делителя частоты, счетный вход которого соединен с выходом генератора тактовых импульсов, а первый выходсо.счетным входом первого счетчика импульсов, отличающийся тем, что, с целью повышения точности умножения, в него ведены инвертор, первый и второй элементы И, триггер, второй делитель частоты, третий счетчик обратного счета и элемент сравнения кодов, вход установки которого соединен с выходом формиро- . вателя импульсов, входом запуска триггера и входом записи третьего счетчика обратного счета, информационный вход которого соединен с первым информапионным выходом первого делителя частоты, счетный вход - с выходом инвертора, вход которого подключен к выходу второго счетчика § обратного счета, и с первым входом (Л первого элемента И, выход которого соединен со счетным входом первого счетчика обратного счета, а второй вход - с выходом генератора тактовых импульсов, счетным входом второго делителя частоты и первым входом вто- рого элемента И, выход которого динен со счетным входом второго счет-, чика обратного счета, второй вход сх .с выходом триггера,, вход сброса ко00 торого соединен с выходом третьего счетчика обратного счета, причем шина установки коэффициента деления соединена с кодовыми входами первого делителя частоты и .элемента сравнения кодов, информационный вход которого соединен с вторым информационным выходом первого дели.теля часто-, . ты, информационный выход - с информационным входом второго делителя частоты, выход которого соединен со счетным входом второго счетчика импульсов, а вход установки - с выходом элемента задержки.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой умножитель частоты | 1979 |

|

SU799146A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-04-23—Публикация

1982-12-30—Подача