1

изобретение отнсх:;ится к области измерительной и вычислительной техники и может быть использовано для делени я повторяющихся временных интервалов на целое число частей,

Известен умножитель частоты, который содержит генератор опорной частоты, счетчики, регистр, схему задержки выходных импульсов, формирователь, схемы контроля нулей и единиц остат- ка 1.

Наиболее близким по технической сущности к устройствам является умножитель частоты, содержащий генератор опорной частоты, входной формирователь, блок управления, делители частоты с переменным и постоянным коэффициентом деления, регистр и элементы И, к выходу делителя.частоты с nocTO-2Q яиным коэффициентом деления подключен yльтивибpaтop, выход которого соединен с управляющим входом элемента И, выход запоминающего регистра через узел переноса кода, управляющий вход 25 которого соединен с выходом делителя частоты с переменным коэффициентом деления, подключен к суммирующему входу делителя частоты с постоянным коэффициентом деления 2.зо

Величина погрешности маис этом устройстве уменьшена до величины Т .. Это достигается тем, что в устройстве производится суммирование остатков от деления Т на п. Если при суммировании остатков возникает переполнение, то запускается мультивибратор и пропускается один период Тр. При этом 1-й выходной импульс умножителя чаатоты появляется через время t, которое

равно ..,МТ„,

rJi-l

целая часть числа от делегдеLhTo ния Т на h-T, а Jдробная часть числа от деления Т на п-Т,

Погрешность определения t равна

r- -tr- - KU V -(

оТак как разность числа и его целой части не может пр осходить единицы,

то л мчсакс оОднако даже такую погрешность в некоторых случаях желательно уменьшить .

Таким образом, недостатками устройства является недостаточно высокая точность.

цель изобретения - повысить точность умножения частоты.

Это достигается тем, что в умножителе частоты, содержащий генератор опорной частоты, входной формироватепьу суммирующий счетчик, буферный регистр, вычитаиощий счетчик, элемент ИЛИ и элемент И, причем выход генератра опорной частоты соединен со счетным входом суммиру1ощего-счетчика и первым входом элемента И, выход которого соединен со счетным входом вычтакндего счетчика, информационные выходы суммирующего счетчика соединены b соответствующим входами буферного регистра, группа выходов старших разрдов буферного регистра соединена с группой информационных входов вычитающего счетчика, первый выход входного формирователя соединен с входом запис информации буферного регистра, второй выход - с входом установки нуля суммирующего счетчика и первым входом элемента ИЛИ, выход которого соединен с входом записи информации вычитающего счетчика, выход переполнения которого соединен с выходной шиной устройства и со вторым входом элемента-ИЛИ, дополнительно введены j-к триггер и накапливающий сумматор,при этом группа входов накапливающего сумматора соединена с группой выходов младших разрядов буферного регистра,вход j jтриггера соединен с шиной логической единицы, вход к - с выходом переноса накапливающего сумматора, а вход синхронизации с выходом генератора опорной частоты, выход j-к триггера соединен со вторым входом элемента И, входы установки нуля и установки единицы старшегоразряда накапливающего сумматора соединены соответственно с первым и вторым выходами входного формирователя, а вход управления вводом информации ншсапливаюш.его сумматора соединен с выходом переполнения вычитающего счетчика.

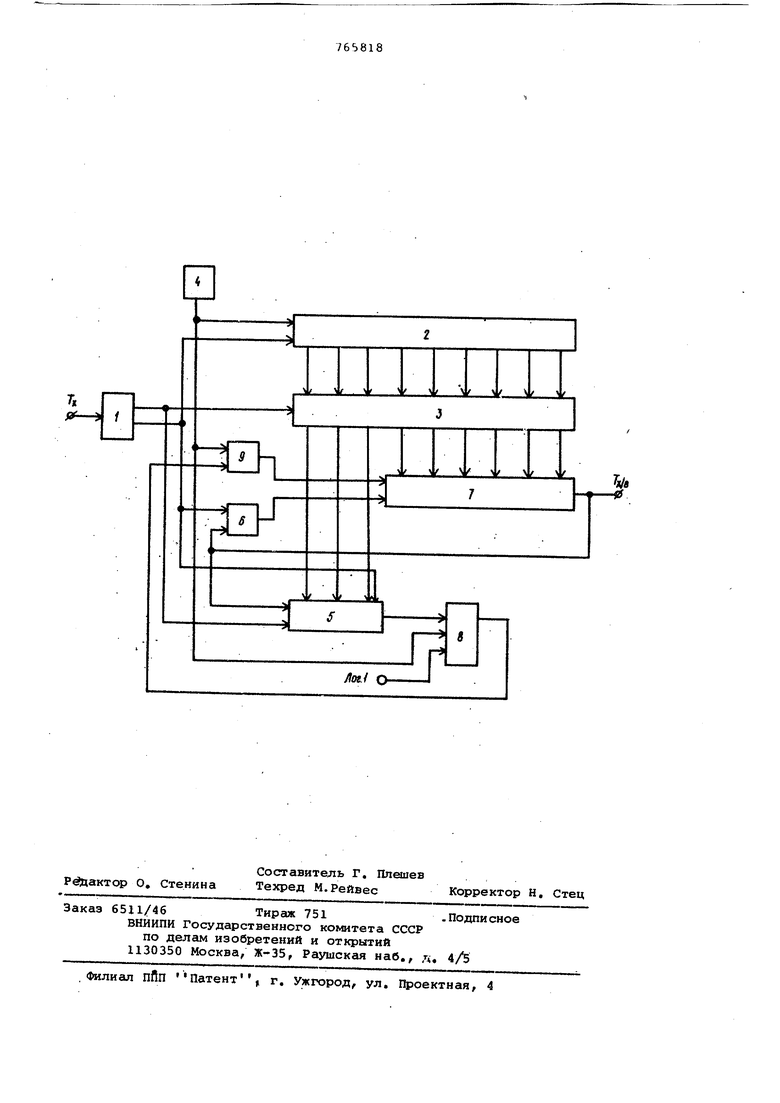

На чертеже -представлена схема предлагаемого устройства.

Устройство содержит входной формирователь 1, суммирующий счетчик 2, буферный регистр 3, генератор 4 опорной частоты, накапливающий сумматор... 5,элемент ИЛИ 6, вычитающий счетчик 7, j-к триггер 8, элемент И 9.

Умнохситель работает следующим образом

На вход формирователя 1 поступает входной сигнал U, имеющий период Т. При переходе через определенный уровень, напримёрчерез U, и возрастаНИИ входного сигнала на выходах формирователя 1 формируются короткие импульсы. Импульс с первого выхода формиров.ат&пЯ 1 используется для ввода из суммирующего счетчика 2 в

буферный регистр 3, а импульс со i. рого выхода - для установки суммиру цего счетчика 2 в нулевое состояние. При этом импульс на первом выходе формирователя 1 вырабатывается раньше, чем на втором выходе.

За период Т входного сигнала U в счетчик- 2 поступает N импульсов с выхода генератора 4 опорной частоты, период которых равен Т, : N .

В начале следующего периода формирователь 1 вырабатывает импульсы на первом и втором выходах. Импульс с первого выхода формирователя записыва,ет код N из счетчика 2 в регистр 3 и устанавливает в нуль сумматор 5, а импульс со второго выхода - устанавливает в нулевое состояние счетчик 2, через элемент ИЛИ 6 поступает на вход записи информации вычитающего счетчика 7 и заносит в него код из старших разрядов регистра 3, равный:

где п - коэффициент умножения частоты а также поступает на вход установки единицы старшего разряда сумматора 5, устанавливая тем самым в сумматоре 5 код, равный п/2.

После того- как на счетный вход счетчика 7 поступит N, импульсов генератора 4, код в счетчике 7 равняется нулю, а на его выходе вырабатывается сигнгш переполнения. Этот сигнал через элемент ЛЛИ б поступает на вход записи информации счетчика 7 и тем caNfdM снова заносит в него код N. из регистра 3, и на входе сумматора 5 при этом суммируется содержимое сумматрра 5 и младших разрядов регистра 3, Содержимое младших разрядов регистра 3 равно

N,j

Первый импульс на выходе счетчика 7 появляется через время Ц , равное

t N TO .

После этого импульса код в сумматоре 5 будет

«слл /2 + N

Если при этом наступило переполнение сумматора 5, т.е. NCM вырабатывается сигнал на выходе переноса сумматора и на входах j триггера 8 две единицы, что приводит к перебросу .триггера 8 в противоположное состояние, в данном случае из. состояния в состояние OV. При этом элемент И 9 закрывается к а время т.е. пропускается один импульс генератора 4. Следующий импульс генератора 4 -проходит на вход синхронизации триггера 8, когда состояние входов j

1

О

Поэтому триггер 8 возвращается в исходное состояние , и элемент И 9 открывается. Если переполнение сумматора 6 н наступило, т.е. М.п, то триггер 8 не меняет своего состояния и эле мент И 9 не закрывается. Так как в сумматоре 5 перенос не накапливаются, то в общем виде можно записать: N.,- wod( ) . Находим общее выражение для мом та появления 1-го выходного импуль са. Для этого учитываем,что до поя ления 1-го выходного импульса умно теля частоты было пропущено число пульсов генератора 4, равное ,)i. тогда N ТД( г)1 Точный момент появления 1-го им пульса равен ()i. Погрешность определения i-ro импульса равна .i, i4,.b,.,,,.(,,,)i -ir-To(). Так .как S- oCif ib lV-oU -t l Ыi тAТак как дробная часть числа не превосходит единицы, то A-t HaK-Toli) Откуда ut йлакс 2 Таким образом, точность предлага мого устройства в два раза выше, че у прототипа, Формула изобретения Умножитель частоты, содержащий нератор опорной частоты, входной ф мирователь, суммирующий счетчик, бу ферный регистр, вычитающий счетчик элемент ИЛИ и элемент И, причем вых генератора опорной частоты соединен со счетным входом суммирующего счетчика и первым входом элемента И, вы-ход которого соединен со счетным входом вычитаиощего счетчика, информационные выходил суммирующего счетчика соединены с соответствующими входами буферного регистра, группа выходов старших разрядов буферного регистра соединена с группой информационных входов вычитающего счетчика, первый выход входного формирователя соединен с входом записи информации буферного регистра , второй выход - с входом установки нуля суммирующего счетчика и первым входом элемента ИЛИ, выход которого соединен с входом записи информации вычитающего счетчика, выход переполнения вычитающего счетчика соединен с выходной шиной устройства и со вторым входом элемента ИЛИ, отличающийс я тем, что, с целью повышения точности устройства, в него дополнительно ввгдены j-K триггер и накапливающий сумматор, при этом групла входов накапливающего сумматора соединена с группой выходов младших разрядов буферного регистра, вход j j-K триггера соединен с шиной логической единицы, вход к - с выхо- . дом переноса нак апливающего с мматора, а вход синхронизации - с выходом генератора опорной частоты , выход j-K триггера соединен со вторым входом элемента И,входи установки нуля и установки единицы старшего разряда накапливающего сумматора соед нены соответственно с первым и вторым выходами входного формирователя, а вход . . управления вводом информации накапливающего сумматора соединен с выходом/ переполнения вычитающего счетчика. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 346721, кл. Н 03 В 19/10, 1971. 2.Авторское свидетельство СССР № 369672, кл. Н 03 В 19/10, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Умножитель частоты | 1978 |

|

SU781832A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Цифровой умножитель частоты | 1983 |

|

SU1190456A1 |

| Умножитель частоты | 1981 |

|

SU1058021A1 |

| Генератор случайного процесса | 1985 |

|

SU1739374A1 |

| Устройство синхронизации | 1990 |

|

SU1781835A1 |

| Измеритель сдвига фаз (его варианты) | 1982 |

|

SU1040432A1 |

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Цифровой измеритель центра прямоугольных видеоимпульсов | 1984 |

|

SU1265689A1 |

Авторы

Даты

1980-09-23—Публикация

1978-09-01—Подача