1

(21)А216154/24-21

(22)25.03.87

(46) 07.07.89. Бюп. № 25

(72) Е.В. Иньков и В.И. Малышев

(53)621.374.4 .(088.8)

(56)Авторское свидетельство СССР

№ 953739, кл. Н 03 К 23/68, 02.02..81.

Авторское свидетельство СССР № 1337988, кл. Н ОЗ В 19/00, 19.08.85.

(54)УМНОЖИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ КОЭФФИЦИЕНТОМ УМНОЖЕНИЯ

(57)Изобретение относится к и myльc- нон технике и может быть использовано в радиотехнике, автоматике и измерительной технике. Полью изобретения является повышение точности умножения путем формирования равномерной выходной последовательности импульсов, синхрош13ованной входными импульса-ми, что дос тигается за счет введения BToporti вычитающего счетчика 14 импульсов и использования многовходового элемента ИЛИ 15. Устройство содержит также генератор 1 опорной частоты, первый 2 и второй 5 делители частоты, счетчик 4 импульсов, первый вычитающий счетчик 3 им- , формирователь 6 импульсов, первьп 8 и второй 9 элементы И, первый элемент ИЛИ 10, RS-триггер 11, первый 16 и второй 17 элементы задержки, 1ЛИНУ 7 обнуления, входную 12 и выходную 13 шины. 1 ил„

с

s

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретный умножитель частоты | 1985 |

|

SU1337988A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Измеритель динамических характеристик | 1987 |

|

SU1532901A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ | 1989 |

|

RU2042261C1 |

| Умножитель частоты | 1978 |

|

SU765818A1 |

| Импульсный преобразователь переменного тока в переменный | 1988 |

|

SU1508321A1 |

| Умножитель частоты следования импульсов | 1983 |

|

SU1140220A1 |

| Цифровой умножитель частоты сле-дОВАНия иМпульСОВ | 1979 |

|

SU824440A1 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2105410C1 |

Изобретение относится к импульсной технике и может быть использовано в радиотехнике, автоматике и измерительной технике. Целью изобретения является повышение точности умножения путем формирования равномерной выходной последовательности импульсов, синхронизованной входными импульсами, что достигается за счет введения второго вычитающего счетчика 14 импульсов и использования многовходового элемента ИЛИ 15. Устройство содержит также генератор 1 опорной частоты, первый 2 и второй 5 делители частоты, счетчик 4 импульсов, первый вычитающий счетчик 3 импульсов, формирователь 6 импульсов, первый 8 и второй 9 элементы И, первый элемент ИЛИ 10, RS - ТРИГГЕР 11, ПЕРВЫЙ 16 И ВТОРОЙ 17 ЭЛЕМЕНТЫ ЗАДЕРЖКИ, ШИНУ 7 ОБНУЛЕНИЯ, ВХОДНУЮ 12 И ВЫХОДНУЮ 13 ШИНЫ. 1 ИЛ.

4

со to

4 g СП

3- 14

Изобретешге относится к импульсной технике и может быть использовано в радиотехнике, автоматике и измерительной технике.

Целью изобретения является повышение точности умножения путем формирования равномерной выходной носле- довательности И№1ульсов, синхрош1зо- ванпой входными имнульсами.

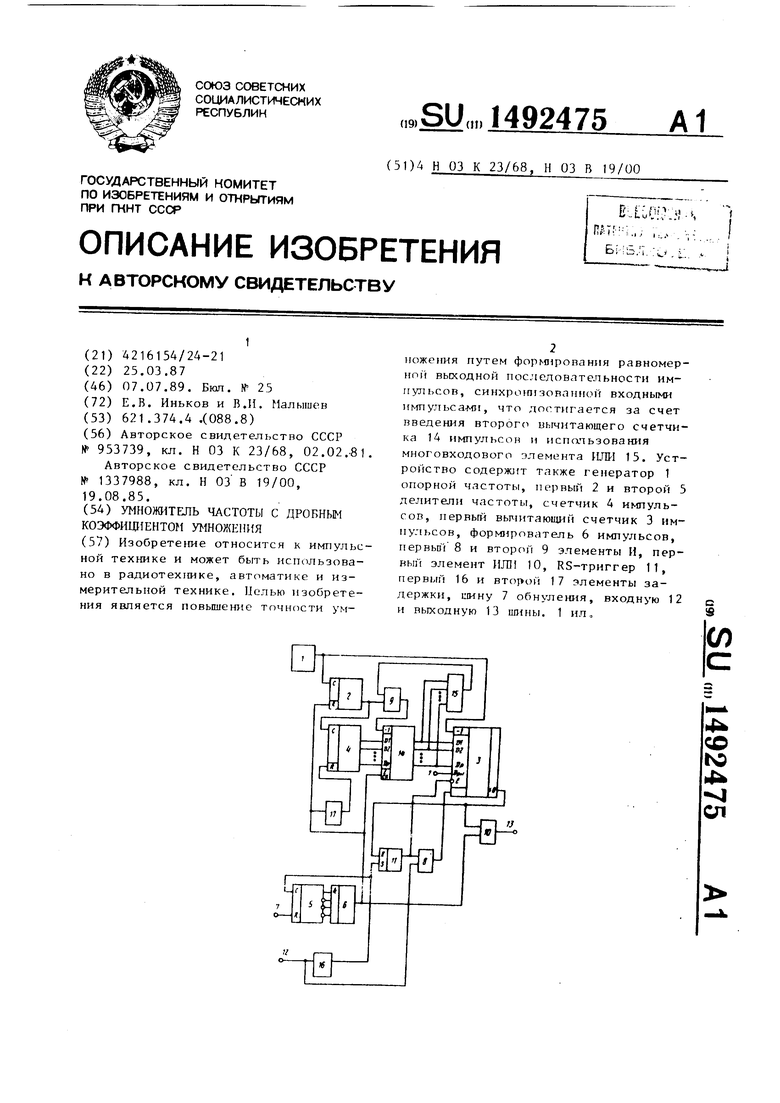

На чертеже представлена структурно-электрическая схема устройства. Устройство содержит генератор 1 опорной частоты, первьй 2 частоты, первый вычитаюио111 счетчик 3 нход обратного счета которого соединен со счетным входом первого делителя 2 частоты и выходом генератора 1 опорной частоты, счетчик 4, счетный вход которого соединен с вьсходом первого делителя 2 частоты, второй делитель 5 частоты, (формирователь 6 импульсов, информационные входы которого соединены с информационными выходами второго делителя 5 частоты, шину 7 обнуления, которая соединена с входом установки в О второго делителя 5 частоты, первый 8 и второй 9 элемент И, первый элемент lUHI 10, RS-триггер 11, входную 12 и выходную 13 шины, второй вьнитаюш11й счетчик 14, второй элемент ИГЦ1 15, первый 16 и второй 17 элементы задержки.

Входная шипа 12 устройства соединена с первым входом первог о элеме1гга И 8 и входом первого элемента 16 задержки, выход которого соединен со счетЕ1Ым входом второго делителя 5 частоты и входом установки RS-триг- гера 11.

Второй вход первого элемента И 8 соединен с выходом RS-триггера 11 и входом разрешения первого вычитающего счетчика 3, вход установки в О которого соединен с выходом первого элемента И 8, а выход - с входом установки в О RS-триггера 11 и первым входом первого элемента ILTDI 10, выход которого соединен с выходной шиной 13 устройства.

Входы второго элемента ШШ 15 со- единены с информащюнными выходами второго вычитающего счетчика 14 и информационными входами первого вычитающего счетчика 3, а выход соединен с первым входом второго элемента И 9 втсфой вход которого соединен с выходом первого делителя 2 частоты, а выход - с входом обратного счета вто

4

5 0 5 о

0 5

5

0

5

75

рого вычитаюшег.о счетчика 14, информационные входы которого соединены с |и1 формационными выходами счетчика 4, а вход установки в О соединен с входом установки в О первого делителя 2 частоты, с вторым входом первого элемента 1ШИ 10 и выходом фор- -мирователя 6 импульсов.

Вход второго элемента 17 задержки соединен с выходом формирователя 6 импульсов, а выход - с входом установки в О счетчика 4.

Умножитель работает следующим образом.

В п периодов входной последовательности укладывается (п+1) период выходной последовательности и fпyль- сов. Совпадающие И№1ульсы этих последовательностей называют первыми.

После второго входного импульса формируется третий выходной импульс и после i-ro входного и lпyльca (1 - i Гп) формируется (i+1)-ri выходной импульс.

Для формирования выходноГ) после- довател1,ности в устройстве используется генератор 1 опорной частоты Ср 7 fgtix причем код выходного периода равен К(,,д .

Таким образом, для получения кода К вы необходимо частоту Е поделить на (п+1) и подсчитать количество имп 71ьсов за п входньсх периодов, для чего сигнал с выхода генератора 1 опорной частоты поступает на первый дeJШтeль 2 частоты на (п+1) и с его выхода на счетньи вход счетчика 4, формирующего код К . по пр.ошествии п периодов входног о сигнала, определяемых с помощью второго делителя 5 частоты на п и формирователя 6 импульсов.

Синхронизация первого делителя 2 частоты и счетчика 4 осуществляется сигналами с выхода формирователя 6 импульсов, который формирует сигнал через каждые п периодов входного сигнала. Следовательно, сигнал с выхода формирователя 6 импульсов совпадает с каждым первым импульсом входной последовательности.

Формирование кода задержки ЛТ (uTj - задержка между i-м входными (i+1)-M выходным импульсами) осуществляется во втором вычитающем счетчике 14, в которьа по импульсу с выхода формирователя 6 записывает

51

ся код К , со гчетчика 4, а на счетный вход его поступает сигнал черет элемент И 9 с делителя 2 частоты на п+1,

Код г адержки JT| с выхода второго вьг1 итаюш,его счетчика 14 переписывается в первый вычитающий счетчик 3 для формирования импульсов выходной последовательности. Перевод первого вычитающего счетчика 3 из режима записи в режим счета осуществляется с помощью RS-триггера 11 при поступлении на его вход установки очередного импульса входной последовательности через элемент 16 задержки.

На счетньп вход вьмитающего счетчика 3 подается сиг нал с генератора

I. При этом вьпитаюппи счетчик 3 досчитывает до нуля и формирует на своем выходе импульс, который через элемент 11ЛИ 10 nocTVTiaeT на выход устройства, переключает RS-триггер

IIв нулевое состояние, а вычитающий счетчик 3 переводит в режим записи очеред1юго кода.

Формула и т (J G р е т е в и я

Умножитель частоты с дробным коэффициентом умножения, содержащий генератор опорной частоты, первьт делител частоты, первый вычи Т аюгщи,) счетчик, счетный,вход первого делителя частоты соединен с выходом генератора опорной частоты, счетчик, счет ный вход которого соединен с выходом псфвого делителя частоты, второй делитель частоты, формирователь имггульса, и.нфор- мационпые входы которого соединены с информационными выходами второго делителя частоты, ппшу обнуления, которая соединена с входом установки в О BTopoi o делителя частоты, первый и второй элементы И, первый элемент ИЛИ, RS-триггер, входную щи10

24

15

0

25

0

5

0

5

756

ну, первьп1 вход первого элемента Н соединен с выходом RS-триггера и входом разрешения первого вычитающего счетчика, вход установки в О которого соединен с выходом первого элемента И, а выход - с входом установки в О RS-триггера и первым входом первого элемента ИЛИ, выход которого соединен с выходной шиной устройства, а второй вход - с выходом формирователя импульсов, о т л и - ч а ю щ и и с я тем, что, с целью повышения точности умножения путем формирования равномерной выходной последовательности импульсов, синх-. ронизованной входными импульсами, в него введены второй вычитающий счетчик, второй элемент ИЛИ, входы которого соединены с информационными выходами второго вычитающего счетчика и информа1Ц1онными входами первого вычитающего счетчика, а выход соединен с первым входом второго элемента И, второй вход которого соединен с выходом первого делителя частоты, а выход - с входом обратного счета второго вычитаю цего счетчика, информационные входы которого соединены с информадионными выходами счетчика, а вход установки в О соединен с входом установки в О первого делителя частоты и выходом формирователя, первый элемент задержки, вход которого соединен с входной шиной устройства, а выход - со счетным входом второго делителя частоты и входом установки в 1 RS-триггера, и второй элемент задержки, вход которого соединен с выходом формирователя, а выход - с входом установки в О счетчика, причем вход обратного счета первого вычитающего счетчика соединен с выходом генератора опорной частоты, а второй вход первого элемента И соединен с входной шиной устройства.

Авторы

Даты

1989-07-07—Публикация

1987-03-25—Подача