резистора соединен с вторым выводом четвертого резистора, второй вьшод второго резистора соединен с вторым выводом пятого резистора, второй вывод третьего резистора соединен с вторым выводом шестого резистора и является первым входом коммутатора, . вторым входом которого является второй вывод первого резистора, третьим

входом коммутатора является второй вывод второго резистора, первым выходом коммутатора является эмиттер шестого транзистора, коллектор которого является первым вьшодом коммутатора, вторым выводом которого является коллектор третьего транзистора, эмиттер которого является вторым выходом коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Электронное телеграфное реле | 1984 |

|

SU1256192A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В БИПОЛЯРНЫЙ КОД | 2002 |

|

RU2218660C2 |

| Транзисторный инвертор | 1991 |

|

SU1815775A1 |

| СТАБИЛИЗИРОВАННЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ С ЦИФРОВЫМИ МИКРОСХЕМАМИ | 1991 |

|

RU2014713C1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2005 |

|

RU2287219C1 |

| ПРЕОБРАЗОВАТЕЛЬ ОДНОПОЛЯРНЫХ СИГНАЛОВ В РАЗНОПОЛЯРНЫЕ | 2007 |

|

RU2329593C1 |

| Транзисторный инвертор | 1988 |

|

SU1818673A1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2002 |

|

RU2233022C1 |

1. УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ЦИФРОВОЙ ИНФОРМАЦИИ, содержащее триггер, первый и второй входы которого подключены к первым входам первого и второго элементов И, вторые входы которых соединены соответственно с первым и вторьм выходами триггера, инвертор, трансформатор и первый, второй, третий и четвертый резисторы, отличающееся тем, что, с целью повышения объема передаваемой информации по одной линии связи, введены коммутатор, пятый, шестой и седьмой резисторы, два диода, дифференциальный усилртель и вьтрямитель, входы которого соединены с выходами дифференциального усилителя, первый вход которого соединен с первым выводом первого резистора и с первым выходом коммутатора, второй выход которого соединен с вторым входом дифференциального усилителя и с первым выводом второго резистора, второй вывод которого подключен ко второму вьгооду первого резистора, к первому выводу третьего резистора и к первому выводу четвертого резистора, второй вывод- которого заземлен, второй вывод третьего резистора подключен к положительному выводу источника питания, причем первь вывод коммутатора подключен к первому выводу пятого резистора и к перво у выводу шестого резистора, второй вывод которого соединен с первым выводом трансформатора и с катодом первого диода, анод которого соединен с анодом второго диода, катод которого соединен в вторым выводом трансформатора и с первым выводом седьмого резистора, второй вывод которого соединен с вторым выводом пятого резистора и с вторым выводом коммутатора, первый вход которого соединен с вы- ходом инвертора, вход которого соединен с первым и вторым входами триггера, третий вход которого сое(Л динен с третьими входами первого и . второго элементов И, выходы которых подключены соответственно к эторому S и третьему входам коммутатора. с 2. Устройство по п. 1, отличающееся тем, что коммута- , тор содержит шесть резисторов и I шесть транзисторов, базы которых подключены к первым выводам соответX) ственно первого, второго, третьего, четвертого, пятого и шестого резис:п торов, причем коллектор первого транзистора подключен к положительному вьшоду источника питания и к коллектору второго транзистора, эмиттер которого соединен с Коллектором третьего транзистора и с коллектором четвертого транзистора, эмиттер которого заземлен и соединен с эмиттером пятого транзистора, коллектор которого соединен с эмиттером первого транзистора и с коллектором шестого транзистора, второй вывод первого

f

Изобретение относится к технике связи и может быть использовано в . системах цифровой передачи информации.

Известно устройство для передачи информации, содержащее триггер,вход которого соединен с первыми входами первого и второго элементов И-НЕ, вторые входы которых подключены к соответствующим выходам триггера, выходы первого и второго элементов И-НЕ соединены с входами преобразователей, выходной согласующий блок, переключатели тока, два инвертора и источник опорных напряжений lj .

Недостатком устройства является сложность конструкции.

Наиболее близким техническим решением к изобретению является устройство, содержащее триггер, первьй и второй входы которого подключены к первым входам первого и второго элементов И, вторые входы которых соединены соответственно с первым и вторым выходами триггера, ин ртор, трансформатор и первый, второй третий и четвертый резисторы 2j.

Однако известное устройство обладает недостаточным объемом передаваемой информации по одной линии связи.

Цель изобретения - повьщ ение объема передаваемой информации по одной линии связи.

Для достижения цели в устройство для передачи и приема цифровой инфомации, содержащее триггер, первый и второй входы которого подключены к. первым входам первого и второго элементов И, вторые входы которых соединены соответственно с первым и

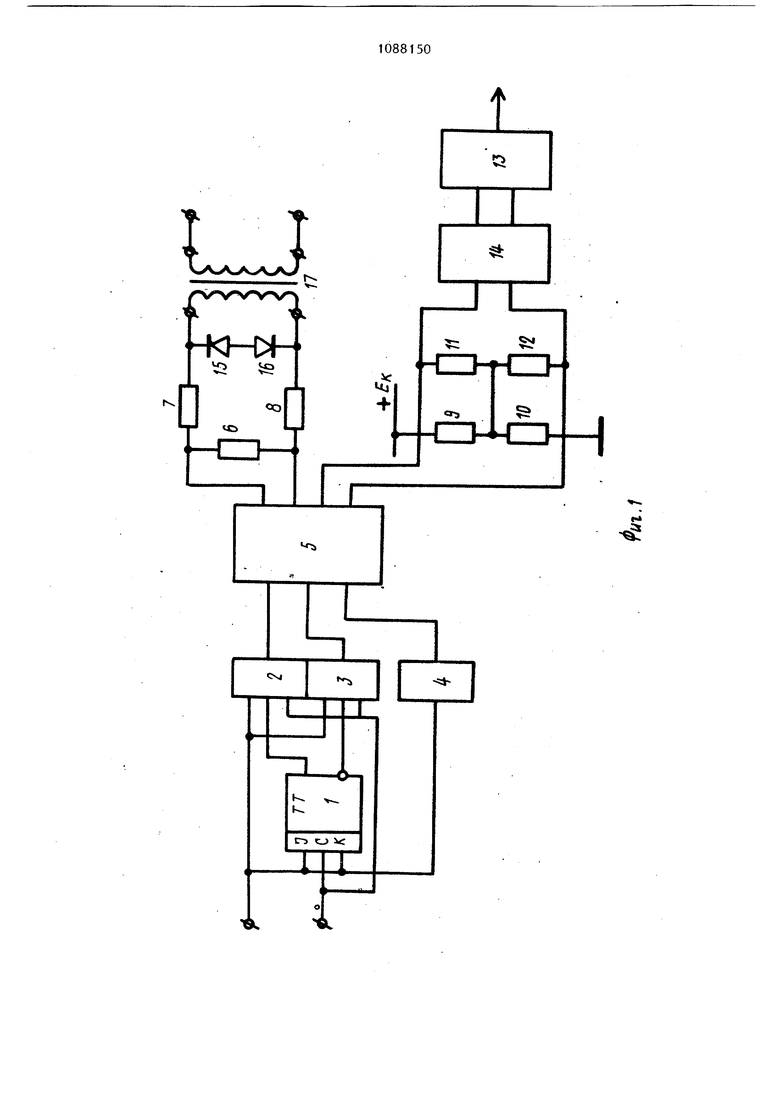

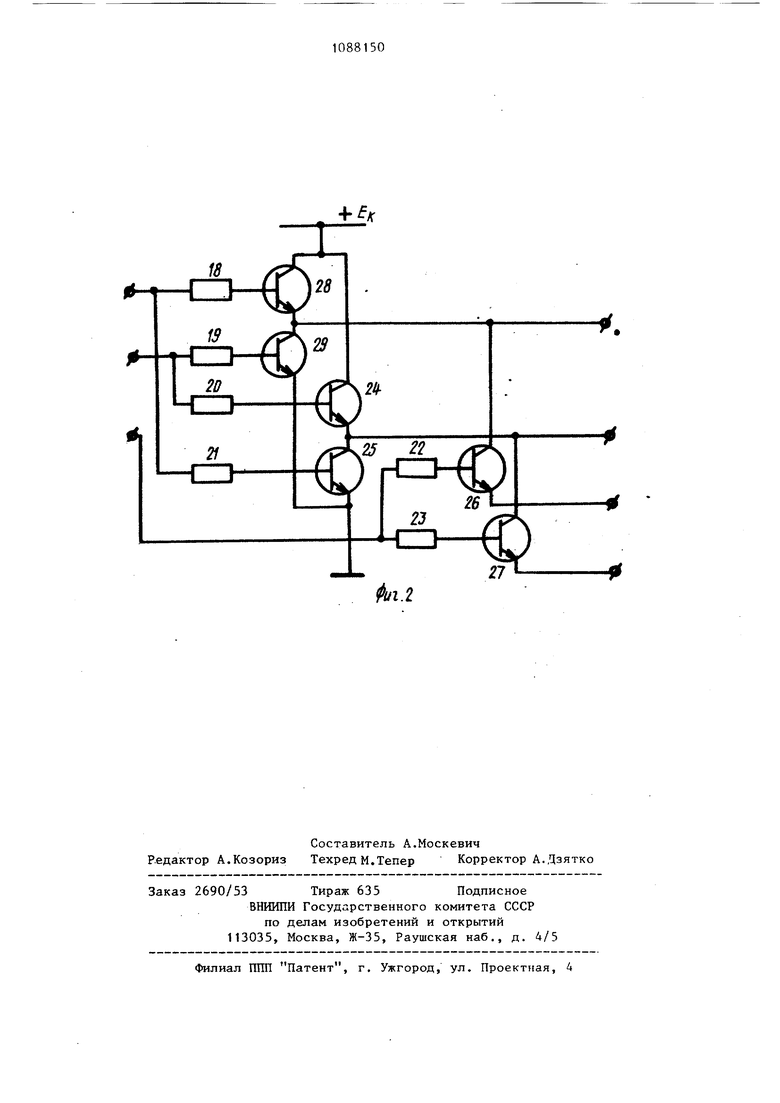

вторым выходами триггера, инвертор, трансформатор и первый, второй, третий и четвертый резисторы, введены коммутатор, пятый, шестой и седьмой резисторы, два диода, дифференциальный усилитель и выпрямитель, входы которого соединены с выходами дифференциального усилителя, первый вход которого соединен с первым выводом первого резистора и с первым выходом коммутатора, второй выход которого соединен с вторым входом дифференциального усилителя и с первым выводом второго резистора, второй вывод которого подключен к второму выводу первого резистора, к первому выводу третьего резистора и к.первому выводу четвертого резистора, второй вывод которого заземлен, второй вывод третьего резистора подключен к положительному выводу источника питания, причем первый вывод коммутатора подключен к первому выводу пятого резистора и к первому выводу шестого резистора, второй вывод которого соединен с первым вьшодом трансформатора и с катодом первого диода, анод которого соединен с анодом второго диода, катод которого соединен с вторым вьгеодом трансформатора и с первым выводом седьмого резистора, второй вывод которого соединен с вторым вьгеодом пятого резистора и с вторьм выводом коммутатора, первый вход которого соединен с выходом инвертора, вход которого соединен с первым и вторым входами триггера, третий вход которого соединен с третьими входами первого и второго элементов И, выходы которых подключены соответственно к второму и третьему входам коммутато ра. При этом коммутатор содержит шесть резисторов и шесть транзисторов, базы которых подключены к первым выводам соответственно первого, второго, третьего, четвертого, пято го и шестого резисторов, причем кол лектор первого транзистора подключен к положительному выводу источника питания и к коллектору второго транзистора, эмиттер которого соединен с коллектором третьего транзистора и с коллектором четвертого транзистора, эмиттер которого заземлен и соединен с эмиттером пятого транзистора, коллектор которого соединен с эмиттером первого транзистора и с коллектором шестого транзистора, второй вывод первого резистора соединен с вторым выводом четвертого резистора, второй вывод второго резистора соединен -с вторым выводом пятого резистора, второй вывод третьего резистора соединен с вторым выводом шестого резистора и является первым входом коммутатора, вторым входом которого является второй вывод первого резистора, третьим входом коммутатора является второй вьгеод второго резистора, пер вым выходом коммутатора является эмиттер шестого траизистора, коллек тор которого является первым выводо коммутатора, вторым выводом которого является колллектор третьего транзистора, эмиттер которого являе ся вторым выходом коммутатора. На фиг. 1 изображена структурная электрическая схема предложенного устройства; на фиг. 2 - структурная электрическая схема коммутатора. Предложенное устройство для пере дачи и приема цифровой информации содержит триггер 1, элементы И 2 и 3, инвертор 4, коммутатор 5, резисторы 6 - 12, выпрямитель 13, дифференциальный усилитель 14, диоды 15 и 16 и трансформатор 17. Коммутатор содержит резисторы 18 - 23 и транзисторы 24 - 29. Устройство работает следующим образом. На первый и второй входы триггера 1 поступают информационные бинар ные СР1гналы, а на третий вход - так товые импульсы, период следования которых Т, а длительность Т/2 (где Т - длительность передачи одного бита информации). Триггер под воздействием тактовых импульсов изменяет свое состояние только в..том случае, если на его первом и втором входах сигнал логической 1. Сигналы с первого и второго выходов триггера 1 поступают, соответст7 венно, на вторые входы элементов И 2 и 3, на первые и третьи входы которых, соответственно, поступают информационные двоичные сигналы и тактовые сигналы. Благодаря такой схеме соединения при наличии на входе бинарного сигнала, равного логической 1, на выходах элементов И 2 и 3 формируются чередующиеся сигналы, длительность которых равна длительности бита информации. Причем, когда на выходе одного из элементов И появляется сигнал, на выходе другого в это время отсутствует. Так формируются биполярные полупериодные сигналы. Для формирования квазитроичных сигналов необходимо отсоединить тр«тьи входы элементов И 2 и 3 от третьего входа триггера 1 и соединить с вторьвии входами элементов И 2 и 3. I При этом на выходах элементов И 2 и 3 будут формироваться чередующиеся сигналы, длительность которых равна длительности бита информации. Сигналы с выходов элементов И 2 и 3 поступают на второй и третий входы коммутатора 5. На первый вход коммутатора 5 подаются с инвертора 4 инвертированные информационные сигналы, которые при сигнале логической 1 на информационном входе отключают первый и второй выходы от первого и второго выводов коммутатора 5, а при сигнале логического О наоборот подключают. С помощью резисторов 9 и 10 через резисторы 11 и 12 на входы дифференциального усилителя 14 подается напряжение смещения. Передача биполярных сигналов в линию связи осуществляется при наличии на выходах элементов И 2 и 3, соответственно, сигналов логической 1 и логического О или наоборот. Прием биполярных сигналов с линии связи осуществляется при наличии на информационном входе сигналов логического О. При зтом под действием сигнала логической 1, поступающего

с выхода инвертора 4 на первый вход коммутатора, первый вывод последнего подсоединяется к его первому выходу, а второй вывод коммутатора 5 подключается к второму своему выходу

Коммутатор 5 работает следуюйщм образом.

Передача биполярных сигналов в линию связи осуществляется при наличии на втсфом и третьем входах, соот ветственно, сигналов логической 1 и логического О или логического О и логической 1, а на первом входе сигнала логического О. Под действием сигнала логического О на первом входе транзисторы 26 и 27 закрьшаются и отключают первый и второй входы дифференциального усилителя 14 от линии связи. При наличии на первом и третьем входах коммутатора 5 сигналов соответственно логической 1 и логического О образуется цепь тока: плюс источника питания - открытый транзистор 28 первый вывод - нагрузка - второй вывод - открытый транзистор 25 - земляная шина. В линию связи подается импульс одной полярности. При наличии на первом и третьем входах сигналов соответственно логического О и логической 1 образуется цепь тока: плюс источника питания - открытый транзистор 24 - второй вьгаод нагрузка - первый вывод - открытый транзистор 29 - земляная шина. В линию связи подается импульс другой полярности.

Прием биполярных сигналов осу ществляется при наличии на втором и третьем входах сигналов логического О, а на первом входе сигналов логической 1. При этом транзисторы 24, 25, 28 и 29 закрыты, а транзисторы 26 и 27 открУты. Биполярные сигналы с первого и второго вьюодов через открытые транзисторы 26 и 27 поступают на первый и второй выходы.

Таким образом, предложенное устройство осуществляет как передачу, так и прием биполярных сигнёшов по одной линии связи, что повышает объем передаваемой информации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 557689, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство формирования биполярного полупериодного сигнала из бинарного сигнала | 1976 |

|

SU686644A3 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-04-23—Публикация

1982-10-25—Подача