равления, отличают, ееся тем, что, с целью повьшепия быстродействия, в устройство введен блок сравнения кодов, а в блок управлениявосьмой элемент И, элемент И-НЕ триггер, причем прямой выход триггера соединен с третьим входом четвертого элемента И, а инверсный выход триггера соединен с вторым входом второго элемента И и с первым входом восьмого элемента И, второй вход которого соединен с выходом первого элемента И, первый вход элемента И-НЕ соединен с вторым входом третьего элемента И, третий вход восьмого элемента И соединен с входом анализа величины делителя блока управления, первый и второй входы мультиплексора соединены соответственно с первым и вторым входами анализа разрядов блока уггравления, второй вход элемента И-11Е соединен с входом управления синхронизацией

блока управления, выход восьмого элемента И соединен с прямым входом триггера, выход элемента И-НЕ соединен с вторым входом первого элемента И, выходы регистров делимого и делителя соединены соответственно с первым и вторым информационными входами блока сравнения кодов, тзыход которого соединен с входом анализа величины делителя блока управления, первый и второй выходы старших разрядов регистра делимого соединены соотве ственно с первым и вторым входами анализа разрядов делимого блока управления ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для деления двоичных чисел | 1984 |

|

SU1233139A1 |

| Устройство для деления | 1983 |

|

SU1141403A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| Устройство для деления двоичных чисел | 1984 |

|

SU1203514A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для деления двоичных чисел | 1975 |

|

SU646331A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ДВОИЧНЫХ ЧИСЕЛ, содержащее регистры делимого, делителя, частного, сумматор, реверсивный счетчик, дешифратор нуля, элемент ИЛИ, блок управления, содержащий мультиплексор, генератор импульсов, семь элементов И, кольцевой сдвигающий регистр, счетчик циклов, элемент НЕ,причем выход генератора импульсов соединен с первым входом .первого элемента И,выход которого соединен с первым входом второго, третьего и четвертого элементов И, второй вход четвертого элемента И соединен с выходом элемента НЕ, вход которого соединен с вторым входом третьего элемента Мне выходом счетчика циклов, вход которого соединен с первым входом пятого элемента И, и первым выходом кольцевого сдвигающего регистра, второй выход которого соединен с первым входом шестого и седьмого элементов И, второй вход пятого, шестого и второй вход седьмого элементов И соединены соответственно с первьсм и вторым выходами мультиплексора, выход четвертого элемента И соединен с яходом запуска кольцевого сдвигающего регистра, третий и второй выходы кол1 цевого сдвигающего регистра являются соответственно первым и вторым выходами блока управления, выходы пятого, шестого, седьмого элементов И являются соответственно третьим, четвертым и пятым выходами блока управления, выходы второго и третьего элементов И являются соответственно шестым и седьмым выходами блока управления, причем первый выход блока управления соединен с входом управления сдвигом регистра делимого и с первым входом элемента ИЛИ, информационный вход регистра делимого соединен с выходом сумматора, выход регистра делимого соединен с первым i информационным входом сумматора, второй Информационный вход которого сое(Л С динен с выходом регистра делителя, второй выход блока управления соединен с входом управления передачей кода регистра делимого, выход элемента ИЛИ соединен с входом сдвига регистра частного, вход записи которого соединен с третьим выходом блока управления, четвертый выход которого соединен с входом управления переносо ю ю сом сумматора и с входом передачи обратного кода регистра делителя, вход передачи прямого кода которого соединен с пятым выходом блока управipik ления, шестой выход которого соединен с входом сдвига регистра делителя и с суммирующим входом реверсивного счетчика, седьмой выход блока управления соединен с вторым входом элемента ИЛИ и с вычитающим входом реверсивного счетчика, выходы разрядов реверсивного счетчика соединены соответственно с входами дешифратора нуля, выход которого соединен с входом управления синхронизацией блока уп

1

Изобретение относится к области вы числительной техники и может быть использовано в специализированных вычислительных машинах.

Известно устройство для деления двоичных чисел, содержащее параллельный сумматор с п старшими и и +1 младшими разрядами, г) разрядные сумматоры частного и делителя, элемент задержки, триггеры, генератор импуль сов, дешифраторы, блок управления, блок разрешения сдвига, элемент И, соединенные определенным образом для выполнения операции деления двух двоичных чисел lj.,.

Недостатком данного устройства является большой объем оборудования и сложность алгоритма операции деления .

Наиболее близким по технической сущности и достигаемому эффекту к изобретению является устройство для деления, содержащее регистр делимого регистр делителя, регистр частного, сумматор, блок управления, элемент 1ШИ, дешифратор нуля, реверсивный счетчик, блок регистрации нуля и единицы, первый выход блока управления соединен с управляющим входом регистра делимого, информационный вход которого соединен с выходом сумматора, выход регистра делимого соединен с

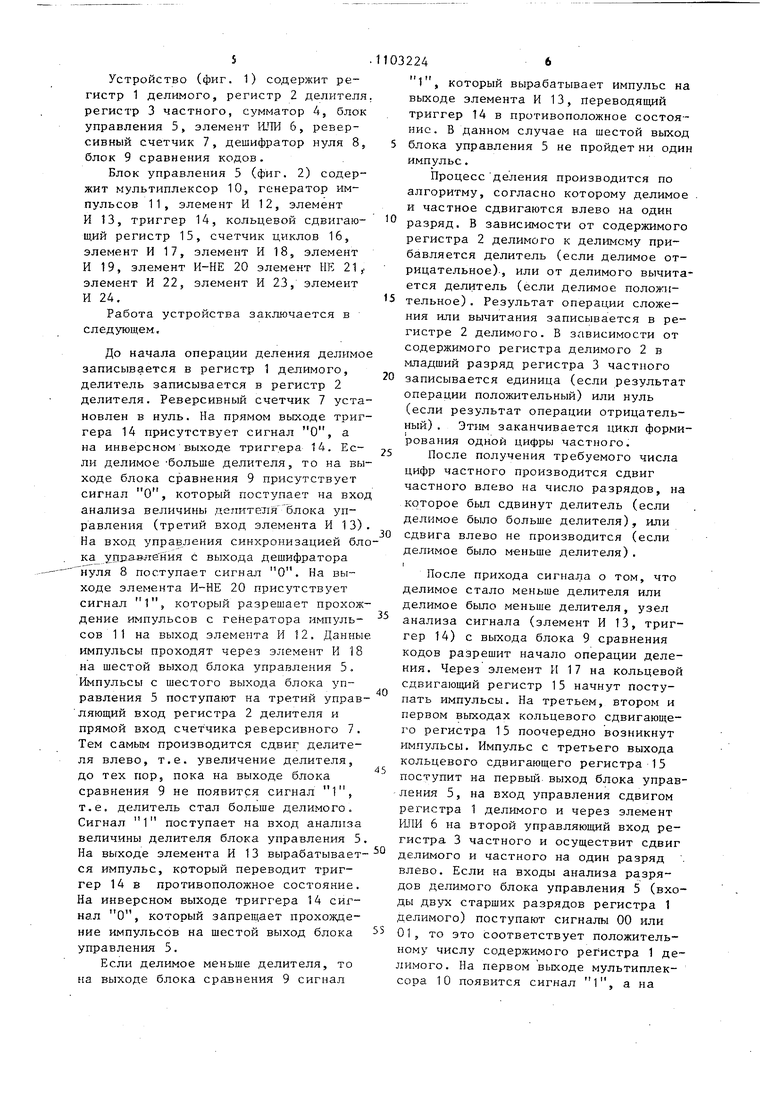

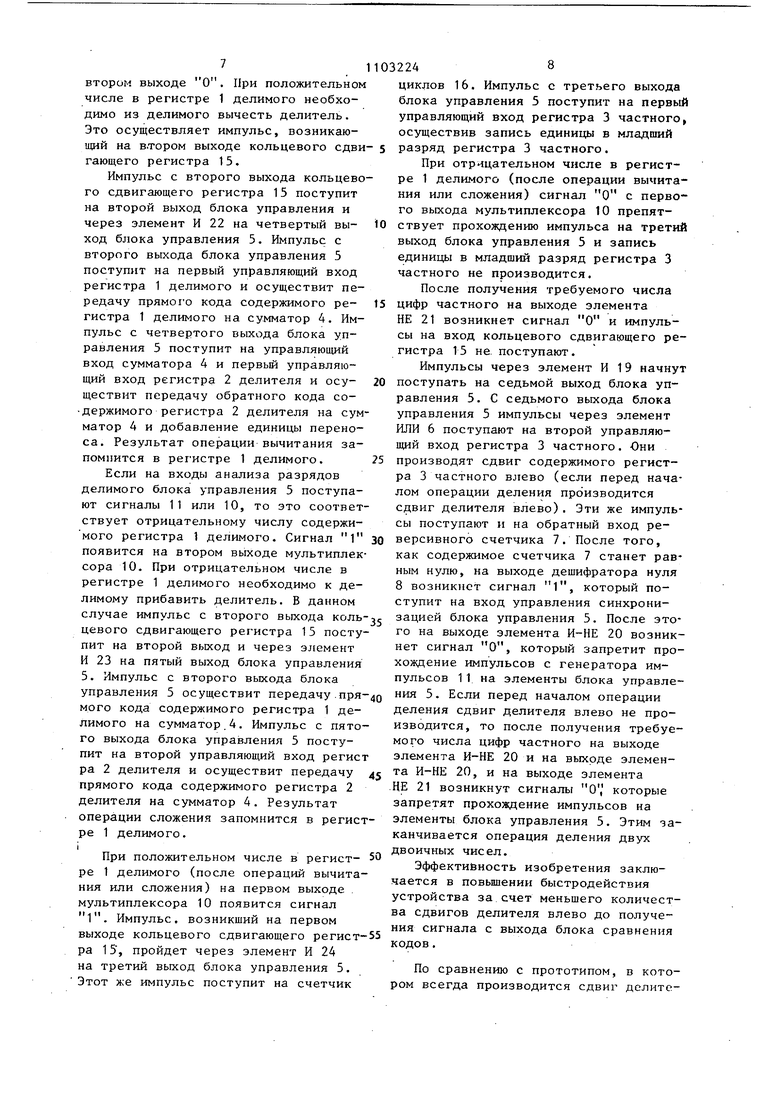

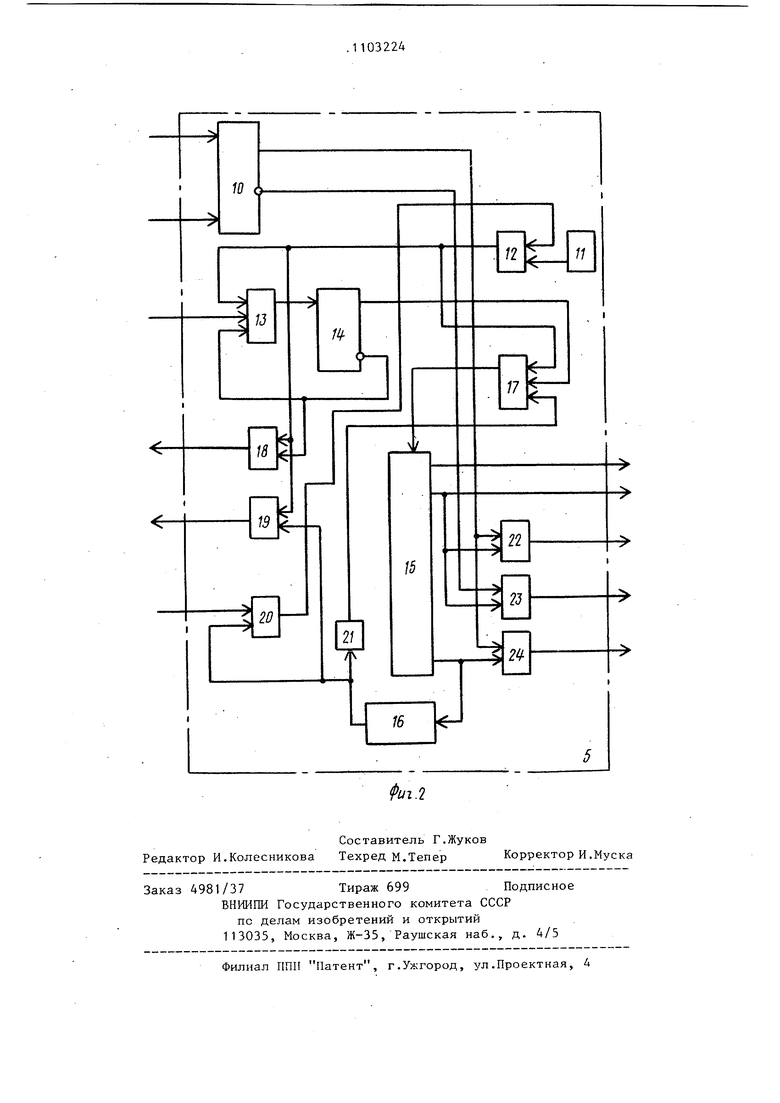

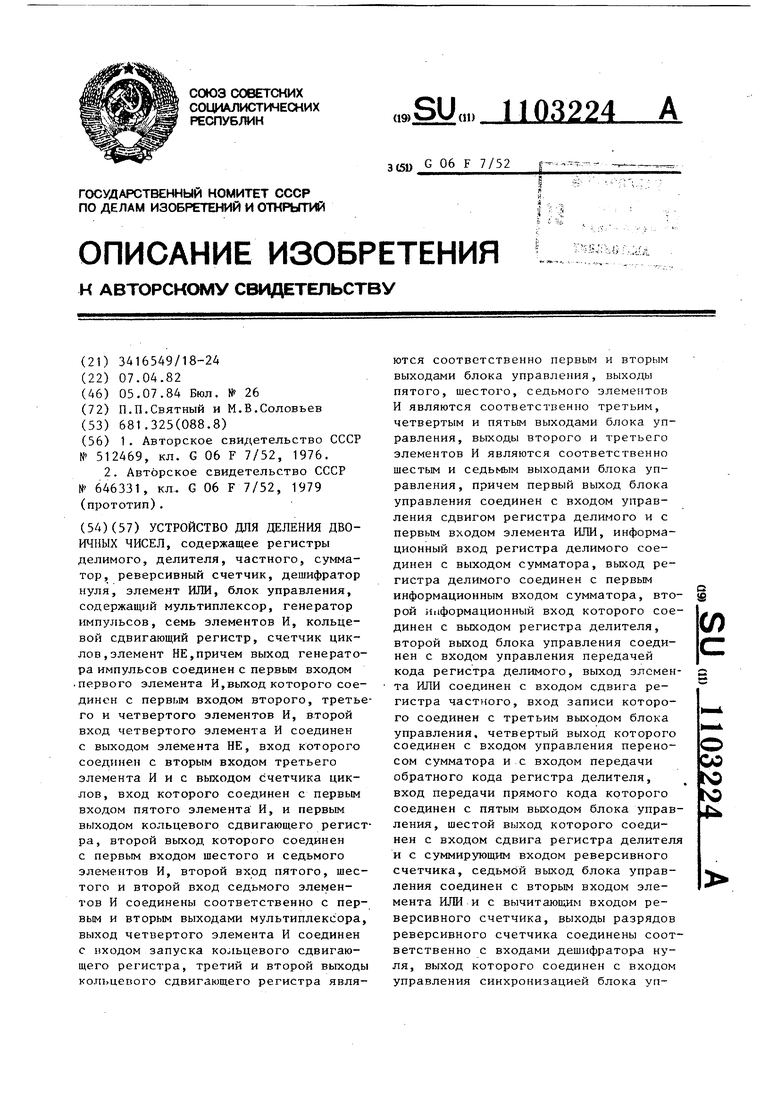

первьпу информационным входом сумматора, второй информационный вход которого соединен с выходом регистра делителя, управляющий вход сумматора соединен с вторым выходом блока управления, третий выход .которого соединен с первым управляющим входом регистра делителя, выход старшего разряда сумматора соединен с входом блока управления, четвертый выход которого соединен с первым управляющим входом регистра частного, первый выход блока регистрации нуля и единицы соединен с вторым входом регистра делителя и суммирующим входом реверсивного счетчика, второй выход блока регистрации нуля и единицы соединен с первым входом элемента ИЛИ и вычитающим входом реверсивного счетчика, третий выход блока регистрации нуля и единицы соединен с установочным входом реверсивного счетчика, выходы которого соединены с входами дешифратора нуля, выход которого соединен с первым входом блока регистрации нуля и единицы, второй вход которого соединен с выходом старшего разряда регистра делителя, пятый выход блока управления соединен с вторым входом элемента ИЛИ, выход которого соединен с вторым управляющим входом регистра частного 2J , Недостатком данного устройства является низкое быстродействие. Цель изобретения - повышение быст родействия устройства для деления. Поставленная цель достигается тем что в устройство для деления двоичных чисел, содержащее регистры делимого, делителя., частного, сумматор, реверсивный счетчик, дешифратор нуля, эле мент ИЛИ, блок управления, содержащий мультиплексор, генератор импульсов, семь элементов И, кольцевой сдвигающий регистр, счетчик циклов, элемент НЕ, причем выход генератора импульсов соединен с первым входом первого элемента И, выход которого соединен с первым входом второго, третьего и четвертого элементов И, второй вход четвертого элемента И соединен с выходом элемента НЕ, вход которого соединен с вторым входом третьего элемента И и с выходом счет чика циклов, вход которого соединен с первым входом пятого элемента И, и первым выходом кольцевого сдвигающего регистра, второй выход которого соединен с первым входом шестого и седьмого элементов И, второй вход пятого, шестого и второй вход седьмо го элементов И соединены соответст венно с первым и вторым выходами мультиплексора, выход четвертого эле мента И соединен с входом запуска кольцевого сдвигающего регистра, тре тий и второй выходы кольцевого сдайгающего регистра являются соответственно первым и вторым выходами блока управления, выходы пятого, шестого, седьмого элементов И являются соотве ственно третьим, четвертым и пятым выходами блока управления, выходы второго и третьего, элементов И являются соответственно шестым и седьмым выходами блока управления, причем пе вый выход блока управления соединен с входом управления сдвигом регистра делимого и с первым входом элемента ИЛИ, информационный вход регистра делимого соединен с выходом сумматор выход регистра делимого соединен с первым информационным входом суммато ра, второй информационный вход которого соединен с выходом регистра делителя, второй выход блока управления соединен с входом управления передачей кода регистра делимого, выход элемента ИЛИ соединен с входом сдвига регистра частного, вход запи.1 4 си которого соединен с третьим выходом блока управления, четвертый выход которого соединен с входом управления переноса сумматора и с входом передачи обратного кода регистра делителя , вход передачи прямого кода которого соединен с пятым выходом блока управления, шестой выход которого соединен с входом сдвига регистра делителя и с суммирующим входом реверсивного счетчика, седьмой выход блока управления соединен с вторым входом элемента ИЛИ и с вычитающим входом реверсивного счетчика, выходы разрядов реверсивного счетчика соединены соответственно с входами дешифратора нуля,, выход которого соединен с входом управления синхронизацией блока управления, введен блок сравнения кодов, а в блок управления восьмой элемент И, элемент И-ЯЕ, триггер, причем прямой выход триггера соединен с третьим входом четвер.того элемента И, а инверсный выход триггера соединен с вторым входом второго элемента И и с первым входом восьмого элемента И, второй вход которого соединен с выходом первого элемента И, первый вход элемента И-НЕ соединен с вторЬ1м входом третьего элемента И, третий вход восьмого элемента И соединен с входом анализа величины делителя блока управления, первый и второй входы мультиплексора соединены соответственно с первым и вторым входами анализа разрядов блока управления, второй вход элемента И-НЕ соединён с входом управления синхронизацией блока управления, выход восьмого элемента И соединен с прямым входом триггера, выход элемента И-НЕ соединен с вторым входом первого элемента И, выходы регистров делимого и делителя соединены соответственно с первым и вторым информационными входами блока сравнения кодов, выход которого соединен с вхохом анализа величины делителя блока управления, первый и второй выходы старших разрядов регистра делимого соединены соответственно с первым и вторым входами анализа разрядов делимого блока управления. На фиг. 1 изображена структурная схема устройства для деления двоичных чисел; на фиг. 2 - функциональная схема блока управления. Устройство (фиг. 1) содержит регистр 1 делимого, регистр 2 делителя регистр 3 частного, сумматор 4, блок управления 5, элемент ИЛИ 6, реверсивный счетчик 7, дешифратор нуля 8, блок 9 сравнения кодов. Блок управления 5 (фиг. 2) содержит мультиплексор 10, генератор импульсов 11, элемент И 12, элемент И 13, триггер 14, кольцевой сдвигающий регистр 15, счетчик циклов 16, элемент И 17, элемент И 18, элемент И 19, элемент И-НЕ 20 элемент НЕ 21 элемент И 22, элемент И 23, элемент И 24. Работа устройства заключается в следующем. До начала операции деления делимо записывается в регистр 1 делимого, делитель записывается в регистр 2 делителя. Реверсивный счетчик 7 уста новлен в нуль. На прямом выходе триг гера 14 присутствует сигнал О, а на инверсном выходе триггера 14. Если делимое -больше делителя, то на вы ходе блока сравнения 9 присутствует сигнал О, который поступает на вхо анализа величины делителя блока управления (третий вход элемента И 13) На вход управления синхронизацией бл ка упдавления с выхода дешифратора нуля 8 поступает сигнал О. На вы ходе элемента И-НЕ 20 присутствует сигнал 1, который разрешает прохож дение импульсов с генератора импуль сов 11 на выход элемента И 12. Данны импульсы проходят через элемент И 18 на шестой выход блока управления 5. Импульсь с шестого выхода блока управления 5 поступают на третий управ ляющий вход регистра 2 делителя и прямой вход счетчика реверсивного 7. Тем самьгм производится сдвиг делителя влево, т.е. увеличение делителя, до тех пор, пока на выходе блока сравнения 9 не появится сигнал 1, т.е. делитель стал больше делимого. Сигнал 1 поступает на вход анализа величины делителя блока управления 5 На выходе элемента И 13 вырабатывает

ся импульс, который переводит триггер 14 в противоположное состояние. На инверсном выходе триггера 14 сигнал О, который запрещает прохождение импульсов на шестой выход блока управления 5.

Если делимое меньше делителя, то на выходе блока сравнения 9 сигнал

влево. Если на входы анализа разрядов делимого блока управления 5 (входы двух старших разрядов регистра 1 делимого) поступают сигналы 00 или 01, то это соответствует положительному числу содержимого регистра 1 делимого. На первом выходе мультиплексора 10 появится сигнал 1, а на 2246 1, который вырабатывает импульс на выходе элемента И 13, переводящий триггер 14 в противоположное состояние. В данном случае на шестой выход блока управления 5 не пройдет ни один импульс. Процессделения производится по алгоритму, согласно которому делимое . и частное сдвигаются влево на один разряд. В зависимости от содержимого регистра 2 делимого к делимому прибавляется делитель (если делимое отрицательное)., или от делимого вычитается делитель (если делимое положительное). Результат операции сложения или вычитания записывается в регистре 2 делимого. В зависимости от содержимого регистра делимого 2 в младший разряд регистра 3 частного записывается единица (если результат операции положительный) или нуль (если результат операции отрицательный) . Этим заканчивается цикл формирования одной цифры частного. После получения требуемого числа цифр частного производится сдвиг частного влево на число разрядов, на которое был сдвинут делитель (если делимое было больше делителя), или сдвига влево не производится (если делимое было м-еньше делителя) . t После прихода сигнала о том, что делимое стало меньше делителя или делимое было меньше делителя, узел анализа сигнала (элемент И 13, триггер 14) с выхода блока 9 сравнения кодов разрешит начало операции деления. Через элемент И 17 на кольцевой сдвигающий регистр 15 начнут поступать импульсы. На третьем, втором и первом выходах кольцевого сдвигающего регистра 15 поочередно возникнут импульсы. Импульс с третьего выхода кольцевого сдвигающего регистра 15 поступит на первый выход блока управления 5, на вход управления сдвигом регистра 1 делимого и через элемент ШШ 6 на второй управляющий вход регистра 3 частного и осуществит сдвиг делимого и частного на один разряд

втором выходе О. При положительном исле в регистре 1 делимого необхоимо из делимого вычесть делитель. Это осуществляет импульс, возникающий на в.тором выходе кольцевого сдви- 5 гающего регистра 15.

Импульс с второго выхода кольцевого сдвигающего регистра 15 поступит на второй выход блока управления и через элемент И 22 на четвертый вы- 10 од блока управления 5, Импульс с второго выхода блока управления 5 поступит на первый управляющий вход регистра 1 делимого и осуществит передачу прямого кода содержимого ре- 15 гистра 1 делимого на сумматор 4. Импульс с четвертого выхода блока управления 5 поступит на управляющий вход сумматора 4 и первый управляющий вход регистра 2 делителя и осу- 20 ществит передачу обратного кода содержимого регистра 2 делителя на сумматор 4 и добавление единицы переноса. Результат операции вычитания запомнится в регистре 1 делимого. 25

Если на входы анализа разрядов делимого блока управления 5 поступают сигналы 11 или 10, то это соответствует отрицательному числу содержимого регистра 1 делимого. Сигнал 1 ЗО появится на втором выходе мультиплексора 10. При отрицательном числе в регистре 1 делимого необходимо к делимому прибавить делитель. В данном случае импульс с второго выхода коль- с цевого сдвигающего регистра 15 поступит на второй выход и через э; емент И 23 на пятый выход блока управления 3. Импульс с второго выхода блока управления 5 осуществит передачу.пря-4о мрго кода содержимого регистра 1 делимого на сумматор.4. Импульс с пятого выхода блока управления 5 поступит на второй управляющий вход регист ра 2 делителя и осуществит передачу 45 прямого кода содержимого регистра 2 елителя на сумматор 4. Результат операции сложения запомнится в регистре 1 делимого.

При положительном числе в регист- 50 ре 1 делимого (после операций вычитания или сложения) на первом выходе мультиплексора 10 появится сигнал 1. Импульс, возникший на первом выходе кольцевого сдвигающего регист-55 ра 15, пройдет через элемент И 24 на третий выход блока управления 5. Этот же импульс поступит на счетчик

циклов 16. Импульс с третьего выхода блока управления 5 поступит на первый управляющий вход регистра 3 частного, осуществив запись единицы в младший разряд регистра 3 частного.

При отрицательном числе в регистре 1 делимого (после операции вычитания или сложения) сигнал О с первого выхода мультиплексора 10 препятствует прохождению импульса на третий выход блока управления 5 и запись единицы в младший разряд регистра 3 частного не производится.

После получения требуемого числа цифр частного на выходе элемента НЕ 21 возникнет сигнал О и импульсы на вход кольцевого сдвигающего регистра 15 не. поступают.

Импульсы через элемент И 19 начнут поступать на седьмой выход блока управления 5. С седьмого выхода блока управления 5 импульсы через элемент ИЛИ 6 поступают на второй управляющий вход регистра 3 частного. Они производят сдвиг содержимого регистра 3 частного влево (если перед началом операции деления производится сдвиг делителя влево). Эти же импульсы поступают и на обратный вход реверсивного счетчика 7. После того, как содержимое счетчика 7 станет равным нулю, на выходе дешифратора нуля 8 возникнет сигнал 1, который поступит на вход управления синхронизацией блока управления 5. После этого на выходе элемента И-НЕ 20 возникнет сигнал О, который запретит прохождение импульсов с генератора импульсов 11 на элементы блока управления 5. Если перед началом операции деления сдвиг делителя влево не производится, то после получения требуемого числа цифр частного на выходе элемента И-НЕ 20 и на выходе элемента И-НЕ 20, и на выходе элемента НЕ 21 возникнут сигналы О, которые запретят прохождение импульсов на элементы блока управления 5. Этим заканчивается операция деления двух двоичных чисел.

Эффектийность изобретения заключается в повьшении быстродействия устройства за счет меньшего количества сдвигов делителя влево до получения сигнала с выхода блока сравнения кодов.

По сравнению с прототипом, в котором всегда производится сдвиг делителя влево до появления единицы в старшем разряде делителя (в случае, когда в старшем разряде делителя нуль), в данном устройстве сдвиг делителя производится на меньшее количество

разрядов и даже может не производиться. Аналогично сдвиг частного происходит на меньшее количество разрядов или не происходит совсем.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для деления двоичных чисел с фиксированной запятой | 1974 |

|

SU512469A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для деления двоичных чисел | 1975 |

|

SU646331A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-15—Публикация

1982-04-07—Подача