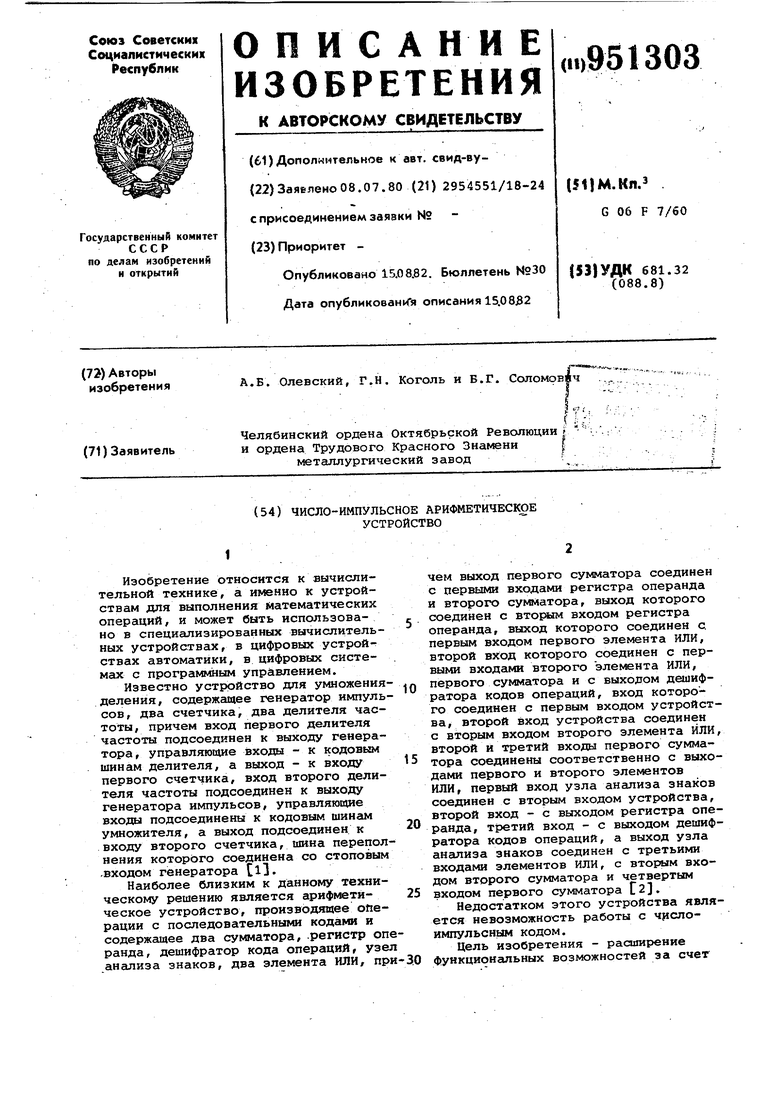

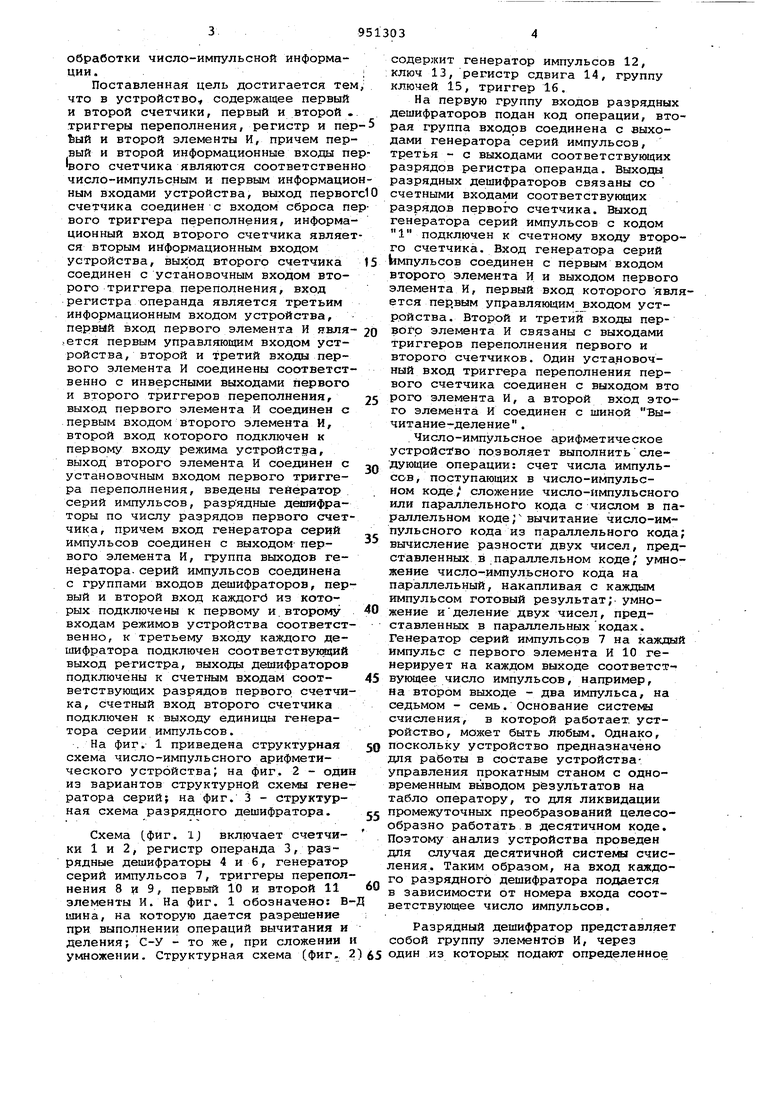

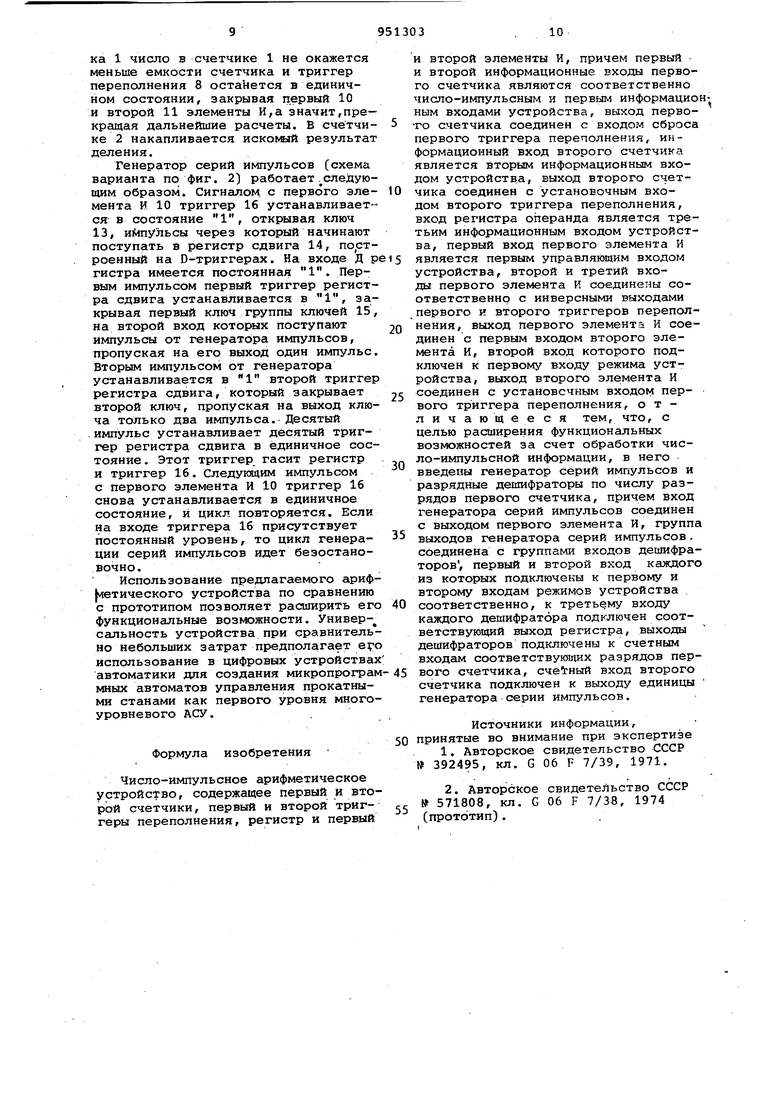

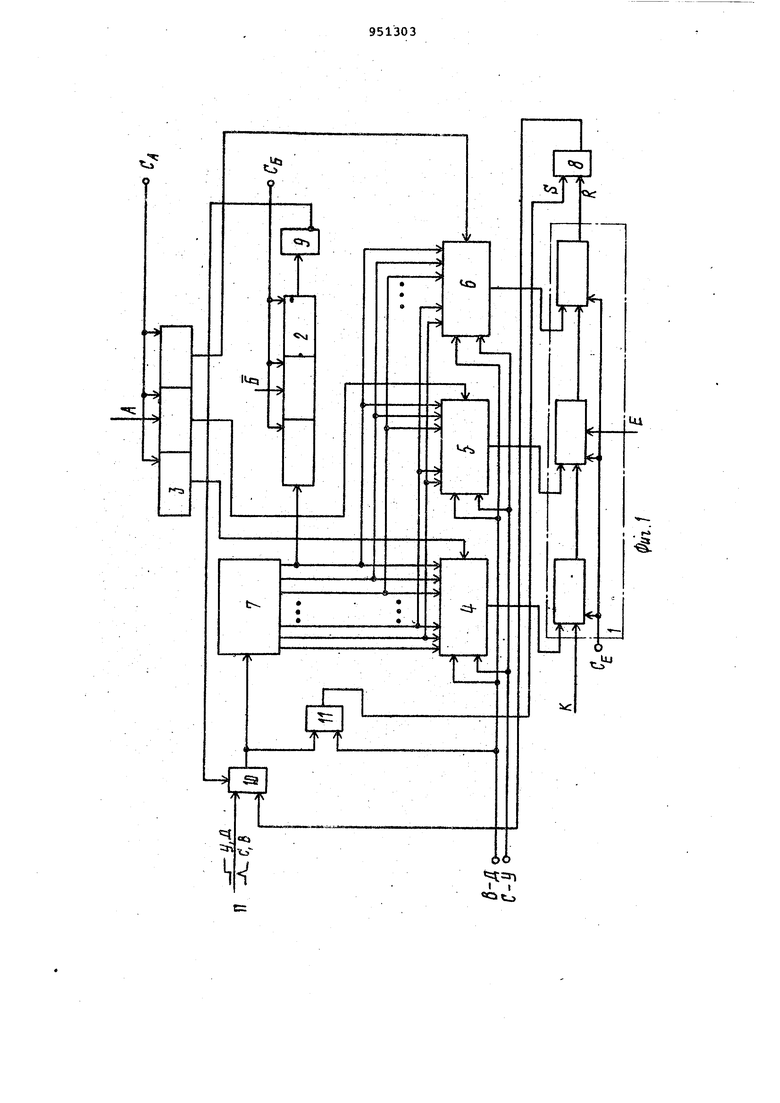

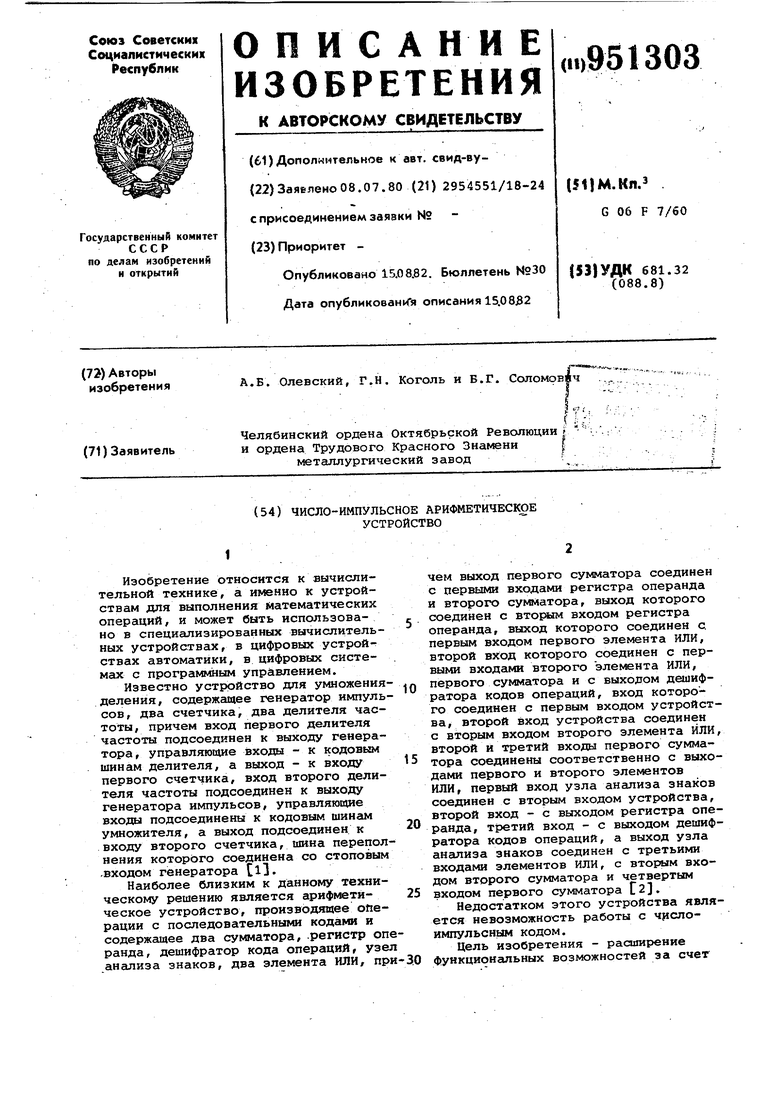

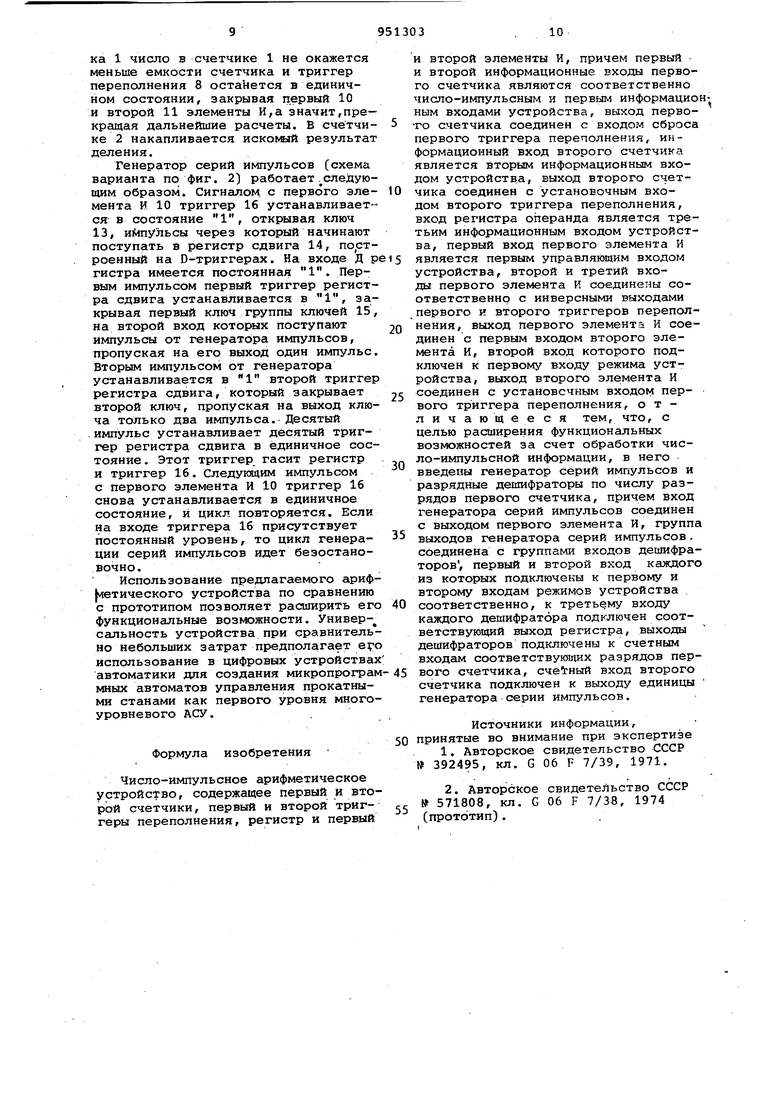

Изобретение относится к вычислительной технике, а именно к устройствам для выполнения математических операций, и может быть использовано в специализированных вычислительных устройствах, в цифровых устройствах автоматики, в цифровых системах с программным управлением. Известно устройство для умножения деления, содержащее генератор импуль сов, два счетчика, два делителя частоты, причем вход первого делителя частоты подсоединен к выходу генератора, управляющие входы - к кодовым шинам делителя, а выход - к входу первого счетчика, вход второго делителя частоты подсоединен к выходу генератора импульсов, управляющие входы подсоединены к кодовым шинам умножителя, а выход подсоединен к входу второго счетчика, шина перепол нения которого соединена со стоповым .входом генератора tl3. Наиболее близким к данному техническому решению является арифметическое устройство, производящее otieрации с последовательными кодами и содержсццее два сумматора, .регистр оп ранда, дешифратор кода операций, узе анализа знаков, два элемента ИЛИ, пр чем выход первого сумматора соединен с первыми входами регистра операнда и второго сумматора, выход которого соединен с BTojaiM входом регистра операнда, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с первыми входгиш второго элемента ИЛИ, первого сумматора и с выходом дешифратора кодов операций, вход которого соединен с первым входом устройства, второй вход устройства соединен с вторым входом второго элемента ИЛИ, второй и третий входы первого сумматора соединены соответственно с выходами первого и второго элементов ИЛИ, первый вход узла анализа знаков соединен с вторым входом устройства, второй вход - с выходом регистра операнда, третий вход - с вЕлходом дешифратора кодов операций, а выход узла анализа знаков соединен с третьими вxoдaNal элементов ИЛИ, с вторым входом второго сумматора и четвертым входом первого сумматора С 2. Недостатком этого устройства является невозможность работы с числоимпульсным кодом. Цель изобретения - расширение функционёшьных возможностей за счет обработки число-импульсной информации. Поставленная цель достигается тем что в устройство содержащее первый и второй счетчики, первый и второй . триггеры переполнения, регистр и пер Ъый и второй элементы И, причем первый и второй информационные входы пе шого счетчика являются соответственн число-импульсным и первым информацио ным входами устройства, выход первог счетчика соединен с входом сброса пе вого триггера переполнения, информационный вход второго счетчика являет ся вторым информационным входом устройства, выход второго счетчика соединен с установочным входом второго триггера переполнения, вход регистра операнда является третьим информационным входом устройства, первай вход первого элемента И явля ется первым управляющим входом устройства, второй и третий входы первого элемента И соединены соответственно с инверсными выходами первого и второго триггеров переполнения, выход первого элемента И соединен с первым входом второго элемента И, второй вход которого подключен к первому входу режима устройства, выход второго элемента И соединен с установочным входом первого триггера переполнения, введены гейератор серий импульсов, разрядные дешифраторы по числу разрядов первого счетчика, причем вход генератора серий импульсов соединен с выходом первого элемента И, группа выходов генератора, серий импульсов соединена с группами входов дешифраторов, первый и второй вход каждогб из которых подключены к первому и второму входам режимов устройства соответственно, к третьему входу каждого деишфратора подключен соответствукрщй выход регистра, выходы дешифраторов подключены к счетным входам соответствующих разрядов первого, счетчика, счетный вход второго счетчика подключен к выходу единицы генератора серии импульсов. . На фиг. 1 приведена структурная схема число-импульсного арифметического устройства; на фиг, 2 - один из вариантов структурной схемы гене ратора серий; на фиг. 3 - структурная схема разрядного дешифратора. Схема (фиг. 1J включает счетчики 1 и 2, регистр операнда 3, разрядные дешифраторы 4 и 6, генератор серий импульсов 7, триггеры перепол нения 8 и 9, первый 10 и второй 11 элементы И. На фиг. 1 обозначено: В шина, на которую дается разрешение при выполнении операций вычитания и деления; С-У - то же, при сложении умножении. Структурная схема (фиг. содержит генератор импульсов 12, ключ 13, регистр сдвига 14, группу ключей 15, триггер 16. На первую группу входов разрядных дешифраторов подан код операции, вторая группа входов соединена с выходами генератора серий импульсов, третья - с выходами соответствующих разрядов регистра операнда. Выходы разрядных дешифраторов связаны со счетными входами соответствукедих разрядов первого счетчика. Выход генератора серий импульсов с кодом 1 подключен к счетному входу второго счетчика. Вход генератора серий Ьмпульсов соединен с первым входом второго элемента И и выходом первого элемента И, первый вход которого является пер, вым управляющим входом устройства. Второй и третий входы первого элемента И связаны с выходами триггеров переполнения первого и второго счетчиков. Один установочный вход триггера переполнения первого счетчика соединен с выходом вто рого элемента И, а второй вход этого элемента И соединен с шиной Вычитание-деление . .Число-импульсное арифметическое устройство позволяет выполнить следующие операции: счет числа импульсов , поступающих в число-импульсном коде, сложение число-импульсного или параллельного кода с числом в параллельном коде; вычитание число-импульсного кода из параллельного кода; вычисление разности двух чисел, представленных в параллельном коде, умножение число-импульсного кода на параллельный, накапливая с каждым импульсом готовый результат;- умножение иделение двух чисел, представленных в параллельных кодах. Генератор серий импульсов 7 на каждый импульс с первого элемента И 10 генерирует На каждом выходе соответствующее число импульсов, например, на втором выходе - два импульса, на седьмом - семь. Основание системы счисления, в которой работает, устройство, может быть любым. Однако, поскольку устройство предназначено для работы в составе устройствауправления прокатным станом с одновременным выводом результатов на табло оператору, то для ликвидации промежуточных преобразований целесообразно работать в десятичном коде. Поэтому анализ устройства проведен для случая десятичной системы счисления. Таким образом, на вход каждого разрядного дешифратора подается в зависимости от номера входа соответствующее число импульсов. Разрядный дешифратор представляет собой группу элементов И, через один из которых подают определенное

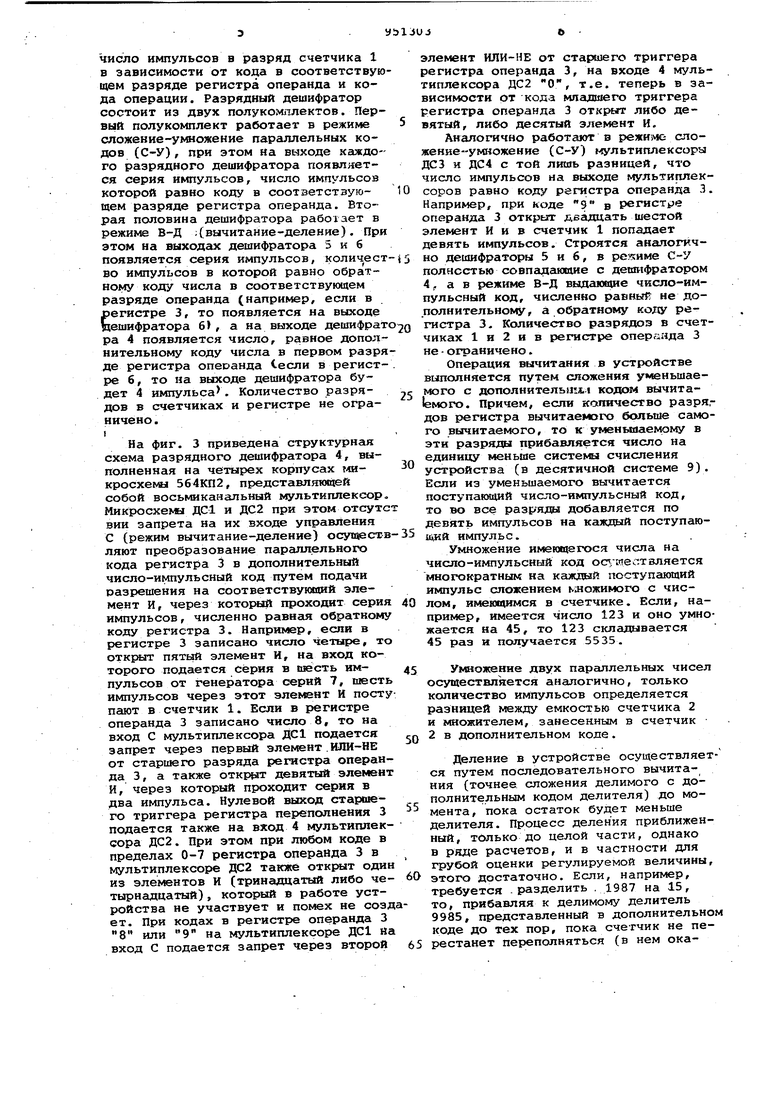

число импульсов в разряд счетчика 1 в зависимости от кода в соответствующем разряде регистра операнда и кода операции. Разрядный дешифратор состоит из двух полукомплектов. Первый полукомплект работает в режиме сложение-умножение параллельных кодов (С-У), при этом На выходе каждого разрядного дешифратора появляется серия импульсов, число импульсов которой равно коду в соответствуютем разряде регистра операнда. Вторая половина дешифратора работает в режиме В-Д ;(вычитание-деление). При этом на выходах дешифратора 5 и 6 появляется серия импульсов, количест во импульсов в которой равно обратному коду числа в соответствующем разряде операнда (например, если в регистре 3, то появляется на выходе дешифратора 6), а на выходе дешифрат ра 4 появляется число, равное дополнительному коду числа в первом разряде регистра операнда 1если в регистре 6, то на выходе дешифратора будет 4 импульса. Количество разрчдов в счетчиках и регистре не ограничено. I

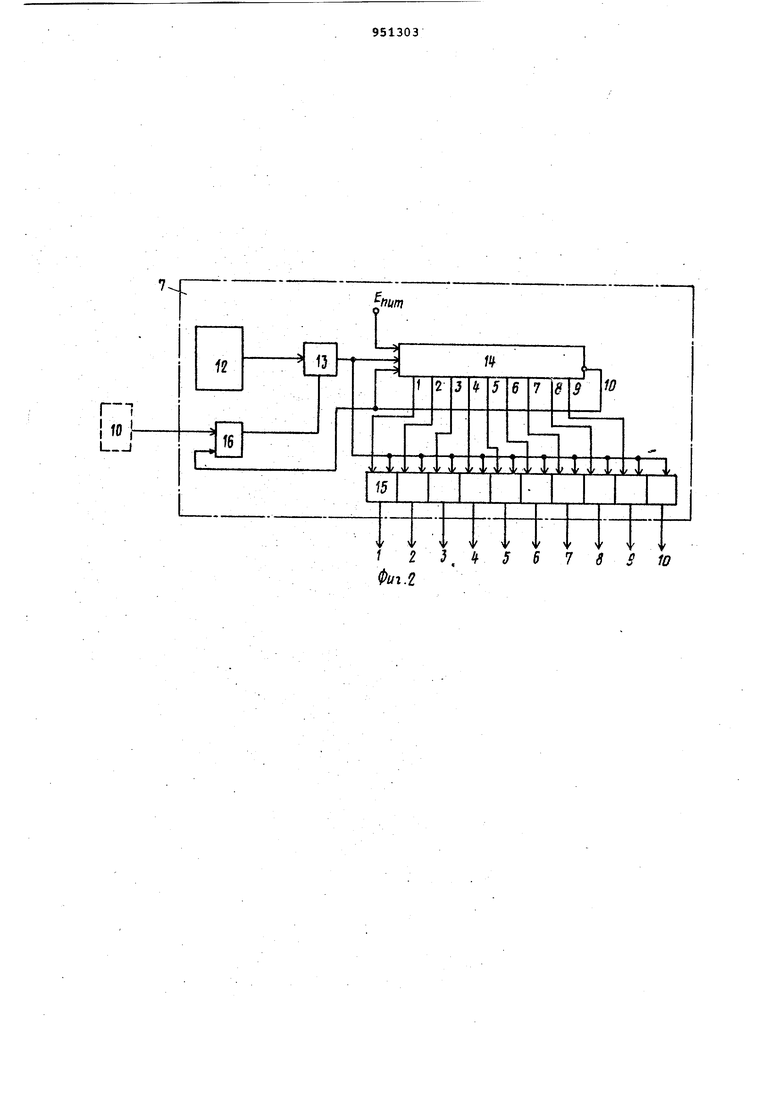

На фиг. 3 приведена структурная схема разрядного дешифратора 4, выполненная на четырех корпусах t«iкросхемы 564КП2, представляющей собой восьмиканальный мультиплексор Микросхемы ДС1 и ДС2 при этом отсутс ВИИ запрета на их входе управления С (режим вычитание-деление) осуществ ляют преобразование параллельного кода регистра 3 в дополнительный число-импульсный код путем подачи разрешения на соответствующий элемент И, через который проходит серия импульсов, численно равная обратному коду регистра 3. Например, если в регистре 3 записано число четыре, то открыт пятьШ элемент И, на вход которого подается серия в шесть импульсов от генератора серий 7, шесть импульсов через этот элемент И поступают в счетчик 1. Если в регистре операнда 3 записано число 8, то на вход С мультиплексора ДС1 подается запрет через первый элемент.ИЛИ-НЕ от старшего разряда регистра операнда 3 , а также открыт девятый элемент И, через который проходит серия в два импульса. Нулевой выход старшего триггера регистра переполнения 3 подается также на вход 4 мультиплексора ДС2. При этом при любом коде в пределах 0-7 регистра операнда 3 в мультиплексоре ДС2 также открыт один из элементов И (тринадцатый либо четырнадцатый), который в работе устройства не участвует и помех не создет. При кодах в регистре операнда 3 8 или 9 на мультиплексоре ДС1 на вход С подается запрет через второй

элемент ИЛИ-НЕ от старшего триггера регистра операнда 3, на входе 4 мультиплексора ДС2 О, т.е. теперь в зависимости от кода младшего триггера регистра операнда 3 открыт либо девятый, либо десятый элемент И,

Аналогично работают в сложение-умножение (С-У) мультиплексора дез и ДС4 с той лишь разницей, что число импульсов на выходе мультиплексоров равно коду регистра операнда 3 Например, при коде 9 в регистре операнда 3 открыт двадцать шестой элемент И и в счетчик 1 попадает девять импульсов. Строятся аналогично дешифраторы 5 и 6, в ре 5:име полностью совпадающие с дешифратором 4,, а в режиме В-Д выдающие число-импульсный код, численно равный не до.полнительномУ, а обратному коду регистра 3. Количество разрядов в счетчиках 1 и 2 и в регистре операнда 3 не -ограниче но.

Операция вычитания в устройстве выполняется путем сложения уменьшаемого с дополнительшл- кодом вычита1емого. Причем, если капичество разрядов регистра вычитаемого больше самого вычитаемого, то к уменьшаемому в эти разряды прибавляется число на единицу меньше системы счисления устройства (в десятичной системе 9). Если из уменьшаемого вычитается поступающий число-импульсный код, то во все разряды добавляется по девять импульсов на каждый поступающий импульс.

Умножение имеющегося числа на число-импульсный код ос гмеатзляется многократным на каждый поступающий импульс сложением ьшожимого с числом, имеющимся в счетчике. Если, например, имеется число 123 и оно умножается на 45, то 123 складывается 45 раз и получается 5535.

Умножение двух параллельных чисел осуществляется аналогично, только количество импульсов определяется разницей между емкостью счетчика 2 и множителем, занесенным в счетчик 2 в дополнительном коде.

Деление в устройстве осуществляется путем последовательного вычитания (точнее сложения делимого с дополнительным кодом делителя) до момента, пока остаток будет меньше делителя. Процесс деления приближенный, до целой части, однако в ряде расчетов, и в частности для грубой оценки регулируемой величины, этого достаточно. Если, например, требуется .разделить .1987 на 15, то, прибавляя к делимому делитель 9985, представленный в дополнительно коде до тех пор, пока счетчик не перестанет переполняться (в нем окажется число 7),мы -получаем частное 132. 1987 + 9985 132 1320007 Устройство работает следующим образом. В режиме счета импульсов импульсы В число-импульсном коде поступают на вход К счетчика 1 и накапливают ся в нем. В режиме сложения двух чисел, есл одно число представлено в параллель ном коде, а другое в число-импульсном, то занося первое число в счетчик 1(Е) и давая на вход К счетчика 1 второе число, мы получаем в счетчике 1 сумму этих чисел. Если оба числа представлены в параллельном коде и расположены - одно в счетчике 1(Е), а второе в регистре операн да (А), то для получения суммы необходимо на шину С - У подать разрешение, на шину В - Д - запрет, а на вход П ключа 13 подать импульс. При этоти- генератор серий импульсов запускается, выдает на выходах серии импульсов, в зависимости от кода в регистре операнда открывается соответствующий элемент И в разрядном дешифраторе, и в разряды счетчика 1 попадает число импульсов, равное ко ду в соответствующих разрядах регист :ра операнда. В счетчике 1 оказывает ся сумма А + Е. При вычитании число-импульсного кода из числа, представленного в па раллельном коде, в счетчик 1 заносится уменьшаемое Е. На шине В - Д разрешение, на С -.У - запрет. В регистр операнда эа;носится А 1. Импульсы вычитаемого поступают на вход П ключа. Первым импульсом через первый элемент И 10 запускается генератор серий импульсов, а также через второй элемент И 11, на втором.входе которого присутствует разрешение с шины В - Д, устанавливается в единичное состояние триггер переполнения 8 (он используется при делении) Разрядные дешифраторы 4-6 пропуска через себя п6 девять импульсов, которые, попадая в счетчик 1, устанавливают в нем код на единицу меньше прежнего (например 028+999 1027), а счетчик 1 при переполнении возвращает триггер переполнения 8 в нулевое состояние. По приходе следующего импульса процесс повторяется. В результате в счетчике 1 накаплива ется число, равное разности уменьшаемого и число-импульсного вычитае мого. При вычислении разности двух чисел, представленных в параллельном коде, уменьшаемое находится в счетчике 1, вычитаемое - в регистре операнда. На шине В - Д - разрешение на С - У - запрет. При подаче на вхо первого элемента И 10 импульса вычитаемое в дополнительном коде прибавляется к уменьшаемому. Полученное в счетчике Число является искомой разностью. При умножении число-импульсного кода на параллельный, множимое записывается в регистр операнда. На шине С - У - разроиение, на В - Д - запрет. С каждым импульсом на входе первого элемента И 10 происходит сложение кода регистра операнда (множимого) с кодом счетчика 1. По приходе последнего импульса множителя в счетчике 1 накапливается искомое произведение чисел. При умножении двух чисел, представленных в параллельных кодах, .множимое (А) заносится в регистр операнда. Множитель (Б) в дополнительном коде заносится в счетчик 2. На вход первого элемента И 10 подается разрешающий сигнал в виде перепада напряжения. Этим перепадом запускается генератор серий импульсов, который начинает суммировать в счетчике 1 содержимое регистра операнда (А) до тех пор, пока не переполнится счетчик 2, и триггер 9 не даст запрет на первый элемент И 10. В результате в счетчике 1 накапливается произведение AsB. Отличие суммирования от умножения заключается в том, что при суммировании дают импульс, а не просто перепад напряжения сигнала. При . делении двух чисел, пред{ставленных в параллельных кодах, делимое (Е) записывается в счетчик 1, делитель (А) - в регистр операнда. На шине. В - Д - разрешение, на С-Узапрет. На вход первого элемента И 10 подается разрешающий сигнал в виде перепада напряжения. Это разрешение запускает генератор серий импульсов 7 и через второй элемент И 11 устанавливает триггер переполнения 8 в единичное состояние. С его выхода сигнал закрывает первый 10 и второй 11 элементы И, снимая установочный уровень со входа триггер.а переполнения 8. Делитель А в обратном коде прибавляется к содержимому счетчика 1, переполняя его и возвращая в нулевое состояние. С выхода триггера переполнения 8 сигнал через первый 10 и второй 11 элементы И снова устанавливает триггер переполнения 8 в единичное состояние. За цикл работы генератора серий импульсов в счетчик 2 поступает один импульс. По окончании цикла генератор серий импульсов запускается вновь, и процесс повторяется до тех пор, пока после очередного цикла сложения обратного . кода делителя с содержимым счетчика 1 число в счетчике 1 не окажется меньше емкости счетчика и триггер переполнения 8 останется в единичном состоянии, закрывая первый 10 и второй 11 элементы И,а значит,прекращая дальнейшие расчеты. В счетчике 2 накапливается искомый результат деления. Генератор серий импульсов (схема варианта по фиг. 2) работает .следующим образом. Сигналом, с первого элемента И 10 триггер 16 устанавливается в состояние открывая ключ 13, И УЛЬСЫ через который начинают поступать в регистр сдвига 14, по строенный на D-триггерах. На входе Д р гистра имеется постоянная 1. Первым импульсом первый триггер регистра сдвига устанавливается в крывая первый ключ группы ключей 15, на второй вход которых поступают импульсы от генератора импульсов, пропуская на его выход один импульс. Вторым импульсом от генератора устанавливается в 1 второй триггер регистра сдвига, который закрывает второй ключ, пропуская на выход ключа только два импульса. Десятый импульс устанавливает десятый триггер регистра сдвига в единичное состояние . Этот триггер гасит регистр и триггер 16. Следующим импульсом с первого элемента И 10 триггер 16 снова устанавливается в единичное состояние, и цикл повторяется. Если на входе триггера 16 присутствует постоянный уровень, то цикл генерации серий импульсов идет безостановочно. Использование предлагаемого ариф «1етического устройства по сравнению с прототипом позволяет расширить его функциональные возможности. Универсальность устройства при сравнитель но небольших затрат предполагает использование в цифровых устройствах автоматики для создания микропрограм мных автоматов управления прокатными станами как первого уровня многоуровневого АСУ. Формула изобретения Число-импульсное арифметическое устройство, содержащее первый и второй счетчики, первый и второй триггеры переполнения, регистр и первый и второй элементы И, причем первый и второй информационные входы первого счетчика являются соответственно число-импульсным и первым информационным входами устройства, выход первого счетчика соединен с входом сброса первого триггера переполнения, информационный вход второго счетчика является вторым информационным входом устройства, выход второго счетчика соединен с установочным входом второго триггера переполнения, вход регистра операнда является третьим информационным входом устройства, первый вход первого элемента И является первым управляющим входом устройства, второй и третий входы первого элемента И соединены соответственно с инверсными выходами первого и второго триггеров переполнения, выход первого элемента И соединен с первым входом второго элемента И, второй вход которого подключен к первому входу режима устройства, выход второго элемента И соединен с установочным входом первого триггера переполнения, отличающее ся тем, что, с целью расширения функциональных возможностей за счет обработки число-импульсной информации, в него введены генератор серий импульсов и разрядные дешифраторы по числу разрядов первого счетчика, причем вход генератора серий импульсов соединен с выходом первого элемента И, группа выходов генератора серий импульсов, соединена с группами входов дешифраторов, первый и второй вход каждого из которых подключены к первому и второму входам режимов устройства . соответственно, к третьему входу каждого дешифратора подключен соответствующий выход регистра, выходы дешифраторов подключены к счетным входам соответствующих разрядов первого счетчика, счетный вход второго счетчика подключен к выходу единицы генератора серии импульсов. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 392495, кл. G 06 F 7/39, 1971. 2. Авторское свидетельство СССР 571808, кл. G 06 F 7/38, 1974 (прототип).

о

t

00

ta

per

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для формирования широкополосного случайного процесса | 1986 |

|

SU1432514A1 |

| Устройство микропрограммного управления | 1987 |

|

SU1539776A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

«м

LI

ш

1

V.

1 t.

L

Ч

00 Хэ

Й

W

66

I I

«о to

1 2 }, i 5 6 7 3 S Ю Фиг.1

Авторы

Даты

1982-08-15—Публикация

1980-07-08—Подача