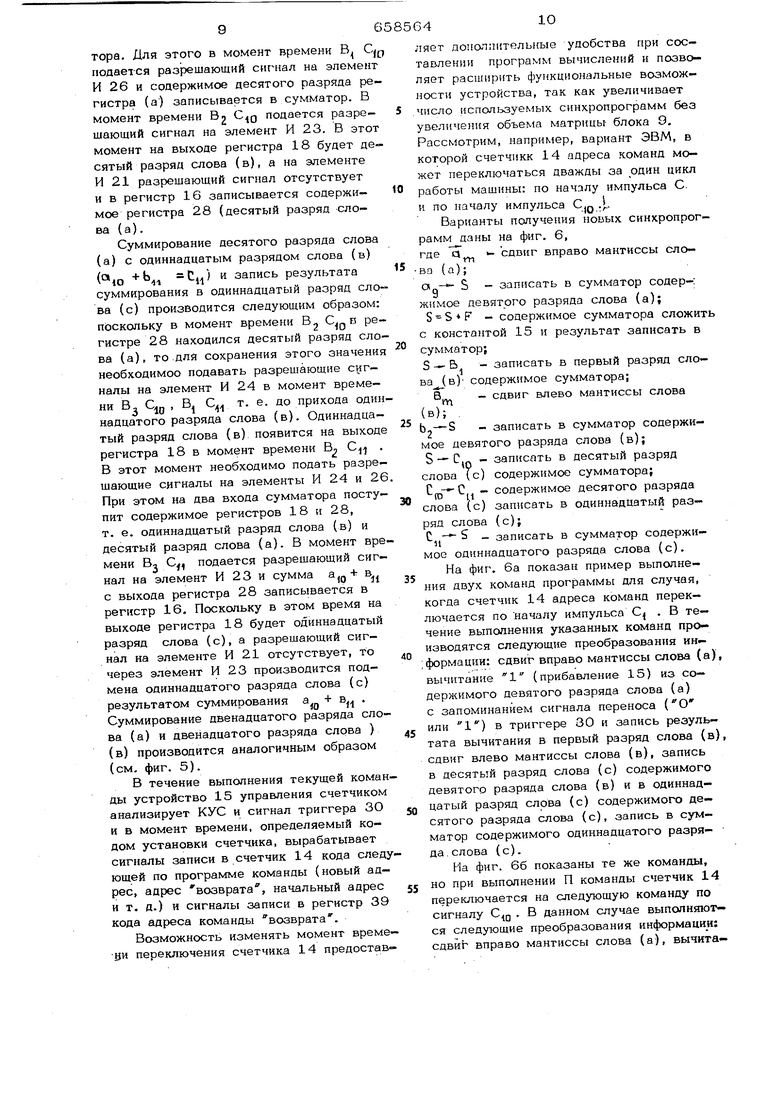

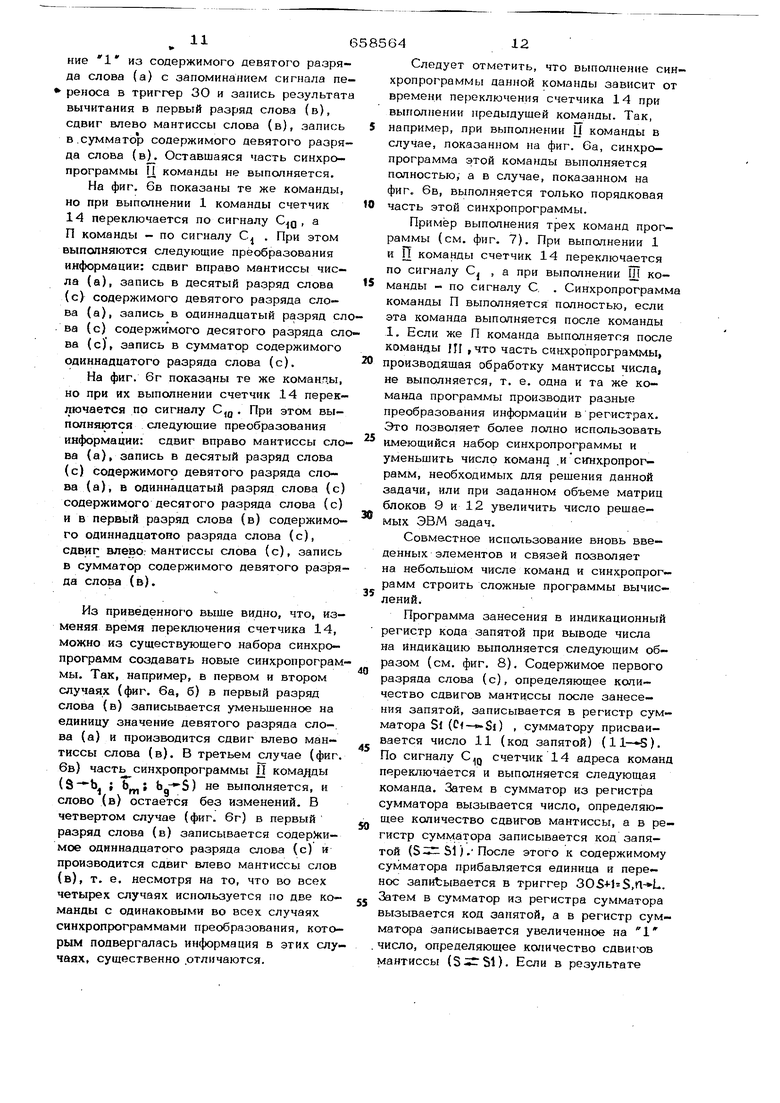

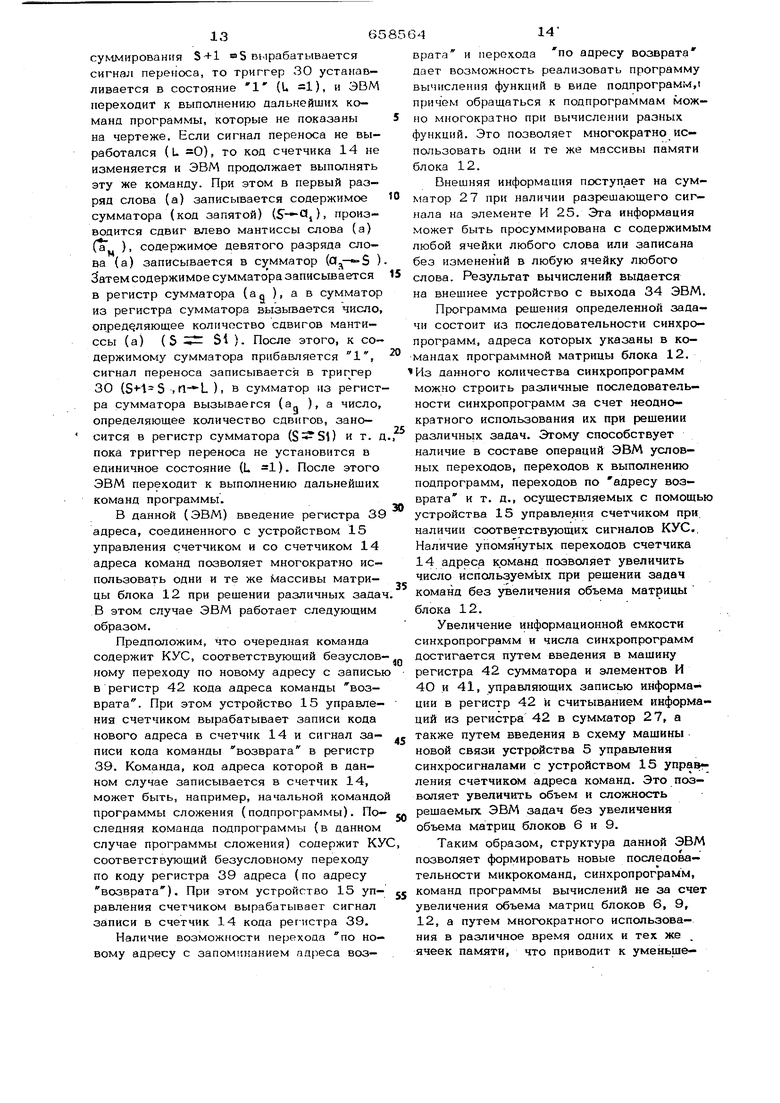

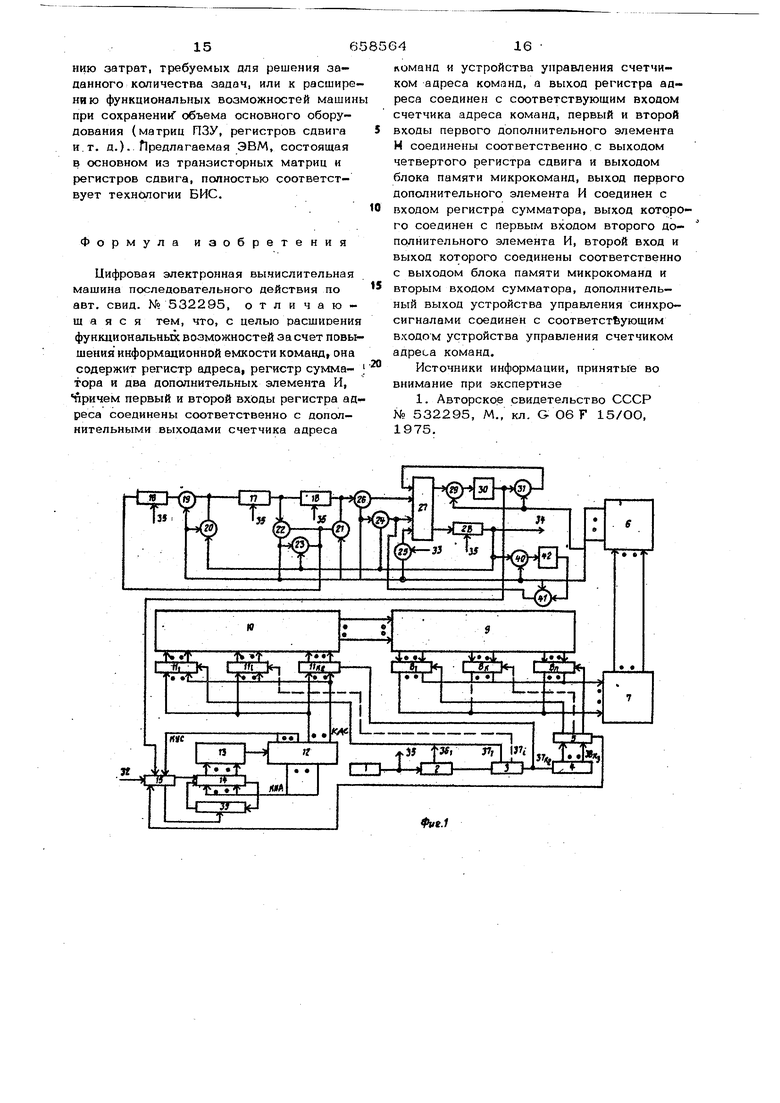

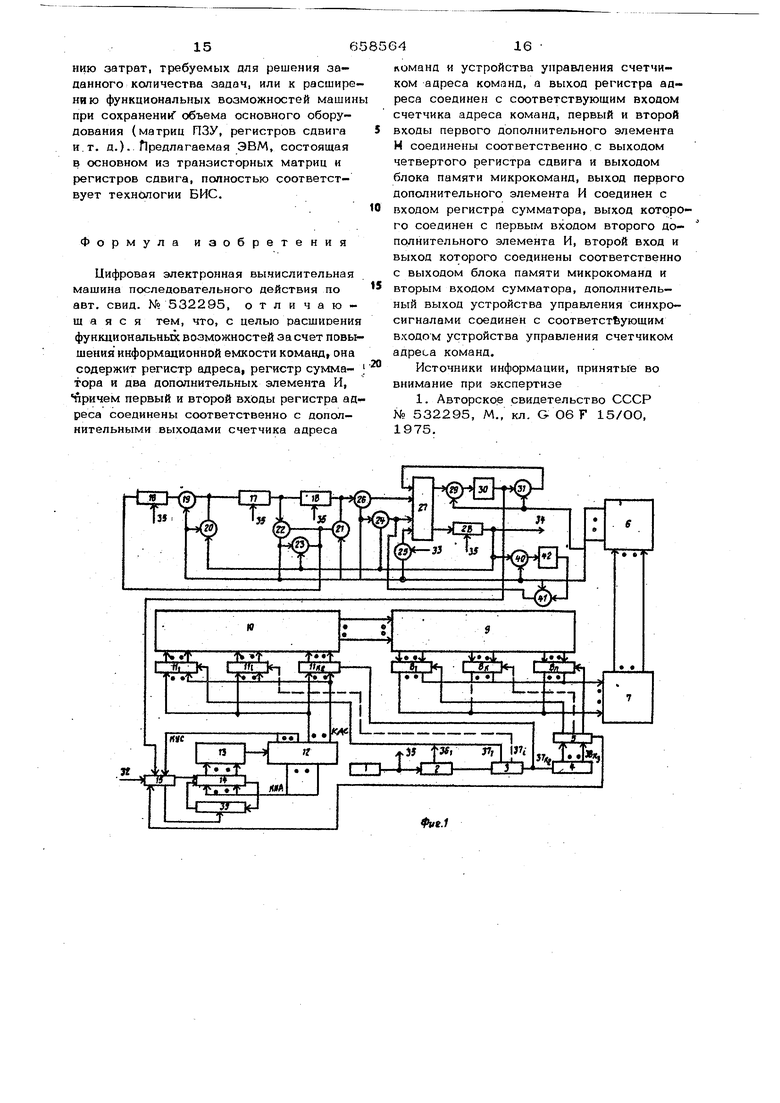

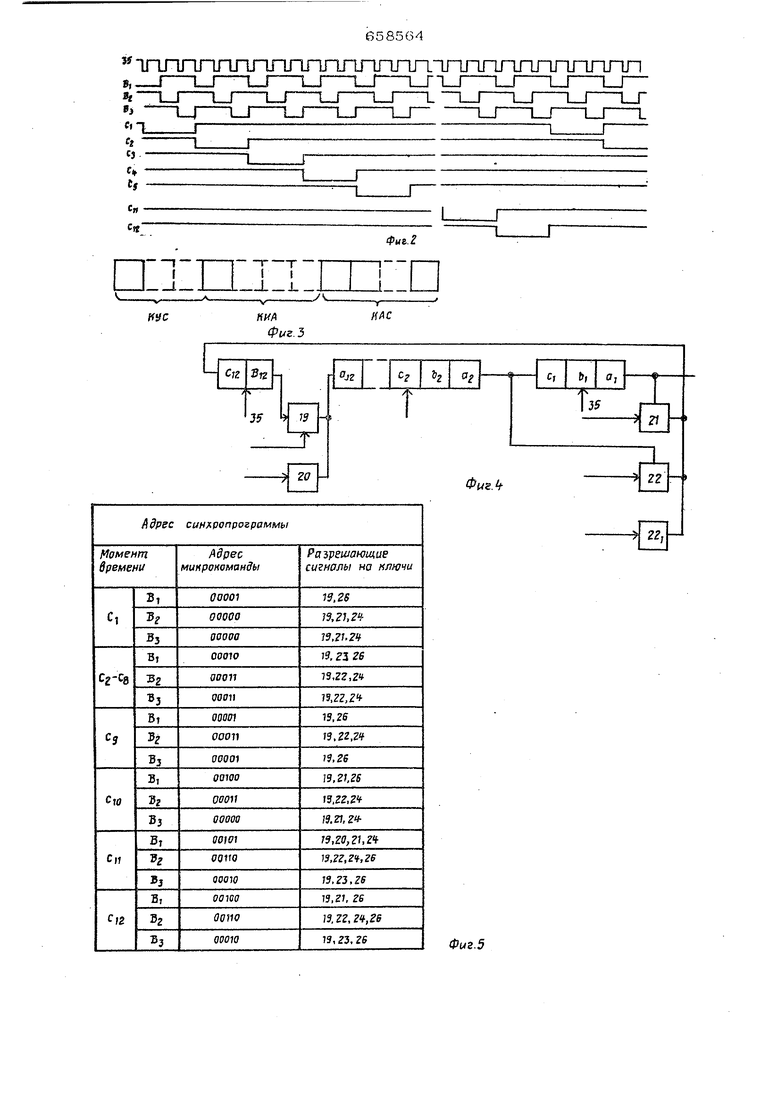

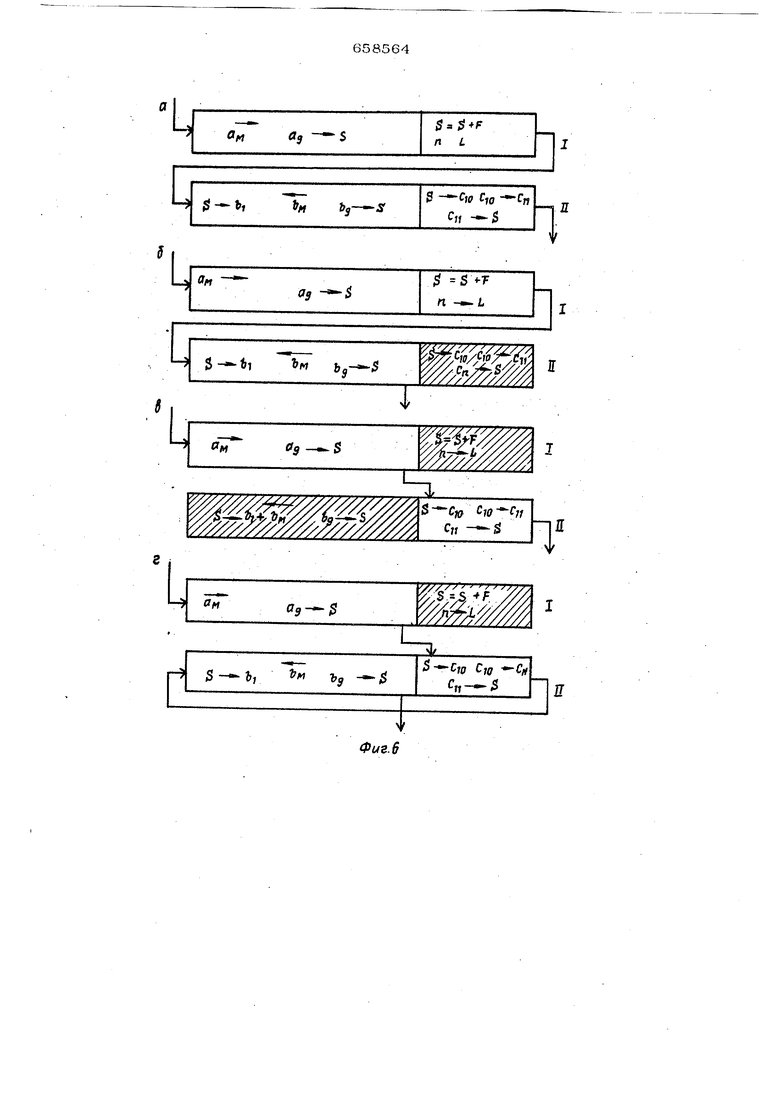

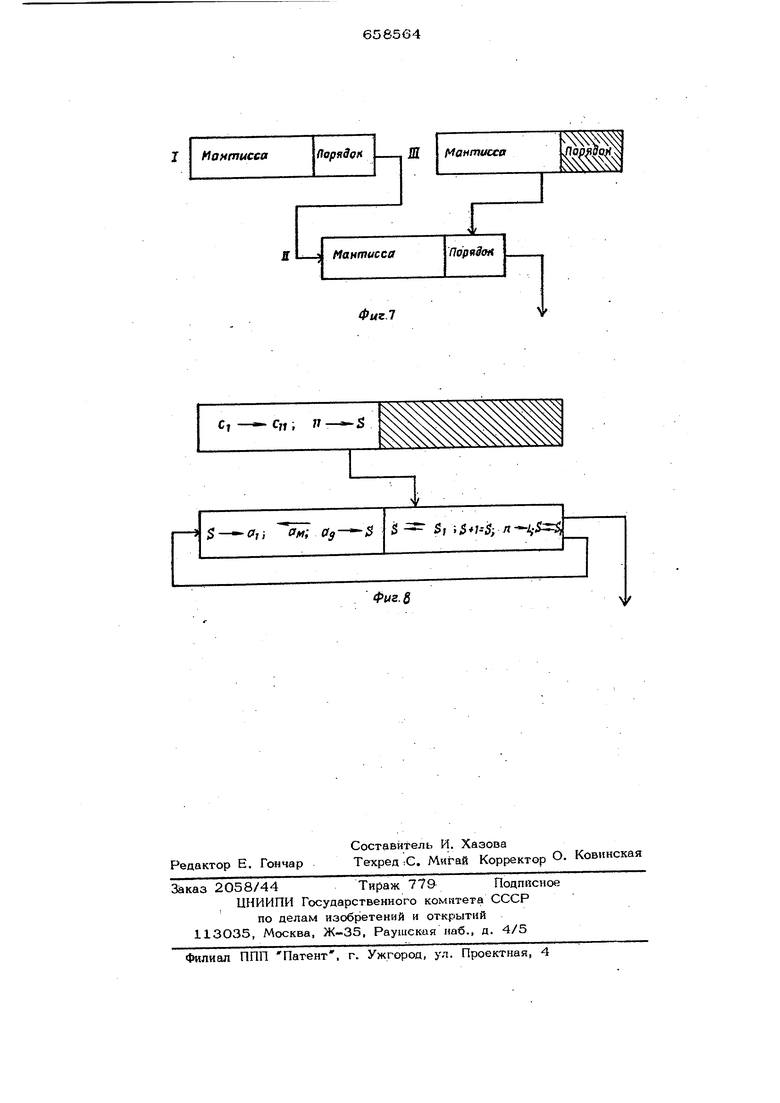

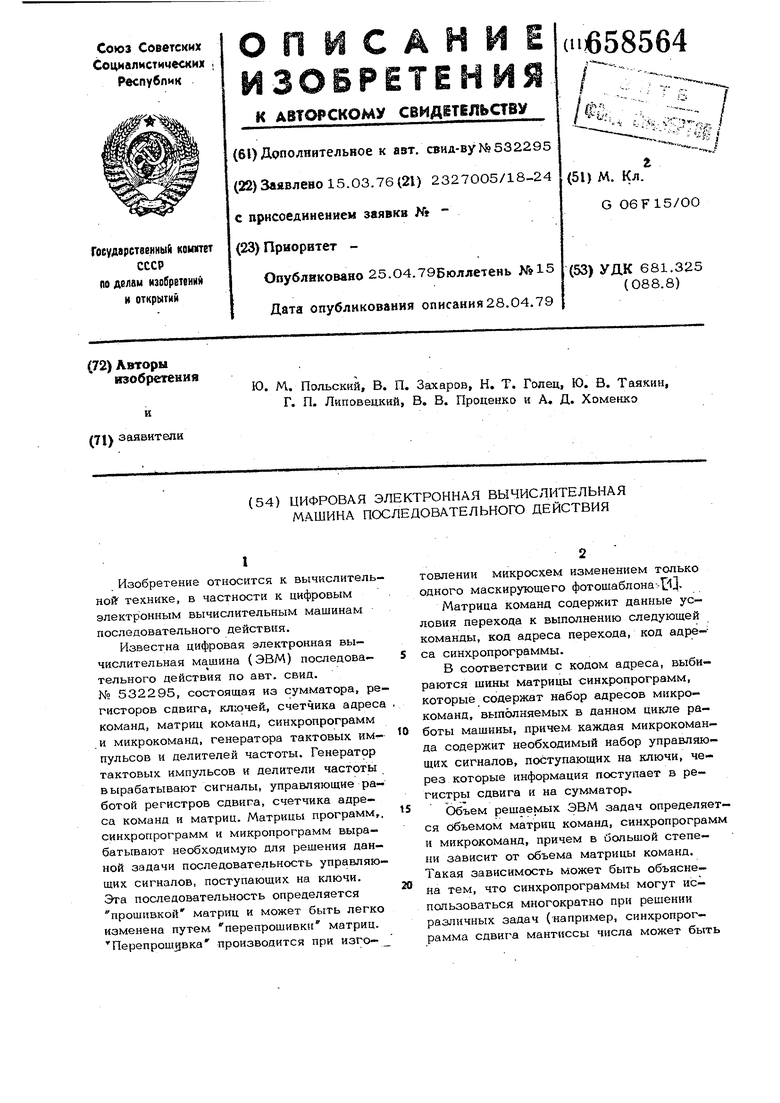

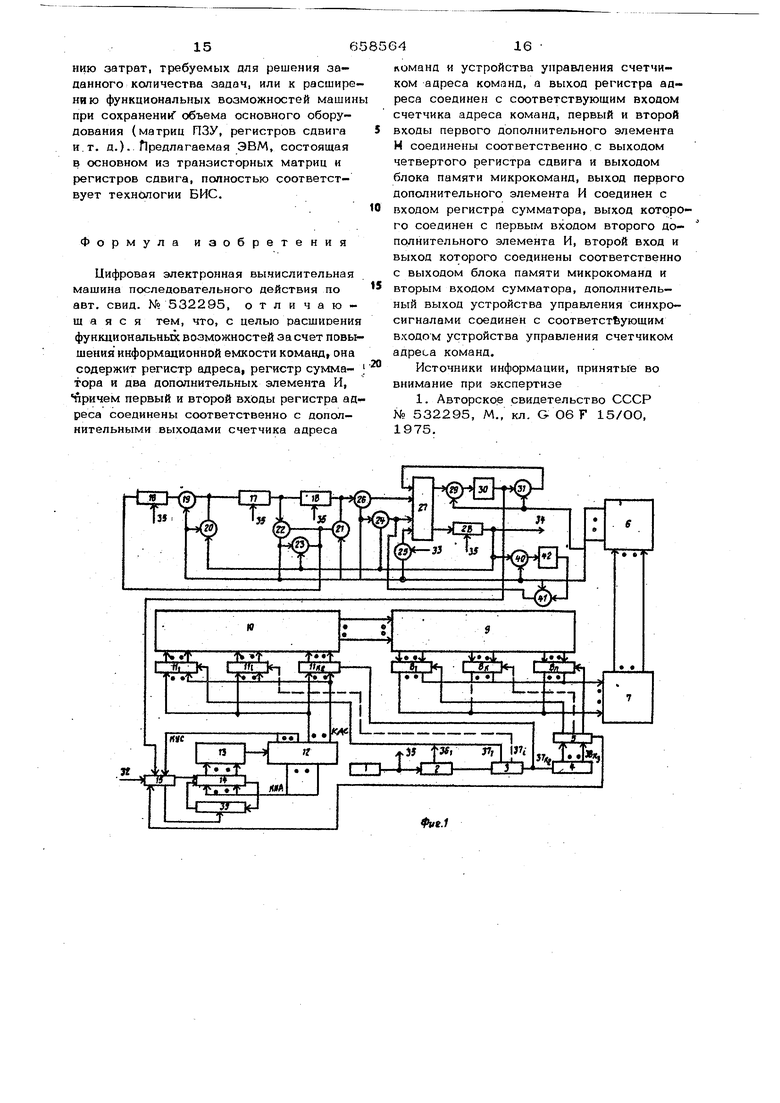

использована в программе сложения и умножения приема, а микрокоманда приема содержимого регистра в сумматор - в самых различных программах), а команды программной матрицы могут испопьзоваться только в фиксированных програм мах (например, программа сложения), поскольку адрес последующей команды определяется либо следующим состоянием счет чика адреса команД| либо кодом нового адреса матрицы команд, которые в известной ЭВМ определяются прошивкой матрицы команд и структурой счетчика адреса команд. Целью изобретения является расшире- ние функциональных возможностей машины за счет повышения информационной емкости команд. Достигается это тем, что цифровая электронная вычислительная машина после довательного действия содержит регистр адреса, регистр сумматора и два дополнительных элемента И, причем первый и вто рой входы регистра адреса соединены соот вественно с дополнительными выходами счётчика адреса команд и устройства упра ления счетчиком, адреса команд, а выход регистра адреса соединен с соответствующим входом счетчика адреса команд, первый и второй входы первого дополнительного элемента И соединенны соответственно с выходом четвертого регистра сдвига и выходом блока памяти микрокоманд, выход первого дополнительного элемента И соединен с входом регистра сумматора, выход которого соединен с первым входом второго дополнительного элемента И, второй вход и выход которого соединены соответственно с выходом блока памяти микрокоманд и вторым аход ом сумматора, дополнительный выход устройства управления синхросигналами соединен с соответствующим входом устройства управле ния счетчиком адреса команд. На фиг. 1 представлена блок-ч;хема цифровой электронной вычислительной машины; на показана временная диаграмма выходных сигналов делителей для этого случая; на фиг. 3 - формат кода команды; на фиг. 4 - расположение информации в регистрах; на фиг. 5 - показан формат синхропрограммы и последовательность разрешающих сигналов на ключах; на фиг. 6 - показаны некоторые варианты получения новых синхропрограмм из существующих} на фиг. 7 - показан пример вы полнения трех команд программы; на фиг. 8 приведен фрагмент программы, занесеНИЯ в индикационный регистр кода запятой при выводе числа на индикацию. Блок-схема цифровой ЭВМ содержит генератор 1 тактовых сигналов, делители частоты 2, 3, 4, устройство 5 управления синхросигналами; блок 6 памяти микрокоманд, дешифратор 7 адресов микрокоманд, коммутаторы 8 ... 8 , блок 9 памяти адресов микрокоманд; дешифратор 10 кода адреса синхропрограммы; коммутаторы llj - . 12 памяти команд, дешифратор 13 адресов команд; счетчик 14 адреса команд; устройство 15 управления счетчиком адреса; регистры сдвига 16, 17,18; элементы И 19 - 26; сумматор 27; регистр сдвига 28; элемент И 29; триггер 30; элемент И 31; входы 32, 33 машины; выход 34 машины; выход 35 генератора 1; выходы 36 - 36, 37 , 38,5 делителей 2, 3, 4; регистр адреса 39; первь1й и второй дополнительные элементы И 4О, 41; регистр сумматора 42. Синхронизация узлов ЭВМ осуществляется сигналами, вырабатываемыми на выходах генератора 1 и делителей частоты 2, 3, 4. Коэффициенты деления К1, К2 и КЗ делителей 2, 3 и 4 йыбирают равными, соответственно числу бит одной буквы, числу обрабатываемых ЭВМ слов и числу разрядов, содержащихся в одном обрабатываемом слове, например для случая обработки трех 12-разрядных двоично-десятичных слов К1-4, К2-3 и КЗ-12. На выходах 37j ...37, делителя 3 (см; фиг. 2) вырабатываются сигналы В( ... Bj.2, которые поступают на коммутаторы 11... llj,2 и определяют номер обрабатываемого слова. На выходах 38 ... 38, делителя 4 вырабатываются сигналы С,... С, которые через устройство 5 управления син-iхросигналами поступают йа коммутаторы 8 ... 8j и определяют номер разряда обрабатываемого слова. Совокупность сигналов BiСГ, сответствует V-разряду { слова. Минимально возможный временнь1й инг тервал ЭВМ равен продолжительности нахождения делителя 2 в одном состоянии и соответствует времени, необходимому для обработки одного бита информации. Общее число таких моментов времени в одном цикле равно К1.К2.КЗ и равно числу разрядов регистров сдвига 16, 17, 18,которые совместно с элементами И 19 и 21 образуют цепь циркуляции информации в ЭВМ. ГЗторая цепь циркуляции информации содержит регистр сдв(П-а 28, элемент И 24 и сумматор 27, причем число разря дов регистра сдвига 28 равно длине (числу двоичных разрядов) одной буквы слова и равно К1 - коэффициенту деления делителя 2. Число разрядов регистров сдвига 16 17, 18 выбирают таким образом, чтобы было возможно производить поразрядный сдвиг слов влево или вправо, различные преобразования информации, содержащейся в регистрах, подавая управляющие сигналы на элементы И 19... 16, 29, 31, 4О, 41. Эти управляющие сигналы поступают с выхода блока 6. Совокупность сигна- поЬ управления ключами в каждый момент времени BlCi является микрокомандой ЭВЛА. Набор необходимых микрокоманд опре деляется прошивкой матрицы блока 6. Выборка микрокоманды осуществляется с помощью дешифратора 7 по коду адреса, поступающего с коммутатора 8. ... 8j . Последовательность микрокоманд в одном цикле pa6q,Tbt ЭВМ в момент времени Bi при изменении I от 1 д К2 и L от 1 до КЗ является синхро- программой ЭВМ и определяет характер обработки всех разрядов всех слов в данном цикле работы машины. Формирование синхропрограммы осуществляется с помощью блоков 9 и 1О и коммутаторов 8j ... 8, и llj ... Ик При этом дешифратор 1О (матрица) дешифрирует код адреса синхропрограммы, в результате чего в блоке 9 происходит выборка кодов адреса микрокоманд. Пор док выборки адресов микрокоманд определяется синхросигналами, поступающими на управляющие входы коммутаторов 8 ...8 и 11 ... . Часто для обработки различных разрядов слов, например мантиссы числа, используются одинаковые микрокоманды. В этом случае объем матрицы блока 9 можно умен шить, т. е. использовать один и тот же участок памяти матрицы этого блока для обработки нескольких разрядов слов При этом устройство управления синхросигналами вырабатывает сигнал, разрешающий прохождение адреса микрокоманды с выхода блока 9 через соответствующий коммутатор 8 в течение време ни обработки указанных разрядов слов. Формироваие адреса синхропрограммы осуществляется с помощью блока 12 де- 646 шифратора 13, счетчика 14 адреса команд и устройства 15 управления счетчиком. Переключение счетчика 14 адреса команд происходит по сигналу С до71ителя 4 или по сигналам , поступающим с устройства 5 управления синхросигналами. Код счетчика 14 адреса команд дешифрируется дешифратором 13, в результате чего выбирается одна из вхо- дных шин матрицы блока 12 и на ее выходе (см. фиг. 3) формируется код команды:КУС - код установки счетчика; КНА - код нового адреса и КАС - код адреса синхропрограммы. КУС определяет условие перехода счетчика 14 в следующее состояние, напри- мер безусловный переход по новому адресу, условный переход по сигналу триггера ЗО, ожидание, переключение счетчика по сигналу Cj или по сигналу С:, и т. д. т. д. Число разрядов КУС, КНА и КАС определяется количеством условий перехода,, разрядностью счетчика 14 адреса команд и объемом матрицы блока 9 соответственно. Работает ЭВМ следующим образом. Предположим, что ЭВМ находится в режиме ожидания. Режим ожидания характеризуется неизменностью информации в регистрах,и возможностью выполнения выбранной программы по команде из внешнего устройства, причем любая программа ЭВМ заканчивается режимом ожидания. Режим ожидания обеспечивается одним из множества состояний счетчика 14 адреса команд. Состояние счетчика 14 дешифри- руется дешифратором 13, при этом выбирается команда программной матрицы блока 12, выходной код которой содержит КУС, КНА и КАС. Режим ожидания ЭВМ обеспечивается кодом установки счетчика (КУС), который поступает на устройство 15 управления счетчиком, которое анализирует КУС и выдает на счетчик 14 сигнал разрешения приема кода нового адреса (КНА) и кода начального адреса, поступающего извне. КНА в режиме ожидания должен совпадать с кодом счетчика 14, по которому выбрана эта команда, т. е. до прихода кода начального адреса выбирается одна и та же команда матрицы блока 12. Пусть, например, в режиме ожидания код счетчика 14 изменяется по сигналу Cj . В момент времени Bj С j код адреса синхропрограммы с выхода блока 12 поступает на матрицу дешифра- тора 10 через коммутатор 11 . Де1ии(} ратор 1О выбирает одну из шин матрицы блока 9, выходной код которого черегз коммутатор 8/ поступает на вход матрицы дешифратора 7, с помощью которого выбирается одна из шин матрицы блока, 6 выдает код микрокоманды, которая обеспе чивает циркуляцию информации в регистра Для того микрокоманда обеспечивает выдачу разрешающих сигналов на элементы И 19, 21, 24, чтоОбеспечивает продвижение информации из одного регистра в другой. В момент времени В С код адреса синхропрограммы поступает на деши рйтор 10 через коммутатор Hi . При этом выбирается другая шина матрицы блока 9, выходной код которой в режиме ожидания одинаков с кодом, выбранным в момент времени В С. , т, е. выбирвется та же микрокоманда (микрокоман- да циркуляция). Аналогично производится выборка адресов микрокоманд в другие моменты времени Любая программа ЭВМ начинается подачей из внешнего устройства по входу начального адреса программы на счетчик 14 адреса команд. По сигналамустройства 15 управления счетчиком код начального адреса программы записывается в счетчик 14. Затем, как и в режиме ожи дания, выбирается соответствующая шина матрицы блока 12, синхропрограмма блока 9 и последовательность микрокоманд блока 6, Причем, в каждом цикле работы машины может выбираться любая синхро- программа и в каждый момент времени могут выбираться любые микрокоманды из всего существующего для данной ЭВМ набора. Предположим, что для случая трех (а, .в, с) двенадцатиразрядных шестнадцатиричных слов необходимо по данной команде блока 12 выполнить следующие. преобразования информации: «9.-DЛC;.g,«,,3ю c„;«lrЬ,o ,2-С, , где а вО - в первый разряд слова (а) записать а «OjCoO- Б девятый разряд слов (а) и Гс) записать (в) на один разв - сдвиг слова ряд вправо; - сдвиг 1-8 разрядов слова (а на один разряд влево; - сдвиг 1-8 разрядов слова (с на один разряд вправо; десятый разряд слова (а) сложить с одиннадцатым разрядом слова (в) и результат записать в одиннадцатьЕй раз- ряд слова (с); - содержимое десятого разряда слова (а) записать в десятый разряд слова (в); о -b.jsC, - двенадцатый разряд слова (а) сложить с двенадцатым разрядом слова (в) и результат записать в двенадцатый разряд слова (с), В момент времени В Cj информация в регистрах расположена, как показано на фиг. 4, а продвижение информации из ячейки в ячейку осуществляется за время между моментами времени В С и 82 Cj ; и Вд С,- и Bj С, и т. д. пись нуля в первый разряд слова (а), девятый разряд слов (а ) и (с) производится запретом в моменты вре- мени В С , В Сд, Bj Cg связи выхода регистра 18 с входом регистра 16 ( отсутствуют разрешающие сигналы на элементе И 21 в указанные моменты времени). Для сохранения остальной t информации на элементе И 19 в.эти моменты времени необходимо подавать разрешающие сигналы. Сдвиг слова (в) на один разряд вправо осуществляется путем подачи разрешающих сигналов на элемент И 22 в моменты времени В. С , В, С,... В С при этом разрешающие сигналы на элементе И 21 должны отсутствовать. Аналогично осуществляется сдвиг 1-8 разрядов слова (с), только разрешающие сигналы подаются на элемент И 22 в моменты времени В, С , В С-.,. кг Bj Cg . Сдвиг 1-8 разрядов слова (а) влево осуществляется с помощью сумматора. Для этого в момент времени Bj С подается разрешающий сигнал на элемент И 26, и содержимое первого разряда слова (а) записывается в сумматор. В моменты времени BjC и В Cj подаются разрешающие сигналы на элемент И 24, обеспечивая циркуляцию первого разряда слова (а) в кольце сумматор 27 - регистр 28. В момент времени В- С подается разрещающий сигнал на элемент И 23 и содержимое регистра 28 (первый разряд слова (а) переписывается в регистр 16. Аналогичным образом осуществляется сдвиг остальных разрядов слова (а). Запись содержимого десятого разряда слова (а) в десятый разряд слова (в) осуществляется также с помощью сумма- 9 тора. Для этого в момент времени В. C подается разрешающий сигнал на элемент И 26 и содержимое десятого разряда ре гистра (а) записывается в сумматор. В момент времени 82 подается разре- шающий сигнал на элемент И 23. В этот момент на выходе регистра 18 будет де сятый разряд слова (в), а на элементе И 21 разрешающий сигнал отсутствует и в регистр 16 записывается содержимое регистра 28 (десятый разряд слова (а). Суммирование десятого разряда слова (а) с одиннадцатым разрядом слова (в) ( +b и запись результата суммирования в одиннадцатый разряд сло ва (с) производится следующим образом: поскольку в момент времени В„ С в регистре 28 находился десятый разряд сло ва (а), то дли сохранения этого значения необходимоо подавать разрешающие сиг- налы на элемент И 24 в момент времеВ, т. е. до прихода один ни В Cjg . надцатого разряда слова (в). Одиннадцатый разряд слова (в) появится на выходе регистра 18 в момент времени В С . В этот момент необходимо подать разрешающие сигналы на элементы И 24 и 26 При этом на два входа сумматора поступит содержимое регистров 18 и 28, т. е. одиннадцатый разряд слова (в) и десятый разряд слова (а). В момент вре мени Ва С, подается разрешающий сигнал на элемент И 23 и сумма а в с выхода регистра 28 записывается в регистр 16, Поскольку в этом время на выходе регистра 18 будет одиннадцатый разряд слова (с), а разрешающий сигнал на элементе И 21 отсутствует, то через элемент И 23 производится подмена одиннадцатого разряда слова (с) результатом суммирования Суммирование двенадцатого разряда слова (а) и двенадцатого разряда слова ) (в) производится аналогичным образом (см. фиг. 5). В течение выполнения текущей команды устройство 15 управления счетчиком анализирует КУС и сигнал триггера ЗО и в момент времени, определяемый кодом установки счетчика, вырабатывает сигналы записи в счетчик 14 кода следующей по программе команды (новый адрес, адрес возврата, начальный адрес и т, д.) и сигналы записи в регистр 39 кода адреса команды возврата. Возможность изменять момент време- -{jH переключения счетчика 14 предоставG4ляет дополнительные удобства при составлении программ вычислений и позволяет расширить функциональные возможности устройства, так как увеличивает число испашхзуемых синхропрограмм без увеличения объема матрицы- блока 9. Рассмотрим, например, вариант ЭВМ, в которой счетчикк 14 адреса команд может переключаться дважды за один цикл работы машины: по началу импульса С. и по началу импульса Сщ ... Варианты получения новых синхропрограмм даны на фиг. 6, где а - сдвиг вправо мантиссы слова (а); S - записать в сумматор содер-: жимое девятого разряда слова (а); S S F - содержимое сумматора сложить с константой 15 и результат записать в сумматор; S - Б - записать в первый разряд слова в) содержимое сумматора; В, - сдвиг влево мантиссы слова - записать в сумматор содержимое девятого разряда слова (в); S - - записать в десятый разряд слова (с) содержимое сумматора; - содержимое десятого разряда слова (с) записать в одиннадцатый разряд слова (с); Cjj- 3 записать в сумматор содержимое одиннадцатого разряда слова (с). На фиг, 6а показан пример выполнения двух команд программы для случая, когда счетчик 14 адреса команд переключается по началу импульса С чение выполнения указанных команд производятся следующие преобразования ин- формации: сдвиг вправо мантиссы слова (а), вычитание 1 (прибавление 15) из содержимого девятого разряда слова (а) с запоминанием сигнала переноса (О или I) в триггере 30 и запись результата вычитания в первый разряд слова (в), сдвиг влево мантиссы слова (в), запись в десятый разряд слова (с) содержимого девятого разряда слова (в) и в одиннадцатый разряд слова (с) содержимого десятого разряда слова (с), запись в сумматор содержимого одиннадцатого разряда, слова (с). На фиг. 66 показаны те же команды, но при выполнении П команды счетчик 14 переключается на следующую команду по сигналу C . В данном случае выполняются следующие преобразования информации; сдвиг вправо мантиссы слова (а), вычита- ние 1 из содержимого девятого разряда слова (а) с запоминанием сигнала переноса в триггер ЗО и запись результата вычитания в первый разряд слова (в), сдвиг влево мантиссы слова (в), запись в.сумматор содержимого девятого разряда слова (в). Оставшаяся часть синхро- программы Ц команды не выполняется. На фиг. 6в показаны те же команды, но при выполнении 1 команды счетчик 14 переключается по сигналу , а П команды - по сигналу С . При этом выполняются следующие преобразования информации: сдвиг вправо мантиссы числа (а), запись в десятый разряд слова (с) содержимого девятого разряда слова (а), запись в одиннадцатый разряд ел ва (с) содержимого десятого разряда ело ва (с), запись в сумматор содержимого одиннадцатого разряда слова (с). На фиг. 6г показаны те же команды, но при их выполнении счетчик 14 переключается по сигналу С,д . При этом выполняются следующие преобразования информации; сдвиг вправо мантиссы елова (а), запись в десятый разряд слова (с) содержимого девятого разряда слова (а), в одиннадцатый разряд слова (с) содержимого десятого разряда слова (с) и в первый разряд слова (в) содержимого одиннадцатоно разряда слова (с), сдвиг влево, мантиссы слова (с), запись в сумматор содержимого девятого разряда слова (в). Из приведенного выше видно, что, изменяя время переключения счетчика 14, можно из существующего набора синхропрограмм создавать новые синхропрограм мы. Так, например, в первом и втором случаях (фиг. 6а, б) в первый разряд слова (в) записывается уменьшенное на единицу значение девятого разряда ело-, ва (а) и производится едвиг влево мантиссы слова (в). В третьем случае (фиг. 6в) часть синхропрограммы П комадоы ( ) не выполняется, и слово (в) остается без изменений. В четвертом случае (фиг. 6г) в первый разряд слова (в) записывается содержи- мое одиннадцатого разряда слова (с) и производитея едвиг влево мантиссы слов (в), т. е. несмотря на то, что во всех четырех случаях используется по две команды с одинаковыми во всех случаях синкропрограммами преобразования, которым подвергалась информация в этих спучаях, существенно .отличаются. 6412 Следует отмстить, что выполнение синхропрограммы данной команды зависит от времени переключения счетчика 14 при выполнении предыдущей команды. Так, например, при выполнении И команды в случае, показанном на фиг. 6а, синхро- программа этой команды выполняется полностью, а в случае, показанном на фиг. 6в, выполняется только порядковая часть этой синхропрограммы. Пример выполнения трех команд программы (см. фиг. 7). При выполнении 1 и П команды счетчик 14 переключается по сигналу Cj , а при выполнении Ш ко- манды - по сигналу С, . Синхропрограмма команды П выполняется полностью, если эта команда выполняется после команды 1. Если же П команда выполняется после команды 1П ,что часть сиахропрограммы, производящая обработку мантиссы числа, не выполняется, т. е. одна и та же команда программы производит разные преобразования информации в регистрах. Это позволяет более полно использовать имеющийся набор синхропрограммы и уменьшить число команд .и синхропрог- рамм, необходимых для рещения данной задачи, или при заданном объеме матриц блоков 9 и 12 увеличить число решаемых ЭВМ задач. Совместное использование вновь введенных элементов и связей позволяет на небольшом числе команд и синхропрог- рамм строить сложные программы вычислений. Программа занесения в индикационный регистр кода запятой при выводе числа на индикацию выполняется следующим образом (см. фиг. 8). Содержимое первого разряда слова (е), определяющее количество сдвигов мантиссы после занесения запятой, записывается в регистр сумматора Si (Cf-p-Sj) , сумматору присваивается число 11 (код запятой) (). По сигналу C;|Q счетчик 14 адреса команд переключается и выполняется следующая команда. Затем в сумматор из регистра сумматора вызывается число, определяющее количество сдвигов мантиссы, а в регистр сумматора записывается код запятой ( S1).После этого к содержимому сумматора прибавляется единица и перенос зaп rt;ывaeтeя в триггер 30S4-liS,(. jj Затем в сумматор из регистра сумматора вызывается код запятой, а в регистр сумматора записывается увеличенное на 1 . число, определяющее количество сдвигов мантиссы (). Если в результате суммирования S-bl «S вырабатывается сигнал переноса, то триггер 30 устанавливается в состояние {U 1), и ЭВМ переходит к выполнению дал1 нейших команд программы, которые не показаны на чертеже. Если сигнал переноса не выработался (L. 0), то код счетчика 14 не изменяется и ЭВМ продолжает выполнять эту же команду. При этом в первый разряд слова (а) записывается содержимое сумматора (код запятой) (), производится сдвиг влево мантиссы слова (а) Са ), содержимое девятого разряда слова (а) записывается в сумматор (О.-«-S ) Затем содержимое сумматора записьшается в регистр сумматора (вц ), а в сумматор из регистра сумматора вызывается число, определяющее количество сдвигов мантиссы (а) (S Si ). После этого, к содержимому сумматора прибавляется i, сигнал переноса записывается в триггер 30 ( , ), в сумматор из регист ра сумматора вызывается (вц ), а число, определяющее количество сдвигов, заносится в регистр сумматора () и т. д пока триггер переноса не установится в единичное состояние (L 1). После этого ЭВМ переходит к выполнению дальнейших команд программы. В данной (ЭВМ) введение регистра 39 адреса, соединенного с устройством 15 управления счетчиком и со счетчиком 14 адреса команд позволяет многократно использовать одни и те же массивы матрицы блока 12 при решении различных зада В этом случае ЭВМ работает следующим образом. Предположим, что очередная команда содержит КУС, соответствующий безуслов ному переходу по новому адресу с записью в регистр 42 кода адреса команды возврата. При этом устройство 15 управле- НИН счетчиком вырабатывает записи кода нового адреса в счетчик 14 и сигнал записи кода команды возврата в регистр 39. Команда, код адреса которой в данном случае записывается в счетчик 14, может быть, например, начальной командо программы сложения (подпрограммы). Последняя команда подпрограммы (в данном случае программь сложения) содержит КУ соответствующий безусловному переходу по коду регистра 39 адреса (по адресу возврата). При этом устройство 15 уп- равления счетчиком вырабатывает сигнал записи в счетчик 14 кода регистра 39. Наличие возможности перехода по новому адресу с запоминанием адреса возврата и перехода по адресу возврата дает возможность реализовать программу вычисления функций в виде подпрограмм, причем обращаться к подпрограммам мож- но многократно при вычислении разных функций. Это позволяет многократно использовать одни и те же массивы памяти блока 12. Внешняя информация поступает на сумматор 27 при наличии разрешающего сигнала на элементе И 25. Эта информация может быть просуммирована с содержимым любой ячейки любого слова или записана без изменений в любую ячейку любого слова. Результат вычислений выдается на внешнее устройство с выхода 34 ЭВМ. Программа решения определенной задачи состоит из последовательности синхро- программ, адреса которых указаны в ко- мандах программной матрицы блока 12, Из данного количества синхропрограмм можно строить различные последовательности синхропрограмм за счет неоднократного использования их при решении различных задач. Этому способствует наличие в составе операций ЭВМ условных переходов, переходов к выполнению подпрограмм, переходов по адресу возврата и т. д., осуществляемых с помощью устройства 15 управлеяия счетчиком при наличии соответствующих сигналов КУС., Наличие упомянутых переходов счетчика 14 адреса команд позволяет увеличить число используемых при решении задач команд без увеличения объема матрицы блока 12. Увеличение информационной емкости синхропрограмм и числа синхропрограмм достигается путем введения в машину регистра 42 сумматора и элементов И 4О и 41, управляющих записью информации в регистр 42 и считыванием информа ций из регистра 42 в сумматор 27, а также путем введения в схему машины новой связи устройства 5 управления синхросигналами с устройством 15 управг; ления счетчиком адреса команд. Это позволяет увеличить объем и сложность решаемьгх ЭВМ задач без увеличения объема матриц блоков 6 и 9. Таким образом, структура данной ЭВМ позволяет формировать новые последовательности микрокоманд, синхропрограмм, команд программы вычислений не за счет увеличения объема матриц блоков 6, 9, 12, а путем многократного использования в различное время одних и тех же ячеек памяти, что приводит к уменьше- нию затрат, требуемых для решения заданного количества задач, или к расшире нию функциональных возможностей машин при сохранени1Г объема основного оборудования (матриц ПЗУ, регистров сдвига и.т. д.).. Предлагаемая ЭВМ, состоящая в основном из транзисторных матриц и регистров сдвига, полностью соответствует технологии БИС. Формула изобретения Цифровая электронная вычислительная машина последовательного действия по авт. свид. № 532295, отличающаяся тем, что, с целые расшисени функциональных возможностей за счет повы шения информационной емкости команд, она содержит регистр адреса, регистр сумматора и два дополнительных элемента И, причем первый и второй входы регистра ад реса соединены соответственно с дополнительными выходами счетчика адреса ломана и устройства управления счетчиком адреса команд, а выход регистра адреса соединен с соответствующим входом счетчика адреса команд, первый и второй входы первого дополнительного элемента М соединены соответственно с выходом четвертого регистра сдвига и выходом блока памяти микрокоманд, выход перрого дополнительного элемента И соединен с входом регистра сумматора, выход которого соединен с первым входом второго дополнительного элемента И, второй вход и выход которого соединены соответственно с выходом блока памяти микрокоманд и вторым входом сумматора, дополнительный выход устройства управления синхросигналами соединен с соответствующим входом устройства управления счетчиком адреса команд. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 532295, М., кл. G- Об F 15/ОО, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая электронная вычислительная машина последовательного действия | 1975 |

|

SU532295A1 |

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU678486A2 |

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU654948A2 |

| Электронные часы | 1980 |

|

SU928169A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU591076A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Устройство для контроля | 1981 |

|

SU1072052A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

1Г1ППГ1ПГ1Г1Г1Г1ПЛГ1ПГ1Г1

с

c«

i I .JJ.

1

v

Фиг.З

ffifC

Фи&.2

Q

S- tiЬм

b

s -S

«м

жш1ё

ж

и

о«

a,

кй1 й ;г W/fA,

J.

fp

g

%

C,(

Т

С;г --S

,//.

П

я

i

ФигЛ

V

,

5-- a,j PM;

S 5, ;5 7--5; Л-.

Авторы

Даты

1979-04-25—Публикация

1976-03-15—Подача