Изобретение относится к вычислительной технике и может Рыть использовано при построении запоминающих устройств на цилиндрических магнитных доменах (ЦМД),

Известен блок считывания информации для доменного запоминающего устройства, содержа.,:ий предварительньй усилитель воспрои, чедения, подключенный к одному из ьходов усилителя воспроизведения, вькод :оторого подсоединен к дискриминатору/, подключенному к входу формирователя сигнала ОЗ.

Однако в данном блоке считывания не предусматривается многократная дискриминация сигнала чтения в разные моменты времени с последующим определением информационной 1 или информационного О по результатам считывания.

Наиболее близким техническим решением к изобретению является блок считывания информации для доменного запоминающего устройства, которьй содержит усилитель воспроизведения, подсоединенный к предварительному усилителю воспроизведения, к формирователю строба,к дискриминатору и к формирователю импульсов f..

Недостатком известного блока считывания является малая информационная надежность, так как D нем отсутствует возможность многократной дискримшшции скпгала чтения, что необходимо для вьщелепия сигнала , чтения при соизмеримости сигнала и помехи, при изменении амплитуды сигнала чтения от считывания к считыванию и 1три повьш1ении неявно выра женного амплитудного знс1ченкя сигнала чтения 1 над помехой в сравнительно ;1пболы1 ОЙ отрезок времени, удобный для временной селекции.

Цель изобретения - повышение надежности блока считьгааирш информаци для доменного запоминаюо{его устрой ства путам многократной дискош-шнащга сигнала чтения,

Поставленная цель достигаетсл

тем, что блок считг шаиия ннЛюрмации для доменного запоминающего устройства, содержащий иредв трительный услитель воспроизведения, вход которого является первым входом блокя. счнтыванйя инфорь5ации, а выход подключен к первому входу усилителя воспроизведения, второй вход которого

является вторым входом блока считывания информации, а выход подключен к входу дискриминатора, В1э1ход которого соединен с входом формирователя сигнала, содержит дополнительные усилители воспроизведения, дискриминаторы и формирователи сигнала, элемент ИЛИ, формирователи импульсов счетчик, элемент сравнения, блоли задержки и регистр, вход которого является третьи - входом блока счигыват-1Я информации, а выход подключен к первому входу элемента сравнения, второй вход которого подключерт к выходу счетчика, а выход является выходом блока считывания информации, вход счетчика соединен с выходом элемента ИЛИ, один из входов которого подключен к выходу формирователя сигнала, а другие - к выходам дополнительных формирователей сигнала, вхды KOTopEiix подключены к выходам допонительных дискри1-1инаторов5 Т1одк:1юченных к выходам дополнительных усилителей воспроизведения, первые входы которых подключенгл к выходу предварительного усилителя воспроизведения, а другие - к выходам соответств:лощих формирователей импульсов., приче:-; вхо первого блока задерлпси псдклю-ен к второму.входу усилителя воспроизведения, а выход соединен с входом первого -формирователя импульсов, )зыход которого соедикен с входом второго блока зад s ржк и.

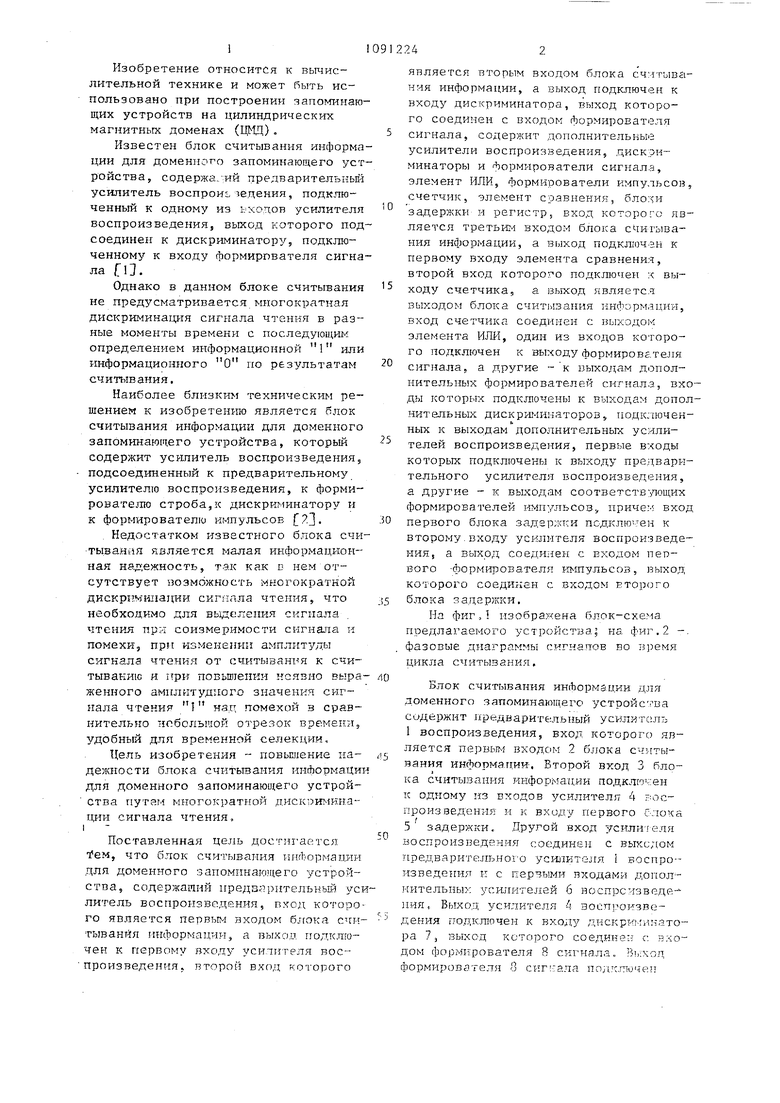

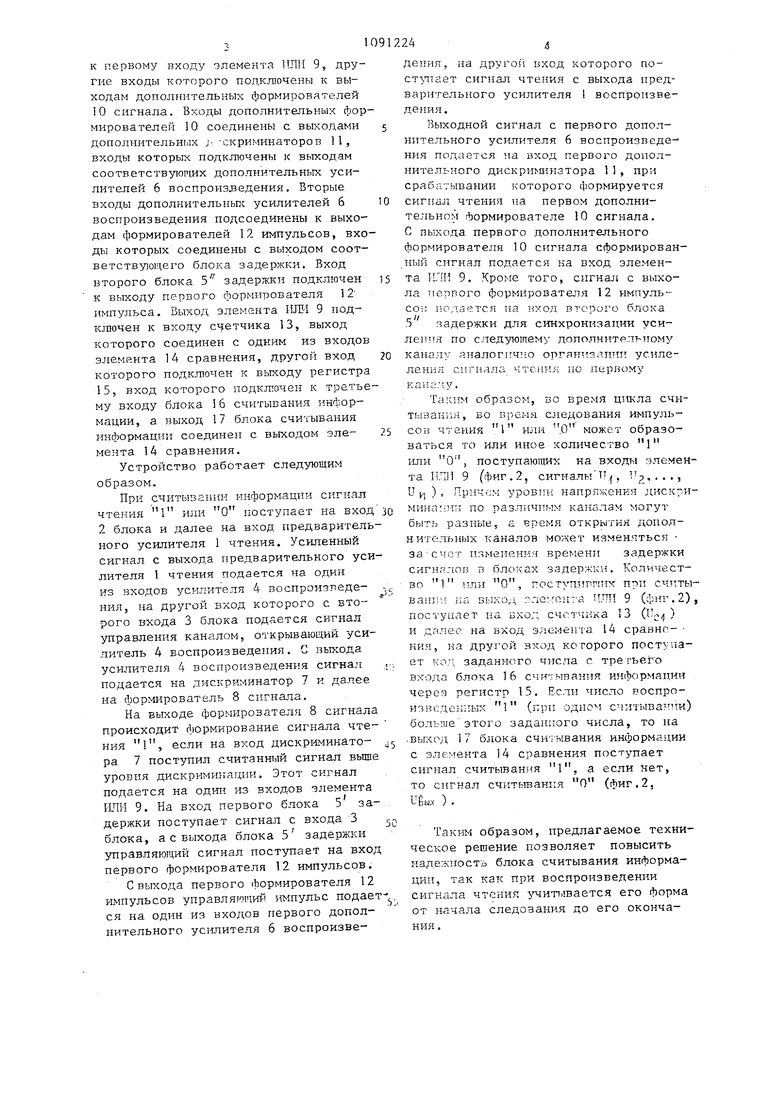

На фиг,1 изображена блок-схема предлагаемого устройства; на фиг,2 фазовые диаграммь сигналов но время цикла считывания.

Блок считывания инФормаи.ии для доменного запоминающего устройства содержит предварительный усилитсшь 1 воспроизведения, вход которого является первьм входоь 2 блока считывания информации-. Второй вход 3 блока считывания инфор; ации подключен к одному 1з входов усилител57 4 ::;оспроизведения и к входу первого с-лока 5 задержки. Другой вход усиличселя воспроизведения соединен с выхсдом предварптельного усилителя i воспроргзведепия к с первыми входами допол кительных усшп- телей 6 воспрсизведе 1ия, Выход усилителя 4 воспроизведения подклочен к вхолу днскркг-п-.катора 7j выход которого соедике:-; с входом формирователя 8 сигнала. Bi,:xon формировател55 О скг -:ала .пю-теп

к первому входу элемента ИЛИ 9, другие входы которого подключены к выходам дополнительных формирователей 10 сигнала. Входы дополнительных формирователей 10 соединены с выходами дополнительных / скриминаторов И, входы которых подключены к выходам соответствующих дополнительных усилителей 6 воспроизледения. Вторые входы дополнительньпс усилителей 6 воспроизведения подсоединены к выходам формирователей 12 импульсов, входы которых соединены с выходом соответствующего блока задержки. Вход второго блока 5 задержки подключен к ВЕ)Тходу первого формирователя 2 импульса. Выход элемента ИЛИ 9 подключен к входу счетчика 13, выход которого соединен с одним из входов элемента 14 сравнения, другой вход которого подключен к выходу регистра 15, вход которого подключен к третьему входу блока 16 считывания информации, а выход 17 блока считывания информации соединен с вькодом элемента 1А сравнения.

Устройство работает следующим образом.

При считывании информации сигнал чтения 1 или О поступает на вход 2 блока и далее на вход предварительного усилителя 1 чтения. Усиленный сигнал с выхода предварительного усилителя 1 чтения подается на один из входов усилителя 4 воспроизледеНИЛ, на другой вход которого с второго входа 3 блока подается сигнал управления каналом, открывающий усилитель 4 воспроизведения. С вькода усилителя 4 воспроизведения сигнал подается на дискриминатор 7 и далее на формирователь 8 сигнала.

На выходе формирователя 8 сигнала происходит формирование сигнала чтеНИН 1, если на вход дискрт минатора 7 поступил считанный сигнал выше уровгш дискриминации. Этот сигнал подается на одш. из входов элемента 1-ШИ 9. На вход первого блока 5 задержки поступает сигнал с входа 3 блока, невыхода блока 5 задержки управляющий сигнал поступает на вход первого формирователя 12 импульсов. С выхода первого формирователя 12 импульсов управляющий импульс подаеся на один из входов первого дополнительного усилителя 6 воспроизведения, на другой вход которого пост п1гет сигнал чтения с выхода предварительного усилителя I воспронзведения.

Выходной сигнал с первого дополнительного усилителя 6 воспроизведе-ния подается па вход первого дополнительного дискриш1натора 11, при срабатывании которого формируется сигнал чтения на первом дополнительном Формирователе 10 сигнала. С выхода первого дополнительного формирователя 10 сигнала сформированный сигнал подается на вход элемента ИЛИ 9. Кроме того, сигнал с выхола первого формирователя 12 импульсов Г одается на вход втооого блока

г

Л задержки для синхронизации усиле1тня по следую1пем-ь дополнительному каналу аналогично оргяпизлцти усилелення сигнала чтс)ня но первому кан;|лу.

Таким образом, во время цикла счить зан11я, во время следования импульсов чтения 1 HJUi О может образоваться то или иное количество 1 или О, поступающих на входы элемета ИЛИ 9 (фиг. 2, сигналы.. Up,..., и k) ) ричем ypoBTii-i напряже 1ия дискрмина ;ми по paзличIIы i каналам могут быть разные, а время открытия дополнительных каналов может изменяться за изменения времени задержки сигнп-юв в блоках задержки. Количество или О, поступ1 РГ1Т1х при считвапп; па выход эле:.ппта ттпи 9 (фиг. 2 поступает на вход счетчика 13 ( ) и далее на вход элемента 14 сравни- ПИЯ, на другой вход которого поступает Koj; заданного числа с тре гьего входа блока 16 считывания информации через регистр 15. Если число рюспронзвсдспиых 1 (при одном считываттпи больше этого заданного числа, то на .выход 17 блока считывания информации с элемента 14 сравнения поступает сигнал считывания 1, а если нет, то сигнал считывания О (фиг.2, иВыд ) .

Таким образом, предлагаемое техническое решение позволяет повысить иадежность блока считывания информации, так как при воспроизведении сигнала чтения .шается его форма от начала следования до его окончания .

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1979 |

|

SU809350A1 |

| Блок считывания информации для запоминающего устройства | 1985 |

|

SU1283849A1 |

| Блок считывания информации для доменного запоминающего устройства | 1983 |

|

SU1105939A1 |

| Блок воспроизведения для запоминающего устройства | 1980 |

|

SU902070A1 |

| Блок считывания для запоминающего устройства | 1981 |

|

SU959155A1 |

| Запоминающее устройство | 1981 |

|

SU982093A1 |

| Запоминающее устройство | 1982 |

|

SU1049969A1 |

| Блок считывания информации для доменного запоминающего устройства | 1982 |

|

SU1056265A1 |

| Блок считывания информации для доменного запоминающего устройства | 1980 |

|

SU930381A1 |

| "Запоминающее устройство | 1979 |

|

SU809369A1 |

БЛОК СЧИТЫВАНИЯ ИНФОРМАЩЗД ДЛЯ ДОМЕННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА, содержащий предварительный усилитель воспроизведения, вход которого является первым входом блока считывания информации, а выход подключен к первому входу усилителя воспроизведения, второй вход которого является вторьтм входом блока счить вания информации, а выход подключен к входу дискриминатора, выход которого соединен с входом формирователя сигнала, отличающийся тем, что, с целью повышения его надежности путем многократной дискриминации сигнала ч РНИЯ, он содержит дополнительные усилители воспроизведения, дискриминаторы и формирователи сигнала, элемент ИЛИ, формирователи импульсов, счетчик, элемент сравне ния, блоки задержки и регистр, вход которого.является третьим входом блока считывания информации, а выход подключен к первому входу элемента сравнения, второй вход которого подклю-чен к выходу счетчика, а выход является выходом блока считывания информации, вход с-гетчика соединен с вьтходом элемента И.ПИ, один из входов которого подключен к выходу формирователя сигнала, а другие - к выходам дополнительных формирователей сигнала, сл .входы которых подключены к выходам дополнительных дискриминаторов,подключенных к выходам дополнительных усилителей воспроизведения, первые входы которых подключены к выходу предварительного усилителя воспроизведения, а другие к выходам соответствующих формирова телей импульсов, причем вход первого блока задержки подклточен к второму tvb входу усилителя воспроизведения, а выход соединен с входом первого фор4;i мирователя импульсов, выход которого соединен с входом второго блока задержки.

f7

n

ro

,

i/г. /

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электронная техника, сер.10, 1978, вып | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-07—Публикация

1983-01-28—Подача