изобретение относится к вычисли тельной технике и предназначено для использования в цифровых вычислитель ных машинах с повышенными требования ми к информационной надежности. Известно устройство, в котором за поминающая матрица (накопитель) подсоединена к усилителям воспроизведения с помощью диодов и транзисторов, входы которых через трансформаторы подсоединены к стробирующему генератору, кроме того в нем RC-цепочки подключены к диодам и эмиттерам тран зисторов. В этом устройстве повышена помехозащищенность за счет одновременного стробирования и предусмот рено подавление помех в нелинейных элементах 1J. Это устройство не исчерпывает до конца всеВОЗМОЖНОСТИ повьииения информационной надежности запомингиодих устройств, так как в нем отсутствуют элементы и блоки, обеспечивающие мно гократное стробирование и сравнение сформированных сигналов. Из известных запоминающих устройств наиболее близким к предлагаемому является устройство, содержащее накопитель, соединенный с ключами X и У и усилителями считывания, которые подключены, к формирователям сигналов и к форилирователям стробирующнх импульсов, подсоединенных к блоку задержки, который подключен к блоку управления. В этом устройстве используется по сути дела жесткое стробирование за счет формирования импульса стробироваиия с помощью блока задержки по сигнешу с блока управления 2 J. Но в данном устройстве отсутствует возможность обеспечения высокой информационной надежности, так как предусмотрено только дублирование блоков с целью обеспечения повышенной конструктивной или схемной надежности, а задача повышения информационной надежности в нем не ставилась и не решалась. В устройстве нет блоков и элементов, позволяющих осуществить многократное стробирование. Цель изобретения - повышение информационной надежности ЗУ путем неоднократного стробирования одного и того же сигнёша чтения в ра:зное время после поступления его на усилитель считывания, что позволяет выделить сигнал чтения из помех с большей достоверностью, т.е. с большей информационной нгцдежностью.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее накопитель, входы которого подключены через координатные ключи к первому входу основного блока управления, выходы накопителя через основные усилители считывания подключены к первым входам основных дискриминаторов, выходы которых подключены к входам основных формирователей сигнала, второй выход основного блока уп равления через основной формирователь уровня дискриминации подключен к вторым входам основных дискриминаторов, а третий выход через блок задержки подключен к выходам-основного формирователя стробирующих импульсов, выход которого соединен с соответствующими входами усилителей считывания, и числовой регистр, введены три группы элементов И, элементы ИЛИ, две группы триггеров и дополнительные формирователь стробирующих импульсов формирователь уровня дискриминации, дискриминаторы, блок управления, формирователи сигналов, усилители считывания, первый и второй входы дополнительных усилителей считывания подключены к одноименным входам основных усилителей считывания, а третий входк выходу дополнительного формирователя стробирующих импульсов, входы которого подключены к соответствующим выходам блока задержки, выходы дополнительныхусилителеи считывания соединены с первыми входгили дополнительных дискриминаторов, выходы которых подключены к входам дополнительных формирователей сигналов, вторые входы дополнительных дискриминатород подключены к выходу дополнительного формирователя уровня дискриминации, вход которого соединен с четвертым выходом основного блока управления, выходы основных и дополнительных формирователей сигналов подключены соответственно к первым входам элементов И первой группы и элементов ИЛИ, к вторым входам элементов И первой группы и элементов ИЛИ, выходы элементов И первой группы и элементов ИЛИ подключены непосредственно к входам числового регистра, а триггеры - к одному из выходов дополнительного блока управлени и первым входам элементов И втоpoi И третьей групп, вторые входы и выходы которых подключены через дополнительный блок управления соответственно к другому входу и первому выходу основного блока.

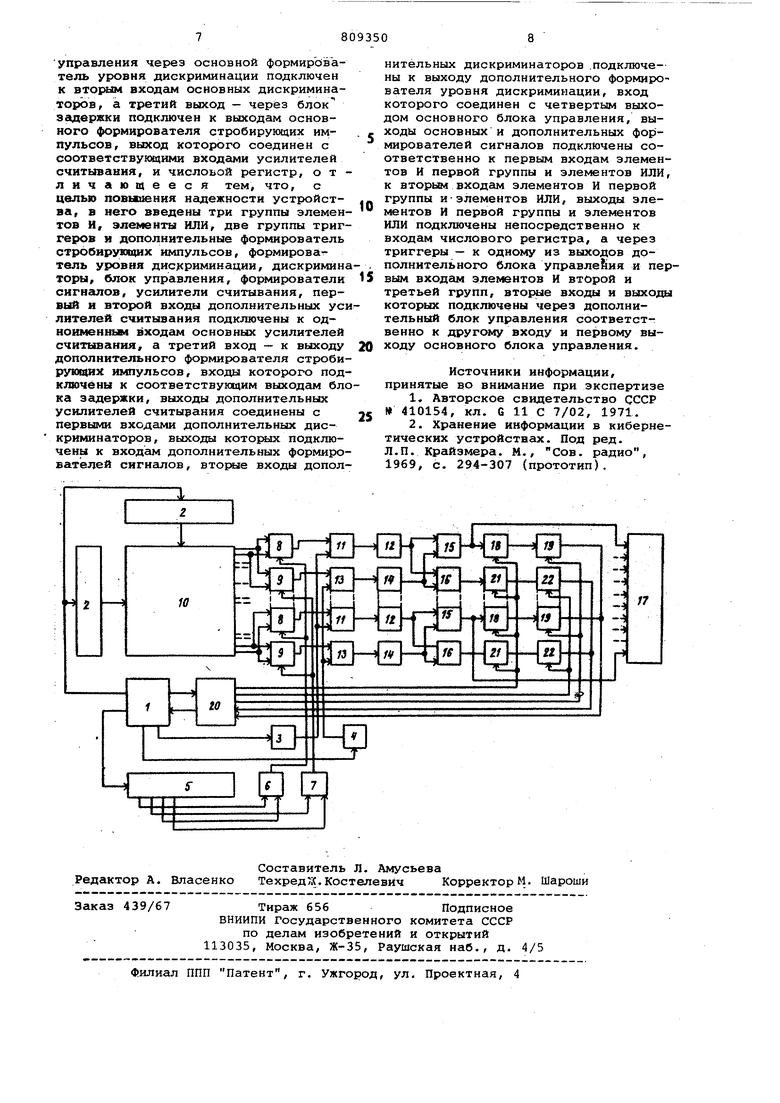

На чертеже представлена схема запоминающего устройства.

Запоминеиощее устройство содержит блок 1 управления соединенный ключами 2 X и У с основным формирователем 3 уровня дискриминации и дополнительным формирователем 4 уровня дискриминации, с блоком 5 задержки.

подключенным к формирователю 6 стробирующих импульсов и к дополнительному формирователю 7 стробирующих импульсов, соединенным соответственно с усилителями 8 считывания и дополнительными усилителями 9 считывания, подключенными к накопителю 10, соединенному с ключами 2 X и У. Усилители 8 считывания соединены с дискриминаторами 11, вторые входы которых подключены к формирователю 3 уроня дискриминации, а выход к формирователям 12 .сигналов. Выходы дополнительных усилителей 9 считывания соединены с дополнительными дискриминаторами 13, вторые входы которых подключены к выходу дополнительного формирователя 4 уровня дискриминации, а выходы с входами дополнительных формирователей 14 сигналов. Выходы формирователей 12 сигналов и дополнительных формирователей 14 сигналов подключены к входам элементов ИЛИ 15 и элементов И 16 первой группы, выходы которых соединены с числовым регистром 17 и с первыми входами триггеров 18 первой группы, соединенных с первыми входами элементов И 19 второй группы, вторые входы и выходы которых подключены к дополнительному блоку 20 управления, соединенному с блоком 1 управления. Вторые входы триггеров 18 первой группы подключен к вторым входам триггеров 21 второй группы и дополнительному блоку 20 управления. Первые входы триггеров 2 второй группы соединены с выходами группы элементов ИЛИ 15, а выходы триггеров 21 второй группы подключены к первым входам элементов И 22 третьей группы, вторые входы и выходы которых соединены с дополнительны блоком 20 управления.

Блок 1 управления включает в себя Элементы И, ИЛИ, счетчик на j-К триггерах, инверторы, усилители мощности для стандартных сигналов, триггеры опроса и задания режима, элементы задержки.

В режиме считывания информации с блока 1 управления запускаются ключи X и У (в случае необходимости и со сдвигом по времени), причем длительность запускающих импульсов определяется элементами задержки, элементами И и ИЛИ и триггером опроса. Затем через определенное время блок 1 управления выдает сигналы на формирователь стробирующих импульсов, усилители воспроизведения. Задание уровня дискриминации с помощью формирователя уровня дискриминации регулируется с помощью блока управления.

Дополнительный блок 20 управления содержит элементы И, ИЛИ, НЕ, триггер установки режима, триггер двой|ного или многократного стробирования счетчик количества стробирующих импульсов и инверторы. Работа дополнительного формирователя уровня дискриминации, дополни тельных дискриминаторов, стробирование дополнительных усилителей воепроизведения и управление группами, элементов И и ИЛИ осуществляется син хронно с работой блока 1 управления с помощью дополнительного блока 20 управления. При поступлении сигнала считывания из блока 1 управления на ключи 2 X и У происходит считывание сигналов по определенному гщресу из накопителя 10, которые поступают на входы усилителей 8 считывания и вход дополнительных усилителей 9 считывания. В этом же такте считывания с другого входа блока 1 управления запускается блок 5 задержки, по -выходным сигналам которого (первьлй и второй выход) запускается и формируется длительность импульса строба на формирователе 6 стробирукяцих импульсов Выходной импульс формирователя стробирующих импульсов служит в качестве стробирующего импульса для 1(силителе 8 считывания. По истечении некоторого наперед заданного времени по срав нению со стробирующим импульсом, поступившим на усилители считывания по управляющему импульсу из блока 1 управления, блок 5 задержки (третий и четвертый выход) запускает- и формирует длительность импульса строба для Дополнительных усилителей 9. Это позволяет стробировать один и тот же сигнал чтения, поступивший из накопителя 10 дважды (аналогичная схема ЗУ может быть выполнена и для многократного стробирования Ьдного и того же сигнала). Поэтому в предложенном запоминающем устройстве возможно решение рационального расположения стробирующих импульсов, когда помеха затухает, а сигнал чтения еще относительно велик. Аппаратное сравнение правильности считывания 1 или 0 осущест вляется с помощью усилителя 8 и дополнительного усилителя 9, на которые проходят не только стробируияцие сигналы в разное время, но и в разные уровни дискриминации. Разные уровни дискриминации подаются с помсмцью действия формирователя 3 уровня дискриминации и дополнительного формирователя 4 уровня дискриминации на дискриминаторы 11 и дополнительные дискриминаторы 13. Дискриминаторы 11 и дополнительные дискриминаторы 13 соединены с формирователем 12 сигналов и дополнительными формирователями сигналов 14, на которых независимо формируются сигналы чтения, считанные по одному и тому же разряду. Эти сигналы поступают на элементы и 16 и элементы ИЛИ 15. В том случае, если сформированы 1 формирователем сигналов 12 и дополнительньлм формирователем 14 сигналов,происхолит, запись 1 в числовой регистр 17. Если же на элементы И 16 и элементы ИЛИ 15 поступают разные информационные сигнс1лы, т.е. 1 и О запись в числовой регистр 17 не происходит/ а происходит поразрядная запись триггера 18 первой группы триггерюв 21 второй группы, т.е. запись О или 1 (или наоборот). Перед этой записью триггеры первой и второй группы по сигналу с дополнительного блока 20 управления сбрасываются в О. После записи информации в эти триггеры происходит опрос состояния триггеров путем подачи управляющего сигнала (потенциала) с дополнительного блока 20 управления на вторые входы элементов И 19 второй группы и вторые входы элементов И 22 третьей группы. В случае несоответствия с формированных сигнашов в формирователе сигналов и в дополнительном формирователе 14 сигналов с выходов соответствующих разрядов элементов И 19 второй группы и элементов И 22 третьей группы в дополнительный блок 20 управленияпоразрядно приходят сигналы 1 и О (или наоборот). Это служит причиной выработки управляющего сигнала дополнительным блоком управления 20, который поступает в блок 1 управления на повторный опрос данного адреса слова или фиксации возможной информационной ошибки в данном слове. Такое воспроизведение одного и того же сигнала позволяет исключить информационную ошибку при определении считанного сигнала 1 или О. Поэтому использование предлагаемого запоминающего устройства в цифровой вычислительной машине может удовлетворить повышенные технические требования к информационной надежности и исключить случайное воспроизведение ложной информации из-за случайных и квазидетерминированных помех. Внедрение такого запоминающего устройства будет способствовать эффективности использования не только запоминающего устройства, но и ЦВМ в целом. Формула изобретения . Запоминакяцее устрюйство, содержащее накопитель, входы которого подключены через координатные ключи к первому входу основного блока управления, выходы накопителя через основные усилители считывания подключены к первым входам основных дискриминаторов, выходы которых подключены к входам основных формирователей сиг- налов, второй выход основного блока

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1981 |

|

SU982093A1 |

| Запоминающее устройство | 1978 |

|

SU781971A1 |

| Запоминающее устройство | 1982 |

|

SU1062787A1 |

| Блок считывания информации для доменного запоминающего устройства | 1980 |

|

SU930381A1 |

| Запоминающее устройство | 1979 |

|

SU809364A1 |

| Запоминающее устройство | 1982 |

|

SU1049969A1 |

| Блок считывания информации для доменного запоминающего устройства | 1983 |

|

SU1091224A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Запоминающее устройство | 1979 |

|

SU809368A1 |

| Блок считывания для запоминающего устройства | 1981 |

|

SU959155A1 |

Авторы

Даты

1981-02-28—Публикация

1979-05-31—Подача