(54) БЛОК СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА

| название | год | авторы | номер документа |

|---|---|---|---|

| "Запоминающее устройство | 1979 |

|

SU809369A1 |

| Блок считывания информации для запоминающего устройства | 1985 |

|

SU1283849A1 |

| Блок воспроизведения для запоминающего устройства | 1980 |

|

SU902070A1 |

| Запоминающее устройство | 1978 |

|

SU781971A1 |

| Запоминающее устройство | 1979 |

|

SU809350A1 |

| Запоминающее устройство | 1982 |

|

SU1049969A1 |

| Запоминающее устройство | 1979 |

|

SU824304A1 |

| Блок считывания информации для доменного запоминающего устройства | 1980 |

|

SU930381A1 |

| Блок считывания информации для доменного запоминающего устройства | 1983 |

|

SU1091224A1 |

| Блок считывания информации для доменного запоминающего устройства | 1983 |

|

SU1105939A1 |

1

Изобретение относится к вычислительной технике и предназначено для использования в цифровых вычислительных машинах.

Известен блок считывания для запоминающего устройства, содержащий предва- 5 рительный усилитель воспроизведения и усилитель воспроизведения. Для повышения надежности предвари ельный усилитель воспроизведения и усилитель воспроизведения соединены с амплитудным селектором и дис- ,Q криминатором 1.

Однако введение стробирования и дискриминации сигнала чтения не обеспечивает высокую надежность этого блока считывания, так как эффективность стробирования и дискриминации ограничена использовани- 15 ем только жесткого стробирования и постоянным уровнем дискриминации.

Наиболее близким техническим решением к данному изобретению является блок считывания для запоминающего устройства, со- о держащий входной каскад, являющийся входным каскадом блока, соединенный с входами линейных предварительных усилителей воспроизведения, другие входы которых подключены к источнику стробирующих импульсов, а выходы через дискриминаторы - к усилителям воспроизведения или к элементам формирования стандартного сигнала 2J.

Недостатком известного блока является то, что в нем отсутствуют схемные решения, позволяющие верировать уровень дискриминации сигнала чтения в зависимости от изменения условий считывания, а также то, что в нем не предусмотрено плавающее стробирование сигнала чтения.

Целью изобретения является повыщекие надежности блока считывания для запоминающего устройства.

Поставленная цель достигается тем, что в блок считьшания для запоминающего устройства, содержащий корреляторы, первые входы которых, являются входами блока считывания, а выходы подключены к первым входам предварительных усилителей воспроизведения, выходы предварительных усилителей воспроизведения соединены с первыми входами усилителей воспроизведения, выходы которых подключены к входам числового регистра, а вторые входы - к выходу дискриминатора, первый и второй выходы тактового генератора подключены соответственно к входам формирователей записи и считывания сигналов, выходы которых соединены с входами эталонных элементов памяти, введены три дополнительных коррелятора, сумматор и дополнительный предварительный усилитель воспроизведения, выход которого подключен к вторым входам предварительных усилителей воспроизведения, а вход - к первому входу сумматора и к выходу первого дополнительного коррелятора, первый и второй входы которого соединены с выходом одного из эталонных элементов памяти, с вторыми вхоДами корреляторов и с первым входом второго дополнительного коррелятора, второй вход которого подключен к выходу другого эталонного элемента памяти и к входам третьего дополнительного коррелятора, причем выходы второго и третьего дополнительных корреляторов соединены соответственно с вторым и третьим входами сумматора, выход которого подключен к выходу дискриминатора.

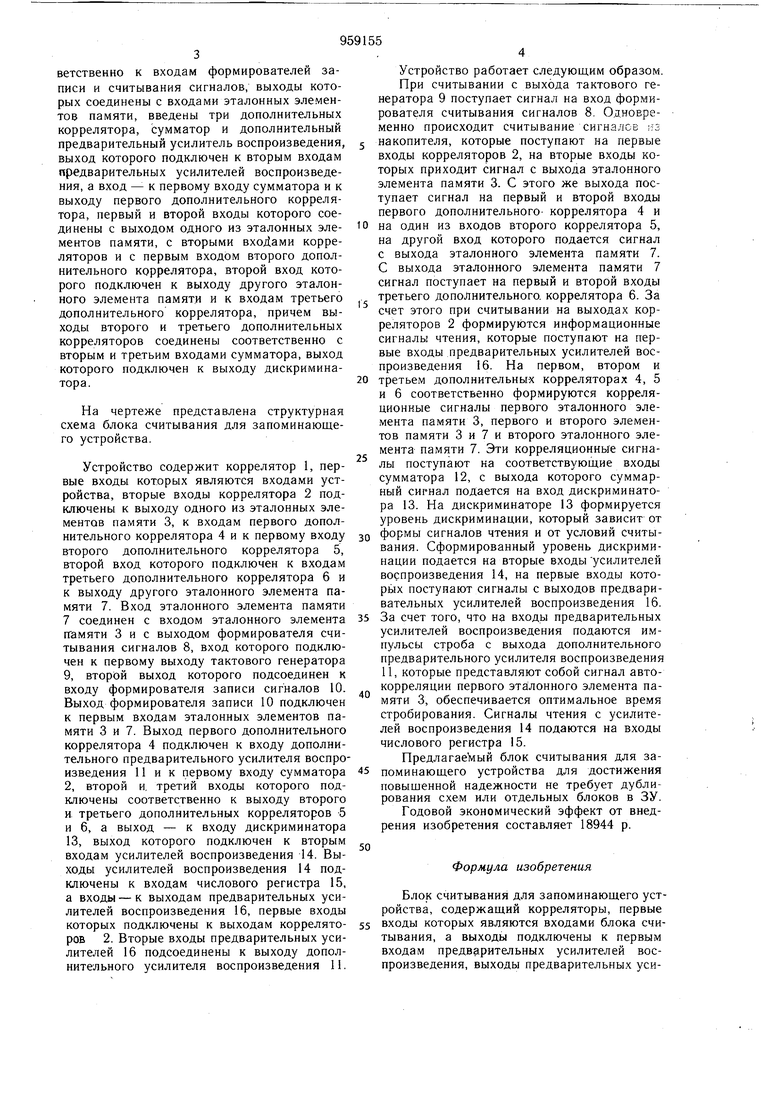

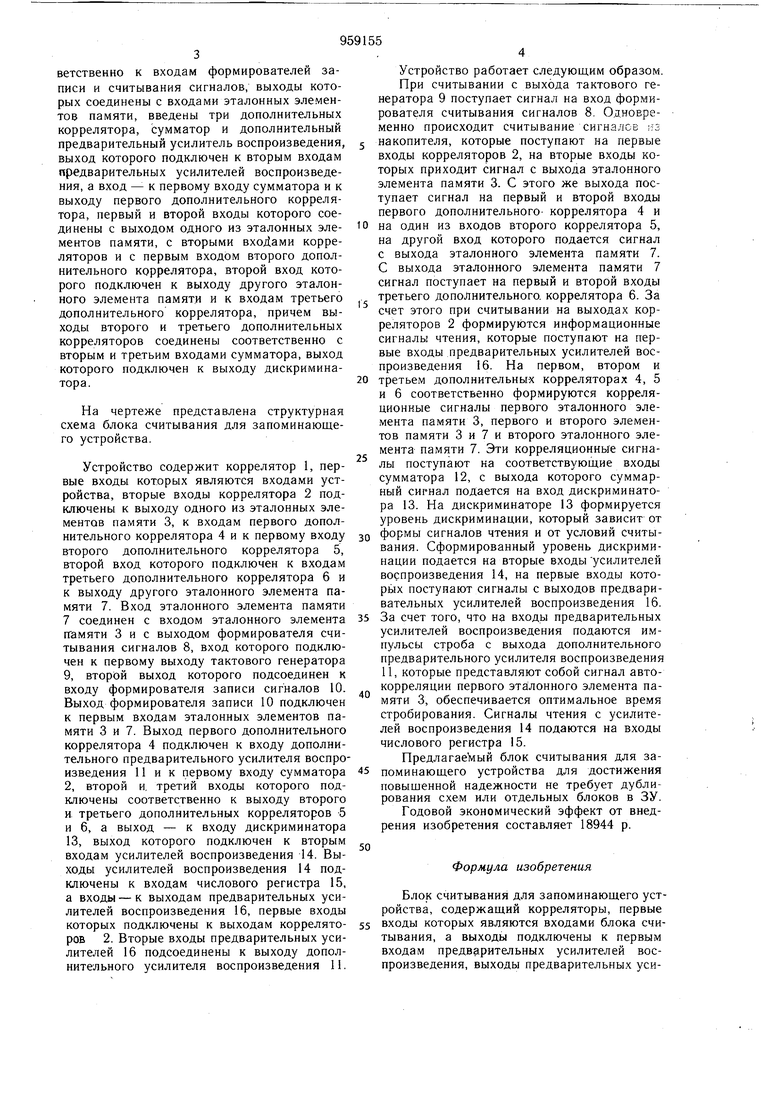

На чертеже представлена структурная схема блока считывания для запоминающего устройства.

Устройство содержит коррелятор 1, первые входы которых являются входами устройства, вторые входы коррелятора 2 подключены к выходу одного из эталонных элементов памяти 3, к входам первого дополнительного коррелятора 4 и к первому входу второго дополнительного коррелятора 5, второй вход которого подключен к входам третьего дополнительного коррелятора 6 и к выходу другого эталонного элемента памяти 7. Вход эталонного элемента памяти 7 соединен с входом эталонного элемента памяти 3 и с выходом формирователя считывания сигналов 8, вход которого подключен к первому выходу тактового генератора 9, второй выход которого подсоединен к входу формирователя записи сигналов 10. Выход формирователя записи 10 подключен к первым входам эталонных элементов памяти 3 и 7. Выход первого дополнительного коррелятора 4 подключен к входу дополнительного предварительного усилителя воспроизведения 11 и к первому входу сумматора 2, второй и. третий входы которого подключены соответственно к выходу второго и третьего дополнительных корреляторов 5 и 6, а выход - к входу дискриминатора 13, выход которого подключен к вторым входам усилителей воспроизведения 14. Выходы усилителей воспроизведения 14 подключены к входам числового регистра 15, а входы - к выходам предварительных усилителей воспроизведения 16, первые входы которых подключены к выходам корреляторов 2. Вторые входы предварительных усилителей 16 подсоединены к выходу дополнительного усилителя воспроизведения И.

Устройство работает следующим образом. При считывании с выхода тактового генератора 9 поступает сигнал на вход формирователя считывания сигналов 8. Одновременно происходит считывание сигналов из

накопителя, которые поступают на первые входы корреляторов 2, на вторые входы которых приходит сигнал с выхода эталонного элемента памяти 3. С этого же выхода поступает сигнал на первый и второй входы первого дополнительного коррелятора 4 и

0 на один из входов второго коррелятора 5, на другой вход которого подается сигнал с выхода эталонного элемента памяти 7. С выхода эталонного элемента памяти 7 сигнал поступает на первый и второй входы третьего дополнительного, коррелятора 6. За счет этого при считывании на выходах корреляторов 2 формируются информационные сигналы чтения, которые поступают на первые входы предварительных усилителей воспроизведения 16. На первом, втором и

третьем дополнительных корреляторах 4, 5 и 6 соответственно формируются корреляционные сигналы первого эталонного элемента памяти 3, первого и второго элементов памяти 3 и 7 и второго эталонного элемента памяти 7. Эти корреляционные сигналы поступают на соответствующие входы сумматора 12, с выхода которого суммарный сигнал подается на вход дискриминатора 13. На дискриминаторе 13 формируется уровень дискриминации, который зависит от

0 формы сигналов чтения и от условий считывания. Сформированный уровень дискриминации подается на вторые входы усилителей воспроизведения 14, на первые входы которь1х поступают сигналы с выходов предваривательных усилителей воспроизведения 16.

5 За счет того, что на входы предварительных усилителей воспроизведения подаются импульсы строба с выхода дополнительного предварительного усилителя воспроизведения 11, которые представляют собой сигнал автокорреляции первого эталонного элемента памяти 3, обеспечивается оптимальное время стробирования. Сигналы чтения с усилителей воспроизведения 14 подаются на входы числового регистра 15.

Предлагаемый блок считывания для за5 поминающего устройства для достижения повыщенной надежности не требует дублирования схем или отдельных блоков в ЗУ. Годовой экономический эффект от внедрения изобретения составляет 18944 р.

Формула изобретения

Блок считывания для запоминающего устройства, содержащий корреляторы, первые 5 входы которых ЯВЛЯЮТСЯ входами блока считывания, а выходы подключены к первым входам предварительных усилителей воспроизведения, выходы предварительных усилителей воспроизведения соединены с первыми входами усилителей воспроизведения, выходы которых подключены к входам числового регистра, а вторые входы - к выходу дискриминатора, первый и второй выходы тактового генератора подключены соответственно к входам формирователей записи и считывания сигналов, выходы которых соединены с входами эталонных элементов памяти, отличающийся тем, что, с целью повышения надежности, в него введены трИ дополнительных коррелятора, сумматор и дополнительный предварительный усилитель воспроизведения, выход которого подключей к вторым входам предварительных усилителей воспроизведения, а вход - к первому входу сумматора и к выходу первого дополнительного коррелятора, первый и второй входы которого соединены с выходом одного из эталонных элементов памяти, с вторыми входами корреляторов и с первым входом второго дополнительного коррелятора, второй вход которого подключен к выходу другого эталонного элемента памяти и к входам третьего дополнительного коррелятора, причем выходы второго и третьего дополнительных корреляторов соединены соответственно с вторым и третьим входами сумматора, выход которого подключен к выходу дискриминатора. Источники информации, принятые во внимание при экспертизе 1.Шигин А. Г. и Дерюгин А. А. Цифровые вычислительные машины. М., «Энергия, 1975, с. 99-102. 2.Гальперин Е. И. и Гордонов А. Ю. Специальные элементы запоминающих устройств ЭВМ на полупроводнико вых прибоIJ J П I D -- LJ i i IICI j ч -f --.- - - -- --J pax. M., «Советское радио, 1971, с. 123- 125.

Авторы

Даты

1982-09-15—Публикация

1981-02-10—Подача