1

Изобретение относится к вычислительной технике и предназначено для использования в магнитных запоминающих устройствах (ЗУ).

Известен блок воспроизведения для ЗУ, содержащий буферный каскад, мостовую схему, короткозамкнутую линию задержки и дифференциальный усилитель 1.

Однако указанный блок не позволяет осуществить воспроизведение сигналов чтения в ЗУ с высокой степенью надежности, так как в нем введено только стробирование сигналов чтения при их воспроизведении, которое не учитывает уровень помех в разрядносчитывающих линиях.

Наиболее близок к предлагаемому блок, содержащий в каждом разряде нелинейные элементы, включенные между разрядно-считывающими линиями и соответствующими входами усилителей воспроизведения, дискриминатор и формирователь стробирующих импульсов 2.

В данном блоке отсутствуют элементы и схемы, позволяющие учитывать при воспроизведении сигнала чтения уровень помех, который может меняться из-за различных

причин от одного цикла считывания к другому.

Цель изобретения - повышение надежности ЗУ.

Поставленная цель достигается тем, что

5 в блок воспроизведения для запонимающего устройства, содержащий первый предварительный усилитель воспроизведения, вход которого подключен к одному из входов блока, второй предварительный усилитель воспроизведения, вход которого подсоединен к другому входу блока, дискриминатор и формирователь стробирующих импульсов, выходы которых соединены с соответствующими входами усилителя воспроизведения, введены два инвертора, два сумматора и дели 5 тель напряжения, вход которого подключен к выходу второго предварительного усилителя воспроизведения, входу формирователя стробирующих импульсов и входу первого сумматора, второй вход которого подключен

20 к выходу первого инвертора, а выход - ко входу второго инвертора, выход которого подключен к перво,му входу второго сумматора, второй вход которого соединен со входом первого инвертора и выходом первого

предварительного усилителя воспроизведения, причем выход второго сумматора подключен к усилителю воспроизведения, а выход делителя напряжения - ко входу дискриминатора.

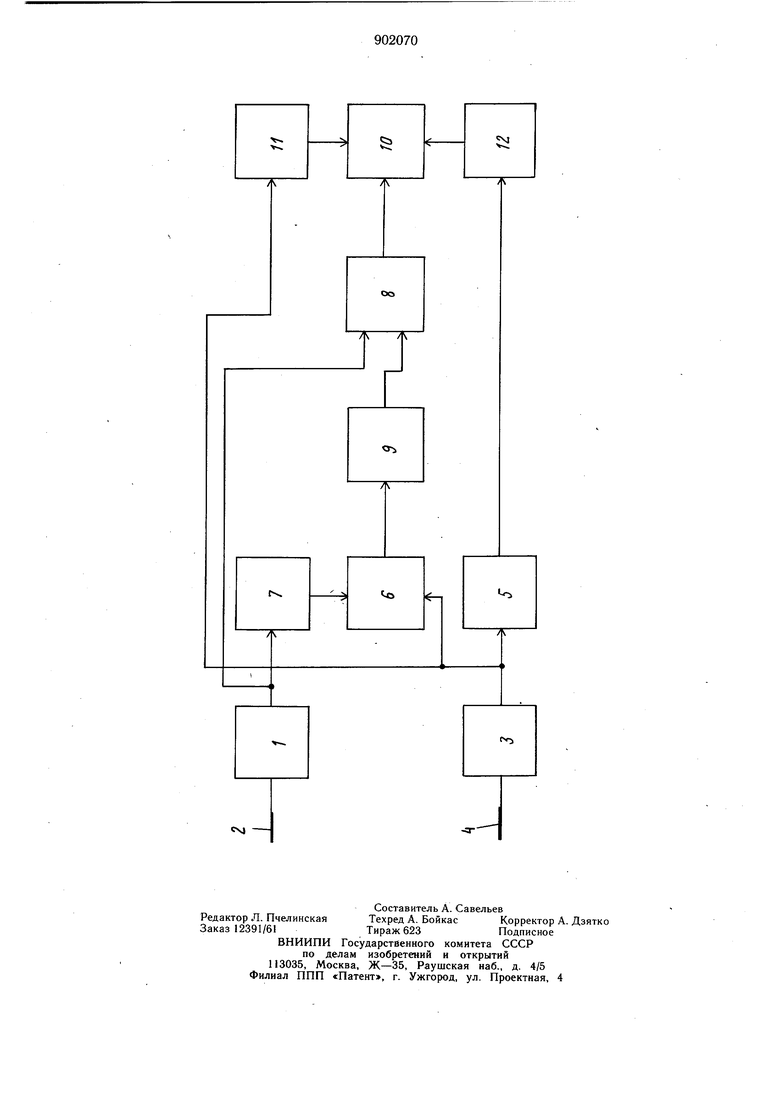

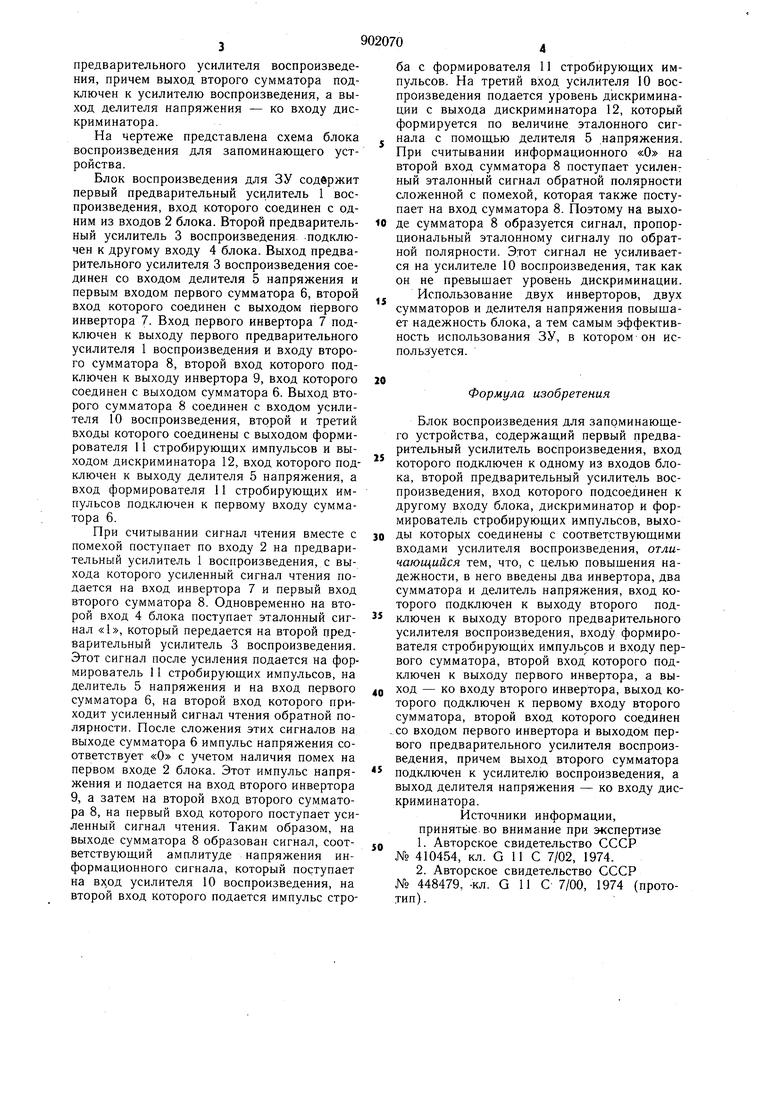

На чертеже представлена схема блока воспроизведения для запоминающего устройства.

Блок воспроизведения для ЗУ содержит первый предварительный усилитель 1 воспроизведения, вход которого соединен с одним из входов 2 блока. Второй предварительный усилитель 3 воспроизведения -подключен к другому входу 4 блока. Выход предварительного усилителя 3 воспроизведения соединен со входом делителя 5 напряжения и первым входом первого сумматора 6, второй вход которого соединен с выходом первого инвертора 1. Вход первого инвертора 7 подключен к выходу первого предварительного усилителя 1 воспроизведения и входу второго сумматора 8, второй вход которого подключен к выходу инвертора 9, вход которого соединен с выходом сумматора 6. Выход второго сумматора 8 соединен с входом усилителя 10 воспроизведения, второй и третий входы которого соединены с выходом формирователя 11 стробирующих импульсов и выходом дискриминатора 12, вход которого подключен к выходу делителя 5 напряжения, а вход формирователя 11 стробирующих импульсов подключен к первому входу сумматора 6.

При считывании сигнал чтения вместе с помехой поступает по входу 2 на предварительный усилитель 1 воспроизведения, с выхода которого усиленный сигнал чтения подается на вход инвертора 7 и первый вход второго сумматора 8. Одновременно на второй вход 4 блока поступает эталонный сигнал «1, который передается на второй предварительный усилитель 3 воспроизведения. Этот сигнал после усиления подается на формирователь 11 стробирующих импульсов, на делитель 5 напряжения и на вход первого сумматора 6, на второй вход которого приходит усиленный сигнал чтения обратной полярности. После сложения этих сигналов на выходе сумматора 6 импульс напряжения соответствует «О с учетом наличия помех на первом входе 2 блока. Этот импульс напряжения и подается на вход второго инвертора 9, а затем на второй вход второго сумматора 8, на первый вход которого поступает усиленный сигнал чтения. Таким образом, на выходе сумматора 8 образован сигнал, соответствующий амплитуде напряжения информационного сигнала, который поступает на вхрд усилителя 10 воспроизведения, на второй вход которого подается импульс строба с формирователя 11 стробирующих импульсов. На третий вход усилителя 10 воспроизведения подается уровень дискриминации с выхода дискриминатора 12, который формируется по величине эталонного сигнала с помощью делителя 5 напряжения. При считывании информационного «О на второй вход сумматора 8 поступает усилен: ный эталонный сигнал обратной полярности сложенной с помехой, которая также поступает на вход сумматора 8. Поэтому на выходе сумматора 8 образуется сигнал, пропорциональный эталонному сигналу по обратной полярности. Этот сигнал не усиливается на усилителе 10 воспроизведения, так как он не превышает уровень дискриминации. Использование двух инверторов, двух сумматоров и делителя напряжения повышает надежность блока, а тем самым эффективность использования ЗУ, в котором-он используется.

Формула изобретения

Блок воспроизведения для запоминающего устройства, содержащий первый предварительный усилитель воспроизведения, вход

которого подключен к одному из входов блока, второй предварительный усилитель воспроизведения, вход которого подсоединен к другому входу блока, дискриминатор и формирователь стробирующих импульсов, выходы которых соединены с соответствующими входами усилителя воспроизведения, отличающийся тем, что, с целью повыщения надежности, в него введены два инвертора, два сумматора и делитель напряжения, вход которого подключен к выходу второго подключей к выходу второго предварительного усилителя воспроизведения, входу формирователя стробирующих импульсов и входу первого сумматора, второй вход которого подключен к выходу первого инвертора, а выход - ко входу второго инвертора, выход которого подключен к первому входу второго сумматора, второй вход которого соединен .со входом первого инвертора и выходом первого предварительного усилителя воспроизведения, причем выход второго сумматора подключен к усилителю воспроизведения, а выход делителя напряжения - ко входу дискриминатора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 410454, кл. G 11 С 7/02, 1974.

2. Авторское свидетельство СССР № 448479, -кл. G 11 С 7/00, 1974 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок считывания информации для доменного запоминающего устройства | 1980 |

|

SU930381A1 |

| Запоминающее устройство | 1979 |

|

SU809350A1 |

| Блок считывания для запоминающего устройства | 1981 |

|

SU959155A1 |

| Блок считывания информации для запоминающего устройства | 1985 |

|

SU1283849A1 |

| Запоминающее устройство | 1978 |

|

SU781971A1 |

| "Запоминающее устройство | 1979 |

|

SU809369A1 |

| Устройство для считывания информации из накопителя | 1980 |

|

SU864334A1 |

| Запоминающее устройство | 1982 |

|

SU1049969A1 |

| Устройство для коррекции уровня ограничения при воспроизведении двоичной последовательности с носителя магнитной записи | 1989 |

|

SU1667152A2 |

| Стробоскопический преобразователь | 1990 |

|

SU1721522A1 |

Авторы

Даты

1982-01-30—Публикация

1980-06-24—Подача