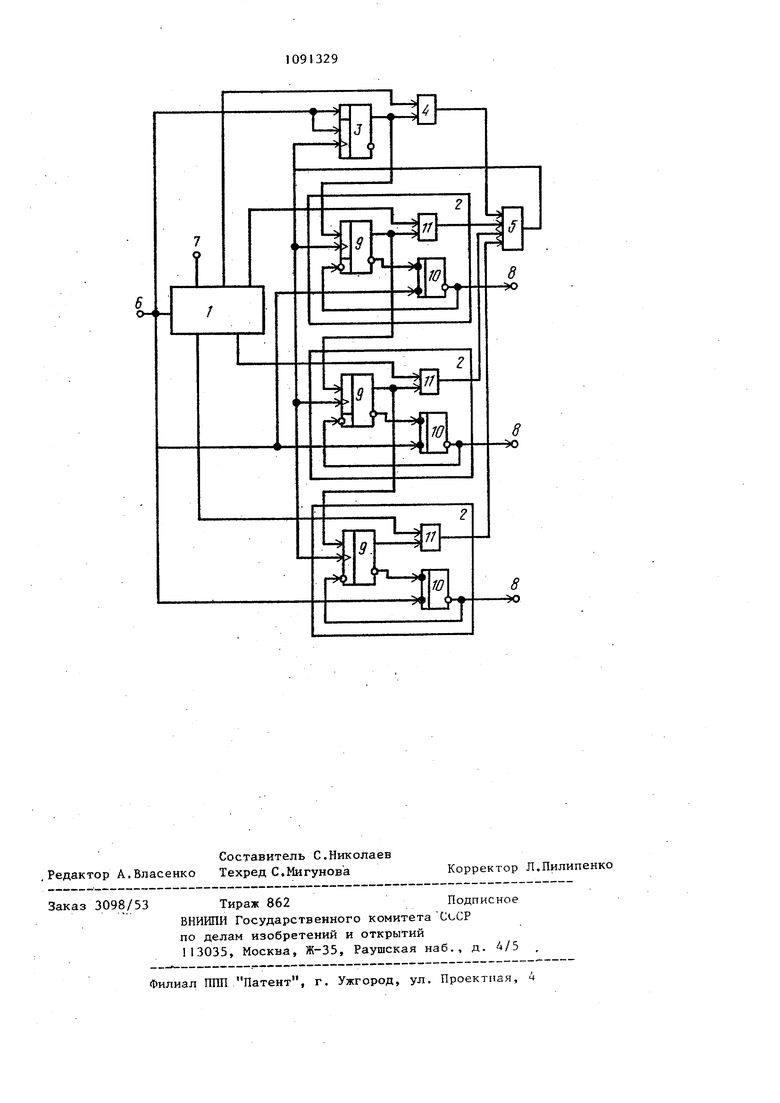

.11 Изобретение относится к импульсной технике и может найти применение в качестве п-канального фильтра для различения импульсных сигналов по частоте в полосе частот. Известен частотный дискриминатор состоящий из п каналов, каждый из которых содержит одновибратор, два элемента И, элемент ИЛИ, интегратор и триггер С3 . Указанное устройство обеспечивает только определение факта наличия, на выходе импульсов данной частоты без сохранения параметров этих импульсов. Наиболее близким к предлагаемому является частотный дискриминатор, со держащий дополнительный триггер,.дополнительный счетчик импульсов, дополнительный элемент совпадения, входы которого соединены с входом установки в нуль счетчика импульсов и выходом дополнительного триггера, первый вход которого Подключен к выходу дополнительного счетчика импуль сов, второй вход - к выходу элемента задежки и п каналов, каждый из которых содержит входной элемент И, первый вход которого соединен с шино эталонного сигнала, второй вход подключен к выходу первого триггера, первый вход которого соединен с выко , дом входного элемента И, а второй вход - с входной тиной, выходной элемент И, первый вход которого подключен к входнойшине, и второй триг гер, включенный между выходом счетчика импульсов и вторым входом выходного элемента И, причем вторые входы первого и второго триггеров в каждом, кроме последнего, канале сое |динены с выходом второго триггера последующего канала, вторые входы первого и второго триггеров последне го канала соединены с выходом дополнительного счетчика импульсов, один вход которого подключен к выходу ВХО него элемента И п-го канала, а второй вход - к входной шине, которая через элемент задержки соединена с третьими входами вторых триггеров всех каналов t2 . Недостатками известного устройства являются низкая функциональная на дежяость и сложное схемное решение Цель изобретения - повьшгение функ циональной надежности при одновре 1енном упрощении устройства. 9 Поставленная цель достигается тем, что в частотный дискриминатор, содержащий счетчик импульсов, элемент И и п каналов дискриминации, каждый из которых включает элемент И и асинхронный, триггер, первьй вход которого подключен к входу установки в нуль счетчика импульсов и входной шине, введены синхронный триггер, вход установки в единицу и информационный вход которого подключены к входной шине, прямой выход - к первому входу элемента И, и элемент ИЛИ, выход которого соединен с тактовым входом синхронного триггера, а в каждый канал дискриминации введен синхронный триггер прямой выход которого соединен с первым входом элемента И данного канала и информационным входом синхронного триггера последующего канала дискриминации, инверсный выход - с вторым входом асинхронного триггера данного канала дискриминации, выход которого подключен к соответствующей выходной шине и входу установки в нуль синхронного триггера данного канала дискриминации, причем вторые входы всех элементов И подключены к соответствующим выходам счетЧика импульсов, их выходы - к входам элемента ИЛИ, при этом тактовые входы всех синхронных триггеров каналов дискриминации соединены с входом синхронного триггера, а вход счетчика импульсов подключен к шине тактовых импульсов. На чертеже приведена функциональная схема частотного дискриминатора. Частотный дискриминатор содержит источник I импульсов, каналы 2 дискриминации, триггер 3 синхронный, элемент И 4, элемент ИЛИ 5, входную шину 6, шину 7 тактовых импульсов и выходные шины 8. Каждый из каналов 2 дискриминации включает триггер 9, синхронный, триггер 10 асинхронный и элемент Mil. В каждом канале 2 прямой выход триггера 9 соединен с первым входом элемента И 11 данного канала 2 и информационным входом триггера 9 последующего канала 2. Инверсный выход триггера 9 соединен с вторьм входом триггера 0, выход которого подключен к выходной щине 8 данного канала и входу установки в нуль триггера 9. Вход установки в единицу и информадаонный вход триггера 3 объединены и подключены к входной шине 6, к которой .подключены также первые входы всех триггеров 10 и вход установки в нуль счетчика 1. Вход счетчика 1 подключен к шине 7 тактовых импульсов . Вторые входы элемента И 4 всех элементов И I1 подключены к соответствующим выходам счетчика 1. Выходы элемента И 4 и всех элементов И 11 соединены с входами элемента ИЛИ 5, выход которого подключей к тактовым входам тригге ра 3 и всех триггеров 9, Прямой выход триггера 3 соединен с первым входом элемента И 4 и информационным входом триггера 9 первого канала 2, Триггер 10 каждого канала 2 вьшол нен на двух элементах И-НЕ. Количество вторых входов у элемен тов 4 и И 1I может быть различным и определяется кодовой комбинацией, ко торую дешифрует соответствующий элемент 4 или И 1 1 . Чпстотный дискриминатор работает следующим образом. При включении напряжения питания низкий потенциал, присутствующий на входной шине 6, и импульсы тактовой частоты, поступающие на шину 7, прив дят частотный дискриминатор в состоя ние, при котором триггер 9 и триггер 10 каждого канала 2, а также триггер 3 обнулены (на прямых выходах этих триггеров присутствует низкий потенциал, а на инверсньк - высокий). Сче чик 1 импульсов считает импульсы так товой частоты и может периодически п-ереполняться, но кодовые комбинации счетчика I импульсов не дешифруются элементами И 11 каналов 2 и элементо И 4, так как появление сигнала дешиф рации на выходе каждого из этих элементов запрещено низким потенциалом поступающим с прямого выхода соотве ствующего синхронного триггера. При поступлении на входную шину первого входного импульса счетчик 1 импульсов обнуляется,одновременно происходит установка триггера 3 в единичное состояние. Таким образом, частотный дискриминатор оказьшается приведенным в исходное состояние, т.е. подготовлен к различению по частоте входных импульсов, следуюгци на шину 6. По окончании на входной шине 6 импульса в счетчик 1 импульсов начинают поступать тактовые импульсы. Верх}шю границу частоты среза первого канала 2 определяет кодовая комбинация, дешифруемая элементом К 4. Нижняя граница частоты среза первого канала определяется кодовой комбинацией, дешифрируемой элементом Н 11 первого канала 2, в то же время нижняя граница частоты среза для первого канала является верхней границей частоты среза для второго канала 2, а Н1ажняя граница частоты среза для второго канала 2, которая определяется кодовой комбинацией дешифрируемой элементом И 11 второго канала, является верхней границей частоты среза для третьего канала и -т.д. При появлении в счетчике 1 кодовой комбинации, на кото.рую настроен элемент И 4, этот элемент переключается и на его выходе формируется высокий потенциал, поступающий на выход Элемента ИЛИ 5. Фронтом высокого потенциала, появляющимся на выходе элемента ИЛИ 5, производится установка синхронного триггера 9 первого канала 2 в единичное состояние и установка синхронного триггера 3 в нулевое состояние, а также подтверждение нулевого состояния синхронных триггеров 9 остальньгх каналов 2. Появление низкого потенциала на прямом выходе синхронного триггера 3 закрьгоает элемент И 4, что приводит к появлению низкого потенциала на выходе элемента ИЛИ 5. Появление низкого потенциала на инверсном выходе синхронного триггера 9 первого канала 2 подготавливает асинхронный триггер 10 к отработке входного импульса. При появлении входного импульса на шине 6 он инвертируется асинхронным триггером 10 первого канала 2 и поступает на шину 8 этого канала. Появление входного импульса на шине 6 вызывает обнуление счетчика 1 импульсов. При появлении выходного импульса на шине 8 первого канала 2 производится переключение синхронного триггера 9 этого канала в исходное нулевое состояние. Однако асинхронный триггер 10 первого канала 2 не переключается в течение длительности входного импульса на шине 6, По, окончании И1.тульса на шине 8 первого канала 2 частотный дискриминатор окаг зывается приведенным в исходное состояние и начинается процесс различения по частоте следующих входных импульсов. Если входной импульс на пшне 6 не появляется после установления в единичное состояние синхронного триггер 9 первого канала 2 и обнуления синхронного триггера 3, то через некотор время в счетчике импульсов появляется кодовая комбинация, на которую настроен элемент И П первого канала 2. Сигнап с выхода элемента И П пер вого канала 2 проходит на выход элеI мента ИЛИ 5,Фронтом сигнала на выход элемента ИЛИ 5 производится установка в единичное состояние синхронного триггера 9 первого канала 2, а также подтверждение нулевого состояния синхронных триггеров 9 остальных каналов 2 и синхронного триггера 3. При появлении входного шчпульса на 6 он инвертируется асинхронным триггером 10 второго канала 2 и поступает на шину 8 этого канала 2.. Если входной импульс на шине 6 появляется после установления в единичное состояние синхронного триггера 9 последующего канала 2 и обнуления синхронного триггера 9 предыдуще го канала 2,то через некоторое время в счетчике 1 импульсов появ1 яется кодовая комбинация, на которую настроен элемент И 11 последующего канала. При появлении входного импульса ha шине 6 процесс формирования импульса на шине 8 последующего канала аналогичен рассмотренному процессу формирования импульса на шине 8 первого или второго каг налов 2о 10 96 Таким образом, если частота входных импульсов находится в полосе прозрачности частотного дискриминатора, то входной импульс инвертируется асинхронным триггером 10 одного из каналов 2 и поступает на шину 8 этого канала. По окончании входного импульса частотный дискриминатор с исходного состояния начинает процесс различения по частоте следуюп1их входных импульсов. Если частота входных импульсов на шине 6 лежит выше верхней границы частоты среза первого канала 2 или ниже нижней границы частоты среза п-го канала 2, то входные импульсы не проходят на шину 8 ни одного из каналов, так как синхронные триггеры 9 всех каналов будут обнулены и высокий потенциал с прямого выхода каждого из синхронных триггеров 9 запрещает переключение соответствующего асинхронного триггера 10. Таким образом, на выходах соответствующих каналов 2 частотного дискриминатора производится вьщеление входных импульсов, частота следования которых находится в полосе прозрачности этих каналов. Предлагаемый частотный дискриминатор приводится в исходное состояние и оказывается подготовленным к обработке следующего входного импульса предыдущим входным импульсом, т.е. имеет практически нулевое время подготовки в обработке входного импульса. При этом он имеет по сравнению с устройством-прототипом более простое схемное решение.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный дискриминатор | 1984 |

|

SU1211868A1 |

| Частотный дискриминатор | 1977 |

|

SU746897A1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| Система связи с асинхронной дельта-модуляцией | 1989 |

|

SU1624695A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Генератор импульсов с увеличивающейся длительностью | 1983 |

|

SU1159157A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Цифровой дискриминатор средней частоты | 1985 |

|

SU1293835A1 |

| Устройство для измерения временных параметров радиоимпульсов | 1977 |

|

SU687415A1 |

| Управляемый делитель частоты следования импульсов | 1990 |

|

SU1793543A1 |

ЧАСТОТНЫЙ ДИСКРИМИНАТОР, содержащий счетчик импульсов, элемент И и п каналов дискриминации, каждый из которых включает элемент И и асинхронный триггер, первый вход которого подключен к входу установки в нуль счетчика импульсов и входной шине, отличающийся тем, что, с целью повышения функциональной надежности при одновременном упрощении, в него введены синх- . ронный -триггер, вход установки в единицу и информационный вход которого подключены к входной шине, прямой выход - к первому входу элемента И, и элемент ИЛИ, выход которого соединен с тактовым входом синхронного триггера, а в каждый канал дискриминации введен синхронный триггер, прямой выход которого соединен с первым входом элемента И данного канала и информационным входом синхронного триггера последующего канала дискриминации, инверсный выход - с вторым входом асинхронного триггера данного канала дискриминации, выход которого подключен к соответствующей вь1ходной щине и входу установки в нуль синхронного триггера данного канала диi скриминации, причем вторые входы всех элементов И подключены к соответс(Л d вующим выходам счетчика импульсов, их выходы - к входам элемента ИЛИ, ПРИ этом тактовые входы всех синхронных триггеров каналов дискриминации соединены с входом синхронного триггера, а вход счетчика Импульсов подключен к шине тактовых импульсо 00 сов. IND со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ПОЛУЧЕНИЯ МУКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2152824C1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Частотный дискриминатор | 1979 |

|

SU885915A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-05-07—Публикация

1983-01-24—Подача