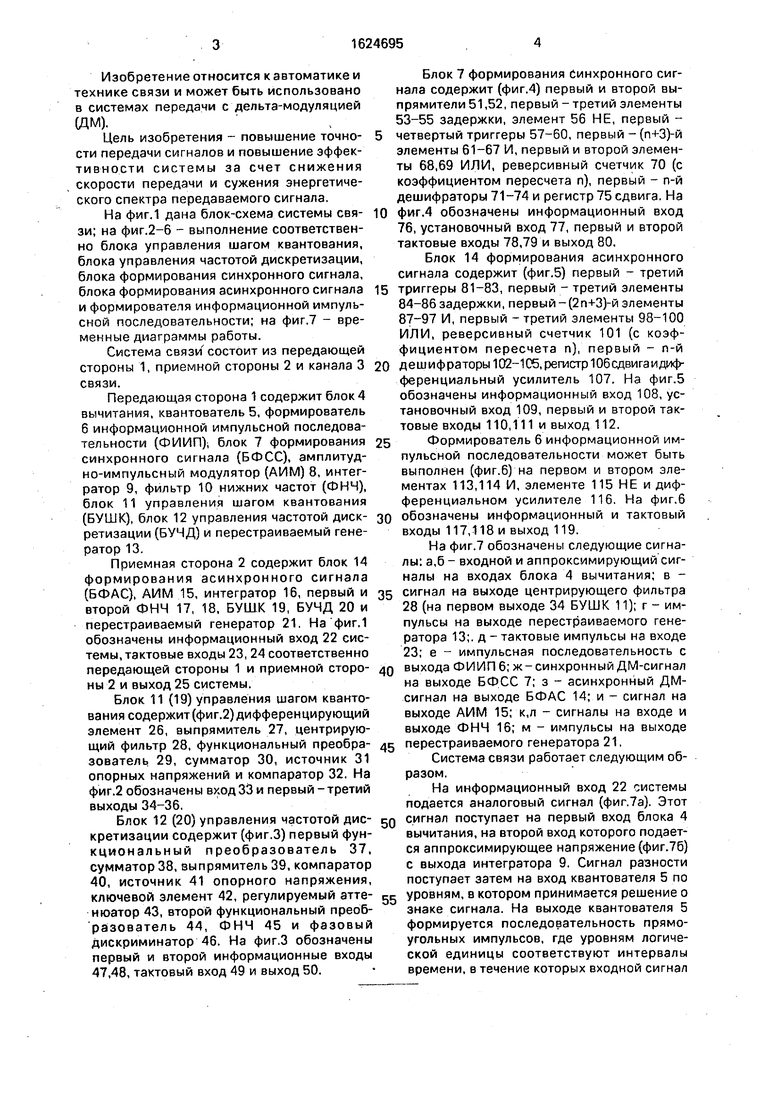

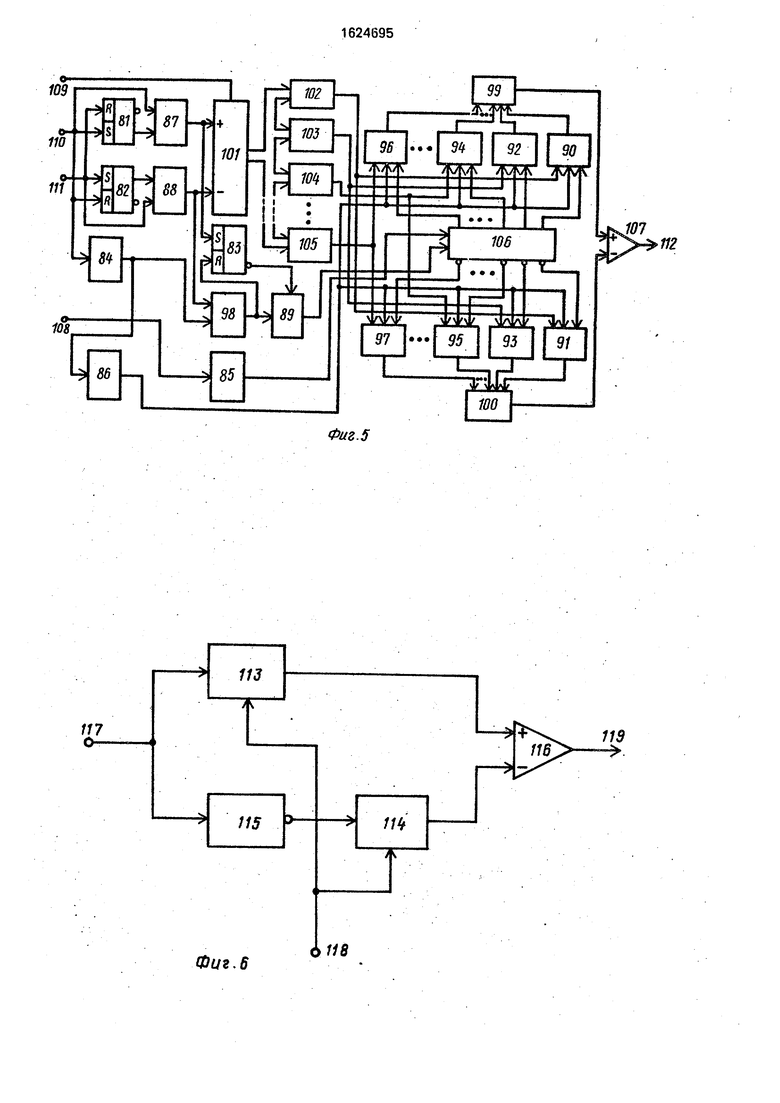

Фиг. 1

Изобретение относится к автоматике и технике связи и может быть использовано в системах передачи с дельта-модуляцией (ДМ).

Цель изобретения - повышение точности передачи сигналов и повышение эффективности системы за счет снижения скорости передачи и сужения энергетического спектра передаваемого сигнала.

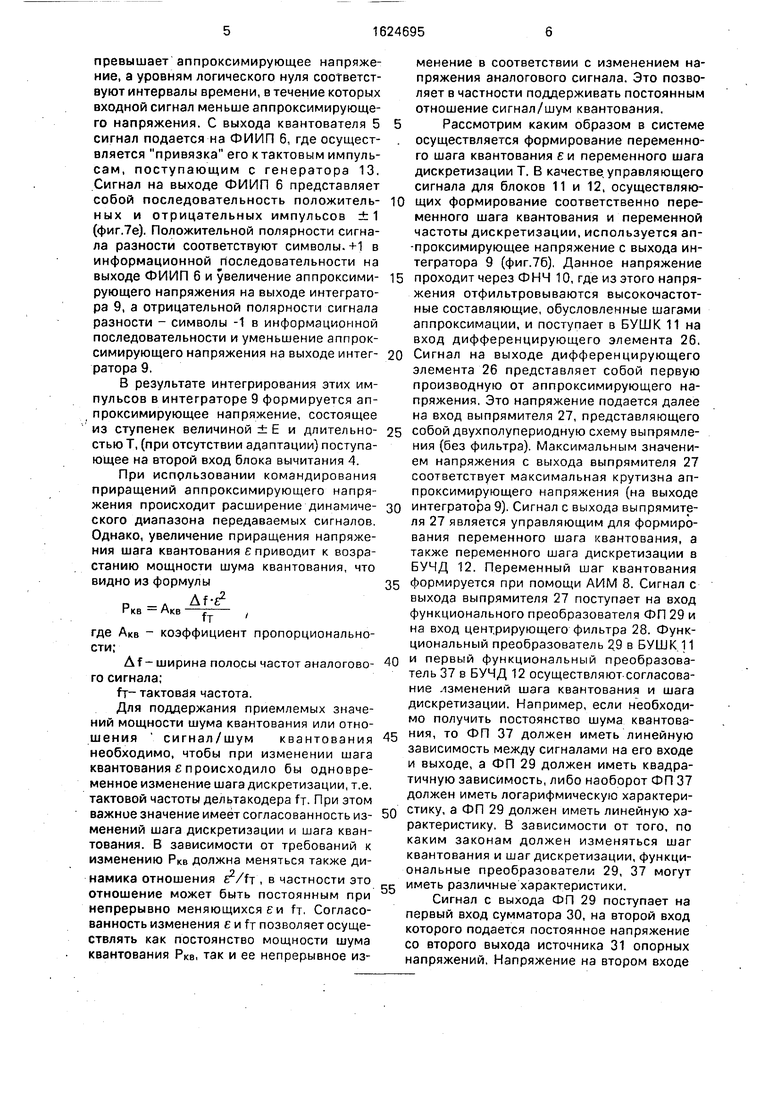

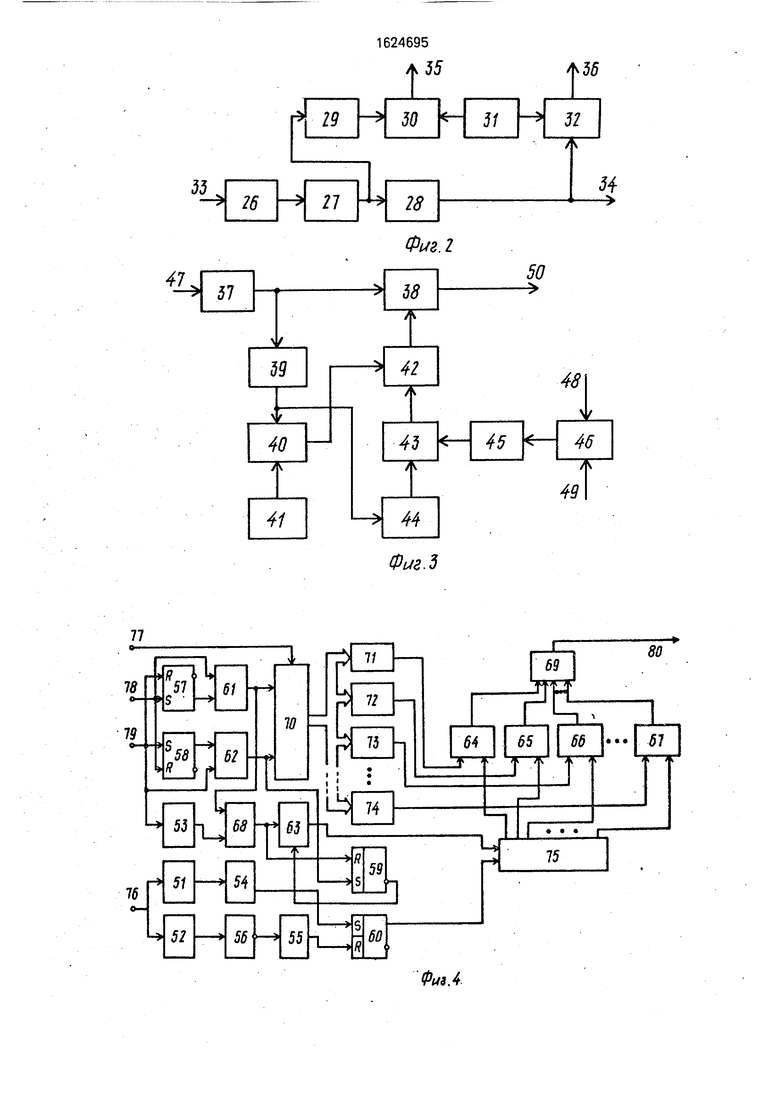

На фиг.1 дана блок-схема системы связи; на фиг.2-6 - выполнение соответственно блока управления шагом квантования, блока управления частотой дискретизации, блока формирования синхронного сигнала, блока формирования асинхронного сигнала и формирователя информационной импульсной последовательности; на фиг.7 - временные диаграммы работы.

Система связи состоит из передающей стороны 1, приемной стороны 2 и канала 3 связи.

Передающая сторона 1 содержит блок 4 вычитания, квантователь 5, формирователь 6 информационной импульсной последовательности (ФИИП), блок 7 формирования синхронного сигнала (БФСС), амплитудно-импульсный модулятор (АИМ) 8, интегратор 9, фильтр 10 нижних частот (ФНЧ), блок 11 управления шагом квантования (БУШК), блок 12 управления частотой дискретизации (БУНД) и перестраиваемый генератор 13.

Приемная сторона 2 содержит блок 14 формирования асинхронного сигнала (БФАС), АИМ 15, интегратор 16, первый и второй ФНЧ 17, 18, БУШК 19, БУНД 20 и перестраиваемый генератор 21. На фиг.1 обозначены информационный вход 22 системы, тактовые входы 23, 24 соответственно передающей стороны 1 и приемной стороны 2 и выход 25 системы.

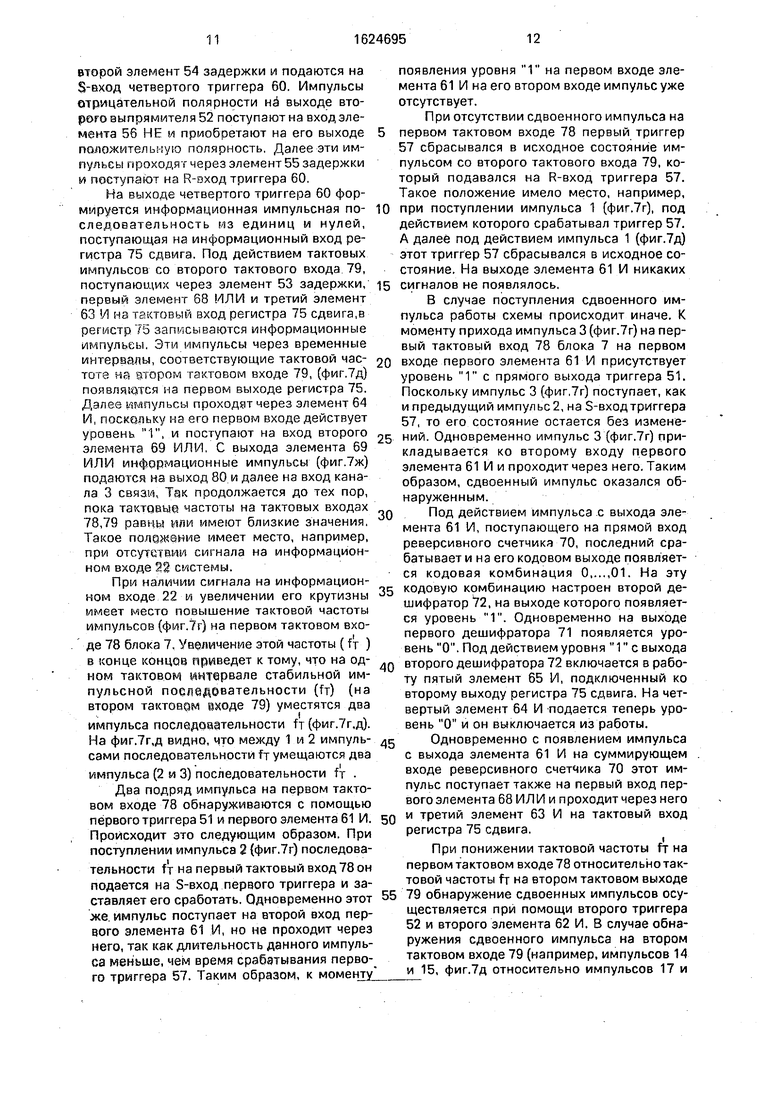

Блок 11 (19) управления шагом квантования содержит (фиг.2) дифференцирующий элемент 26, выпрямитель 27, центрирующий фильтр 28, функциональный преобразователь 29, сумматор 30, источник 31 опорных напряжений и компаратор 32. На фиг.2 обозначены вход 33 и первый - третий выходы 34-36.

Блок 12 (20) управления частотой дискретизации содержит (фиг.З) первый фун- кциональный преобразователь 37, сумматор 38, выпрямитель 39, компаратор 40, источник 41 опорного напряжения, ключевой элемент 42, регулируемый аттенюатор 43, второй функциональный преобразователь 44, ФНЧ 45 и фазовый дискриминатор 46. На фиг.З обозначены первый и второй информационные входы 47,48, тактовый вход 49 и выход 50.

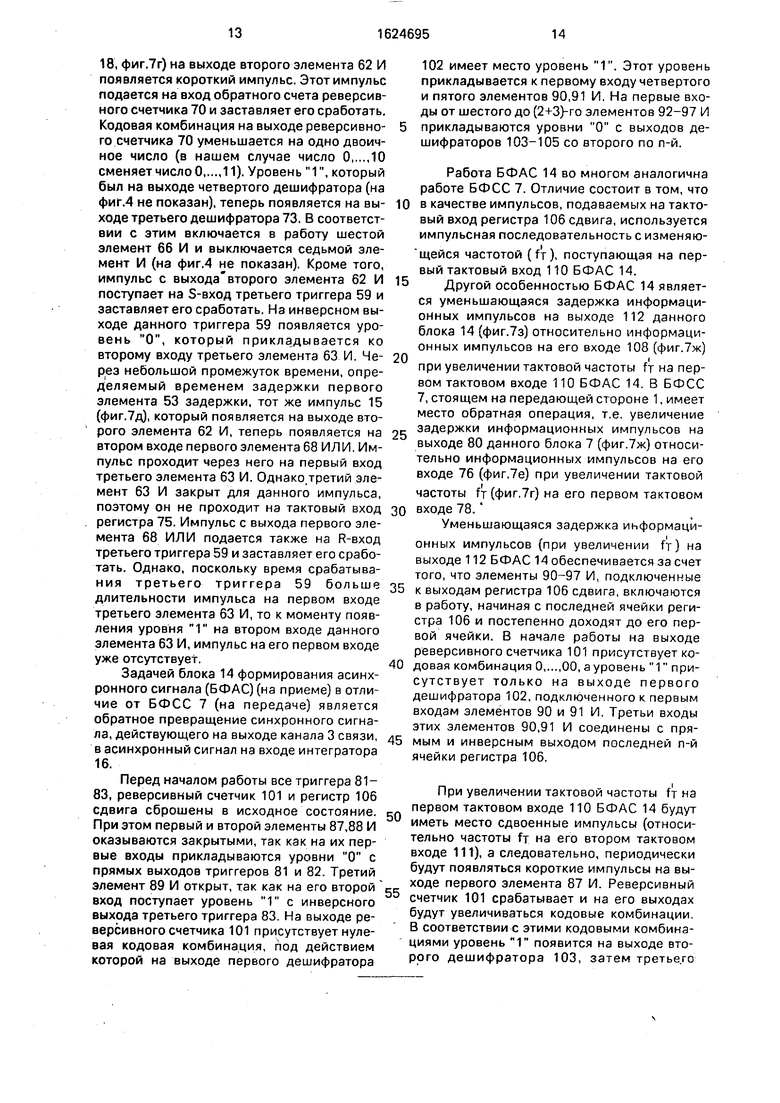

Блок 7 формирования синхронного сигнала содержит (фиг.4) первый и второй выпрямители 51,52, первый - третий элементы 53-55 задержки, элемент 56 НЕ, первый четвертый триггеры 57-60, первый - (п+3)-й элементы 61-67 И, первый и второй элементы 68,69 ИЛИ, реверсивный счетчик 70 (с коэффициентом пересчета п), первый - п-й дешифраторы 71-74 и регистр 75 сдвига. На

0 фиг.4 обозначены информационный вход 76, установочный вход 77, первый и второй тактовые входы 78,79 и выход 80.

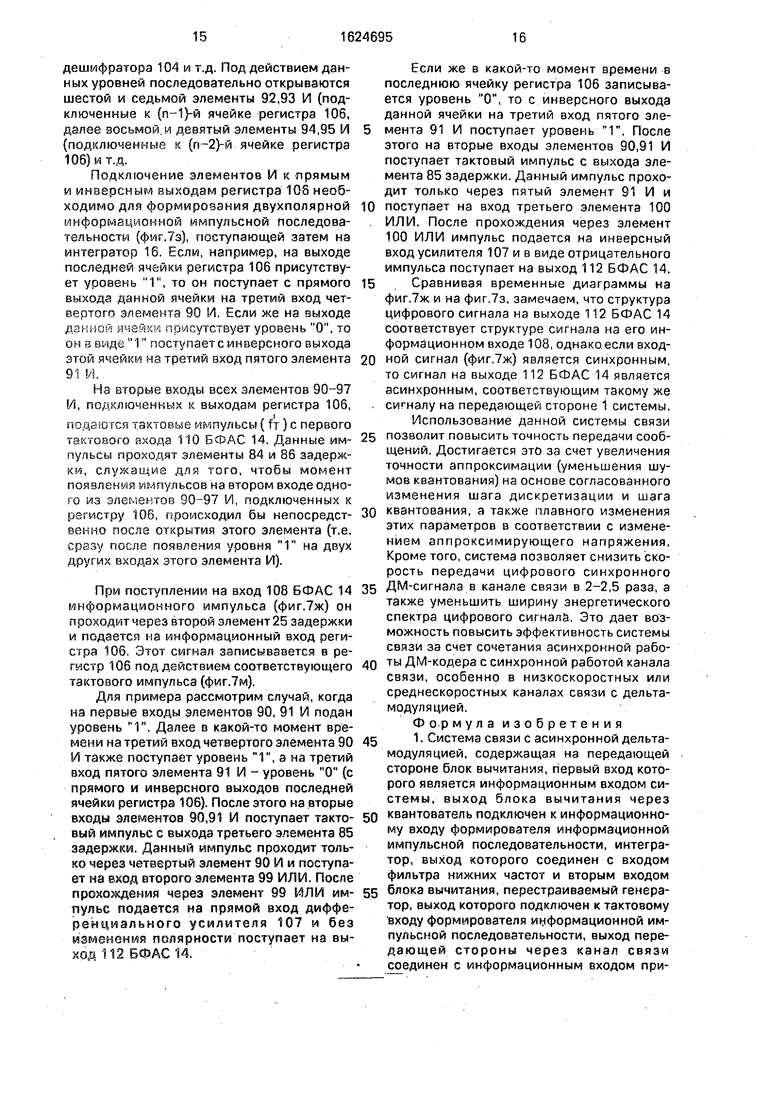

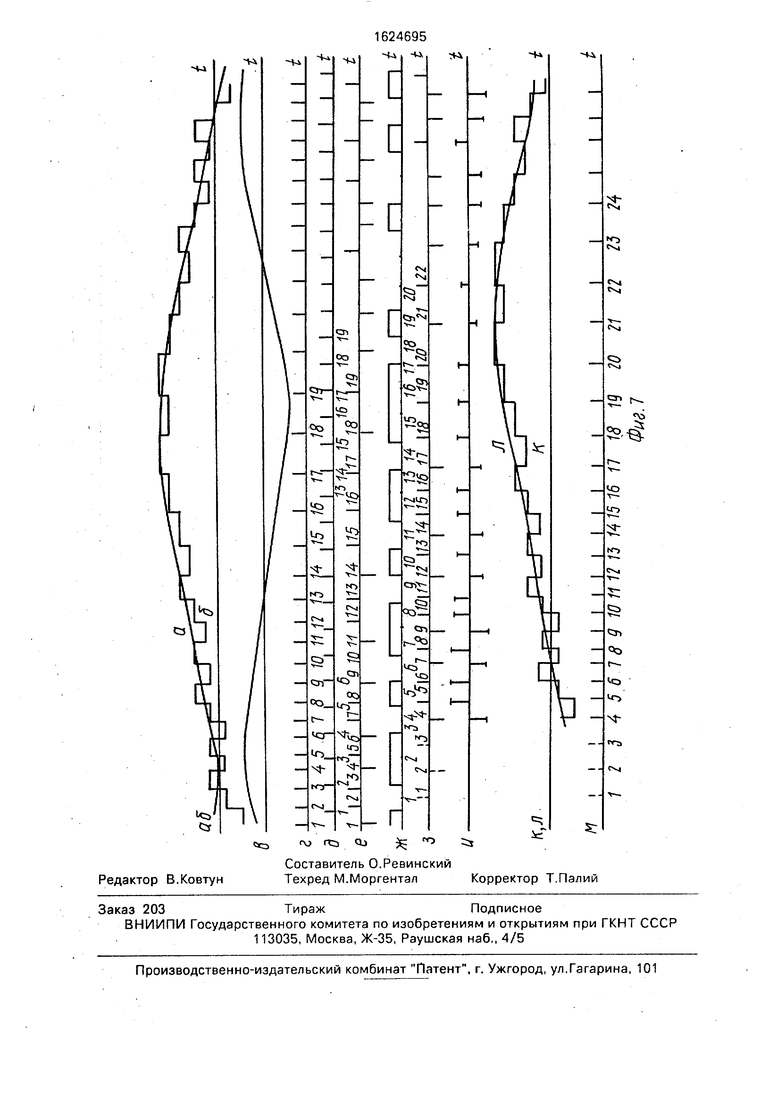

Блок 14 формирования асинхронного сигнала содержит (фиг.5) первый - третий

5 триггеры 81-83, первый - третий элементы 84-86задержки, первый-(2п+3)-йэлементы 87-97 И, первый - третий элементы 98-100 ИЛИ, реверсивный счетчик 101 (с коэффициентом пересчета п), первый - п-й

0 дешифраторы 102-1С5, регистр 106 сдвига и дифференциальный усилитель 107. На фиг.5 обозначены информационный вход 108, установочный вход 109, первый и второй тактовые входы 110,111 и выход 112.

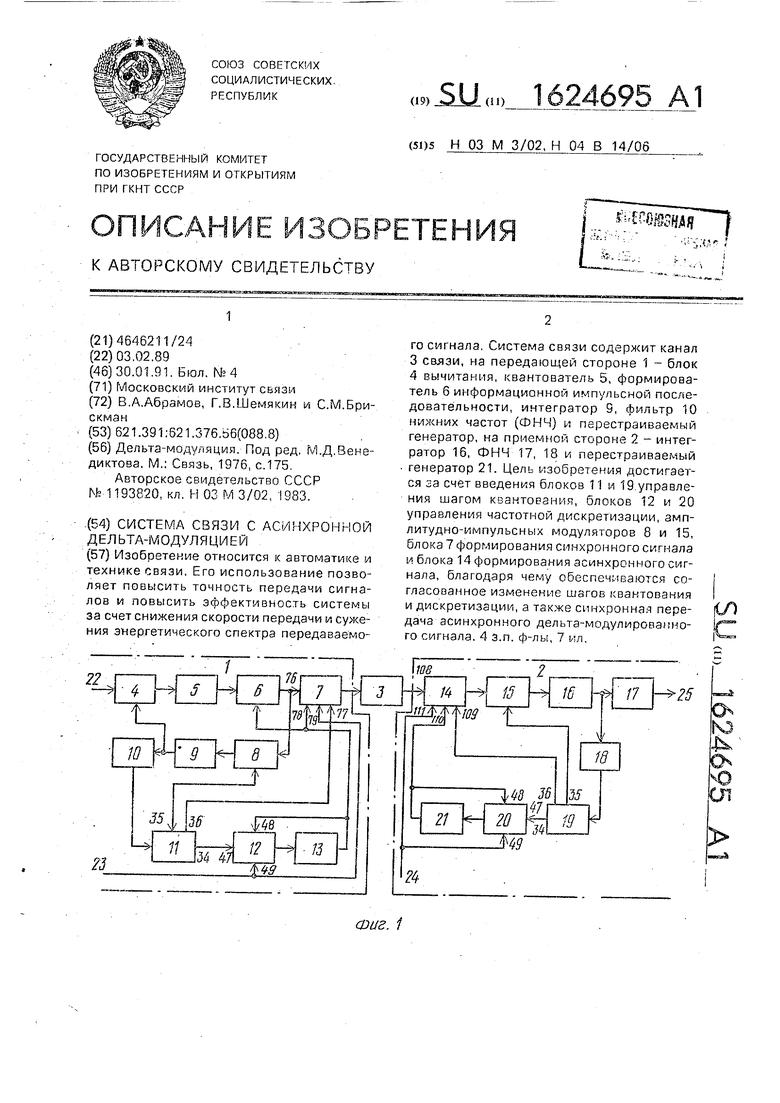

5Формирователь 6 информационной импульсной последовательности может быть выполнен (фиг.6) на первом и втором элементах 113,114 И, элементе 115 НЕ и дифференциальном усилителе 116. На фиг.6

0 обозначены информационный и тактовый входы 117,118 и выход 119.

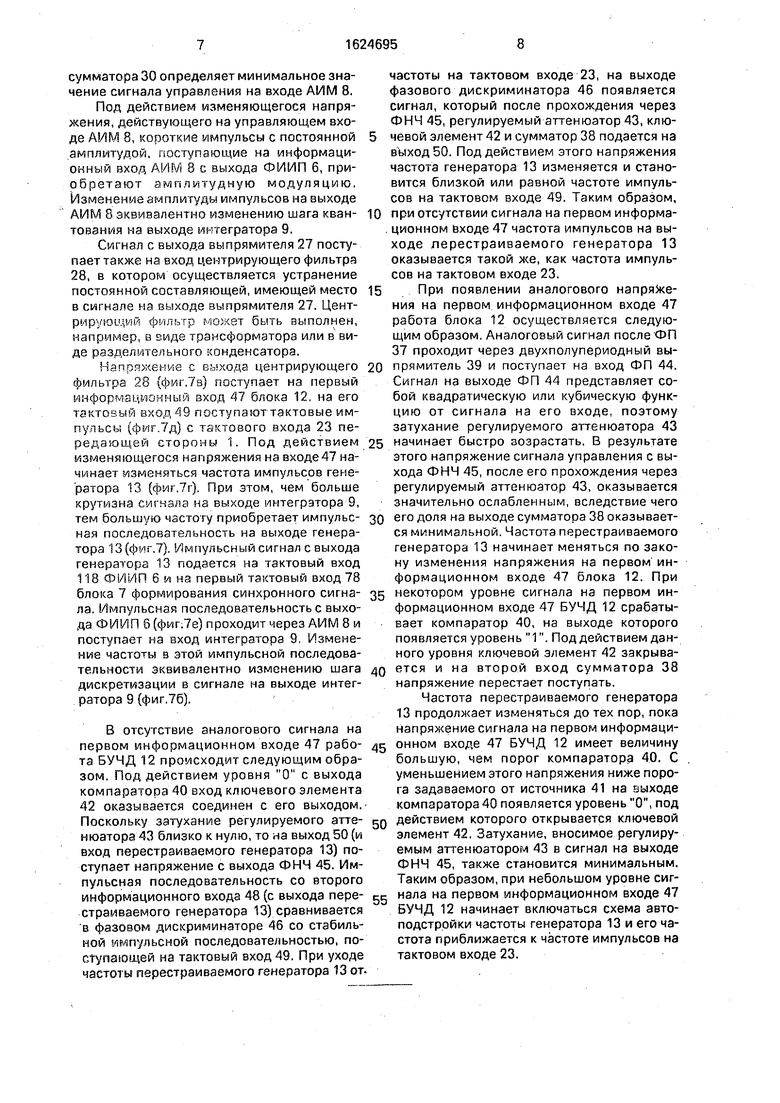

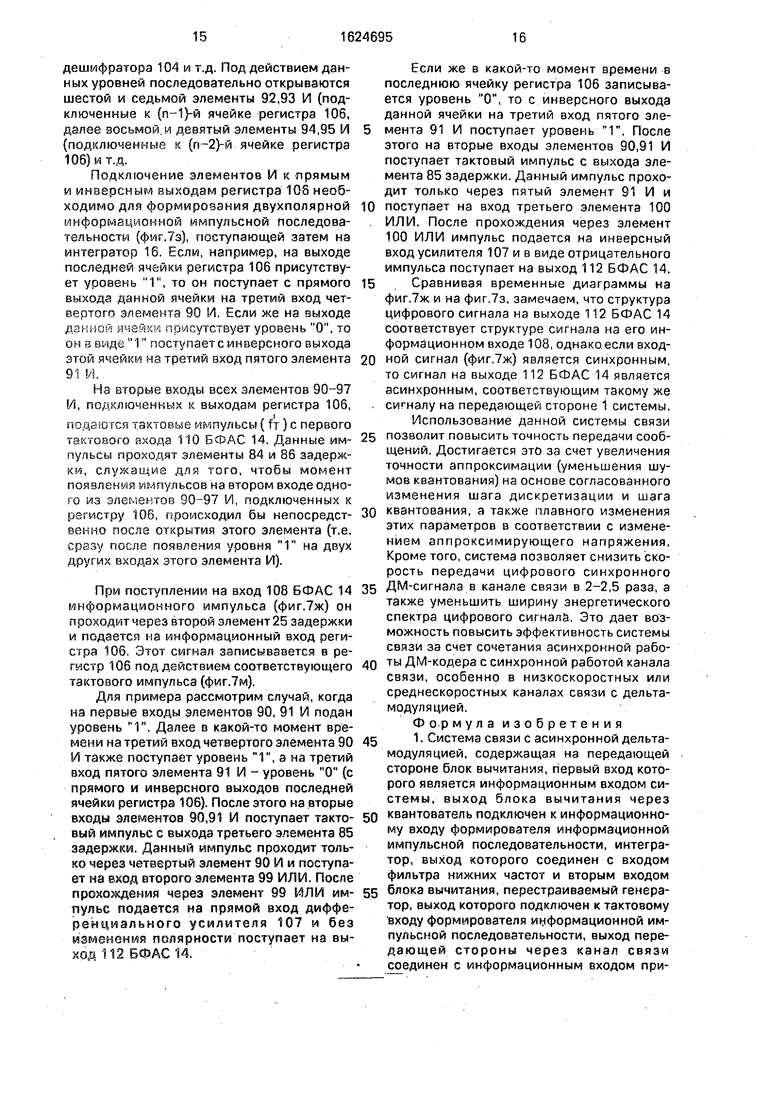

На фиг.7 обозначены следующие сигналы: а,б - входной и аппроксимирующий сигналы на входах блока 4 вычитания; в 5 сигнал на выходе центрирующего фильтра 28 (на первом выходе 34 БУШК 11); г - импульсы на выходе перестраиваемого генератора 13;. д - тактовые импульсы на входе 23; е - импульсная последовательность с

Q выхода ФИИП 6; ж-синхронный ДМ-сигнал на выходе БФСС 7; з - асинхронный ДМ- сигнал на выходе БФАС 14; и - сигнал на выходе АИМ 15; к,л - сигналы на входе и выходе ФНЧ 16; м - импульсы на выходе

5 перестраиваемого генератора 21.

Система связи работает следующим образом.

На информационный вход 22 системы подается аналоговый сигнал (фиг,7а). Этот

0 сигнал поступает на первый вход блока 4 вычитания, на второй вход которого подается аппроксимирующее напряжение (фиг.7б) с выхода интегратора 9. Сигнал разности поступает затем на вход квантователя 5 по

5 уровням, в котором принимается решение о знаке сигнала. На выходе квантователя 5 формируется последовательность прямоугольных импульсов, где уровням логической единицы соответствуют интервалы времени, в течение которых входной сигнал

превышает аппроксимирующее напряжение, а уровням логического нуля соответствуют интервалы времени, в течение которых входной сигнал меньше аппроксимирующего напряжения. С выхода квантователя 5 сигнал подается на ФИИП 6, где осуществляется привязка его к тактовым импульсам, поступающим с генератора 13. Сигнал на выходе ФИИП 6 представляет собой последовательность положительных и отрицательных импульсов ±1 (фиг.Те). Положительной полярности сигнала разности соответствуют символы. +1 в информационной последовательности на выходе ФИИП 6 и увеличение аппроксимирующего напряжения на выходе интегратора 9, а отрицательной полярности сигнала разности - символы -1 в информационной последовательности и уменьшение аппроксимирующего напряжения на выходе интегратора 9.

В результате интегрирования этих импульсов в интеграторе 9 формируется аппроксимирующее напряжение, состоящее из ступенек величиной ± Е и длительностью Т, (при отсутствии адаптации) поступающее на второй вход блока вычитания 4.

При испдльзовании командирования приращений аппроксимирующего напряжения происходит расширение динамического диапазона передаваемых сигналов. Однако, увеличение приращения напряжения шага квантования Б приводит к возрастанию мощности шума квантования, что видно из формулы

Р -А М Ј гкв - Акв1 /

где Акв - коэффициент пропорциональности;

Af - ширина полосы частот аналогового сигнала;

fr тактовая частота.

Для поддержания приемлемых значений мощности шума квантования или отношения сигнал/шум квантования необходимо, чтобы при изменении шага квантования Ј происходило бы одновременное изменение шага дискретизации, т.е. тактовой частоты дельтакодера тт. При этом важное значение имеет согласованность изменений шага дискретизации и шага квантования. В зависимости от требований к изменению РКв должна меняться также динамика отношения eVfT , в частности это отношение может быть постоянным при непрерывно меняющихся Б и ft. Согласованность изменения Е и тт позволяет осуществлять как постоянство мощности шума квантования Ркв, так и ее непрерывное изменение в соответствии с изменением напряжения аналогового сигнала. Это позволяет в частности поддерживать постоянным отношение сигнал/шум квантования. 5Рассмотрим каким образом в системе

. осуществляется формирование переменного шага квантования Ј и переменного шага дискретизации Т. В качестве управляющего сигнала для блоков 11 и 12, осуществляю- 0 щих формирование соответственно переменного шага квантования и переменной частоты дискретизации, используется ап- -проксимирующее напряжение с выхода интегратора 9 (фиг.7б), Данное напряжение 5 проходит через ФНЧ 10, где из этого напряжения отфильтровываются высокочастотные составляющие, обусловленные шагами аппроксимации, и поступает в БУШК 11 на вход дифференцирующего элемента 26, 0 Сигнал на выходе дифференцирующего элемента 26 представляет собой первую производную от аппроксимирующего напряжения. Это напряжение подается далее на вход выпрямителя 27, представляющего 5 собой двухполупериодную схему выпрямления (без фильтра). Максимальным значением напряжения с выхода выпрямителя 27 соответствует максимальная крутизна аппроксимирующего напряжения (на выходе 0 интегратора 9). Сигнал с выхода выпрямителя 27 является управляющим для формирования переменного шага квантования, а также переменного шага дискретизации в БУЧД 12. Переменный шаг квантования 5 формируется при помощи АИМ 8. Сигнал с выхода выпрямителя 27 поступает на вход функционального преобразователя ФП 29 и на вход центрирующего фильтра 28. Функциональный преобразователь 29 в БУШК 11 0 и первый функциональный преобразователь 37 в БУЧД 12 осуществляют согласование изменений шага квантования и шага дискретизации. Например, если необходимо получить постоянство шума квантова- 5 ния, то ФП 37 должен иметь линейную зависимость между сигналами на его входе и выходе, а ФП 29 должен иметь квадратичную зависимость, либо наоборот ФП 37 должен иметь логарифмическую характери- Q стику, а ФП 29 должен иметь линейную характеристику, В зависимости от того, по каким законам должен изменяться шаг квантования и шаг дискретизации, функциональные преобразователи 29, 37 могут g иметь различные характеристики.

Сигнал с выхода ФП 29 поступает на первый вход сумматора 30, на второй вход которого подается постоянное напряжение со второго выхода источника 31 опорных напряжений. Напряжение на втором входе

сумматора 30 определяет минимальное значение сигнала управления на входе АИМ 8.

Под действием изменяющегося напряжения, действующего на управляющем входе АИМ 8, короткие импульсы с постоянной амплитудой, поступающие на информационный вход АИМ 8 с выхода ФИИП 6, приобретают амплитудную модуляцию. Изменение амплитуды импульсов на выходе АИМ 8 эквивалентно изменению шага квантования на выходе интегратора 9.

Сигнал с выхода выпрямителя 27 поступает также на вход центрирующего фильтрч 28, в котором осуществляется устранение постоянной составляющей, имеющей место в сигнале на выходе выпрямителя 27. Центрирующей ф ЛЛЬгр МОХ8Т бЫТЬ ВЫПОЛНвН,

например, в зиде трансформатора или в виде разделительного конденсатора.

Напряжение с выхода центрирующего фильтра 28 (фиг.7в) поступает на первый информационный вход 47 блока 12, на его тактовый вход 49 поступают тактовые им- пупьсы (фиг.7д) с тактового входа 23 передающей стороны 1. Под действием изменяющегося напряжения на входе47 начинает изменяться частота импульсов генератора 13 (фиг.7г). При этом, чем больше крутизна сигнала на выходе интегратора 9, тем большую частоту приобретает импульсная последовательность на выходе генератора 13 (ф /г.7). Импульсный сигнал с выхода генератора 13 подается на тактовый вход 118 ФИИП 6 и на первый тактовый вход 78 блока 7 формирования синхронного сигнала. Импульсная последовательность с выхода ФИИП б (фиг.7е) проходит через АИМ 8 и поступает на вход интегратора 9. Изменение частоты в этой импульсной последовательности эквивалентно изменению шага дискретизации в сигнале на выходе интегратора 9 (фиг.76).

В отсутствие аналогового сигнала на первом информационном входе 47 работа БУНД 12 происходит следующим образом. Под действием уровня О с выхода компаратора 40 оход ключевого элемента 42 оказывается соединен с его выходом. Поскольку затухание регулируемого аттенюатора 43 близко к нулю, то на выход 50 (и вход перестраиваемого генератора 13) поступает напряжение с выхода ФНЧ 45. Импульсная последовательность со второго информационного входа 48 (с выхода перестраиваемого генератора 13) сравнивается в фазовом дискриминаторе 46 со стабильной импульсной последовательностью, поступающей на тактовый вход 49. При уходе частоты перестраиваемого генератора 13 от.

частоты на тактовом входе 23, на выходе фазового дискриминатора 46 появляется сигнал, который после прохождения через ФНЧ 45, регулируемый аттенюатор 43, ключевой элемент 42 и сумматор 38 подается на выход 50. Под действием этого напряжения частота генератора 13 изменяется и становится близкой или равной частоте импульсов на тактовом входе 49. Таким образом,

при отсутствии сигнала на первом информационном входе 47 частота импульсов на выходе перестраиваемого генератора 13 оказывается такой же, как частота импульсов на тактовом входе 23.

При появлении аналогового напряжения на первом информационном входе 47 работа блока 12 осуществляется следующим образом. Аналоговый сигнал после ФП 37 проходит через двухполупериодный выпрямитель 39 и поступает на вход ФП 44. Сигнал на выходе ФП 44 представляет собой квадратическую или кубическую функцию от сигнала на его входе, поэтому затухание регулируемого аттенюатора 43

начинает быстро возрастать, В результате этого напряжение сигнала управления с выхода ФНЧ 45, после его прохождения через регулируемый аттенюатор 43, оказывается значительно ослабленным, вследствие чего

его доля на выходе сумматора 38 оказывается минимальной. Частота перестраиваемого генератора 13 начинает меняться по закону изменения напряжения на первом информационном входе 47 блока 12. При

некотором уровне сигнала на первом информационном входе 47 БУЧД 12 срабатывает компаратор 40, на выходе которого появляется уровень 1. Под действием данного уровня ключевой элемент 42 закрывается и на второй вход сумматора 38 напряжение перестает поступать.

Частота перестраиваемого генератора 13 продолжает изменяться до тех пор, пока напряжение сигнала на первом информационном входе 47 БУЧД 12 имеет величину большую, чем порог компаратора 40. С уменьшением этого напряжения ниже порога задаваемого от источника 41 на выходе компаратора 40 появляется уровень О, под

действием которого открывается ключевой элемент 42, Затухание, вносимое регулируемым аттенюатором 43 в сигнал на выходе ФНЧ 45, также становится минимальным. Таким образом, при небольшом уровне сигс нала на первом информационном входе 47 БУЧД 12 начинает включаться схема автоподстройки частоты генератора 13 и его частота приближается к частоте импульсов на тактовом входе 23.

Поскольку импульсная последовательность на выходе ФИИП 6 непрерывно изменяется по частоте, то ее уже нельзя характеризовать как синхронный ДМ-сиг- нал, а система связи с таким сигналом уже не является синхронной. Для преобразования асинхронного сигнала с выхода ФИИП 6 в синхронный, т.е. для согласования асинхронного ДМ-кодера с синхронным каналом 3 связи служит блок 7 формирования синхронного сигнала.

Функционирование БФСС 7 основано на изменении времени задержки ДМ-еигна- ла в соответствии с изменением частоты сигнала на информационном входе 76 данного блока 7. На увеличение частоты импульсной последовательности на выходе ФИИП 6 БФСС 7 отвечает увеличением времени задержки и наоборот. На приемной стороне 2 блок 14 формирования асинхронного сигнала работает несколько иначе, т.е. с увеличением частоты импульсной последовательности на его первом тактовом входе 110 происходит уменьшение времени задержки и наоборот. Вследствие того, что при увеличении времени задержки ДМ-сиг- нала на передаче происходит уменьшение времени задержки на приеме точно на такую же величину, то суммарное время задержки сигнала оказывается в любой момент времени постоянным.

Импульсная последовательность, флуктуирующая по частоте, с выхода ФИИП 6 (фиг.7е) поступает в БФСС 7, а затем считывается с помощью высокостабильного тактового колебания, поступающего на второй тактовый вход 79 блока 7 (фиг.7д). Таким образом, синхронный ДМ-сигнал, сформированный на выходе БФСС 7 (фиг.7ж), поступает в канал 3 связи.

С целью автоматической установки БФСС 7 в нужный режим работы при включении системы или при сбоях служит компаратор 32 в блоке 11. Сигнал на информационный вход компаратора 32 поступает с выхода центрирующего фильтра 28 (фиг.7в). При переходе данного сигнала через ноль (из отрицательной области в положительную) на выходе компаратора 32 появляется короткий импульс, который подается на установочный вход 77 БФСС 7. Компаратор 32 может либо непосредственно вырабатывать короткий импульс при переходе через 0 сигнала на его информационном входе,либо включать в свой состав формирователь коротких импульсов.

Работа приемной стороны 2 системы происходит следующим образом. Цифровой ДМ-сигнал с выхода канала 3 связи (фиг.7ж) поступает на информационный вход 108

БФАС 14, который выполняет задачу, противоположную той, что выполняет БФСС 7 на передающей стороне 1: необходимо синхронный ДМ-сигнал, поступающий из канала 5 3 связи, снова преобразовать в асинхронный по такому же закону, как это имело место на передающей стороне 1.

Цифровой ДМ-сигнал с выхода канала 3 связи поступает в БФАС 14 и считывается с 10 помощью флуктирующей по частоте импульсной последовательности, поступающей с выхода генератора 21 (фиг,7м). Далее асин- хронный ДМ-сигнал (фиг.7з) проходит через АИМ 15, где подвергается амплитудной мо- 5 дуляции (фиг.7и) и поступает на вход интегратора 16. Изменение частоты и амплитуды импульсной последовательности на входе интегратора 16 эквивалентно изменению шага дискретизации и шага квантования в 0 сигнале на выходе интегратора 16. Сигнал с выхода интегратора 16 (фиг.7к) после прохождения через первый ФНЧ 17 поступает на выход 25 системы (фиг.7л).

Формирование управляющих сигналов 5 Для работы АИМ 15 и генератора 21 осуществляется, как и на передающей стороне 1 при помощи БУШК 19 и БУНД 20, работа которых ничем не отличается от работы подобных же блоков 11,12 на передающей 0 стороне V системы. Установка БФАС 14,в исходное состояние осуществляется, как и на передающей стороне 1, при помощи компаратора 32 БУШК 19.

Работа БФСС 7 происходит следующим 5 образом.

Перед началом работы все триггеры 57- 60, реверсивный счетчик 70 и регистр 75 сдвига сброшены в исходное состояние. При этом первый и второй элементы 61,62 И Q оказываются закрытыми, так как на их первые входы прикладываются уровни О с пряг-.ых выходов триггеров 57,58. На выходе реверсивного счетчика 70 присутствует нулевая кодовая комбинация, под действием 5 которой на выходе первого дешифратора 71 имеет место уровень 1. Этот уровень прикладывается к первому входу четвертого элемента 64 И. На первые входы от пятого до (п+3)-го элементов 65-67 И прикладыва- Q ются уровни О с выходов дешифраторов 72-74 со второго по п-й.

При появлении импульсов на тактовых входах 78,79 и на информационном входе 76 работа БФСС осуществляется следующим 5 образом. Импульсы положительной и отрицательной полярности, поступающие на информационный вход 76 блока 7, проходят далее на первый и второй выпрямители 51,52. Положительные импульсы на выходе первого выпрямителя 51 проходят через

второй элемент 54 задержки и подаются на S-вход четвертого триггера 60. Импульсы отрицательной полярности ни выходе второго выпрямителя 52 поступают на вход элемента 56 НЕ и приобретают на его выходе положительную полярность, Далее эти импульсы проходят через элемент 55 задержки и поступают на R-вход триггера 60.

На выходе четвертого триггера 60 формируется информационная импульсная последовательность из единиц м нулей, поступающая на информационный вход регистра 75 сдвига. Под действием тактовых импульсов со второго тактового входа 79, поступающих через элемент 53 задержки, первый элемент 68 ИЛИ и третий элемент 63 1/1 на тактовый вход регистра 75 сдвига,в регистр 75 записываются информационные импульсы. Эти импульсы через временные интервалы, соответствующие тактовой частоте на втором тактовом входе 79, (фиг.7д) появля отся на первом выходе регистра 75. Далее импульсы проходят через элемент 64 И, поскольку на его первом входе действует уровень 1, и поступают на вход второго элемента 69 ИЛИ, С выхода элемента 69 ИЛИ информационные импульсы (фиг.7ж) подаются на выход 80 и далее на вход канала 3 связи, Так продолжается до тех пор, пока тактовые частоты на тактовых входах 78,79 равны или имеют близкие значения, Такое положение имеет место, например, при отсутствии сигнала на информационном входе 22 системы.

При наличии сигнала на информационном входе 22 и увеличении его крутизны имеет место повышение тактовой частоты импульсов (фиг.7г) на первом тактовом входе 78 блока 7. Увеличение этой частоты (fy ) в онце концов приведет к тому, что на одном тактовой интервале стабильной импульсной последовательности (fr) (на втором тактовом входе 79) уместятся два

импульса последовательности fr (фиг.7г,д). На фиг.7г,д видно, что между 1 и 2 импульсами последовательности тт умещаются два

импульса (2 и 3) последовательности fV .

Два подряд импульса на первом тактовом входе 78 обнаруживаются с помощью первого триггера 51 и первого элемента 61 И. Происходит это следующим образом. При поступлении импульса 2 (фиг.7г) последовательности fr на первый тактовый вход 78 он подается на S-вход первого триггера и заставляет его сработать. Одновременно этот же. импульс поступает на второй вход первого элемента 61 И, но не проходит через него, так как длительность данного импульса меньше, чем время срабатывания первого триггера 57. Таким образом, к моменту

появления уровня 1 на первом входе элемента 61 И на его втором входе импульс уже отсутствует.

При отсутствии сдвоенного импульса на

первом тактовом входе 78 первый триггер 57 сбрасывался в исходное состояние импульсом со второго тактового входа 79, который подавался на R-вход триггера 57. Такое положение имело место, например,

0 при поступлении импульса 1 (фиг.7г), под действием которого срабатывал триггер 57. А далее под действием импульса 1 (фиг.7д) этот триггер 57 сбрасывался в исходное состояние. На выходе элемента 61 И никаких

5 сигналов не появлялось.

В случае поступления сдвоенного импульса работы схемы происходит иначе. К моменту прихода импульса 3 (фиг.7г) на первый тактовый вход 78 блока 7 на первом

0 входе первого элемента 61 И присутствует уровень 1 с прямого выхода триггера 51. Поскольку импульс 3 (фиг,7г) поступает, как и предыдущий импульс 2, на S-вход триггера 57, то его состояние остается без измене5 ний. Одновременно импульс 3 (фиг.7г) прикладывается ко второму входу первого элемента 61 И и проходит через него. Таким образом, сдвоенный импульс оказался обнаруженным.

0 Под действием импульса с выхода элемента 61 И, поступающего на прямой вход реверсивного счетчика 70, последний срабатывает и на его кодовом выходе появляется кодовая комбинация 0,...,01. На эту

5 кодовую комбинацию настроен второй дешифратор 72, на выходе которого появляется уровень 1. Одновременно на выходе первого дешифратора 71 появляется уровень О. Под действием уровня 1 с выхода

0 второго дешифратора 72 включается в работу пятый элемент 65 И, подключенный ко второму выходу регистра 75 сдвига. На четвертый элемент 64 И подается теперь уровень О и он выключается из работы.

5 Одновременно с появлением импульса с выхода элемента 61 И на суммирующем входе реверсивного счетчика 70 этот импульс поступает также на первый вход первого элемента 68 ИЛ И и проходит через него

Q и третий элемент 63 И на тактовый вход регистра 75 сдвига.

При понижении тактовой частоты fr на первом тактовом входе 78 относительно тактовой частоты fr на втором тактовом выходе 5 79 обнаружение сдвоенных импульсов осуществляется при помощи второго триггера 52 и второго элемента 62 И. В случае обнаружения сдвоенного импульса на втором тактовом входе 79 (например, импульсов 14 и 15, фиг.7д относительно импульсов 17 и

18, фиг.Тг) на выходе второго элемента 62 И появляется короткий импульс. Этот импульс подается на вход обратного счета реверсивного счетчика 70 и заставляет его сработать. Кодовая комбинация на выходе реверсивно- го счетчика 70 уменьшается на одно двоичное число (в нашем случае число 010

сменяетчислоО11). Уровень 1, который

был на выходе четвертого дешифратора (на фиг.4 не показан), теперь появляется на вы- ходе третьего дешифратора 73. В соответствии с этим включается в работу шестой элемент 66 И и выключается седьмой элемент И (на фиг.4 не показан). Кроме того, импульс с вы ход а второго элемента 62 И поступает на S-вход третьего триггера 59 и заставляет его сработать. На инверсном выходе данного триггера 59 появляется уровень О, который прикладывается ко второму входу третьего элемента 63 И. Че- рез небольшой промежуток времени, определяемый временем задержки первого элемента 53 задержки, тот же импульс 15 (фиг.7д), который появляется на выходе второго элемента 62 И, теперь появляется на втором входе первого элемента 68 ИЛИ. Импульс проходит через него на первый вход третьего элемента 63 И. Однакодретий элемент 63 И закрыт для данного импульса, поэтому он не проходит на тактовый вход регистра 75. Импульс с выхода первого элемента 68 ИЛИ подается также на R-вход третьего триггера 59 и заставляет его сработать. Однако, поскольку время срабатывания третьего триггера 59 больше длительности импульса на первом входе третьего элемента 63 И, то к моменту появления уровня 1 на втором входе данного элемента 63 И, импульс на его первом входе уже отсутствует.

Задачей блока 14 формирования асинхронного сигнала (БФАС) (на приеме) в отличие от БФСС 7 (на передаче) является обратное превращение синхронного сигнала, действующего на выходе канала 3 связи, в асинхронный сигнал на входе интегратора 16.

Перед началом работы все триггера 81- 83, реверсивный счетчик 101 и регистр 106 сдвига сброшены в исходное состояние. При этом первый и второй элементы 87,88 И оказываются закрытыми, так как на их первые входы прикладываются уровни О с прямых выходов триггеров 81 и 82. Третий элемент 89 И открыт, так как на его второй вход поступает уровень 1 с инверсного выхода третьего триггера 83. На выходе реверсивного счетчика 101 присутствует нулевая кодовая комбинация, под действием которой на выходе первого дешифратора

102 имеет место уровень 1. Этот уровень прикладывается к первому входу четвертого и пятого элементов 90,91 И. На первые входы от шестого до (2+3)-го элементов 92-97 И прикладываются уровни О с выходов дешифраторов 103-105 со второго по п-й.

Работа БФАС 14 во многом аналогична работе БФСС 7. Отличие состоит в том, что в качестве импульсов, подаваемых на тактовый вход регистра 106 сдвига, используется импульсная последовательность с изменяю щейся частотой (fr), поступающая на первый тактовый вход 110 БФАС 14.

Другой особенностью БФАС 14 является уменьшающаяся задержка информационных импульсов на выходе 112 данного блока 14 (фиг.7з) относительно информационных импульсов на его входе 108 (фиг.7ж)

при увеличении тактовой частоты fy на первом тактовом входе 110 БФАС 14. В БФСС 7, стоящем на передающей стороне 1, имеет место обратная операция, т.е. увеличение задержки информационных импульсов на выходе 80 данного блока 7 (фиг.7ж) относительно информационных импульсов на его входе 76 (фиг.7е) при увеличении тактовой

частоты тт(фиг.7г) на его первом тактовом входе 78.

Уменьшающаяся задержка информационных импульсов (при увеличении fr) на выходе 112 БФАС 14 обеспечивается за счет того, что элементы 90-97 И, подключенные к выходам регистра 106 сдвига, включаются в работу, начиная с последней ячейки регистра 106 и постепенно доходят до его первой ячейки. В начале работы на выходе реверсивного счетчика 101 присутствует кодовая комбинация 000, а уровень 1 присутствует только на выходе первого дешифратора 102, подключенного к первым входам элементов 90 и 91 И. Третьи входы этих элементов 90,91 И соединены с прямым и инверсным выходом последней п-й ячейки регистра 106.

При увеличении тактовой частоты тт на первом тактовом входе 110 БФАС 14 будут иметь место сдвоенные импульсы (относительно частоты fr на его втором тактовом входе 111), а следовательно, периодически будут появляться короткие импульсы на выходе первого элемента 87 И. Реверсивный счетчик 101 срабатывает и на его выходах будут увеличиваться кодовые комбинации. В соответствии с этими кодовыми комбинациями уровень 1 появится на выходе второго дешифратора 103, затем третьего

дешифратора 104 и т.д. Под действием данных уровней последовательно открываются шестой и седьмой элементы 92,93 И (подключенные к (п-1}-й ячейке регистра 106, далее восьмой и девятый элементы 94,95 И (подключенные к (п-2)-й ячейке регистра 106) и т.д.

Подключение элементов И к прямым и инверсным выходам регистра 106 необходимо для формирования двухполярной информационной импульсной последовательности (фиг.Тз), поступающей затем на интегратор 16. Если, например, на выходе последней ячейки регистра 106 присутствует уровень , то он поступает с прямого выхода данной ячейки на третий вход четвертого элемента 90 И, Если же на выходе дакло1 ячеЧк : присутствует уровень О, то он з виде 1 поступает с инверсного выхода этой ячейки на третий вход пятого элемента 91 И.

На вторые входы всех элементов 90-97 И, подключенных к выходам регистра 106,

подаются тактовые импульсы (тт)с первого тактового входа 110 БФАС 14. Данные импульсы проходят элементы 84 и 86 задержки, служащие для того, чтобы момент появления импульсов на втором входе одного из элементов 90-97 И, подключенных к регистру 106, происходил бы непосредственно после открытия этого элемента (т.е. сразу после появления уровня 1 на двух других входах этого элемента И).

При поступлении на вход 108 БФАС 14 информационного импульса (фиг.7ж) он проходит через второй элемент 25 задержки и подается на информационный вход регистра 106. Этот сигнал записывавется в регистр 106 под действием соответствующего тактового импульса (фмг.7м).

Для примера рассмотрим случай, когда на первые входы элементов 90, 91 И подан уровень 1. Далее в какой-то момент времени на третий вход четвертого элемента 90 И также поступает уровень 1, а на третий вход пятого элемента 91 И - уровень О (с прямого и инверсного выходов последней ячейки регистра 106). После этого на вторые входы элементов 90,91 И поступает тактовый импульс с выхода третьего элемента 85 задержки. Данный импульс проходит только через четвертый элемент 90 И и поступает на вход второго элемента 99 ИЛИ. После прохождения через элемент 99 ИЛИ импульс подается на прямой вход дифференциального усилителя 107 и без изменения полярности поступает на выход 112 БФАС 14.

Бели же в какой-то момент времени в последнюю ячейку регистра 106 записывается уровень О, то с инверсного выхода данной ячейки на третий вход пятого элемента 91 И поступает уровень Г. После этого на вторые входы элементов 90,91 И поступает тактовый импульс с выхода элемента 85 задержки. Данный импульс проходит только через пятый элемент 91 И и

0 поступает на вход третьего элемента 100 ИЛИ. После прохождения через элемент 100 ИЛИ импульс подается на инверсный вход усилителя 107 и в виде отрицательного импульса поступает на выход 112 БФАС 14.

5 Сравнивая временные диаграммы на фиг,7ж и на фиг.7з, замечаем, что структура цифрового сигнала на выходе 112 БФАС 14 соответствует структуре сигнала на его информационном входе 108,однако если вход0 ной сигнал (фиг.7ж) является синхронным,

то сигнал на выходе 112 БФАС 14 является

асинхронным, соответствующим такому же

сигналу на передающей стороне 1 системы.

Использование данной системы связи

5 позволит повысить точность передачи сообщений. Достигается это за счет увеличения точности аппроксимации (уменьшения шумов квантования) на основе согласованного изменения шага дискретизации и шага

0 квантования, а также плавного изменения этих параметров в соответствии с изменением аппроксимирующего напряжения, Кроме того, система позволяет снизить скорость передачи цифрового синхронного

5 ДМ-сигнала в канале связи в 2-2,5 раза, а также уменьшить ширину энергетического спектра цифрового сигнала, Это дает возможность повысить эффективность системы связи за счет сочетания асинхронной рабо0 ты ДМ-кодера с синхронной работой канала связи, особенно в низкоскоростных или среднескоростных каналах связи с дельта- модуляцией.

Формула изобретения

51 Система связи с асинхронной дельтамодуляцией, содержащая на передающей стороне блок вычитания, первый вход которого является информационным входом системы, выход блока вычитания через

0 квантователь подключен к информационному входу формирователя информационной импульсной последовательности, интегратор, выход которого соединен с входом фильтра нижних частот и вторым входом

5 блока вычитания, перестраиваемый генератор, выход которого подключен к тактовому входу формирователя информационной импульсной последовательности, выход передающей стороны через канал связи соединен с информационным входом приемной стороны, содержащей перестраиваемый генератор, интегратор, выход которого подключен к входам первого и второго фильтров нижних частот, выход первого фильтра нижних частот является выходом системы, отличающаяся тем, что, с целью повышения точности передачи сигналов и повышения эффективности системы за счет снижения скорости передачи и сужения энергетического спектра передаваемо- го сигнала, на передающей стороне в ведены амплитудно-импульсный модулятор, блок управления шагом квантования, блок управления частотой дискретизации и блок формирования синхронного сигнала, выход формирователя информационной импульсной последовательности соединен с информационными входами блока формирования синхронного сигнала и амплитудно-импульсного модулятора, выход которого подключен к входу интегратора, выход фильтра нижних частот соединен с входом блока управления шагом квантования, первый-третий выходы которого подключены соответственно к первому информационному входу блока управления частотой дискретизации, управляющему входу амплитудно-импульсного модулятора и установочному входу блока формирования синхронного сигнала, первый тактовый вход которого объединен с вторым информационным входом блока управления частотой дискретизации и подключен к выходу перестраиваемого генератора, вход которого соединен с выходом блока управления частотой дискретизации, тактовый вход которого объединен с вторым тактовым входом блока формирования синхронного сигнала и является тактовым входом передающей стороны, выход блока формирова- ния синхронного сигнала является выходом передающей стороны, на приемной стороне введены амплитудно-импульсный модулятор, блок управления шагом квантования, блок управления частотой дискретизации и блок формирования асинхронного сигнала, информационный вход которого является информационным входом приемной стороны, выход блока формирования асинхронного сигнала соединен с информационным входом амплитудно- импульсного модулятора, выход которого подключен к входу интегратора, выход второго фильтра нижних частот соединен с входом блока управления шагом квантования, первый-третий выхо- ды которого подключены соответственно к первому информационному входу блока управления частотой дискретизации, управляющему входу амплитудно-импульсного модулятора и установочному входу блока

формирования асинхронного сигнала, выход блока управления частотой дискретизации соединен с входом перестраиваемого генератора, выход которого подключен к первому тактовому входу блока формирования асинхронного сигнала и второму инфор- мационному входу блока управления частотой дискретизации, тактовый вход которого объединен с вторым тактовым входом блока формирования асинхронного сигнала и является тактовым входом приемной стороны.

2.Система по п.1, отличающаяся тем, что блок управления шагом квантования содержит выпрямитель, функциональный преобразователь, центрирующий фильтр, сумматор, компаратор, источник опорных напряжений и дифференцирующий элемент, вход которого является входом блока, а выход через выпрямитель подключен к входам функционального преобразователя и центрирующего фильтра, выход которого соединен с первым входом компаратора и является первым выходом блока, выход функционального преобразователя и первый выход источника опорных напряжений подключены к входам сумматора, выход которого является вторым выходом блока, второй выход источника опорных напряжений соединен с вторым входом компаратора, выход которого является третьим выходом блока.

3.Система по п.1,отличающаяся тем, что блок управления частотой дискретизации содержит сумматор, компаратор, выпрямитель, первый и второй функциональные преобразователи, источник опорного напряжения, регулируемый аттенюатор, ключевой элемент, фазовый дискриминатор и фильтр нижних частот, вход первого функционального преобразователя является первым информационным входом блока, выход первого функционального преобразователя соединен с первым входом сумматора и входом выпрямителя, выход которого подключен к первому входу компаратора и входу второго функционального преобразователя, выход которого соединен с управляющим входом регулируемого аттенюатора, первый и второй входы фазового дискриминатора являются соответственно вторым информационным и тактовым входами блока, выход фазового дискриминатора через фильтр нижних частот подключен к информационному входу регулируемого аттенюатора, выход которого соединен с информационным входом ключевого элемента, выход источника опорного напряжения подключен к второму входу

компаратора, выход которого соединен с управляющим входом ключевого элемента, выход которого подключен к второму входу сумматора, выход которого является выходом блока,

4. Система по п.1,отличающаяся тем, что блок формирования синхронного сигнала содержит первый - четвертый триггеры, реверсивный счетчик, регистр сдвига, первый - n-й дешифраторы, (п - коэффициент пересчета реверсивного счетчика), первый - (п+3)-й элементы И, первый и второй элементы ИЛИ, первый-третий элементы задержки, элемент НЕ и первый и второй выпрямители, входы которых объединены и являются информационным входом блока, выходы первого и второго выпрямителей через соответственно второй элемент задержки и последовательно соединенные элемент НЕ и третий элемент задержки подключены к первому и второму входам четвертого триггера, выход которого соединен с информационным входом регистра сдвига, первые входы первого и второго триггеров и первого элемента И объединены и являются первым тактовым входом блока, вторые входы первого и второго триггеров, первый вход второго элемента И и вход первого элемента задержки объединены и являются вторым тактовым входом блока, выходы первого и второго триггеров соединены с вторыми входами одноименных элементов И, выход первого элемента И подключен ,к суммирующему входу реверсивного счетчика и первому входу первого элемента ИЛИ, выход второго элемента И соединен с первым входом третьего триггера и вычитающим входом реверсивного счетчика, установочный вход которого является установочным входом блока, выходы реверсивного счетчика подключены к входам первого - п-го дешифраторов, выходы которых соединены с первыми входами соответственно четвертого - (п+3)-го элементов И, выход первого элемента задержки подключен к второму входу первого элемента ИЛИ, выход которого соединен с первым входом третьего элемента И и вторым входом третьего триггера, выход которого подключен к второму входу третьего элемента И, выход которого соединен с тактовым входом регистра сдвига, выходы первого - п-го разрядов которого подключены к вторым входам соответственно четвёртого - (л+3)-го элементов И, входы которых соединены с входами .второго элемента ИЛИ, выход которого является выходом блока.

5. Система по п.1,отличающаяся тем, что блок формирования асинхронного сигнала содержит первый - третий триггеры, реверсивный счетчик, первый - п-й дешифраторы (п - коэффициент пересчета реверсивного счетчика), первый - (2п+3)-й элементы И, первый - третий элементы ИЛИ, первый - третий элементы задержки, дифференциальный усилитель и регистр

сдвига, информационный вход которого через второй элемент задержки подключен к информационному входу блока, первые входы первого и второго триггеров, первого элемента задержки и первого элемента И

объединены и являются первым тактовым входом блока, вторые входы первого и второго триггеров и первый вход второго элемента И объединены и являются вторым тактовым входом блока, выходы первого и

второго триггеров соединены с вторыми входами одноименных элементов И, выход первого элемента И подключен к первому входу третьего триггера и суммирующему входу реверсивного счетчика, установочный

вход которого является установочным входом блока, выход второго элемента И соединен с первым входом первого элемента ИЛИ и вычитающим входом реверсивного счетчика, выходы которого подключены к

входам первого - п-го дешифраторов, выходы которых соединены с первыми входами соответственно четвертого и пятого, шестого и седьмого, ..., (2п+2}-го и (2п+3}-го элементов И, выход первого элемента

задержки подключен к второму входу первого элемента ИЛИ и входу третьего элемента задержки, выход которого соединен с вторыми входами четвертого - (2п+3)-го элементов И, выход первого элемента ИЛИ

подключен к первому входу третьего элемента И и второму входу третьего триггера, выход которого соединен с вторым входом третьего элемента И, выход которого подключен к тактовому входу регистра сдвига,

инверсный и прямой выходы первого - п-го разрядов которого соединены с третьими входами соответственно (2п+3)-го и (2п+2)-го, (2п+1}-го и (2п)-го, ..., пятого и четвертого элементов И, выходы четвертого, шестого,

,,., (2п+2}-го элементов И подключены к входам второго элемента ИЛИ, выходы пятого, седьмого(2п+3)-го элементов И соединены с входами третьего элемента ИЛИ; выходы второго и третьего элементов ИЛИ

5 подключены к первому и второму входам дифференциального усилителя, выход которого является выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодер | 1987 |

|

SU1429321A1 |

| Универсальный дельта-кодек | 1982 |

|

SU1078612A1 |

| СПОСОБ ДИСКРЕТНОГО КОНТРОЛЯ РАССТОЯНИЙ ДО ИСТОЧНИКА КОЛЕБАНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2028579C1 |

| ВЫСОКОИНФОРМАТИВНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ИСПОЛЬЗОВАНИЕМ ДЕЛЬТА-МОДУЛЯЦИИ ДЛЯ СЕЙСМИЧЕСКИХ ИССЛЕДОВАНИЙ | 1997 |

|

RU2128880C1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| Устройство для регистрации сейсмических сигналов | 1989 |

|

SU1681288A1 |

| Устройство измерения параметров радиоимпульсов | 1976 |

|

SU656401A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1510091A1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

Изобретение относится к автоматике и технике связи, Его использование позволяет повысить точность передачи сигналов и повысить эффективность системы за счет снижения скорости передачи и сужения энергетического спектра передаваемого сигнала. Система связи содержит канал 3связи, на передающей стороне 1 - блок 4вычитания, квантователь 5, формирователь 6 информационной импульсной последовательности, интегратор 9, фильтр 10 нижних частот (ФНЧ) и перестраиваемый генератор, на приемной стороне 2 - интегратор 16, ФНЧ 17, 18 и перестраиваемый генератор 21. Цель изобретения достигается са счет введения блоков 11 и 19 управления шагом квантования, блоков 12 и 20 управления частотной дискретизации, амплитудно-импульсных модуляторов 8 и 15, блока 7 формирования синхронного сигнала и блока 14 формирования асинхронного сигнала, благодаря чему обеспечиваются согласованное изменение шагов квантования и дискретизации, а также синхронная передача асинхронного дельта-модулированно- го сигнала. 4 э.п. ф-лы, 7 ил.

2 Мф

9t

I

SS

I

S69fr29l

109

о

ПО

111

Фиг. 5

Фиг. 6

107

т

ч-

Vi

S t

v

Ю Оч

Cj

QO

Q 10

Nh s f

| Дельта-модуляция | |||

| Под ред | |||

| М.Д.Бенедиктова | |||

| М.: Связь, 1976, с.175 Авторское свидетельство СССР № 1193820, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-01-30—Публикация

1989-02-03—Подача