1

Изобретение относится к импульсной технике и может найти применение в качестве л -канального фильтра для различения импульсных сигналов по частоте в полосе частот.

Цель изобретения - повьшение надежности функционирования за счет исключения неоднозначности выходного эквивалента при определенных соотношениях времени поступления входного сигнала и времени срабатывания элементов при одновременном упрощении.

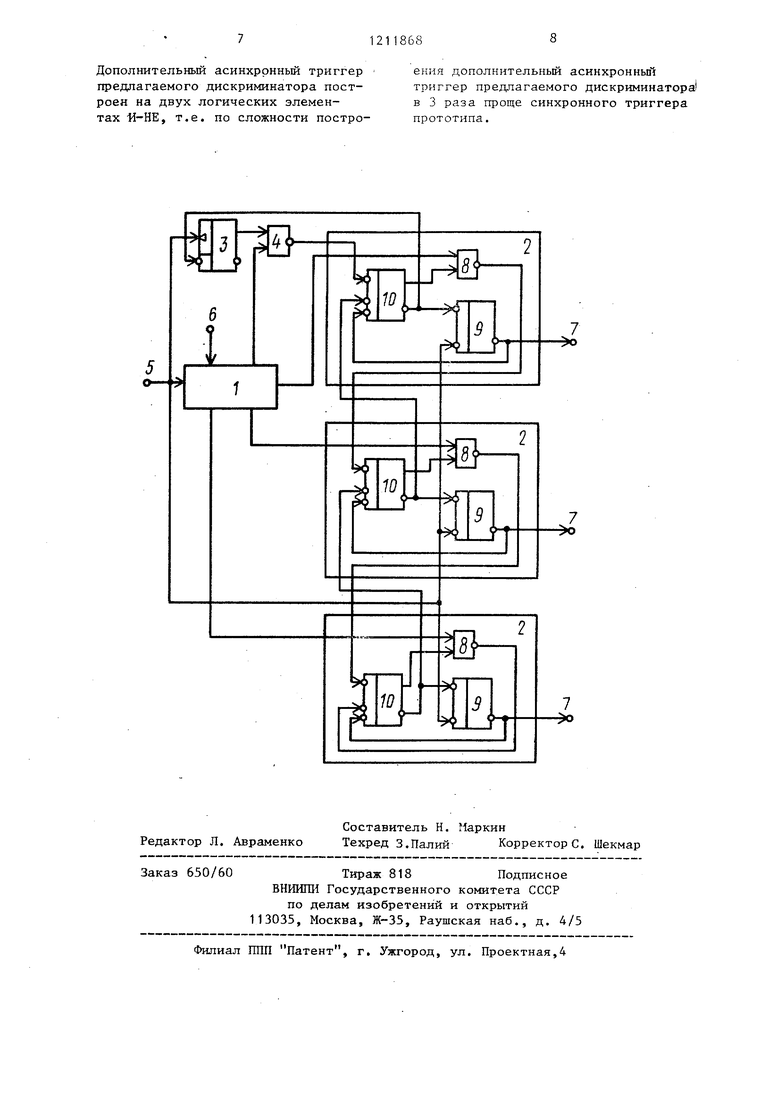

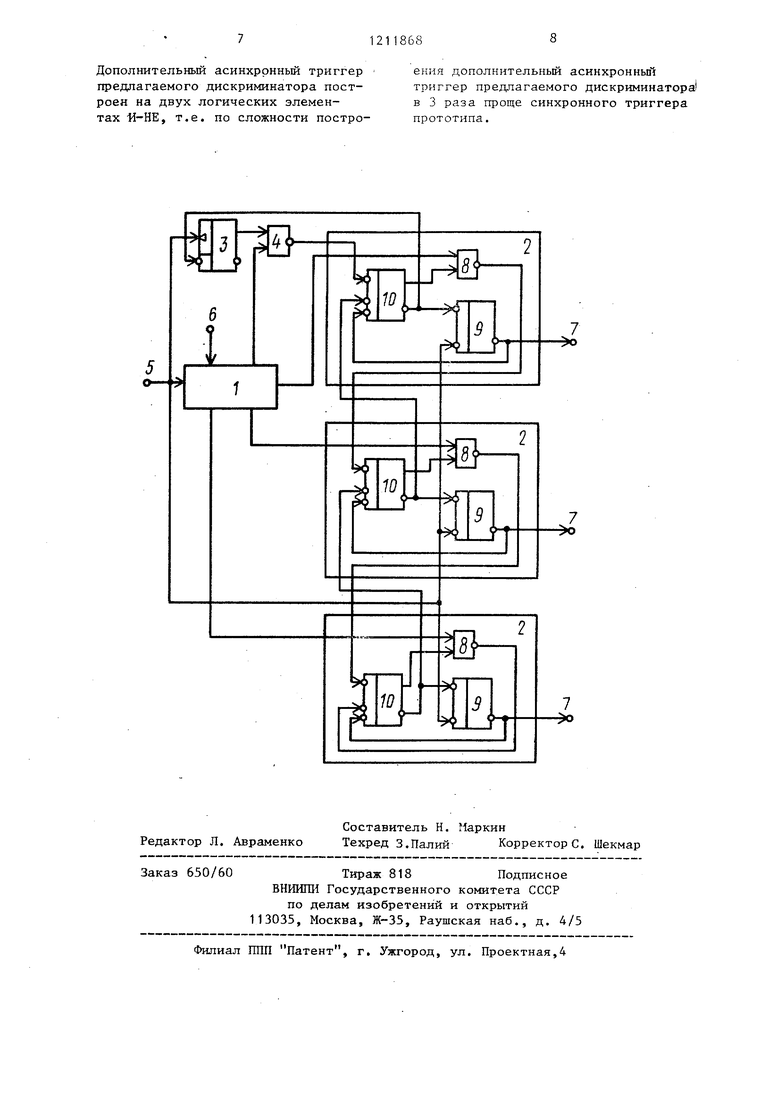

На чертеже представлена структурная схема частотного дискриминатора

Частотньй дискриминатор содержит счетчик 1 импульсов и каналы 2 дискриминации, при этом вход установки в нуль счетчика 1 импульсов подключен к тактовому входу синхронного триггера 3, прямой выход которого подключен к входу элемента 4 совпадения, и входной шине 5,а тактовый вход счетчика 1 импульсов соединен с шиной 6 тактовых импульсов., выходы 7 каналов 2 дискриминации являются выходами устройства, причем каждый канал 2 дискриминации содержит элемент 8 совпадения, первые входы которого соединены с соответствующими выходами счетчика 1 импульсов, и асинхронный триггер 9, входом соединенным с инверсным выходом дополнительного асинхронного триггера 10,

Счетчик 1 импульсов является двоичным счетчиком и может быть построен по асинхронной схеме, например, на интегральных микросхемах 133ИЕ5, Наращивание разрядов счетчика 1 импульсов производится путем подключения выхода старшего разряда счетчика 133Iffi5 к входу младшего разряда следующего счетчика 133ИЕ5,

В каждом канале 2 дискриминации элемент 8 совпадения является элементом И-НЕ, асинхронный триггер 9 и дополнительный асинхронный триггер 10 выполнен каждый на двух элементах И-НЕ, причем отличие этих триггеров состоит в том, что триггер 10 имеет второй вход установки в нуль,

Синхронный триггер 3 выполнен на 33-триггере интегральной микросхемы 133ТМ2, на тактовом входе которого дополнительно вклкзчается ин-

18682

вертор, вход которого является тактовым входом синхронного триггера 3.

Элемент 4 совпадения может быть выполнен на элементе И-НЕ.

Количество первых входов у элемента 4 и элементов 8 совпадения-может быть различным и определяется кодовой комбинацией, которую дед шифрирует соответствующий элемент 4 или элемент 8.

Частотный дискриминатор работает следующим образом.

При включении напряжения питания,

5 низкий потенциал, присутствующий на входной шине 5 и импульсы тактовой частоты, поступающие на щину 6 тактовых импульсов, приводят частотный дискриминатор в состояние, при коQ тором асинхронный триггер 9 и дополнительный асинхронный триггер 10 каждого канала 2, а также синхронный триггер 3 обнулены (на прямых выходах этих триггеров присутствует

5 низкий потенциал, а на инверсных - высокий потенциал). Счетчик 1 импульсов считает импульсы тактовой частоты и может периодически переполняться, но кодовые комбинации счетчика 1 импульсов не дешифрируются элементами 8 И-НЕ каналов 2 и элементом 4 И-НЕ, так как появление сигнала дешифрации на выходе каждого из этих элементов запрещено низким потенциалом, поступающим с

прямого выхода соответствующего дополнительного асинхронного триггера 10 канала 2 и синхронного триггера 3. При поступлении на входную шину 5 первого входного импульса, счетчик 1 импульсов обнуляется, При окончании первого входного импульса по его заднему фронту синхронный триггер 3 устанавливается в единичное состояние, после этого частотный дискриминатор оказывается приведенным в исходное состояние, т.е. подготовлен к различению по частоте входных импульсов, следующих на входную шину 5. По окончании вход50 ного импульса на входной шине 5

в счетчик 1 импульсов начинают поступать тактовые импульсы. Верхнюю 1 раницу частоты среза первого канала 2 определяет кодовая комбина55 ция, дешифрируемая элементом И-НЕ 4 Ншкняя граница частоты среза первр- го канала определяется кодовой ком- бинацией, дешифрируемой элементом

0

0

5

3

И-НЕ 8 первого канала 2, в то же время нижняя граница частоты среза для первого канала является верхней границей частоты среза для второго канала 2, а нижняя граница частоты среза для второго канала 2, которая определяется кодовой комбинацией, дешифрируемой элементом И-НЕ 8 второго канала 2, является ве рхней границей частоты среза для третьего канала и т.д. При появлении в счетчике 1 кодовой комбинации, на которую настроен элемент 4 И-НЕ, этот элемент переключается и на выходе этого элемента формируется низкий потенциал, которьй поступает на единичный вход дополнительного асинхронного триггера 10 первого ка,нала 2. Производится установка дополнительного асинхронного триггера 10 первого канала 2 в единичное состояние. Появление низкого потенциала на инверсном выходе дополнительного асинхронного триггера 10 первого канала 2 подготавливает асинхронный триггер 9 первог канала 2 к отработке входного импульса, при появлении его на входно шине 5. Низкий потенциал, появляю- на инверсном выходе дополнительного асинхронного триггера 10 проводит установку синхронного триггера 3 в нулевое состояние. При появлении входного импульса на шине 5 он инвертируется асинхронным триггером 9 первого канала 2 и поступае на выход 7 этого канала 2. Появление входного импульса на входной шине 5 вызьшает обнуление счетчика

1импульсов. При появлении вьгходног импульса на выходе 7 первого канала

2производится переключение допол- нительногб асинхронного триггера 10 этого канала в исходное нулевое состояние. Однако асинхронный триггер 9 первого канала 2 ,не переклю- |чается в течение длительности входного импульса на входной шине 5. При окончании входного импульса на входной пшне 5 синхронный триггер 3 устанавливается в единичное состояние, импульс на выходе 7 первого канала 2 оканчивается. Частотный дискриминатор оказьшается приведенным в исходное состояние и начинается процесс различения по частоте еледзтощих входных импульсов.

Если входной импульс на входной шине 5 не появляется после установ-868

кн в единичное состояние дополнительного асинхронного триггера 10 первого канала 2 и обнуления синхронного триггера 3, то через некоторое время в счетчике 1 импульсов появляется кодовая комбинация, на которую настроен элемент И-НЕ 8 первого канала 2. При появлении в счетчике 1 кодовой комбинации, на

0 которую настроен элемент И-НЕ 8

первого канала 2, этот элемент переключается и на выходе этого элемента формируется низкий потенциал, который поступает на единичный вход

5 триггера 10 второго канала 2. Производится установка дополнительного асинхронного триггера 10 второго канала 2 в единичное состояние . Появление низкого потенциала

0 на икверсном выходе дополнительного асинхронного триггера 10 второго канала 2 подготавливает асин- хронньпг триггер 9 второго канала 2 к отработке входного импульса при

5 появлении его на шине 5. Низкий потенциал, появляющийся на инверсном выходе дополнительного асинхронного триггера 10 второго канала 2, производит установку дополп нитсльного асинхронного триггера 10 первого канала 2 в нулевое состояние , При появлении входного импульса на шине 5 он инвертируется асинхронным триггером 9 второго канала 2 и поступает на выход 7 второго канала 2. Появление входного импульса на входной шине 5 вызывает обнуление счетчика 1 импульсов.При появлении выходного импульса на выходе 7 второго канала 2 производится переключение дополнительного асинхронного триггера 10 этого канала 2 в исходное нулевое состояние. Однако асинхронный триггер 9 второго канала 2 не переключается в течение длительности входного импульса на входной шине 5. При окончании входного импульса на входной шине 5 синхронный триггер 3 устанавливается в единичное состояние, импульс на выходе 7 второго канала дискриминации оканчивается. Частотный дискриминатор оказывается приведен- .ным в исходное состояние и начинается процесс различения по частоте следующих входных импульсов.

Если входной импульс на входной шине 5 не появляется после установки в единичное состояние дополни5

0

5

0

5

тельного асинхронного триггера 10 последующего канала 2 и обнуления дополнительного асинхронного триггера 10 предыдущего канала 2, то через некоторое время в счетчике 1 импульсов появляется кодовая комбинация, на которую настроен элемент 8 совпадения последующего канала 2 дискриминации. При появлении входного импульса на входцой шине 5 процесс формирования импульса на выходе 7 последующего канала 2 дискриминации аналогичен рассмотренному процессу формирования импульса на выходе 7 первого или второго каналов 2. Это верно и для последнего канала 2 с той только разницей, что при отсутствии входного импульса на шине 5 после установки дополнительного асинхронного триггера 10 последнего канала в единичное состояние , через некоторое время в счетчике 1 импульсов появляется кодовая комбинация, на которую настроен элемент 8 совпадения последнего канала. При этом элемент 8 совпадения переключается и низким потенциалом с его выхода производится установка дополнительного асинхронного триггера 10 последнего канала в исходное нулевое состояние что вызывает переключение элемента 8 совпадения в исходное состояние .

Таким образом, если частота входных импульсов находится в полосе прозрачности частотного дискриминатора, то входной импульс инвертируется асинхронным триггером 9 одного из каналов 2 дискриминации и поступает на выход 7 этого канал;а 2. По окончании входного импульса, частотный дискриминатор с исходного состояния начинает процесс различения по частоте следующих входных импульсов.

Если частота входных импульсов на входной шине 5 лежит выше верхней частоты среза первого канапа 2 или ниже нижней границы частоты среза Г) -го канала 2, то входные импульсы не проходят на вых;од 7 ни одного из каналов, так как синхронный триггер 3 и дополнительные асинхронные триггеры 10 всех каналов 2 будут обнулены. Высокий потенциал с инверсного выхода каждо5

0

го из триггеров 10 запрещает переключение соответствующего асинхронного триггера 9.

5 Таким образом, на выходах 7 соответствующих каналов 2 частот ного дискриминатора производится выделение входных импульсов, частота следования которых находится

О в полосе прозрачности этих каналов 2. 1

В предлагаемом частотном дискриминаторе синхронный триггер 3 устанавливается в единичное состояние задним фронтом входного импульса, т.е. после обнуления счетчика 1 импульсов, что исключает возможность прохождения на выход первого канала 2 входных импульсов, частота которых лежит ниже нижней частоты среза последнего канала 2. Так как в этом случае запрещено срабатывание элемента 4

, совпадения при наличии соответствующего его настройке кода в счетчике 1 импульсов в моменты поступления входных импульсов на шину 5, и открывание первого канала 2. В то время, как в прототипе существует возможность нарушения алгоритма работы, состоящая в прохождении входных импульсов, частота которых лежит ниже нижней частоты среза последнего канала, на выход первого

5 канала, если в момент появления

этих импульсов в счетчике импульсов содержится код, соответствующий настройке элемента совпадения и время установки в нуль счетчика импульсов

достаточно для срабатывания цепи - синхронньй триггер, элемент совпадения, элемент ИЛИ, синхронный триггер первого канала дискриминации Таким образом, предлагаемое устрой ство обеспечивает повышение функциональной надежности.

0

Кроме того, схема предлагаемого частотного дискриминатора является проще, исключается многовходо- вой элемент ИЛИ и заменяется в каждом канале дискриминации синхронный триггер на относительно простой дополнительный асинхронньй триггер. В качестве синхронного триггера в прототипе использован Л -триггер микросхемы 133ТМ2, который содержит шесть логических элементов И-НЕ.

Дополнительный асинхронный триггер - предлагаемого дискриминатора построен на двух логических элементах И-НЕ, т.е. по сложности построения дополнительный асинхронньпЧ триггер предлагаемого дискриминатора в 3 раза проще синхронного триггера прототипа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный дискриминатор | 1983 |

|

SU1091329A1 |

| Управляемый делитель частоты следования импульсов | 1990 |

|

SU1793543A1 |

| Цифровой дискриминатор средней частоты | 1985 |

|

SU1293835A1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Цифровой частотный дискриминатор | 1979 |

|

SU849419A1 |

| Формирователь синхронизированных импульсов по фронту и спаду | 1982 |

|

SU1115211A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2000 |

|

RU2167493C1 |

| Устройство тактовой синхронизации | 1978 |

|

SU748839A1 |

Редактор Л. Авраменко

Составитель Н. Маркин

Техред 3.Палий Корректоре. Шекмар

650/60

Тираж 818Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная,4

| Частотный дискриминатор | 1979 |

|

SU885915A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Частотный дискриминатор | 1983 |

|

SU1091329A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1986-02-15—Публикация

1984-06-26—Подача