Изобретение относится к импульсной технике и может быть использовано в качестве управляемого делителя частоты следования импульсов.

Известен делитель частоты следования импульсов поа.с. №993439, кл. Н 03 КЗ/281, содержащий управляющую шину, два инвертора, элемент И, компаратор, времяза- дающую RC-цепь и делитель напряжения. Известный делитель при отсутствии управляющего сигнала формирует последовательность импульсов определенной частоты, а при подаче управляющего сигнала (высокого потенциала) обеспечивает дискретное изменение частоты следования выходных импульсов. Недостатком известного делителя является узкий диапазон частот следования выходных импульсов, т.к. при поступлении управляющего сигнала (высокого потенциала) частота следования выходных импульсов не более чем в 4 раза может отличаться от определенной частоты, формируемой известным делителем при отсутствии управляющего сигнала.

Наиболее близким по технической сущности к предлагаемому делителю является Управляемый делитель частоты следования импульсов по а.с. № 1211878, кл. Н 03 К 23/40. Этот делитель содержит последовательно соединенные элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, счетчик импульсов на N, первый Т-триггер, выход которого подключен к первому входу элемента ИСКЛ ЮЧ АЮ- ЩЕЕ ИЛИ, второй вход которого соединен с входной шиной, элемент И, первый вход которого подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход - к С-входу первого Т-триггера, шину управления коэффициентом деления и шину управления дробным коэффициентом деления, причем информационные входы счетчика импульсов на N соединены с шиной управления коэффициентом деления, вход разрешения параллельной записи кода счетчика импульсов на N соединен с выходом элемента И, С-входом первого Т-триггера - с выходной шиной, инверсный выход заема счетчика импульсов на N подключен к инверсному R-входу второго Т-триггера, инверсный выел

С

V ю

03 СЛ

N

CJ

ход которого подключен к второму входу элемента И, а инверсный R-вход первого Т-триггера соединен с шиной управления дробным коэффициентом деления. Недостатком известного управляемого делителя является низкая функциональная надежность, Управляющий сигнал асинхронен по отношению к импульсам опорной частоты. Поэтому равновероятно, что поступление на шину 6 управления дробным коэффициентом деления управляющего сигнала (низкого потенциала) придется на момент времени, когда на входной шине 8 действует импульс или пауза между импульсами .опорной частоты. Однако нормальное функционирование известного делителя, т.е. алгоритм работы, нарушается каждый раз при поступлении управляющего сигнала в момент действия импульса опорной частоты, Причем нарушение алгоритма работы может иметь различный характер. В одном случае, вследствие преждевременного изменения фазы импульса на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2, последний период следования выходных импульсов уменьшается относительно установленного на время 0,5Тьп, где Ton - период следования импульсов опорной частоты на входной шине 8. В другом случае, вследствие уменьшения длительности выходного импульса относительно номинального значения, не обеспечивается надежная запись кода в счётчик 1, в результате очередной выходной импульс формируется через случайный период времени. В третьем случае также из-за уменьшения длительности выходного импульса относительно номинального значения может не обеспечиться переключение в единичное состояние триггера 5, вследствие чего через элемент И 3 на выходную шину 7 будет поступать последовательность импульсов с периодом Топ. Таким образом, нарушение алгоритма работы известного делителя при поступлении управляющего сигнала в момент действия импульса опорной частоты снижает функциональную надежность.

Цель изобретения - повышение функциональной надежности за счет исключения нарушения алгоритма работы при поступлении управляющего сигнала в момент действия импульса опорной частоты.

Поставленная цель достигается тем, что в управляемый делитель частоты следования импульсов, содержащий два триггера, счетчик импульсов, управляющий вход, вход опорной частоты и кодовые входы, соединенные с информационными входами счетчика импульсов, введены элемент И-НЕ, первый и второй инверторы, причем первый

вход элемента И-НЕ соединен с входом опорной частоты делителя и с тактовым входом счетчика импульсов, выход которого соединен с тактовым входом первого триггера и через первый инвертор соединен с тактовым входом второго триггера, выход которого соединен с входом сброса счетчика импульсов, с входами I и К первого триггера, вход установки которого соединен с выходом элемента И-НЕ, второй вход которого Соединен с входом разрешения записи счетчика импульсов и с выходом первого триггера, управляющий вход делителя соединен с входом I и через второй инвертор соединен с входом К второго триггера.

Введение в управляемый делитель элемента И-НЕ и двух инверторов с соответствующимисвязями повысило функциональную надежность за сч.ет исключения нарушения алгоритма работы при поступлении управляющего сигнала в момент действия импульса опорной частоты. В предлагаемом делителе на втором триггере

5 осуществляется привязка моментов поступления и окончания управляющего сигнала (высокого потенциала) к фронту импульсов опорной частоты, т.е. синхронизация по фазе управляющего сигнала импульсами опорной частоты. Таким образом, в предлагаемом делителе исключены нарушения работы, присущие прототипу и связанные с асинхронностью управляющего сигнала относительно импульсов опорной частоты.

В известных заявителю и авторам технических решениях нет признаков, отличающих предлагаемый делитель от делителя-прототипа. Следовательно, можно предположить, что предлагаемый делитель обладает существенными отличиями от известных делителей.

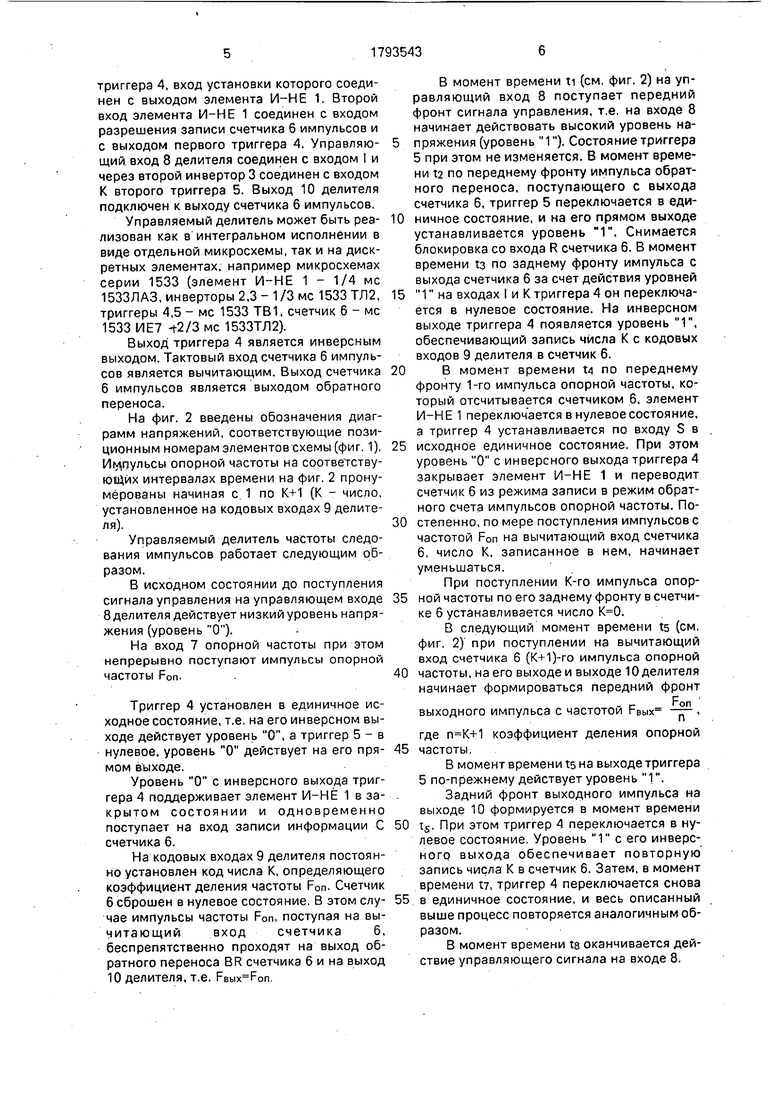

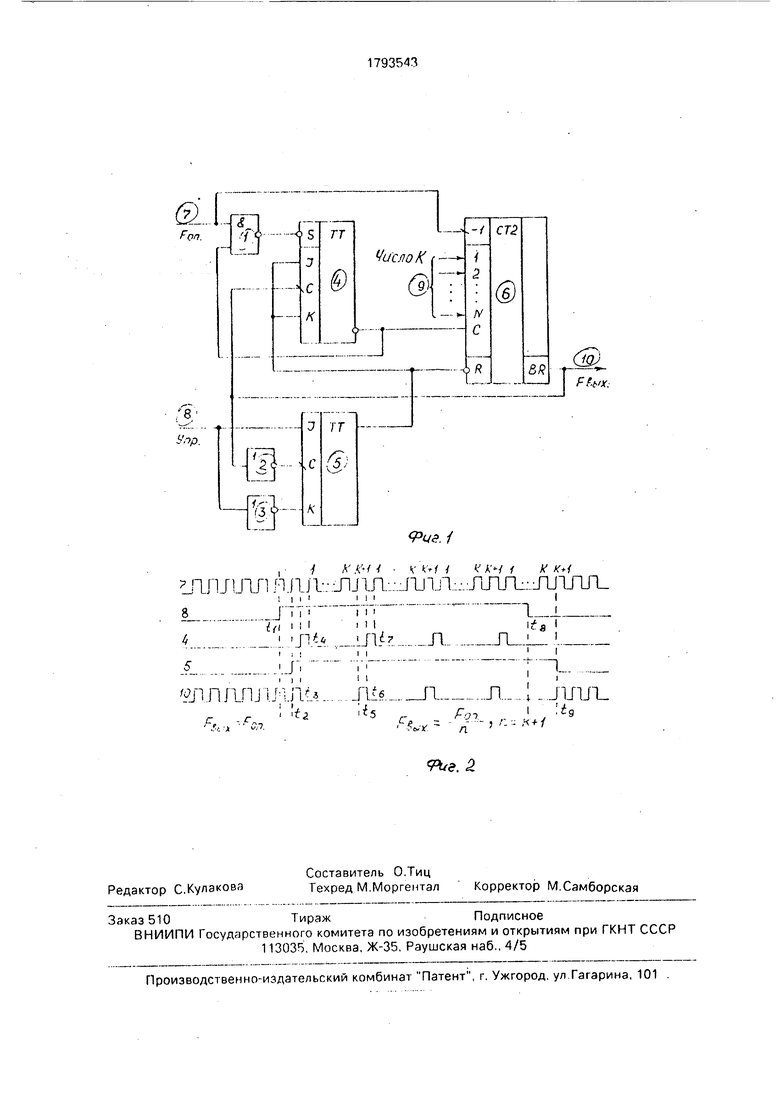

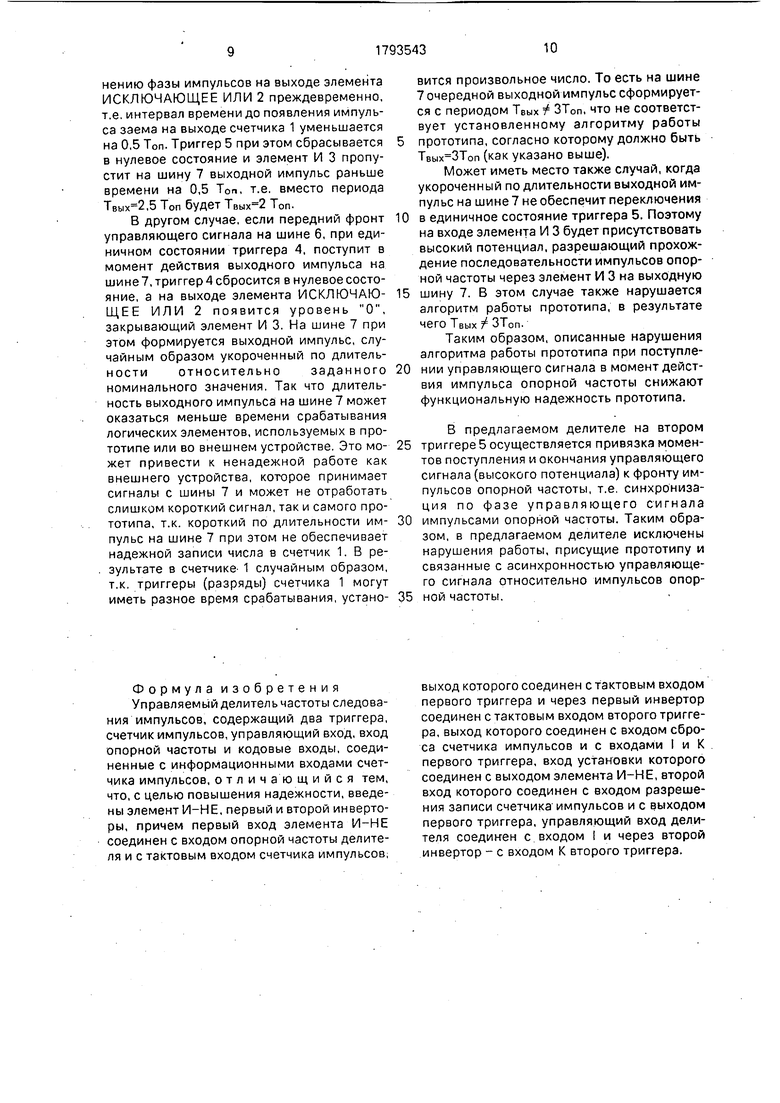

На фиг. 1 приведена функциональная схема делителя; на фиг. 2 - временные диаграммы его работы.

Управляемый делитель содержит элемент И-НЕ 1, первый и второй инверторы 2 и 3, первый и второй триггеры 4 и 5, счетчик

6 импульсов, вход 7 опорной частоты, управляющий вход 8, кодовые входы 9 и выход 10. Кодовые входы 9 соединены с информационными входами счетчика 6 импульсов. Первый вход элемента И-НЕ 1 соединен с входом 7 опорной частоты делителя и с тактовым входом счетчика 6 импульсов. Выход 5 счетчика б импульсов соединен с тактовым входом первого триггера 4 и через первый инвертор 2 соединен с тактовым входом второго триггера 5. Выход второго триггера 5 соединен с входом сброса счетчика 6 импульсов, соединен с входами I и К первого

0

5

0

5

0

5

0

5

0

триггера 4, вход установки которого соединен с выходом элемента И-НЕ 1. Второй вход элемента И-НЕ 1 соединен с входом разрешения записи счетчика 6 импульсов и с выходом первого триггера 4. Управляющий, вход 8 делителя соединен с входом I и через второй инвертор 3 соединен с входом К второго триггера 5. Выход 10 делителя подключен к выходу счетчика 6 импульсов.

Управляемый делитель может быть реализован как в интегральном исполнении в виде отдельной микросхемы, так и на дискретных элементах, например микросхемах серии 1533 (элемент И-НЕ 1 - 1/4 мс 1533ЛАЗ, инверторы 2.3- 1/3 мс 1533 ТЛ2. триггеры 4,5 - мс 1533 ТВ1, счетчик 6 - мс 1533 ИЕ7 -t2/3 мс 1533ТЛ2).

Выход триггера 4 является инверсным выходом. Тактовый вход счетчика 6 импульсов является вычитающим. Выход счетчика 6 импульсов является выходом обратного переноса.

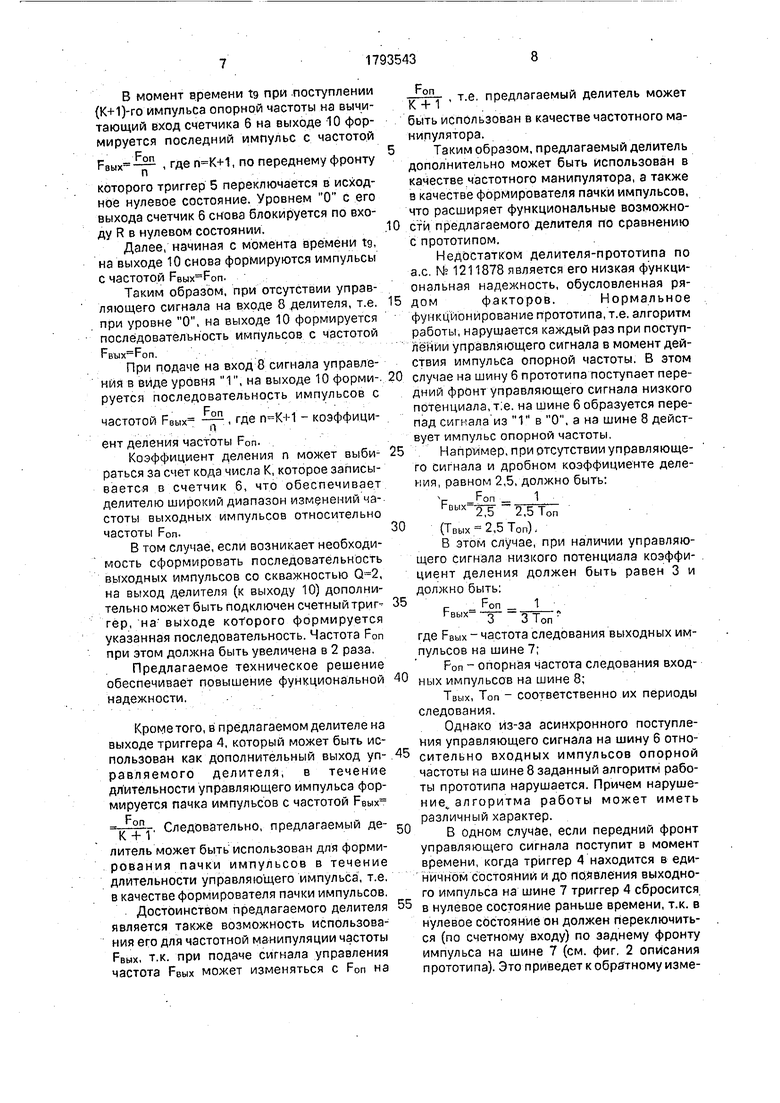

На фиг. 2 введены обозначения диаграмм напряжений, соответствующие позиционным номерам элементов схемы (фиг. 1). Импульсы опорной частоты на соответствующих интервалах времени на фиг. 2 пронумерованы начиная с. 1 по К+1 (К - число, установленное на кодовых входах 9 делителя).

Управляемый делитель частоты следования импульсов работает следующим образом.

В исходном состоянии до поступления сигнала управления на управляющем входе 8 делителя действует низкийуровень напряжения (уровень О).

На вход 7 опорной частоты при этом непрерывно поступают импульсы опорной частоты Fon.

Триггер 4 установлен в единичное исходное состояние, т.е. на его инверсном выходе действует уровень О, а триггер 5 - в нулевое, уровень О действует на его прямом выходе.

Уровень О с инверсного выхода триггера 4 поддерживает элемент И-НЁ 1 в закрытом состоянии и одновременно поступает на вход записи информации С счетчика 6.

На кодовых входах 9 делителя постоянно установлен код числа К, определяющего коэффициент деления частоты F0n. Счетчик 6 сброшен в нулевое состояние. В этом случае импульсы частоты F0n, поступая на вычитающий вход счетчика 6, беспрепятственно проходят на выход обратного переноса BR счетчика 6 и на выход 10 делителя, т.е. .

В момент времени ti (см. фиг. 2) на управляющий вход 8 поступает передний фронт сигнала управления, т.е. на входе 8 начинает действовать высокий уровень напряжения (уровень 1). Состояние триггера 5 при этом не изменяется. В момент времени t2 по переднему фронту импульса обратного переноса, поступающего с выхода счетчика 6, триггер 5 переключается в единичное состояние, и на его прямом выходе устанавливается уровень 1, Снимается блокировка со входа R счетчика 6. В момент времени тз по заднему фронту импульса с выхода счетчика 6 за счет действия уровней

1 на входах I и К триггера 4 он переключается в нулевое состояние. На инверсном выходе триггера 4 появляется уровень Г, обеспечивающий запись числа К с кодовых входов 9 делителя в счетчик 6.

В момент времени t4 по переднему фронту 1-го импульса опорной частоты, который отсчитывается счетчиком 6. элемент И-НЕ 1 переключается в нулевое состояние, а триггер 4 устанавливается по входу S в

исходное единичное состояние. При этом уровень О с инверсного выхода триггера 4 закрывает элемент И-НЕ 1 и переводит счетчик 6 из режима записи в режим обратного счета импульсов опорной частоты. Постепенно, по мере поступления импульсов с частотой Fon на вычитающий вход счетчика 6, число К, записанное в нем, начинает уменьшаться.

При поступлении К-го импульса опорной частоты по его заднему фронту в счетчике 6 устанавливается число .

В следующий момент времени ts (см, фиг. 2) при поступлении на вычитающий вход счетчика 6 (К+1)-го импульса опорной

частоты, на его выходе и выходе 10 делителя начинает формироваться передний фронт

г- ОП

выходного импульса с частотой гвых -- ,

где коэффициент деления опорной

частоты,

В момент времени ts на выходе триггера 5 по-прежнему действует уровень Г.

Задний фронт выходного импульса на выходе 10 формируется в момент времени

ts. При этом триггер 4 переключается в нулевое состояние. Уровень 1 с его инверсного выхода обеспечивает повторную запись числа К в счетчик 6. Затем, в момент времени :, триггер 4 переключается снова

в единичное состояние, и весь описанный выше процесс повторяется аналогичным образом,

В момент времени ts оканчивается действие управляющего сигнала на входе 8.

В момент времени tg при .поступлении (К+1)-го импульса опорной частоты на вычитающий вход счетчика 6 на выходе 10 формируется последний импульс с частотой

, где , по переднему фронту

которого триггер 5 переключается в исходное нулевое состояние. Уровнем О с его выхода счетчик 6 снова блокируется по входу R в нулевом состоянии.

Далее, начиная с момента времени tg, на выходе 10 снова формируются импульсы с частотой .

Таким образом, при отсутствии управляющего сигнала на входе 8 делителя, т.е. при уровне О, на выходе 10 формируется последовательность импульсов с частотой ..- .

При подаче на вход 8 сигнала управления в виде уровня 1, на выходе 10 форми-. руется последовательность импульсов с

частотой Рвых --., где - коэффициент деления частоты F0n.

Коэффициент деления п может выбираться за счет кода числа К, которое записывается в счетчик 6, что обеспечивает делителю широкий диапазон изменений ча-- стоты выходных импульсов относительно частоты FOR.

В том случае, если возникает необходимость сформировать последовательность выходных импульсов со скважностью , на выход делителя (к выходу 10) дополнительно может быть подключен счетный триггер, на выходе которого формируется указанная последовательность. Частота F0n при этом должна быть увеличена в 2 раза.

Предлагаемое техническое решение обеспечивает повышение функциональной надежности.

Кроме того, в предлагаемом делителе на выходе триггера 4, который может быть использован как дополнительный выход управляемого делителя, в течение длительности управляющего импульса формируется пачка импульсов с частотой РВых

. Следовательно, предлагаемый деК. т

литель может быть использован для форми- рования пачки импульсов в течение длительности управляющего импульса, т.е. в качестве формирователя пачки импульсов. Достоинством предлагаемого делителя является также возможность использования его для частотной манипуляции частоты Рвых, т.к. при подаче сигнала управления частота РВых может изменяться с F0n на

0

5

0

5

0

5

0

5

0

5

РВЫХ-

тг-rV . т-е предлагаемый делитель может

1ч т I

быть использован в качестве частотного манипулятора.

Таким образом, предлагаемый делитель дополнительно может быть использован в качестве частотного манипулятора, а также в качестве формирователя пачки импульсов, что расширяет функциональные возможности предлагаемого делителя по сравнению с прототипом.

Недостатком делителя-прототипа по а.с. № 1211878 является его низкая функциональная надежность, обусловленная рядомфакторов. Нормальное функционирование прототипа, т.е. алгоритм работы, нарушается каждый раз при поступлении управляющего сигнала в момент действия импульса опорной частоты. В этом случае на шину 6 прототипа поступает передний фронт управляющего сигнала низкого потенциала, т:е. на шине 6 образуется перепад сигнала из 1 в О, а на шине 8 действует импульс опорной частоты.

Например, при отсутствии управляющего сигнала и дробном коэффициенте деления, равном 2,5, должно быть: ;Fon 1 2,5 2,5 Топ

(Твых 2,5 Топ) ,

В этом случае, при наличии управляющего сигнала низкого потенциала коэффициент деления должен быть равен 3 и должно быть:

с - оп 1

гвых V - о о I оп

где FBbix - частота следования выходных импульсов на шине 7;

Fon - опорная частота следования входных импульсов на шине 8;

Твых, Топ - соответственно их периоды следования.

Однако из-за асинхронного поступления управляющего сигнала на шину 6 относительно входных импульсов опорной частоты на шине 8 заданный алгоритм работы прототипа нарушается. Причем нарушение алгоритма работы может иметь различный характер.

В одном случае, если передний фронт управляющего сигнала поступит в момент времени, когда триггер 4 находится в единичном состоянии и до появления выходного импульса на шине 7 триггер 4 сбросится в нулевое состояние раньше времени, т.к. в нулевое состояние он должен переключиться (по счетному входу) по заднему фронту импульса на шине 7 (см. фиг. 2 описания прототипа). Это приведет к обратному изменению фазы импульсов на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 преждевременно, т.е. интервал времени до появления импульса заема на выходе счетчика 1 уменьшается на 0,5 Топ. Триггер 5 при этом сбрасывается в нулевое состояние и элемент И 3 пропустит на шину 7 выходной импульс раньше времени на 0,5 Т0п, т.е. вместо периода ,5 Топ будет Топ.

В другом случае, если передний фронт управляющего сигнала на шине 6, при единичном состоянии триггера 4, поступит в момент действия выходного импульса на шине 7, триггер 4 сбросится в нулевое состояние, а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 появится уровень О, закрывающий элемент И 3. На шине 7 при этом формируется выходной импульс, случайным образом укороченный по длительности относительно заданного номинального значения. Так что длительность выходного импульса на шине 7 может оказаться меньше времени срабатывания логических элементов, используемых в прототипе или во внешнем устройстве. Это может привести к ненадежной работе как внешнего устройства, которое принимает сигналы с шины 7 и может не отработать слишком короткий сигнал, так и самого прототипа, т.к. короткий по длительности импульс на шине 7 при этом не обеспечивает надежной записи числа в счетчик 1. В результате в счетчике- 1 случайным образом, т.к. триггеры (разряды) счетчика 1 могут иметь разное время срабатывания, установится произвольное число. То есть на шине 7 очередной выходной импульс сформируется с периодом Твых ЗТоп, что не соответствует установленному алгоритму работы

прототипа, согласно которому должно быть (как указано выше).

Может иметь место также случай, когда укороченный по длительности выходной импульс на шине 7 не обеспечит переключения

в единичное состояние триггера 5. Поэтому на входе элемента И 3 будет присутствовать высокий потенциал, разрешающий прохождение последовательности импульсов опорной частоты через элемент И 3 на выходную

шину 7. В этом случае также нарушается алгоритм работы прототипа, в результате чего Твых / ЗТ0п.

Таким образом, описанные нарушения алгоритма работы прототипа при поступлении управляющего сигнала в момент действия импульса опорной частоты снижают функциональную надежность прототипа.

В предлагаемом делителе на втором триггере 5 осуществляется привязка моментов поступления и окончания управляющего сигнала (высокого потенциала) к фронту импульсов опорной частоты, т.е. синхронизация по фазе управляющего сигнала импульсами опорной частоты. Таким образом, в предлагаемом делителе исключены нарушения работы, присущие прототипу и связанные с асинхронностью управляющего сигнала относительно импульсов опор- ной частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты | 1988 |

|

SU1529450A1 |

| Система управления | 1987 |

|

SU1444707A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Блок управления для запоминающего устройства | 1977 |

|

SU723679A1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1980 |

|

SU949821A1 |

| Селектор импульсов по периоду сле-дОВАНия | 1979 |

|

SU813766A1 |

| Управляемый делитель частоты | 1984 |

|

SU1238234A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для синхронизации импульсов | 1985 |

|

SU1325677A1 |

| Формирователь импульсной последовательности с кодоуправляемой скважностью | 1990 |

|

SU1746535A1 |

Сущность изобретения; управляемый делитель частоты следования импульсов содержит два триггера, счетчик импульсов, управляющий вход, вход опорной частоты и кодовые входы,соединенные с информационными входами счетчика импульсов. Введение в управляемый делитель элемента И-НЕ и двух инверторов повышает функциональную надежность устройства за счет исключения нарушения алгоритма работы при поступлении управляющего сигнала в момент действия импульса опорной частоты. 2 ил.

Формула изобретения Управляемый делитель частоты следования импульсов, содержащий два триггера, счетчик импульсов, управляющий вход, вход опорной частоты и кодовые входы, соединенные с информационными входами счетчика импульсов, отличающийся тем, что, с целью повышения надежности, введены элемент И-НЕ, первый и второй инверторы, причем первый вход элемента И-НЕ соединен с входом опорной частоты делителя и с тактовым входом счетчика импульсов;

выход которого соединен с тактовым входом первого триггера и через первый инвертор соединен с тактовым входом второго триггера, выход которого соединен с входом сброса счетчика импульсов и с входами I и К первого триггера, вход установки которого соединен с выходом элемента И-НЕ, второй вход которого соединен с входом разрешения записи счетчика импульсов и с выходом первого триггера, управляющий вход делителя соединен с входом I и через второй инвертор - с входом К второго триггера.

Фчг. i

, 1 #/ f V V,/ / «. 1 К К+1

LTU1J1ЛЛ ЛJ1J1-: :ЛJ1ГЬJU 1.Л ;.ЛЛГЬЛЛГШ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Импульсный генератор | 1981 |

|

SU993439A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Управляемый делитель частоты следования импульсов | 1984 |

|

SU1211878A1 |

Авторы

Даты

1993-02-07—Публикация

1990-08-27—Подача