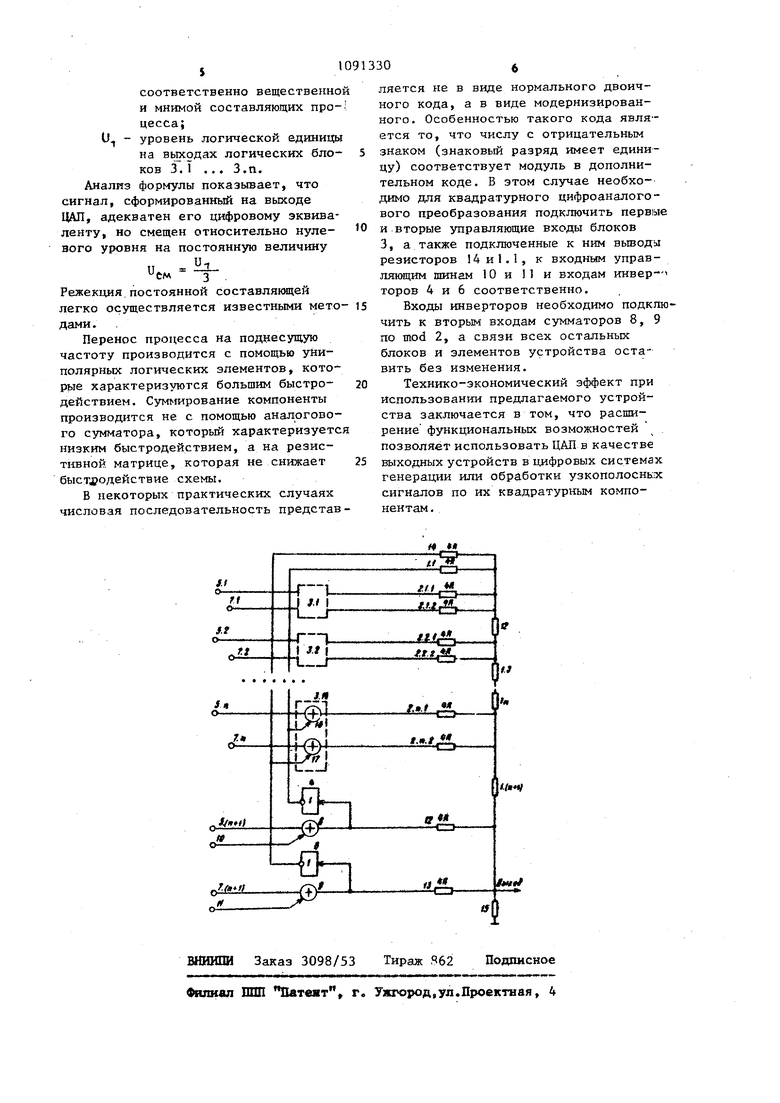

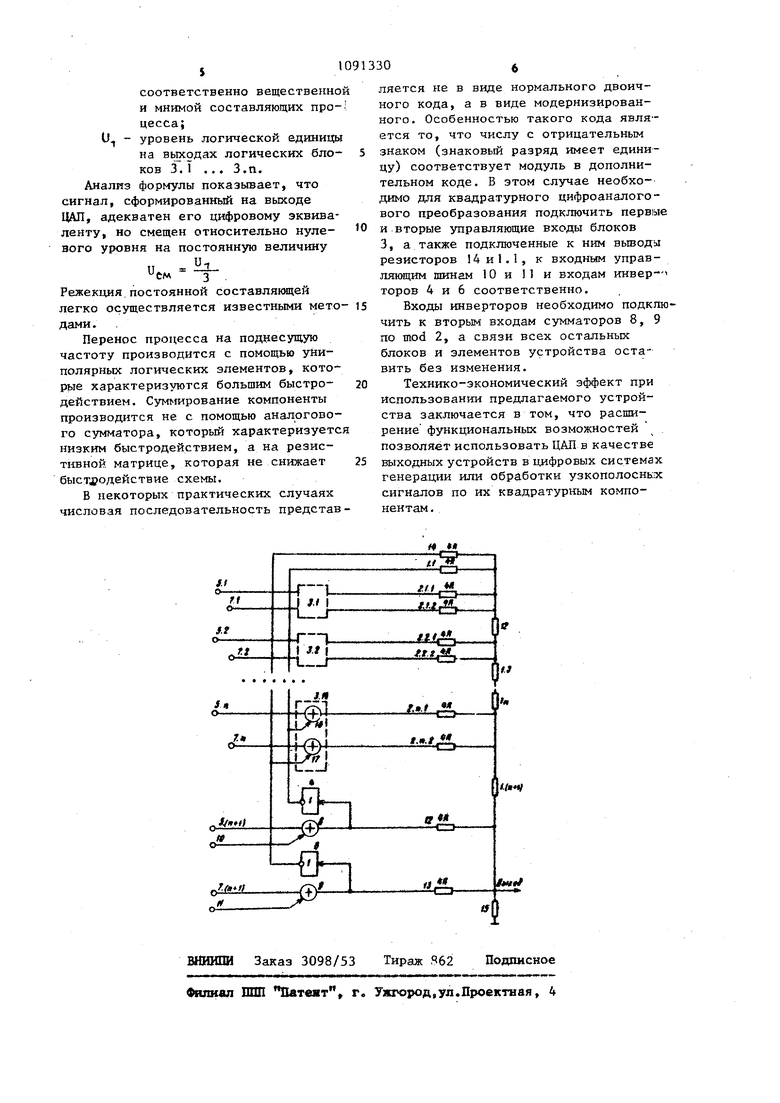

Изобретение относится к вычислительной технике и может быть использовано в устройствах, где необходимо квадратурное цифроаналоговое преобра зование сигналов, представленных в виде двух квадратурных компонент. Известен биполярный цифроаналоговый преобразователь, содержащий униполярный цифроаналоговый преобразова тель с матрицей R-2R, операционный усилитель с обратной связью, ключ управления знаком f Для обеспечения квадратурного пре образования сигналов необходимо параллельное включение двух известных преобразователей. Однако при этом усложняется устройство и, кроме того оно характеризуется низким быстродей ствием из-за наличия биполярных кпючей и операционного усилителя, имеющих значительную задержку передачи. Наиболее близким к предлагаемомуявляется цифроаналоговьм преобразова тель, содержащий цепь из п + 1 после довательио соединенных резисторов, к п узлам которой подключены первыми вьгаодами пары 2п резисторов, вторые вьгаоды которых подключены соответственно к первому и второму выходам п логических блоков, первые управляющие входы которых подключены к выходу первого инвертора, а первые информационные входы - к соответствуюпунм шинам первого преобразуемого кода кода t23. , Недостатком известного преобразов теля также является невозможность осуществления квадратурного цифроана логового преобразователя, что сущест венно расширило бы его функциональные возможности. Цель изобретенная - расширение функциональных возможностей. Поставленная цель достигается тем что в цифроаналоговьй преобразовател содержащий цепь из п+1 последователь но соединенных резисторов, к п узлам которой подключены первыми вьгаодами пары 2п резисторов, вторые выводы ко торых подключень соответственно к первому и второму выходам п логических блоков, первые управляющие входы которьк подключены к выходу первого инвертора, а первые кнформацио шые входы - к соответствующим шинам первого преобразуемого кода, введены второй инвертор, четыре дополнительных резистора, два суммятора по mod 2 первые входы которых подключены к соответствующим знаковым шинам преобразуемых кодов, вторые входы - соответственно к первой и второй управляюЕ5Им шинам, выходы соответственно к входам первого и второго инверторов и к первым выводам первого и второго дополнительных резисторов, вторые выводы которых подключены к выходной шине и к первому выводу цепи п + 1 последовательно соединенных резисторов, второй вьтод которой пбдключен.1 к первым управляющим входам п логических блоков, вторые информационные входы которых подключены к соответствующим второго преобразуемого кода, вторые управляющие входы - к выходу второго инвертора и к первому вьшоду третьего дополнительного резистора, второй вьтод которого подключен к узлу, ближайшему к второму вьшоду цепи из п + 1 последовательно соединенных резисторов, первый вьшод которой через четвертый дополнитель- ньй резистор подключен к общей шине. Кроме того, Кг-икдьш логический блок содержит два сумматора по mod 2, первые входы которых подключеьш соответственно к первому и второму информационным входам логического блока, вторые входы - соответственно к первому и второму управляющим входам лоп-гческого блока, выходы - соответственно к первому и второму выходам; логического блока. На чертеже изображена схема цифреаналогового преобразователя. Цифроаналоговый преобразователь (ЦАП) содержит цепь из п + I последовательно соединенных резисторов 1.1, 1,2;.,.1.i,.,.I.(п+1),к п узлам которой подключены первыми выводами пары 2п резисторов 2. 1,1, 2.1.2 ..,; Z.i.l, 2.i,2| 2.П.1, 2.n,2, вторые вьюоды которых подключены соответственно к первому и второму выходам п логических блоков 3.1, ..., Зп, первые управляющие входы которых подключены к выходу первого инвертора 4 , а первые информационные входы к соответствующим шинам 5,1,..,, 5Л5...5.П первого преобразуемого кода, вторые управляющие входы блоков 3, 1 ,,.. , ,3.п подключены к выходу второго инвертора 6, а вторые информационные входы - к соответствующим щинам 7„1,,.,,7.1,... 7.П второго преобразуемого кода, первьш и второй 310 сумматоры 8 и 9 по mod 2, первые входы которых подключены к соответствующим знаковым шинам 5.(п+1), 7.(п+1) двух преобразуемых кодов, вторые входы - соответственно к первой и второй управляющим шинам 10 и 11, выходы соответственно к входам первого и второго инверторов 4 и 6 и к первым выводам первого и второго дополнительных резисторов 12 и 13, вторые выводы которых подключены к выходной шине и к первому вьшоду цепи из п + 1 последовательно соединенных резисторов 1.1, 1.2,..., l.i, ... 1.(п+1),второй вывод кото рой подключен к выходу первого инвертора 4, третий дополнительный резистор 14, включенный мелсду выходо второго инвертора 6 и точкой соедине ния резисторов 1.1 и 1.2, четвертый дополнительный резистор 15, включенный между выходной и общей шинами. При этом каждый логический блок 3 содержит два сумматора 16 и 17 по mod 2, первые входы которых подключе ны соответственно к первому и втором информационным входам логического ч блока 3, вторые входы - соответствен но к первому и второму управляющим входам логического блока 3, выходы соответственно к первому и второму выходам логического блока 3. Индекс при позиции 2 состоит из номера пары резисторов и номера резистора в паре ЦАП работает следующим образом. Аналитический процесс х (t), состоящий из вещественной и мнимой компонент x(t) Retx(t)3 + jIm Cx(t)3 представлен в виде двух числовьпс последовательностей и поступает на . входные шины ЦАП 5.1, ... 5. () и 7.1, ... 7(п+1). Вещественная (t и мнимая Iratx(t)J компоненты процесс имеют п разрядов модуля и один (п+1) разряда знака, причем единице соотве ствует отрицательный знак функции.

Поднесущая, на которую необходимо произвести квадратурное преобразование, имеет вид двух знаковых ортогональных функций Sgn sin tOot и Sgn cos и представ пена в ЦАПе в виде

2- Sgn () +lj;

Sgn (cosOJ t) +l ; где Wjj - поднесущая частота.

a, Ь - отрицание a, b c(||,,l| - коэффицие гты m-ro разряда 0 Эти две функции поступают на шины 10 и 11, осуществляя на сумматорах 8 и 9 полярное перемножение знаков , аналитического процесса и поднесущей. Если логические состояния на входах сумматора 8 (9) совпадают, что соответствует несовпадению знаков,. то на его выходе имеем нуль, а на инвертора 4(6) - единицу. При этом на выходах сумматоров 16(17) имеем числа, инвертированные относительно входных шин 5.,,..,5.п (7,1, ...,7.п). Так как выход инвертора 4(6) эквивалентен весу первого разря да ЦАП, то на первых (вторых) выходах логических блоков 3.1, .,., З.п и инверторе 4(6) 1смеем число в дополнительном коде. Если логические состояния на входах сумматора 8(9) не совпадают, то на его выходе единицу, на выходе инвертора 4(6) - нуль, а на выходах логических блоков 3.1, ...,3.ппрямой код числа.. Таким образом осуществляется цифроаналоговое релейное перемножение вещественной (мнимой) компоненты со знаковой функцией поднесущей. Так как соответствующие разряды o6ei-tx компонент аналитического процесса абсолютно симметрично подключены к цепочке резисторов 1.1,.,., 1.(п+), 15, то очевидно, одновременно происходит и их равновесное сложение по выходу ЦАП. Если резистивная матрица вьшолнена таким образом, что резисторы 2.1.1, 2,1.2; ...; 2.i..l, 2.1.2; .,,;2,n.l, 2.n,2; 14; 1.1; 12; 13 равны 4R, резисторы 1.2, ... 1.(п+1) равны R, а резистор 15 равен 2R, а также, если считать внутренние сопротивления выходов логические блоков равными нулю и напряжение логического нуля Ц О то можно записать мгновен-: но значение напряжения на выходе ЦАП соответственно вещественно и мнимой составляющих npoцесса;0 - уровень логической единицы на вьпсодах логических блоков 3.1 ... З.п. Анализ формулы показывает, что сигнал, сформированный на выходе ЦДЛ, адекватен его цифровому эквиваленту, но смещен относительно нулевого уровня на постоянную величину -V Режекция.постоянной составлякщей легко осуществляется известными мето Перенос процесса на поднесущую частоту производится с помощью униполярных логических элементов, которые характеризуются большим быстродействием. Суммирование компоненты производится не с помощью аналогового сумматора, который характеризуетс низким быстродействием, а на резистивной матрице, которая не снижает бысТ|СоДбйствие схемы. В некоторых практических случаях числовая последовательность представ ляется не в виде нормального двоичного кода, а в виде модернизированного. Особенностью такого кода является то, что числу с отрицательным знаком (знаковый разряд имеет единицу) соответствует модуль в дополнительном коде. В этом случае необходимо для квадратурного цифроаналогового преобразования подключить первые и вторые управляющие входы блоков 3, а также подключенные к ним вьшоды резисторов 14 и 1.1, к входным управяянщим шинам 10 и 11 и входам инвер- торов 4 и 6 соответственно. Входы инверторов необходимо подключить к вторым входам сумматоров 8, 9 по mod 2, а связи всех остальных блоков и элементов устройства оставить без изменения. Технико-экономический эффект при использовании предлагаемого устройства заключается в том, что расширение функциональных возможностей позволяет использовать ЦАП в качестве выходных устройств в цифровых системах генерации или обработки узкополоснь:;х сигналов по их квадратурным компонентам. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального преобразования | 1978 |

|

SU734712A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Цифроаналоговый преобразователь с самоконтролем | 1986 |

|

SU1398100A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2433528C2 |

| Система для программного управления | 1989 |

|

SU1675847A1 |

| Цифроаналоговый преобразователь | 1989 |

|

SU1735999A1 |

| Устройство для цифроаналогового преобразования | 1985 |

|

SU1327294A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Устройство цифроаналогового преобразования | 1987 |

|

SU1524180A1 |

1. ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий цепь из п+1 последовательно соединенных резисторов, к п узлам которой подключены первыми выводами пары 2п резисторов, вторые выводы которых подключены соответственно к первому и второму выходам п логических блоков, первые управляющие входы которых-подключены к выходу первого инвертора, а первые информационные входы - к соответствующим шинам первого преобразуемого кода, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены второй инвертор, четьфе дополнительных резистора, два сумматора, по mod 2, первые входы которых подключены к соответствуюшд-iM знаковым шинам преобразуемых кодов, вторые входы - соответственно к первой и второй управ... / ляющим шинам, выходы - соответственно к входам первого и второго инверторов .и к первым выводам первого и второго дополнительных резисторов, вторые выводы которых подключены к вьпюдной щине и к первому выводу цепи п + 1 последовательно соединенных резисторов , второй вывод которой подключен к первым управляющим входам п логических блоков, вторые информационные входы которых подключены к соответствующим шинам второго преобразуемого кода, вторые управляющие входы - к В1з1ходу второго инвертора и к первому выводу третьего дополнительного рес & зистора, второй вьгоод которого подключен к узлу, ближайшему к второму ел вьшоду цепи из п + 1 последовательно соединенных резисторов, первый вывод которой через четвертьш дополнительный резистор подключен к общей шине. 2. Преобразователь по п.1, о т личающийся тем, что.каждый о со логический блок содержит два сумматора по mod 2, первые входы которых подключены соответственно к первому и второму информационным входам логиО5 со ческого блока, вторые входы - соответственно к первому и второму управо ляющим входам логического блока, выходы - соответственно к первому и второму выходам логического блока,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Биполярный цифро-аналоговый преобразователь | 1973 |

|

SU474933A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Генератор псевдослучайных узкополосных сигналов | 1980 |

|

SU955046A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-07—Публикация

1982-07-05—Подача