,113

i Изобретение относится к вычисли- 11ельной технике и цифровой измери- т ельной технике и может быть испольэовано для преобразования цифровых величин в аналоговые.

Цель изобретения - повышение достоверности и точности метрологического контроля.

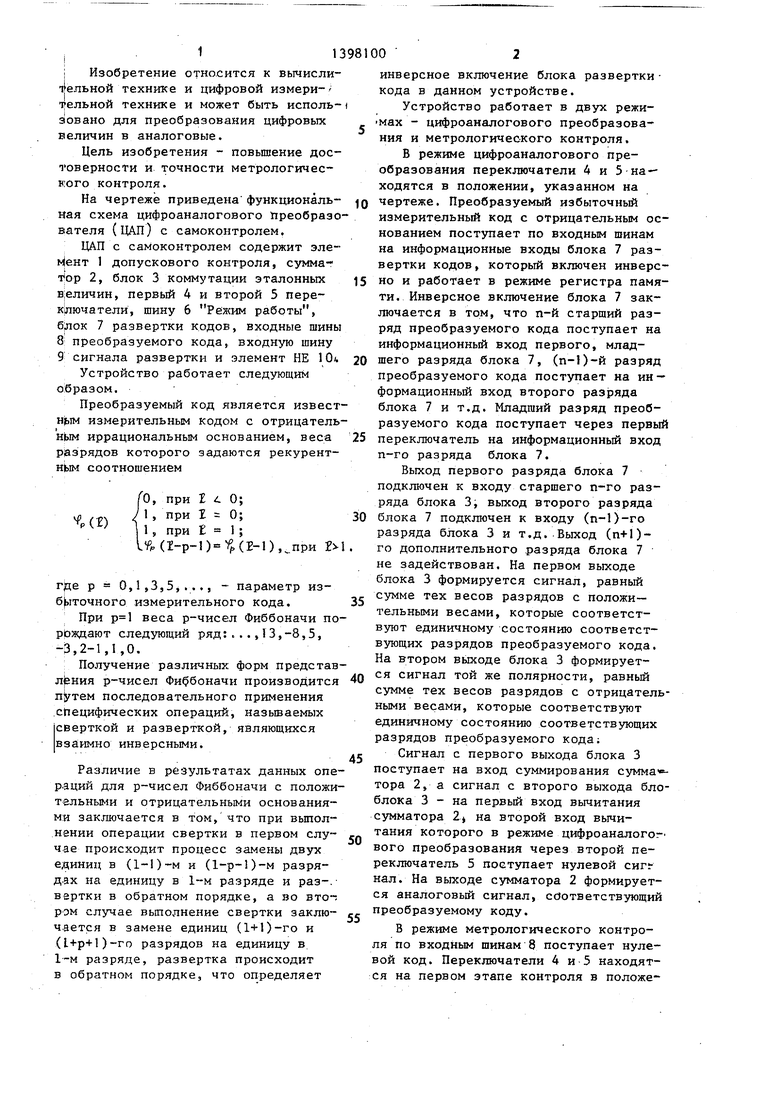

На чертеже приведена функциональ- ная схема цифроаналогового Преобразователя (ЦАП) с самоконтролем.

ЦАП с самоконтролем содержит эле- Цент 1 допускового контроля, сумма- т ор 2, блок 3 коммутации эталонных в;еличин, первый 4 и второй 5 переключатели, шину 6 Режим работы, блок 7 развертки кодов, входные шины 8; преобразуемого кода, входную шину 9 сигнала развертки и элемент НЕ 10/.

Устройство работает следующим образом.

Преобразуемый код является извест HjbiM измерительным кодом с отрицатель HbiM иррациональным основанием, веса разрядов которого задаются рекурент- HfciM соотношением

Го, при г. 0;

U) /.рч / 1 . при

Ч, при Е 1;

Lf I-p-0 f (Б-1),при f

где р 0,1,3,5,..., - параметр из- б| 1точного измерительного кода,

При веса р-чисел Фиббоначи порождают следуюш;ий ряд: . . ., 1 3,-8,5, -3,2-1,1,0.

Получение различных форм представ Л|ЕНИЯ р-чисел Фиббоначи производится п{утем последовательного применения .специфических операций, назьшаемых сверткой и разверткой, являющихся вза;имно инверсными.

Различие в результатах данных операций для р-чисел Фиббоначи с положительными и отрицательными основаниями заключается в том, что при выполнении операции свертки в первом слу- чае происходит процесс замены двух единиц в (l-I)-M и (1-р-)-м разрядах на единицу в 1-м разряде и раз-.- вертки в обратном порядке, а во ром случае выполнение свертки заклю- чается в замене единиц (1+1)-го и (1+р+1)-го разрядов на единицу в 1-м разряде, развертка происходит в обратном порядке, что определяет

0 2

инверсное включение блока развертки - кода в данном устройстве.

Устройство работает в двух режи- мах - цифроаналогового преобразования и метрологического контроля.

В режиме цифроаналогового преобразования переключатели 4 и 5 находятся в положении, указанном на чертеже. Преобразуемый избыточный измерительный код с отрицательным основанием поступает по входным шинам на информационные входы блока 7 развертки кодов, который включен инверсно и работает в режиме регистра памяти. Инверсное включение блока 1 заключается в том, что п-й старший разряд преобразуемого кода поступает на информационный вход первого, младшего разряда блока 7, (п-1)-й разряд преобразуемого кода поступает на ин- формационньй вход второго разряда блока 7 и т.д. Младший разряд преобразуемого кода поступает через первый переключатель на информационный вход п-го разряда блока 7.

Выход первого разряда блока 7 подключен к входу старшего п-го разряда блока 3; выход второго разряда блока 7 подключен к входу (n-l)-ro разряда блока 3 и т.д. Выход (п+1)- го дополнительного разряда блока 7 не задействован. На первом выходе блока 3 формируется сигнал, равный сумме тех весов разрядов с положительными весами, которые соответст- вутот единичному состоянию соответствующих разрядов преобразуемого кода. На втором выходе блока 3 формируется сигнал той же полярности, равный сумме тех весов разрядов с отрицательными весами, которые соответствуют единичному состоянию соответствующих разрядов преобразуемого кода;

Сигнал с первого выхода блока 3 поступает на вход суммирования сумма тора 2, а сигнал с второго выхода бло- блока 3 - на первый вход вычитания сумматора 2 на второй вход вычитания которого в режиме цифроаналогог- вого преобразования через второй переключатель 5 поступает нулевой нал. На выходе сумматора 2 формируется аналоговый сигнал, соответствующий преобразуемому коду.

В режиме метрологического контроля по входным шинам 6 поступает нулевой код. Переключатели 4 и 5 находятся на первом этапе контроля в положеНИИ, указанном на чертеже. На информационный вход (п+1)-го разряда блока 7 с выхода элемента НЕ 10 пос - тупает логическая единица. Сигнал развертки кода, поступающий по шине 9, приводит к появлению логических единиц на выходах п-гр и (n-l)-ro разрядов блока 7. которым вследствии инверсного включения соответствуют веса +1 и -1 и соответствующие величины сигналов на первом и втором выходах блока 3. На выходе сумматора 2 и на входе элемента I допускового контроля должен при этом сохраниться нулевой сигнал.

При отклонении реальных весов одного или обоих разрядов от эталонных величин, превышающем допустимое, а выходе элемента I допускового контроля появляется сигнал логической единицы. После подачи по шине 9 следующего импульса происходит развертка (n-l)-ro разряда и в этом состоянии еще раз проверяют нахождение выходного сигнала сумматора 2 в заанном диапазоне допустимых отклонений от нулевой величины и т.д.,11ока не будут вьшолнены все возможные операции развертки. Теоретически существуют отклонения весов разрядов, которые не будут обнаружены на первом этапе контроля, например, при выполнении условий /4 i/ /ii-f-l/ , где 1 - отклонение (погрешность) t-ro разряда, i-«-l - отклонение (i+l)-ro разряда.

Для обнаружения всех возможных отклонений разрядов необходимо, чтот бы каждый разряд участвовал, как минимум, в двзгх операциях развертки в качестве i-ro и (i+2)-ro разрядов. Это позволяет локализовать отклонив- шийся разряд с точностью до одного разряда, что повышает эффективность контроля всего устройства. Поэтому после первого этапа контроля, заключающегося в последовательной развертке кода числа, соответствующего нулевой выходной величине логические единицы только в (п+О-м не задействованном разряде блока 7),осуществляется второй этап контроля, иа котором по шине 6 подается сигнал, пег реводящий переключатели 4 и 5 в положение, противоположное указанному на чертеже. При этом на информационный вход п-го разряда блока 7 через переключатель 4 подается логическая

единица, а на остальных информационных входах блока 7, включая (п+1)-й, присутствует сигнал логического нуля.

Через переключатель 5 на второй вход вычитания сумматора 2 подается сигнал, равный весу младшего разряда. По сигналам развертки, поступающим по шине 9, осуществляется полная развертка исходного кода, соответствующего числу 1. При соответстг ВИИ весов разрядов их идеальным значением на выходе сумматора 2 и в этом

случае должен быть нулевой сигнал вследствие наличия указанного дополнительного сигнала на втором вычитающем входе сумматора 2.

Таким образом, при использовании

двух кодовых комбинаций, соответствующих числам О и 1, производится контроль линейности выходной характеристики ЦАП и локализация неверных весов разрядов. При этом одновременно возможен и контроль дрейфа нуля при подаче на вход ЦАП кодовой комбинации, эквивалентной числу О, на первом этапе контроля до по- дачи первой команды на развертку кода.

Формула изобретения Цифроаналоговый преобразователь с самоконтролем, содержащий блок развертки кодов, управляющий вход которого является входной шиной сигнала развертки, блок коммутации эталонных величин, первый выход эталонных ве- , личин нечетных, начиная с младшего,

разрядов которого подключен к входу суммирования сумматора, выход которого является выходной шиной, отличающийся тем, что, с целью повышения достоверности и

точности метрологического контроля, введены элемент допускового контроля, первый и второй переключатели, элемент НЕ, а блок развертки кодов выполнен (п-«-1)-разрядным, где п число разрядов преобразуемого кода, при этом информационный вход старшего (п+О-го разряда блока развертки кодой подключен к выходу инвертора, п-й информационный вход блока

развертки кодов объединен с входом инвертора и. подключен к выходу первого переключателя, первый информационный вход которого является шиной первого младшего разряда преобразуемого кода, второй информационный вход подключен к шине потенциала логической единицы, управляющий вход объединен с управляющим входом второго переключателя и является шиной Режим работы, информационные входы блока развертки кодов с первого по (п-Ц-й являются входными шинами преобразуемого кода соответственно с старшего разряда по второй, выходы блока развертки кодов с первого по п-й подключены к входам блока коммутации эталонных величин с п-го входа эталонной величины старшего разря,да по первый соответственно, выход эталонных величин четных разрядов подключен к первому входу вычитания сумматора, второй вход вычитания которого подключен .к выходу второго переключателя, первый информационный вход которого подключен к шине эталонного сигнала, соответствующего

весу младшего разряда, при этом выход сумматора подключен к первому входу элемента дрпускового контроля, второй вход которого подключен к шине нулевого потенциала, выход является контрольной выходной шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1287290A1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Цифро-аналоговый преобразователь с автоматической коррекцией нелинейности | 1980 |

|

SU930651A2 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1197079A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Цифро-аналоговый преобразователь с автоматической коррекцией нелинейности | 1980 |

|

SU951692A1 |

| Дифференциальный цифроаналоговый преобразователь | 1983 |

|

SU1138949A1 |

| Измеритель нелинейности цифро-аналоговых преобразователей | 1983 |

|

SU1112547A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифро-аналоговый преобразователь | 1977 |

|

SU809541A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-05-23—Публикация

1986-06-26—Подача