соединены соответственно с вторым и первым входами слагаемого-вычитаемого вычислительных ячеек в ( Е +К)-й строке и (Р +K+j-1)-M столбце (к 1, 2 , 3, .... .т , где п х ) , а первый и второй входы слагаемоговычитаемого вычислительных ячеек

в (6-+К)-и строке и.столбце, начиная с nej)Boro последовательно до (-f-K+j-l )-го5 соединены соответственно с вторым и первым выходами суммы вычислительной ячейки в строке и первом столбце.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

| Матричное вычислительное устройство тригонометрических функций | 1984 |

|

SU1238060A1 |

| Матричное вычислительное устройство | 1984 |

|

SU1247892A1 |

| Вычислительное устройство | 1983 |

|

SU1164701A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1984 |

|

SU1171787A1 |

| Устройство для извлечения квадратного корня | 1976 |

|

SU661550A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ м n-РАЗРЯДНЫХ ЧИСЕЛ | 2011 |

|

RU2475815C1 |

| Матричное устройство для деления | 1987 |

|

SU1462297A1 |

| Вычислительное устройство | 1983 |

|

SU1117635A1 |

МАТРИЧНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, состоящее из матрицы вычислительных ячеек, причем первый и второй управляющие входы вычислительной ячейки в i-й строке и j-м столбце (i 1, 2, ..., п, j 1, 2,...,п, где п - разрядность устройства) соединены соответственно с первым и вторым управляющими выходами вычислительной ячейки в этой же строке и (j-l)-M столбце, второй управляющий вход каждой вычислительной ячейки в первом столбце соединен через инвертор с первым управляющим входом этой же вычислительной ячейки и является входом первой группы входов матрицы, первый и второй входы переноса вычислительной ячейки в i-й строке и j-м столбце соединены соответственно с первым и вторым выходами переноса вычислительной ячейки в этой же строке и (j + 1)-м столбце, первый и второй входы переноса каждой вычислительной ячейки последнего столбца соединены соответственно с первым и вторым управляющими выходами этой же вычислительной ячейки, первый и второй входы слагаемого-вычитаемого вычислительной ячейки в i-й строке и j-м столбце соединены соответственно с вторым и первым выходами суммы вычислительной ячейки в (i-1)-й строке и (j-i+1)-M столбце, первый и второй входы слагаемого-вычитаемого вычислительных ячеек в i-й строке и j-м столбце, начиная с первого и последовательно до i-ro, соединены соответственно с вторым и первьм вмходами суммы вычислительной ячейки в (i-1)-й строi ке и первом столбце, первый и втоСЛ рой входы слагаемого вычислительной ячейки в i-й строке и j-м столбце соединены соответственно с первым и вторым выходами суммы вычислительной ячейки в (i-1)-й строке и этом же столбце, первый и второй входы слагаемого каждой вычислительной ячейки первой строки соединены соответсо го ственно с вторым и первым входами слагаемого-вычитаемого этой же вы4 числительной ячейки и являются вхоСО дами второй и третьей группы входов матрицы соответственно, первый и второй выходы суммы каждой вычислительной ячейки последней строки являются соответственно выходами первой и второй группы выходов матрицы, отличающееся тем, что, с целью повышения быстродействия, первой и второй выходы суммы вычислительной ячейки матрицы в И-и строке и j-м столбце, где равно наибольшему целому от половины номера последнего столбца.

f

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих процессорах и специализированных вычислительных устройствах.

Известны матричные вычислительные устройства, вычисляющие функции и cos Ч по методу цифра за цифрой и состоящие из двух матриц. Алгоритм вычисления функций sinLp и cos Ч , по методу цифра за цифрой имеет вид

Этап 1 e..a.-f. ,

2 х. X,- - 2- у

I f 1Г

У1Ч у,- + ,-2- х у - текущие координаты вектора;УГ, - конечные координаты

вектора,

п - число итераций. е условия: , (К

п-1

где

-2;

k-n

1-0

Матричные вычислительные устройства для вычисления функций sin и совЧ состоят из- двух матриц. Первая матрица вычислительных ячеек выполняет первый этап алгоритма и вырабатывает значения упраляющих сигна,лов S. . Поэтому ее целесообразно назвать управляющей. Вторая матрица вычислительных ячеек выполняет второй этап алгоритма т.е. вычисляет значергия х |, cos и у sin Ч , и ее целесообразно назвать вычис.шющей. Управляющая и вычисляюшля мат11ицм могут иметь

различные варианты исполнения, причем каждьй вариант у множества управляющих матриц может быть объединен с одним из вариантов из множества матриц, вычисляющих в матричное вычислительное устройство tl 1и С2. Недостатком этих устройств является их низкое быстродействие. Наиболее близким к изобретению по технической сущности является матричное вычислительное устройство С 21Основным недостатком этого матрИчного вычислительного устройства является малое быстродействие ее вы5 числяющей матрицы.

Цель изобре.тения - повышение быстродействия вычисляющей матрицы матричного вьтислительного устройства.

0 Поставленная цель достигается тем, что матричное вычислительное устройство, состоящее из матрицы вычислительных ячеек, причем первьй и второй управляюпще входы вычислительной ячейки в i-й строке и J-M столбце соединены соответственно с первым и вторым управляющими выходами вычислительной ячейки в этой же строке и (j-1)-M столбце,

0 второй управляющий вход каждой вычислительной ячейки в первом столбце соединен через инвертор с первым управляющим входом этой же вычислительной ячейки и является входом

5 первой группы входов матрицы, первый и второй входы переноса вычислительной ячейки в i-й строке и j-м столбце соединены соответственно с первым и вторым выходами перено0 са вычислительной ячейки в этой

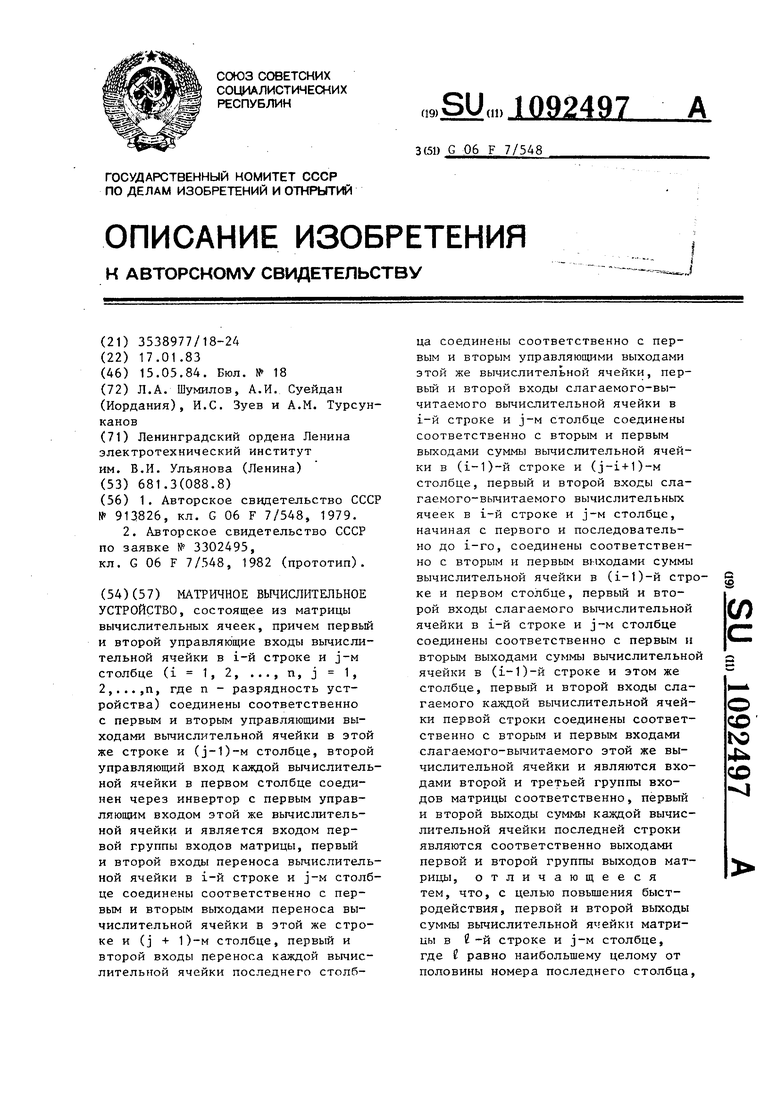

же строке и (j-f-l)-M столбце, первьш и второй входы переноса каждой вычислительной ячейки последнего столбца соединены соответственно с первым и вторым управляющими выходами этой же вычислительной ячейки, первый и второй входы слагаемого-вычитаемого вычислительной ячейки в i-й строке и J-M столбце соединены соответственно с вторым и первым выходами суммы вычислительной ячейки в (1-1)-й строке и (j-i+1)-M столбце, первый и второй входы слагаемого-вычитаемого вычислительных ячеек в i-й строке и J-M столбце, начиная с первого и последовательно до i-ro, соединены соответст венно с вторым и первым выходами суммы вычислительной ячейки в (1-1) строке и первом столбце, первый и второй входы слагаемого вычислитель ной ячейки в i-й строке и J-M столб це соединены соответственно с первым и вторым выходами суммы вычисли тельной ячейки в (i-1)-й строке и этом же столбце, первый и второй входы слагаемого каждой вычислитель ной ячейки первой строки соединены соответственно с вторым и первым входами слагаемого-вычитаемого этой же вычислительной ячейки и являются входами второй и третьей группы входов матрицы соответственно, первый и второй выходы суммы каждой вычислительной ячейки последней строки являются соответственно выхо дами первой и второй группы выходов матрицы, в вычислительной матрице первый и второй выходы суммы вычислительной ячейки в Р-и строке и J-M столбце, где К равно наибольшем целому от половины номера последнего столбца, соединены соответственн с вторым и первым входами слагаемого-вычитаемого вычислительных ячеек в (+К)-й строке и (E-i-K+j-O-M стол це, а первый и второй входы слагаемого-вычитаемого вычислительных ячеек в (в+К)-й строке и столбце, н чиная с первого последовательно до (S+K+j-1)-ro, соединены соответстёен но с вторым и первым выходами суммы вычислительной ячейки в -и строке и первом столбце. На фиг. 1 и 2 представлена структурная схема вьтисляющей матрищ,, на фиг-. 3 - структурная схема одного из вариантов выполнения вычислительной ячейки вычисляющей матрицы. Вычисляющая матрица (фиг. 1 и 2) содержит вычислительные ячейки 1, первую - третью группы входов 2, 3 74 и 4, выходы 5 и 6, первую и вторую группы выходов 7 и 8, Согласно варианту исполнения вычислительная ячейка 1 содержит два сумматора 9 и 10 по модулю два, два сумматора 11 и 12, входы 13-20, выходы 21-26. Вход 14 вычислительной ячейки 1 в i-й строке и первом столбце соединен через инвертор с входом 13 этой же вычислительной ячейки с входом группы входов 2 вычисляющей матрицы. Входы 17 и 18 каждой вычислительной ячейки первой строки соединены соответственно с входами 16 и 15 этой же вычислительной ячейки и соответственно с входами групп входов 3 и 4 вычисляющей матрицы, входы 13 и 14 вычислительной ячейки- в i-й строке и J-M столбце соединены соответственно с выходами 21 и 22 вычислительной ячейки в этой же строке и (j-l)-M столбце, входы 19 и 20 вычислительной ячейки в i-й строке и J-M столбце соединены соответственно с выходами 23 и 24 вычислительной ячейки в этой же строке и (j+1)-M столбце, входы 19 и 20 каждой вычислительной ячейки последнего столбца соединены соответственно с выходами 21 и 22 этой вычислительной ячейки, входы 15 и 16 вычислительной ячейки в i-й строке (i Е, 1 - наибольшее целое от половины номера последнего столбца) и J-M столбце соединены соответственно с выходами 26 и 25 вычислительной ячейки в (i-1)-й строке в (j-i+1)-M столбце, входы 15 и 16 вычислительных ячеек в i-й строке (i 1) и столбце, начиная с первого последовательно до i-ro, соединены соответственно с выходами 26 и 25 вычислительной ячейки в (i-1)-й строке и первом столбце, входы 17 и 18 вьиислительной ячейки в i-й строке и J-M столбце соединены соответственно с выходами 25 и 26 вычислительной ячейки в (i-1)-й строке и этом же столбце, выходы 25 и 26 вычислительной ячейки в Е-и строке и J-M столбце соединены соответственно с входами 16 и 15 вычислительных яче.ек в (+К)-й строке и (-i-K+j-1 )-м столбце, входы 15 и 16 вычислительных ячеек в (+к)-й строке и столбце, начиная с первого последовательно до (+K+j-1)-го, соединены соответственно с выходами 26 и 25 выЧислительной ячейки в В-и строке и первом столбце, выходы 25 и 26 каждой вычислительной ячейки после ней строки соединены соответственн с выходами 7 и 8 групп выходов выч ляющей матрицы. Вычисляющая матрица входит в со тав матричного вычислительного уст ройства, вычисляющего элементарные функции sin Ч и cos Ч по методу цифра за цифрой. Рекуррентные соотношения, описы вающие алгоритм цифра за цифрой для функций cosM следующ Этап 1 Этап 2 а число шагов итерации, X ., л . - текущие координаты вектора. - конечные координаты векто ра. Начальные условия 0 Ч i х -1/К-, УО О, где К - коэффициент деформации вектора, зависящий только от числа шагов итераций. Результаты вычислений У ( sinS Xf, cos Ч . Вычисляющая матрица выполняет второй этап алгоритма и работает с дующим образом. На входы 17 и 18 вычислительных ячеек 1 первой строки матрицы подаются соответственно значения начальных условий УО и X , на вход вычислительных ячеек 1 первого сто ца подаются управляющие сигналы Явьфабатываемые управляющей матрице матричного вычислительного устройства. Каждая строка вычислительных ячеек матрицы выполняет две операции алгебраического суммирования. Как видно из алгоритма вычисления, на выходах 25 и 26 вычислительных ячеек t-й строки получаются соответственно значения sin4 и с точностью до 2 (1). Следовательно, на выходах 25 и 26 вычислитель ных ячеек ITL строки получаются значения вз.пЧисозЧ с точностью до . Таким образом, после -й итерации (на выходах f-й строки) получаются первые С - правильные разряды значений вычисляег апс функций, где первый разряд знаковый. Поэтому будет справедливо соотношение (e + k--i; g+K-i е -(р4(С-1/ +K-i2 где ,К 1, 2, ... Исходя из этого, входы 15 и 16 вычислительной ячейки в i-й строке (i Z) и J-M столбце можно соединить соответственно с входами 15 и 16 вычислительной ячейки в f-и строке и (j-i+1)-M столбце, -а. входы 15 и 16 вычислительных ячеек в i-й строке () и J-M столбце (1 j i) соединить соответственно с выходами 26 и 25 вычислительной ячейки в f-и строке и первом столбце. С учетом того, что управляющие сигналы , ,7+, ...,fn-ii a вычисляющую матрицу прототипа приходят одновременно, временные затраты на вычисляющую матрицу сокращаются на величину t n-ei- - t,.(n-e)tg-(n-e)Y Чпни„(|м)(п-€К -{снн , где t- - время формирования суммы одноразрядным двоичным сумматором, t - время формирования переноса одноразрядным двоичным сумматоромj п - разрядность операндов, Очевидно, что временные затраты вычисления матричным вычислительньш устройством, состоящим из данной вычисляющей матриць и управляющей матритды матричного вычислительного устройства 2, сокращаются на величину At, равную л1.(|м|(п.(ми, , Матричное вычислительное устройство, содержащее предлагаемую вычисляющую матрицу, эффективнее всего реализовывать в виде БИС. В настоящее время в СССР нет БИС, вычисляющих функции COS4 . Поэтому в качестве базового объекта для определения эффективности изобретени взят CORDIC. Арифметический процес сор на кристалле (САР-кристалл), созданный фирмой NOSC (Naval Ocean Systems Centre) САР-кристалл вычис ляет функции вида sinS и cosf по методу цифра за цифрой (алгоритм Волдера). Время вычисления функций вида sinV и cosV С АР-к рис таллом для двадцатичетырехразрядных данных (п 24) составляет величину т f. -c.5i « чи C;/ CA6+ tj;,« CAB время сдвига на i разрядов вправо-, t с - время суммирования двух двадцатичетырехразрядных операторов. Матричное вычислительное устройство, состоящее из управляющей матрицы устройства Г2 и предлагаемой вычисляющей матрицы, вычисляет значения sin и cos за время,равное ; -еде А97 Тл1в 206 tn 3 - 5 где tp - время формирования сигнала переноса одноразрядным сумматором; tg - время формирования сигнала суммы одноразрядным сумматоромин инвертирования сигнала; время формирования суммы по по модулю два. Время tc равно t 23 t „ t... Значит ТСДР 71t 1633t +71t.. ,T4ri: fL.;:i Tat I- , Г с 5 ЧИТЬ. ЧТО ,,„ „. ЧИТЬ, что САР-кристалл вычисляет значения функций sinЧи созЧ не менее чем в.4 раза медленнее матричного вычислительного устройства, состоящего из предлагаемой вычисляющей матрицы и управляющей матрицы устройства С 23. Эффективность изобретения заключается в существенном повьшении скорости вычислений значений функций sinV и cos f

15

16

13

W

18

17

f

21

12

/

21

//

24

20

r

26

Y У

Фи1.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 913826, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3302495, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-15—Публикация

1983-01-17—Подача