Изобретение относится к области вычислительной техники и может быть использовано в быстродействующих процессорах и специализированных вычислительных устройствах.

Целью изобретения является повышение быстродействия устройства.

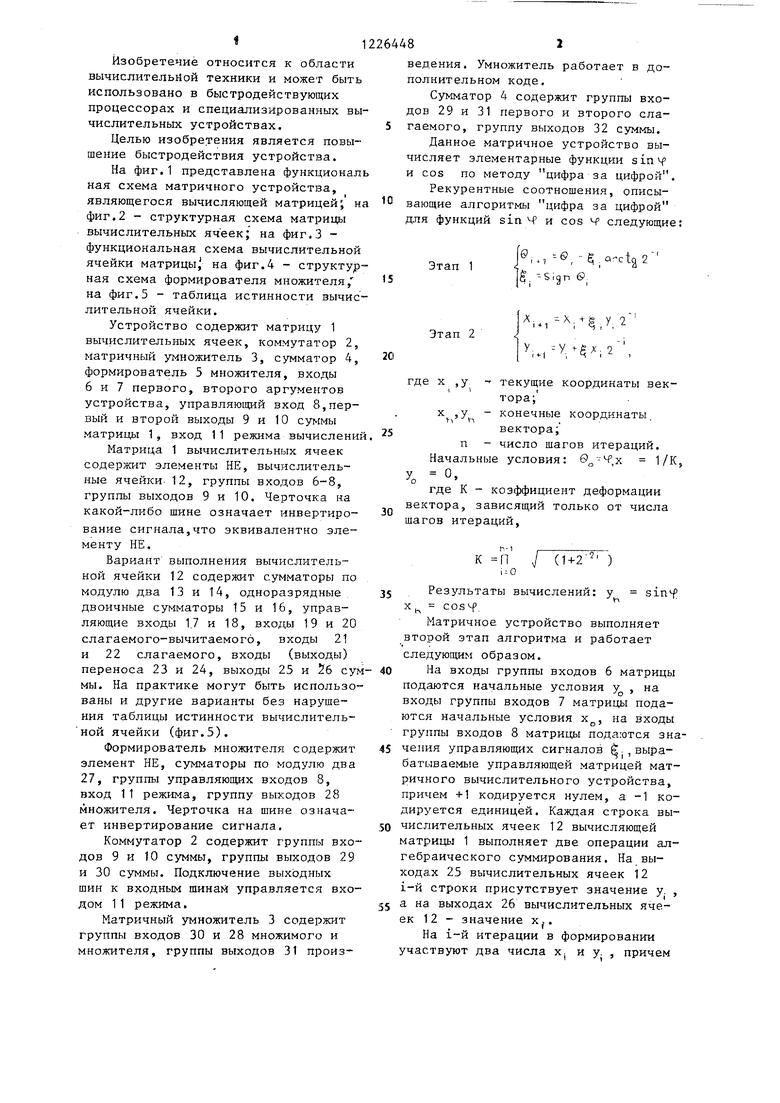

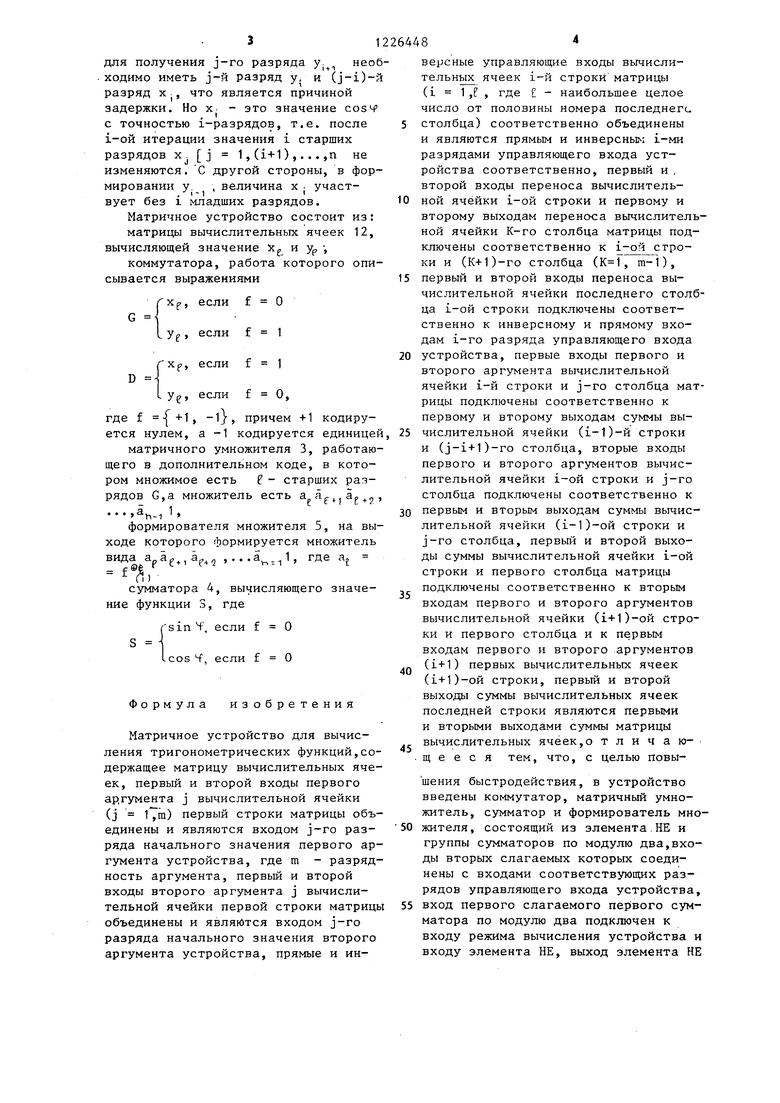

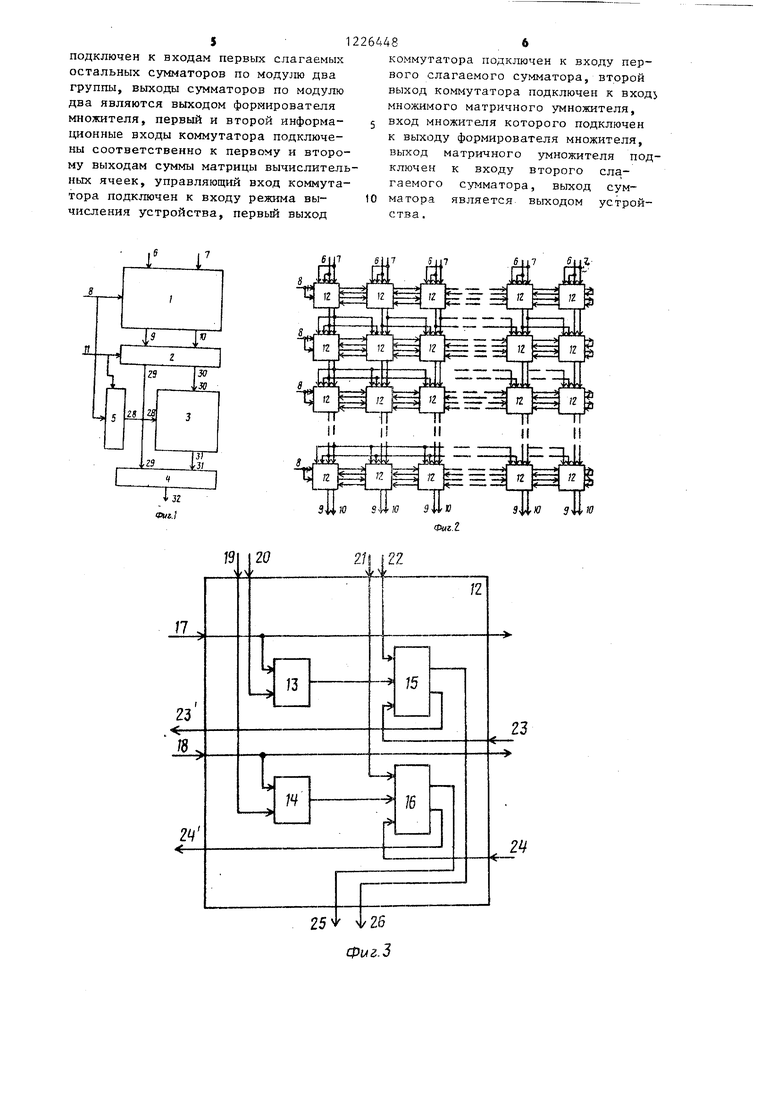

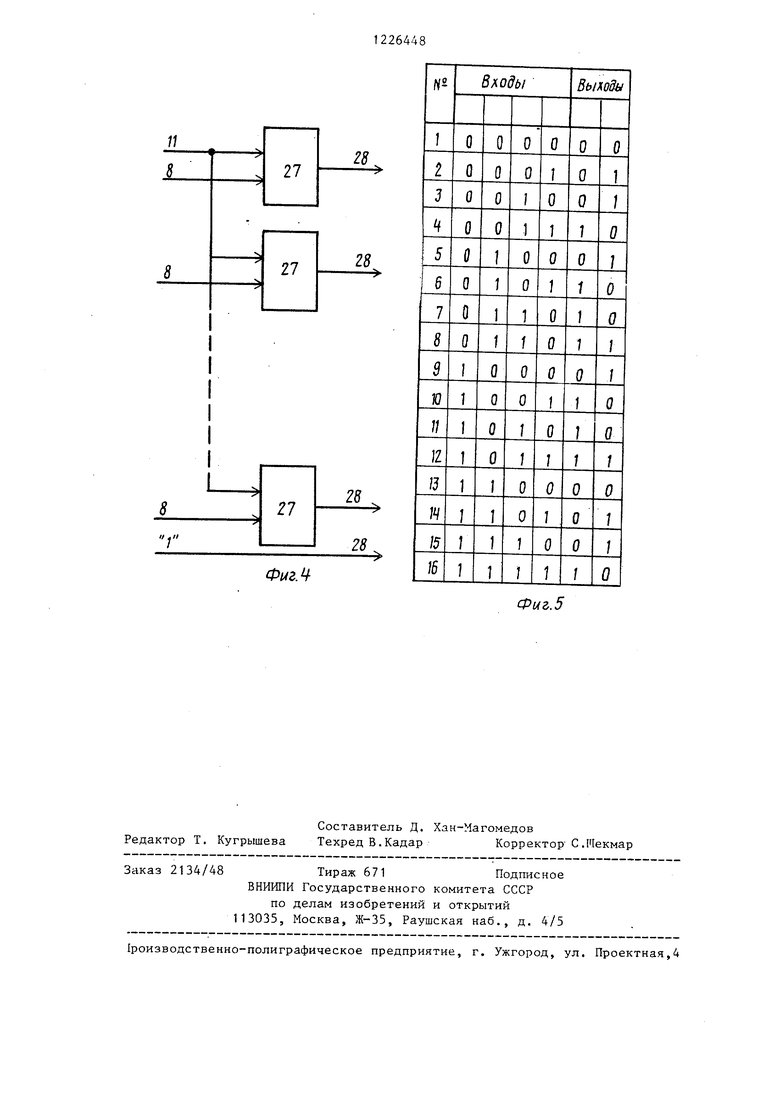

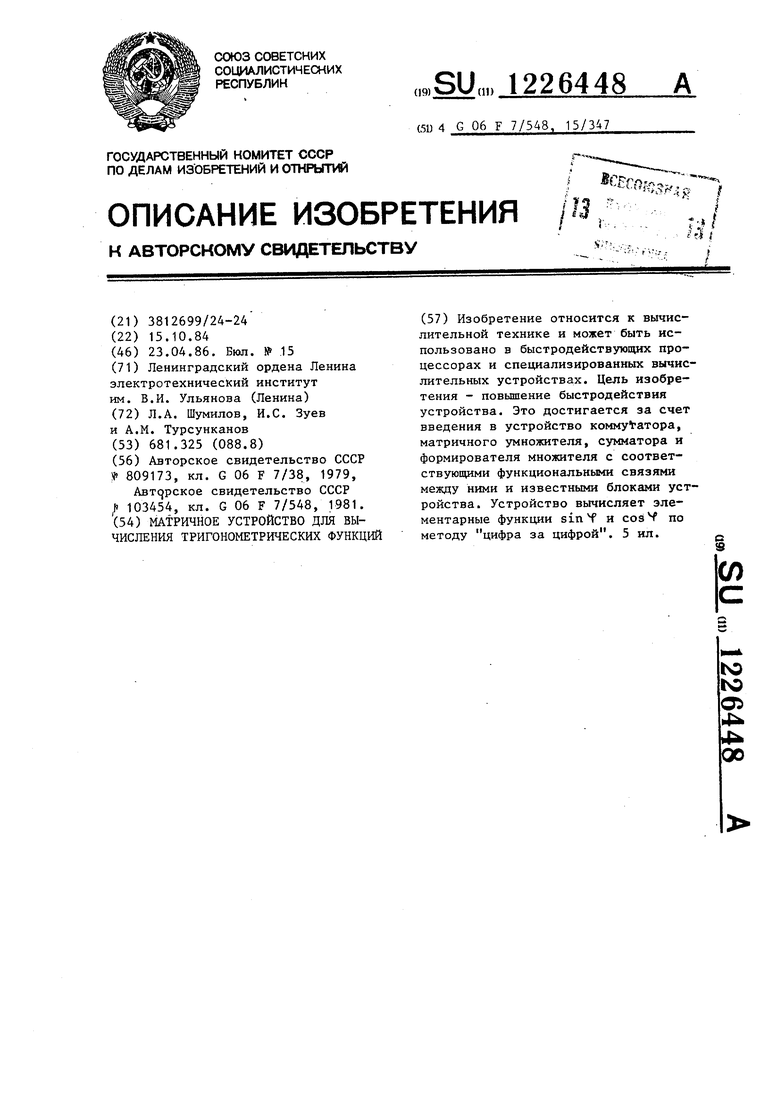

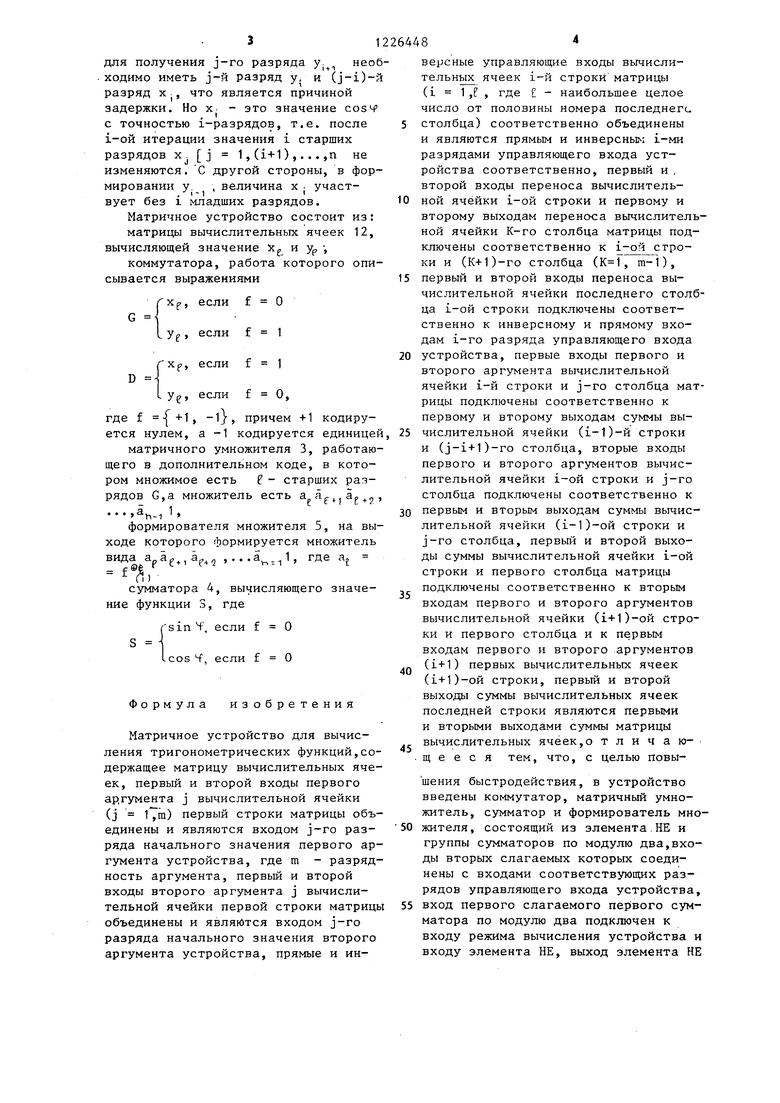

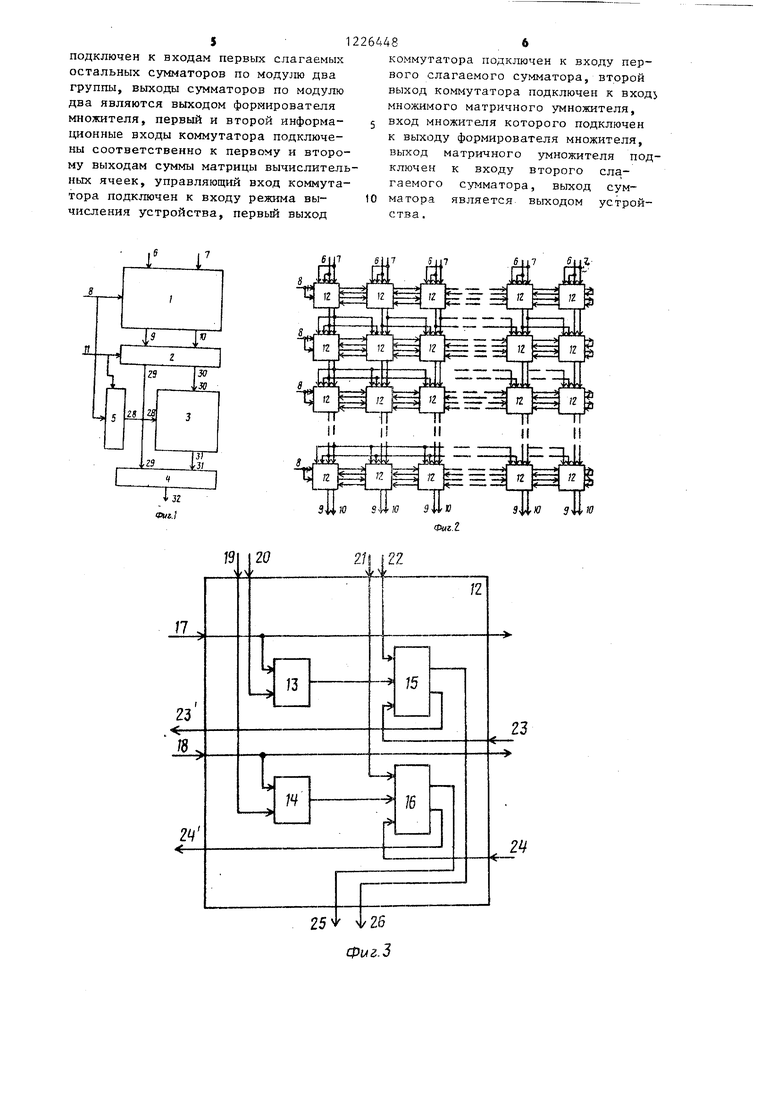

На фиг.1 представлена функциональ ная схема матричного устройства, являющегося вычисляющей матрицей; на фиг.2 - структурная схема матрицы вычислительных ячеек; на фиг.З - функциональная схема вычислительной ячейки матрицы, на фиг.4 - структурная схема формирователя множителя, на фиг.З - таблица истинности вычислительной ячейки.

Устройство содержит матрицу 1 вычислительных ячеек, коммутатор 2, матричный умножитель 3, сумматор 4, формирователь 5 множителя, входы 6 и 7 первого, второго аргументов устройства, управляю1ций вход 8,первый и второй выходы 9 и 10 суммы матрицы 1, вход 11 режима вычислений

Матрица 1 вычислительных ячеек содержит элементы НЕ, вычислительные ячейки- 12, группы входов 6-8, группы выходов 9 и 10. Черточка на какой-либо шине означает инвертирование сигнала,что эквивалентно элементу НЕ.

Вариант выполнения вычислительной ячейки 12 содержит сумматоры по модулю два 13 и 14, одноразрядные, двоичные сумматоры 15 и 16, управляющие входы 1.7 и 18, входы 19 и 20 слагаемого-вычитаемого, входы 21 и 22 слагаемого, входы (выходы) переноса 23 и 24, выходы 25 и 5б суммы. На практике могут быть использованы и другие варианты без нарушения таблицы истинности вычислитель- ной ячейки (фиг.З).

Формирователь множителя содержит элемент НЕ, сумматоры по модулю два 27, группы управляющих входов В, вход 11 режима, группу выходов 28 множителя. Черточка на шине означает инвертирование сигнала.

Коммутатор 2 содержит группы входов 9 и 10 суммы, группы выходов 29 и 30 суммы. Подключение выходных шин к входным шинам управляется входом 11 режима.

Матричный умножитель 3 содержит группы входов 30 и 28 множимого и множителя, группы выходов 31 произ

ведения. Умножитель работает в дополнительном коде.

Сумматор 4 содержит группы входов 29 и 31 первого и второго слагаемого, группу выходов 32 суммы.

Данное матричное устройство вычисляет элементарные функции sin -p и cos по методу цифра за цифрой.

Рекурентные соотношения, описывающие алгоритмы цифра за цифрой для функций sin Ч и cos Ч следующие:

Этап 1

Этап 2

,..

V.., -У.

у 2

X; 2

где X

УИ

п текущие координаты вектора;

- конечные координаты, вектора;

число шагов итераций. Начальные условия: 1/К,

УО 0.

где К - коэффициент деформации

вектора, зависящий только от числа шагов итераций,

h-l

п

i 0

У ( )

Результаты вычислений: у sin f X .

Матричное устройство выполняет второй этап алгоритма и работает следующим образом.

На входы группы входов 6 матрицы подаются начальные условия у , на входы группы входов 7 матрицы подаются начальные условия х, на входы группы входов 8 матрицы подаются значения управляюш;их сигналов , выра- батыва гмые управляюш;ей матрицей матричного вычислительного устройства, причем +1 кодируется нулем, а -1 кодируется единицей. Каждая строка вычислительных ячеек 12 вычисляющей матрицы 1 выполняет две операции алгебраического суммирования. На выходах 23 вычислительных ячеек 12 i-й строки присутствует значение у. , а на выходах 26 вычислительных ячеек 12 - значение х.

На i-й итерации в формировании участвуют два числа х и у. , причем

для получения j-ro разряда у. необходимо иметь j-й разряд у, и (j-i)-ft разряд X j, что является причиной задержки. Но х- - это значение cos Ч с точностью i-разрядов, т.е. после i-ой итерации значения i старших разрядов X. J 1,(i+1),...,n не изменяются. С другой стороны, в формировании у. , величина х j участвует без i младших разрядов.

Матричное устройство состоит из: матрицы вычислительных ячеек 12, вычисляющей значение Х и ур ,

коммутатора, работа которого описывается выражениями

Хр, если f О

у, если f 1

Хр, если f 1

L ур, если f О,

где f f+1 l} причем +1 кодируется нулем, а -1 кодируется единицей матричного умножителя 3, работающего в дополнительном коде, в котором множимое есть f- старших разрядов G,a множитель есть а ,,,

h-i

формирователя множителя 5, на выходе которого формируется множитель вида ,..., где а

f®()

сумматора 4, вычисляющего значение функции 3, где

sin Ч если f О

S

сов Ч, если f О

Формула изобретения

Матричное устройство для вычисления тригонометрических функций,содержащее матрицу вычислительных ячеек, первый и второй входы первого аргумента j вычислительной ячейки (j l7ra) первый строки матрицы объединены и являются входом j-ro разряда начального значения первого аргумента устройства, где m - разрядность аргумента, первый и второй входы второго аргумента j вычислительной ячейки первой строки матрицы объединены и являйтся входом j-ro разряда начального значения второго аргумента устройства, прямые и ин

5

0

версные управляющие входы вычислительных ячеек i-й строки матрицы (i 1 ,f , где Е - наибольшее целое число от половины номера последнего столбца) соответственно объединены и являются прямым и инверсным i-ми разрядами управляющего входа устройства соответственно, первый и , второй входы переноса вычислительной ячейки i-ой строки и первому и второму выходам переноса вычислительной ячейки К-го столбца матрицы подключены соответственно к строки и (К+1)-го столбца (, т-1), первый и второй входы переноса вычислительной ячейки последнего столбца i-ой строки подключены соответственно к инверсному и прямому входам i-ro разряда управляющего входа устройства, первые входы первого и второго аргумента вычислительной ячейки i-й строки и j-ro столбца матрицы подключены соответственно к первому и второму выходам суммы вы- 5 числительной ячейки (i-1)-й строки и (j-i+1)-ro столбца, вторые входы первого и второго аргументов вычислительной ячейки i-ой строки и j-ro столбца подключены соответственно к первым и вторым выходам суммы вычислительной ячейки (i-l)-oй строки и j-ro столбца, первый и второй выходы суммы вычислительной ячейки i-ой строки и первого столбца матрицы подключены соответственно к вторым входам первого и второго аргументов вычислительной ячейки (i+1)-oй строки и первого столбца и к первым входам первого и второго аргументов (i+1) первых вычислительных ячеек {i+1)-oй строки, первый и второй выходы суммы вычислительных ячеек последней строки являются первыми и вторыми выходами суммы матрицы вычислительных ячеек,о т л и ч а ю- щ е е с я тем, что, с целью повы0

5

0

5

шения быстродействия, в устройство введены коммутатор, матричный умножитель, сумматор и формирователь множителя, состоящий из элемента.НЕ и группы сумматоров по модулю два,входы вторых слагаемых которых соединены с входами соответствующих разрядов управляющего входа устройства,

вход первого слагаемого первого сумматора по модулю два подключен к входу режима вычисления устройства и входу элемента НЕ, выход элемента НЕ

$ 1

подключен к входам первых слагаемых остальных сумматоров по модулю два группы, выходы сумматоров по модулю два являются выходом формирователя множителя, первый и второй информационные входы коммутатора подключены соответственно к первому и второму выходам суммы матрицы вычислитель ных ячеек, управляющий вход коммутатора подключен к входу режима вычисления устройства, первый выход

264486

коммутатора подключен к входу первого слагаемого сумматора, второй выход коммутатора подключен к вход множимого матричного умножителя, 5 вход множителя которого подключен к выходу формирователя множителя, выход матричного умножителя подключен к входу второго слагаемого сумматора, выход сум- 10 матора является выходом устройства .

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1983 |

|

SU1117635A1 |

| Вычислительное устройство | 1987 |

|

SU1509872A1 |

| Устройство для умножения | 1989 |

|

SU1697078A1 |

| Матричный умножитель | 1988 |

|

SU1615704A1 |

| Матричное вычислительное устройство тригонометрических функций | 1984 |

|

SU1238060A1 |

| Вычислительное устройство | 1983 |

|

SU1164701A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1024910A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1092497A1 |

| Вычислительное устройство | 1981 |

|

SU1032454A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих процессорах и специализированных вычислительных устройствах. Цель изобретения - повышение быстродействия устройства. Это достигается за счет введения в устройство коммутатора, матричного умножителя, сумматора и формирователя множителя с соответ- ствуюпщми функциональными связями между ними и известными блоками устройства. Устройство вычисляет элементарные функции sinf и cosN по методу цифра за цифрой. 5 ил. IND ю 05 Oiiii 00

Z9

30 130

LZ9

1з;

ч

I 3Z Фиг.

фиг.З

Ф14гМ

Фиг. 5

| Матричное вычислительное устройство | 1979 |

|

SU809173A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-23—Публикация

1984-10-15—Подача