И четвертым входом седьмого элемента И вычислительной ячейки матрицы, тре тий вход шестого элемента И которой Соединен с вторым входом второго, восьмого и девятого элементов И и че вертым входом пятого элемента И вычислительной ячейки матрицы, третий вход девятого элемента И которой сое динен с третьим входом четвертого элемента И вьмислительной ячейки мат рицы, третий вход восьмого элемента И которой соединен с третьим входом третьего элемента И вычислительной, ячейки матрицы, выходы первого, второго и шестого элементов И которой соединены соответственно с первым, вторым и третьим входом первого элемента ИЛИ вычислительной ячейки матрицы, выходы третьего, четвертого, пятого, седьмого, восьмого и девятого элементов И которой соединены соответственно с первым, вторым, третьим, четвертым, пятым и шестым входом второго элемента ИЛИ вычислительной ячейки.матрицы, входы первых элементов НЕ вычислительных ячеек матриць: п-го столбца i-й строки соединены с шиной логического О устройства, вход первого элемента НЕ вычислительной ячейки s-й строки (,...,m) и г-го столбца (,..., п-1) матрицы соединены с выходом вто рого элемента ИЛИ вычислительных яче ек (8-1)-й строки и (г+1)-го столбца матрицы, выход первого элемента ИЛИ вычислительной ячейки i-й строки И 1-го столбца (,...,п)матрицы со динен с входом второго элемента НЕ вычислительной ячейки t-й строки и (6+1)-го столбтщ матрицы, выход элемента И уэла памяти вычислительной ячейки к-й строки (,...,т-1) и 1г6 столбца матрицы соединен с входом четвертого элемента НЕ вьиислительно ячейки (к+1)-й строки и 1-го стобца матрицы, выходы первых и вторых элементов ИЛИ вычислительных ячеек т-й строки q-ro столбца (,...,in) и первого элемента РШИ вычислительной ячейки первого столбца ш-й строки матрицы соединены с соответствующими весовыми входами параллель ного румматора, п выходов которого соединены с п старших разря дов устройства, m выходов младших разрядов устройства соединены соотве ;ственно с выходами элементов ИЛИ т-й г-руппы узлов памяти, вторые входы вторых элементов И которой соединены с (ш+1)-м тактируиицим входом устройства, первые входы элементов И (i-l)-x узлов памяти j-й группы соединены соответственно с выходами элементов ИЛИ (3-1)-й группы, первый вход элемента И j-ro узла памяти j-й группы соединен с выходом второго элемента ИЛИ вычислительной ячейки j-й строки первого столбца матрицы вычислительных ячеек, отличающеес я тем, что, с целью увеличения быстродействия, в каждую вычислительную ячейку устройства дополнительно введены десятый и одиннадцатый элементы И, пятый-элемент НЕ и элемент задержки, в каждый узел памяти введен элемент задержки, причем первьй вход десятого элемента И вьиислительной ячейки соединен с выходом первого элемента ИЛИ вычислительной ячейки матрицы, второй вход которого соединен с соответствующим тактовым входом устройства и первым входом одиннадцатого элемента И вычислительной ячейки матрицы, второй вход которого соединен с выходом второго элемента ИЛИ вычислительной ячейки мат- . рицы, пятый вход пятого элемента И которой соединен с пятым входом седьмого элемента И, четвертыми входами первого, третьего, четвертого, шестого, восьмого и девятого элементов И, с третьим входом второго элемента И и выходом пятого элемента НЕ вычислительной ячейки матриць, вход пятого элемента НЕ которой соединен с выходом элемента задержки вычислительной ячейки матрицы, вход которого соединен с вторым входом третьего элемента И и входом элемента задержки узла памяти вычислительной ячейки матрицы, вькод которого соединен с входом элемента НЕ узла памяти вычислительной ячейки матрицы, вход первого элемента НЕ вычислительной ячейки соединен с первым входом первого элемента И вьщислительной ячей си матрицы, выход первого элемента НЕ которой соединен с первьш входом восьмого элемента И, выход второго элемента НЕ вычислительной ячейки соединен с третьим входом седьмого элемента И, вход второго элемента НЕ вьмислительной ячейки соединен с четвертым входом пятого элемента И, второй вход которого соединен с входом третьего элемента НЕ вычислительной ячейки матрицы, выход которого соеданен с третьим входом восьмого элемента И, вход четвертого элемента НЕ вычислительной ячейки соединен с третьим входом первого элемента И вычислительной ячейки матрицы, выход четвертого элемента НЕ которой соединен с третьим входом девятого элемента И, вход элемента задержки каждого узла памяти соединен с вторым входом третьего элемента И узла памяти, выход элемента задержки которого соединен с входом элемента НЕ узла памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1987 |

|

SU1509872A1 |

| Конвейерное устройство для умножения шестнадцатиразрядных чисел | 1984 |

|

SU1291970A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Умножитель разреженных полиномов | 1989 |

|

SU1649564A1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Устройство для умножения | 1989 |

|

SU1697078A1 |

| Вычислительное устройство | 1989 |

|

SU1697077A2 |

| Устройство для умножения | 1988 |

|

SU1603379A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

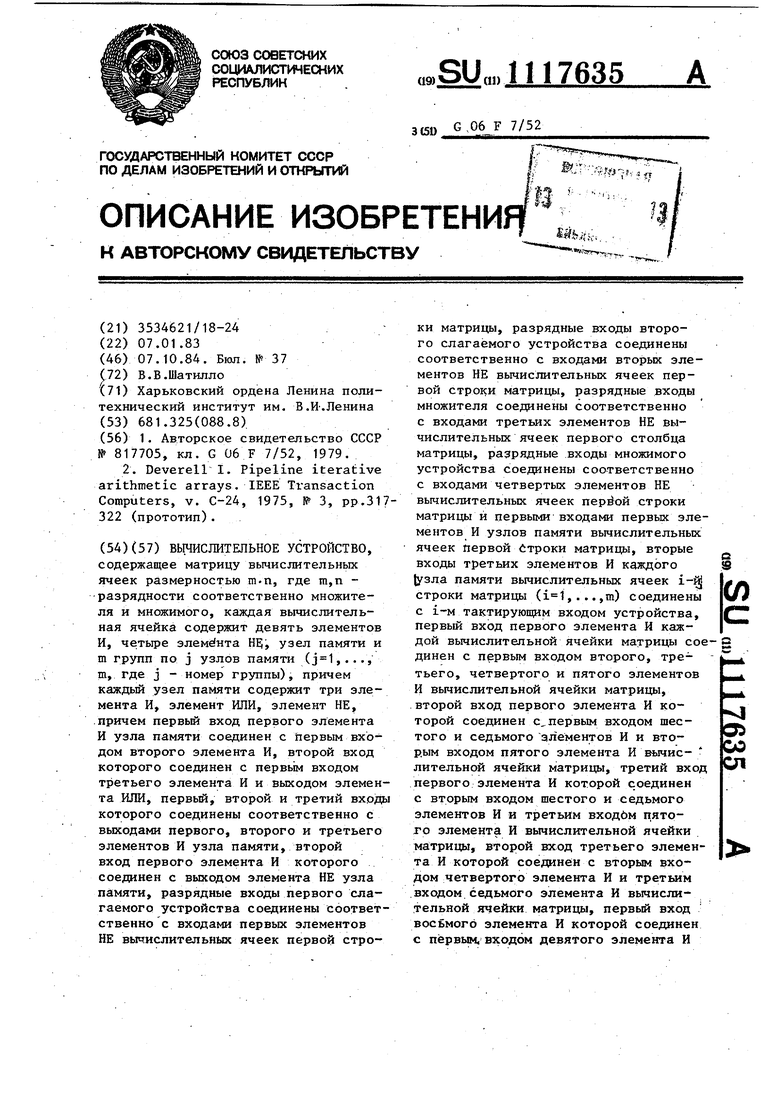

ВЬГЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее матрицу вычислительных ячеек размерностью m.n, где m,n разрядности соответственно множителя и множимого, каждая вычислительная ячейка содержит девять элементов И, четыре элемента HEjj узел памяти и m групп по j узлов памяти (,..., m, где j - номер группы), причем каждьй узел памяти содержит три элемента И, элемент ИЛИ, элемент НЕ, причем первый вход первого элемента И узла памяти соединен с первым входом второго элемента И, второй вход которого соединен с первьгм входом третьего элемента И и выходом элемента ИЛИ, первый, второй и третий входа которого соединены соответственно с выходами первого, второго и третьего элементов И узла памяти, второй вход первого элемента И которого соединен с выходом элемента НЕ узла памяти, разрядные входы первого слагаемого устройства соединены соответственно с входами первых элементов НЕ вычислительных ячеек первой строки матрицы, разрядные входы второго слагаемого устройства соединены соответственно с входами вторых элементов НЕ вычислительных ячеек первой строки матрицы, разрядные входы множителя соединены соответственно с входами третьих элементов НЕ вычислительных ячеек первого столбца матрицы, разрядные входы множимого устройства соединены соответственно с входами четвертых элементов НЕ вычислительных ячеек строки матрицы и первыми входами первых элементов И узлов памяти вычислительных ячеек первой Строки матрицы, вторые § входы третьих элементов И каждого (узла памяти вычислительных ячеек i(П строки матрицы (, ...,т) соединены с i-M тактирующим входом устройства, первый вход первого элемента И каждой вычислительной ячейки матрицы сое - а динен с первым входом второго, третьего, четвертого и пятого элементов И вычислительной ячейки матрицы, второй вход первого элемента И ко торой соединен с,первым входом шеса того и седьмого элементов И и вто00 рым входом пятого элемента И вычиссд лительной ячейки матрицы, третий вход первого элемента И которой соединен с вторым входом шестого и седьмого элементов И и третьим входбм пятого элемента И вычислительной ячейки матрицы, второй вход TpeTisero элемента И которой соединен с вторым входом четвертого элемента И и третьим входом седьмого элемента И вычислительной ячейки матрицы, первый вход восьмого элемента И которой соединен с первым, входбм девятого элемента И

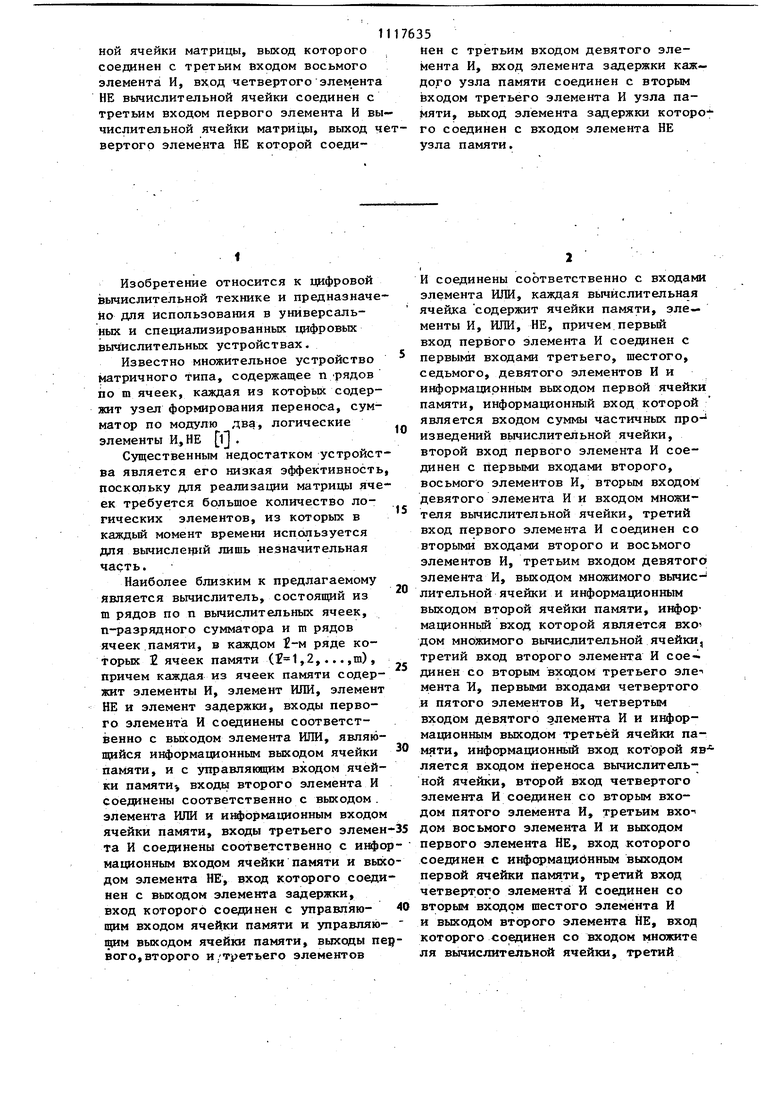

Изобретение относится к цифровой вычислительной технике и предназначе но для использования в универсальных и специализированных цифровых вычислительных устройствах. Известно множительное устройство матричного типа, содержащее п /рядов по m ячеек, каждая из которых содержит узел формирования переноса, сумматор по модулю два, логические элементы И, НЕ l . Существенным недостатком устройст ва является его низкая эффективность поскольку для реализации матрицы яче ек требуется большое количество логических элементов, из которых в каждый момент времени используется для вьмислен11й лишь незначительная часть. Наиболее близким к предлагаемому является вычислитель, состоящий из m рядов по п вычислительных ячеек, п-разрядного сумматора и m рядов ячеек.памяти, в каждом J-м ряде которых 2 ячеек памяти (,2,...,т), причем каждая из ячеек памяти содержит элементы И, элемент ИЛИ, элемент НЕ и элемент задержки, входы первого элeмeнтia И соединены соответственно с выходом элемента ИЛИ, являющийся информационным выходом ячейки памяти, и с управляющим входом ячейки памяти-, входы второго элемента И соединены соответственно с выходом . элемента ИЛИ и информационным входом ячейки памяти, входы третьего элемен та И соединены соответственно с инфо мационным входом ячейки памяти и вых дом элемента НЕ, вход которого соеди нен с выходом элемента задержки, вход которого соединен с управляющим входом ячей.ки памяти и управляюnpiM выходом ячейки памяти, выходы пе вого, второго и.Третьего элементов И соединены соответственно с входами элемента ИЛИ, каждая вычислительная ячейка содержит ячейки памяти, элементы И, ИЛИ, НЕ, причем первый вход первого элемента И соединен с первыми входами третьего, шестого, седьмого, девятого элементов И и информационным выходом первой ячейки памяти, информационный вход которой является входом суммы частичных про- изведений вычислительной ячейки, второй вход первого элемента И соединен с первыми входами второго, восьмого элементов И, вторым входом девятого элемента И и входом множителя вычислительной ячейки, третий вход первого элемента И соединен со вторыми входами второго и восьмого элементов И, третьим входом девятого элемента И, выходом множимого вычислительной ячейки и информационным выходом второй ячейки памяти, информационный вход которой является вхо дом множимого вычислительной ячейки, третий вход второго элемента И соединен со вторым входом третьего элемента И, первыми входами четвертого и пятого элементов И, четвертым входом девятого элемента И и информационным выходом третьей ячейки памяти, информационный вход которой является входом переноса вычислительной ячейки, второй вход четвертого элемента И соединен со вторым входом пятого элемента И, третьим входом восьмого элемента И и выходом первого элемента НЕ, вход которого соединен с инф(}рмащ1днным выходом первой ячейки памяти, третий вход четвертого элемента И соединен со вторым входрм шестого элемента И и выходом втсфого элемента НЕ, вход которого соединен со входом множите ля вычислительной ячейки, третий

вход пятого элемента И соединен со вторым входом седьмого элемента И и выходом третьего элемента НЕ, вход которого coejcpHeH с информационным выходом второй ячейки памяти, третий вход шестого элемента И соединен с третьим входом седьмого элемента И, четвертым входом седьмого элемента И, четвертым входом восьмого элемента И и выходом четвертого элемента НЕ, вход которого соединен с информационным выходом третьей ячейки памяти, выходы первого, второго, третьего элементов И соединены соответственно со входами первого элемента ИЛИ, выход которого является выходом переноса вычислительной Ячейки, выходы четвертого, пятого, шестого, седьмого, восьмого и девятого элементов И соединены соответствённо со входами второго элемента ИЛИ, выход которого является выходом суммы частичных проиэведений, управлякшще входы первой, второй и третьей ячеек памяти подключены к уп равляклцему входу вычислительной ячейки, управляющий выход второй ячейки памяти подключен к управляющему выходу вычислительной ячейки вход множителя вычислительной ячейки соединен с выходом множителя вычислительной ячейки, входы множимого входы суммы частичных произведений, входы переноса вычислительных ячеек первого ряда, а также входы множителя первых вычислительных ячеек всех рядов, являются информационными входами .матричного умножителя, выход множителя и управлякнций выход к-и вычислительной ячейки каждого ряда сое динены соответственно со входом множителя и управляющим входом (к+1)-й вычислительной ячейки того же ряда (к-1,2,.,.,п-1), вход суммы частич:.ных произведений к-й вычислительной ячейки каждого ряда, начиная со второго, соединен с выходом суммы часЭтичных произведений (к+1)-й вычислительной ячейки предьщущего ряда, (,2,.. .,п-1) вход множимого и вхо переноса к-й вычислительной ячейки каждого ряда, начиная со второго, соединены соответственно с выходом :множимого и выходом переноса к-й- выт ;числительной ячейки предвдущего ряда ;(,2,...,п), на входы суммы частичных произведений а- вычислительных ячеек каждого ряда, начиная со второго, подаются сигналы логического нуля, выходы переноса и выходы суммы частичных произведений вычислительных ячеек т-го ряда соединены с соответствукщими по весу входами п-разрядного сумматора, информационный вход каждой 1-й ячейки памяти 1-го ряда соединен с информационным выходом i-й ячейки памяти (1-1)-го ряда (,2,...,1-1; ,3,...,т), управляющий выход каждой 1-й ячейки памяти 1-го ряда соединен с управляющим входом (1+1)-й ячейки памяти 1-го ряда (,2,...,1-1; 1 2,3,...,1),управляющий выход 1-й ячейки памяти 1-г6 разряда соеди нен с управляпзцим входом первой вычислительной ячейки р-го ряда, где ,2.. .,1п-1, информационный вход 1-й ячейки памяти 1-го ряда соединен с выходом суммы частичных произведений первой вычислительной ячейки р-го ряда, где , ,2,...,т, управляющий вход первой вычислительной ячейки первого ряда и управляющие входы первых ячеек памяти всех рядов являются управлянхцими входами Матричного у; ножителя, информационные выходы ячеек памяти т-го ряда и выходы п-разрядного сумматора являются информационными выходами матричного умножителя.

Умножитель более эффективен, при- ; менение конвейерной организации обеспечивает полное использование матричной логики (2j.

Однако введение ячеек памяти увеличило число логических уровней, через которые должны пройти сигналы, что снизило быстродействие умножителя. . - ;

Цель изобретения - увеличение быстродействия мат ричного умножителя за счет сокращения количества логических уровней, через которые проходят сигналы, при условии сохранения Конвейерного принщ1па работы.

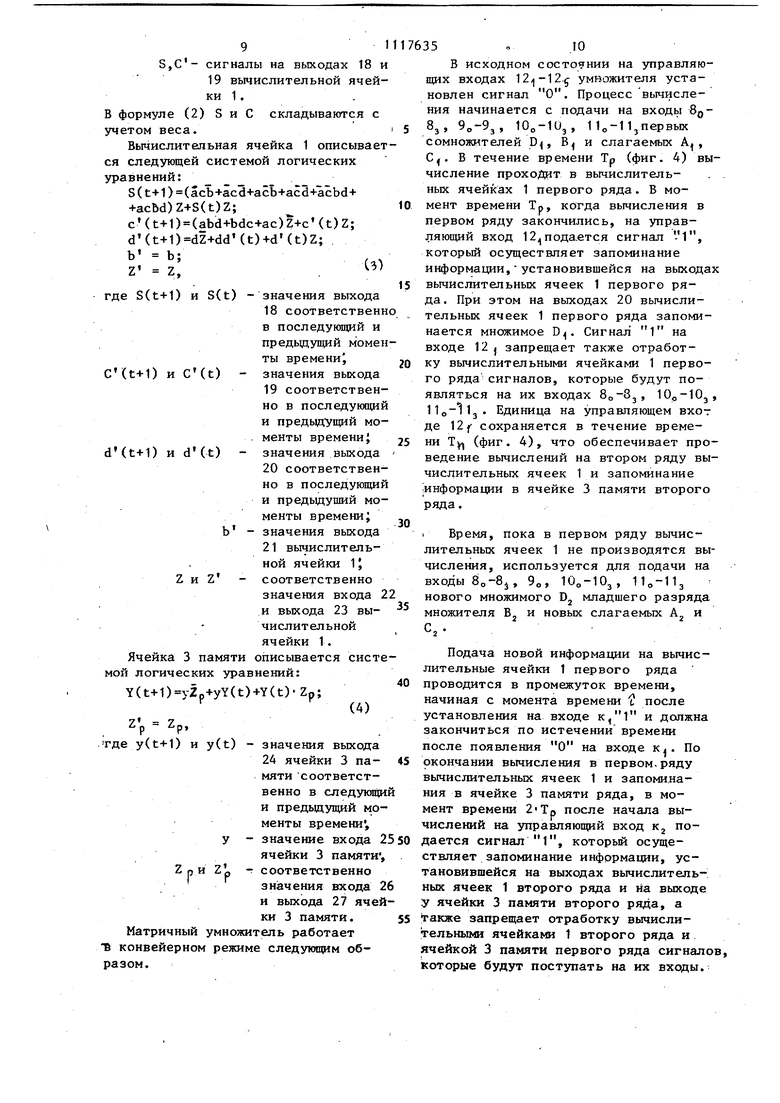

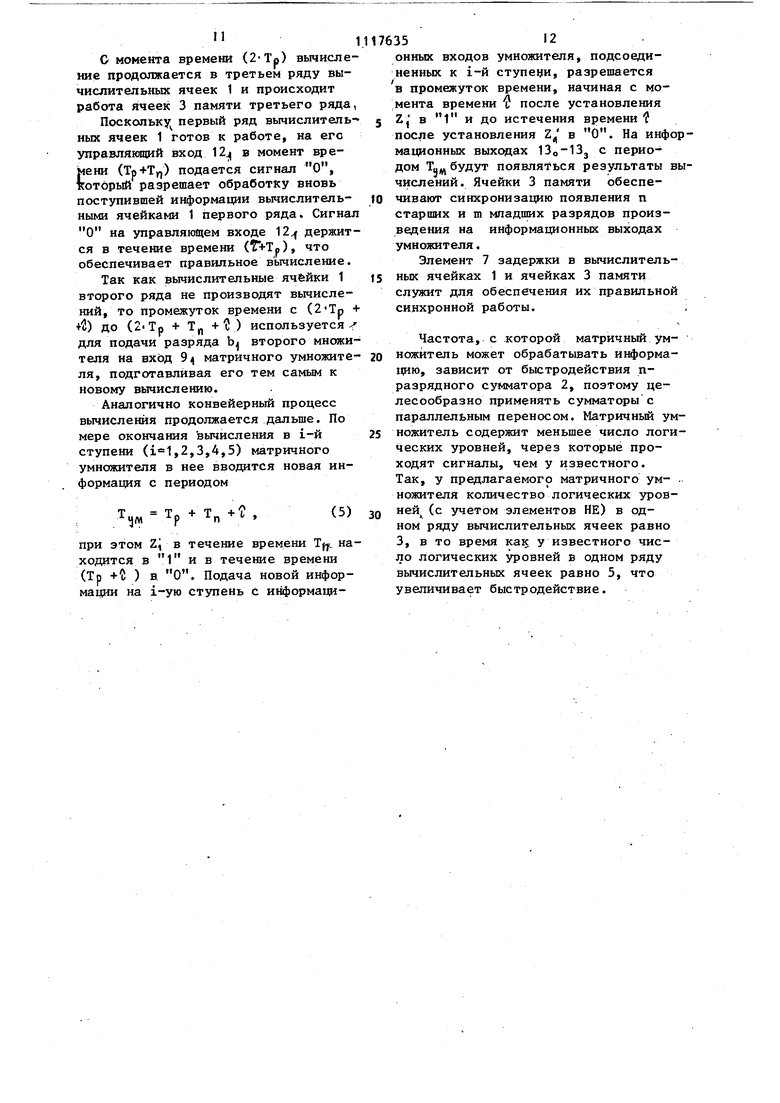

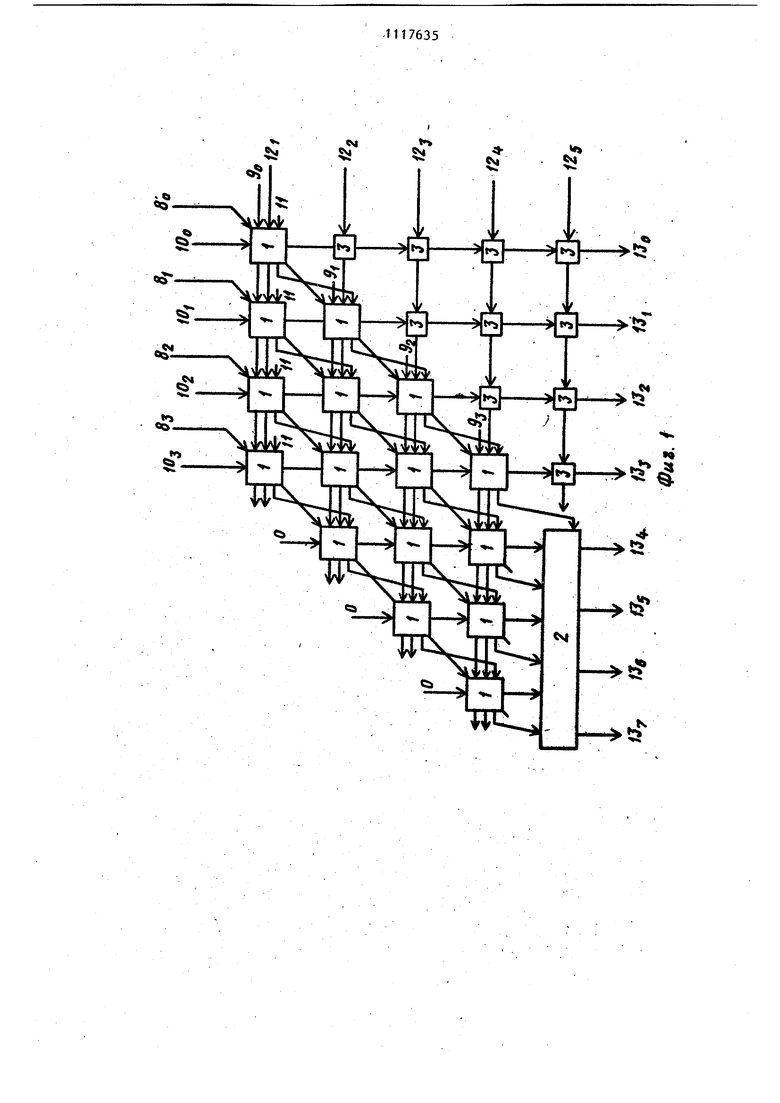

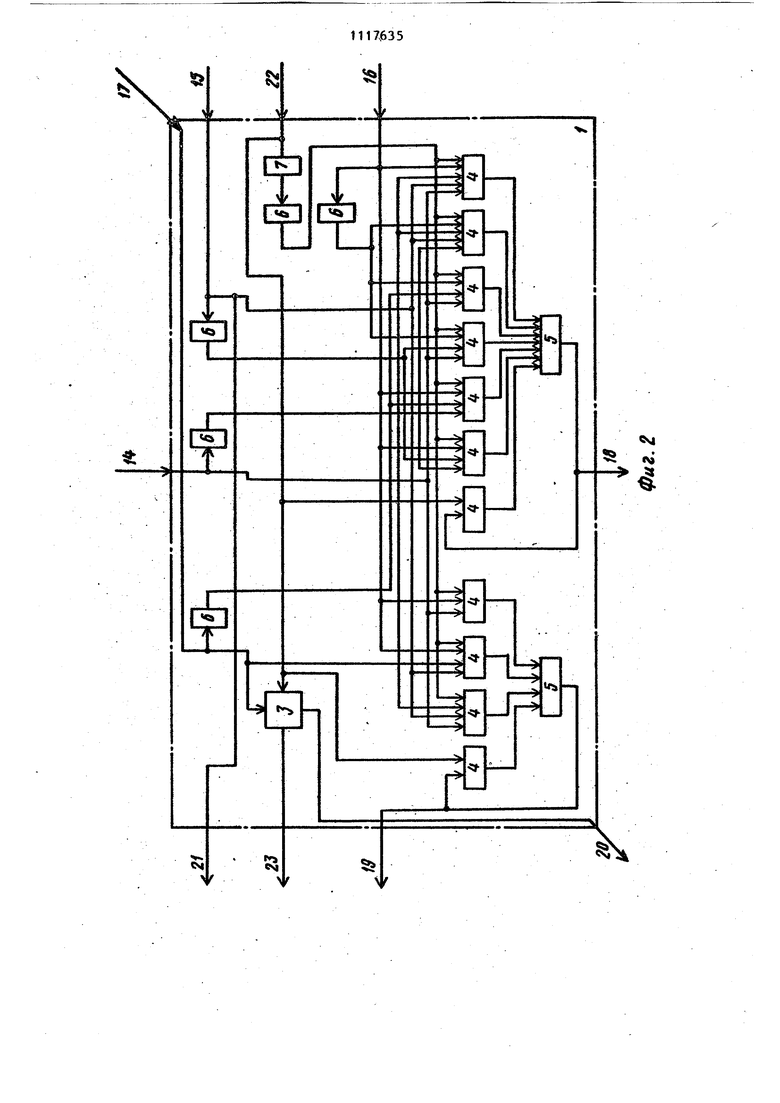

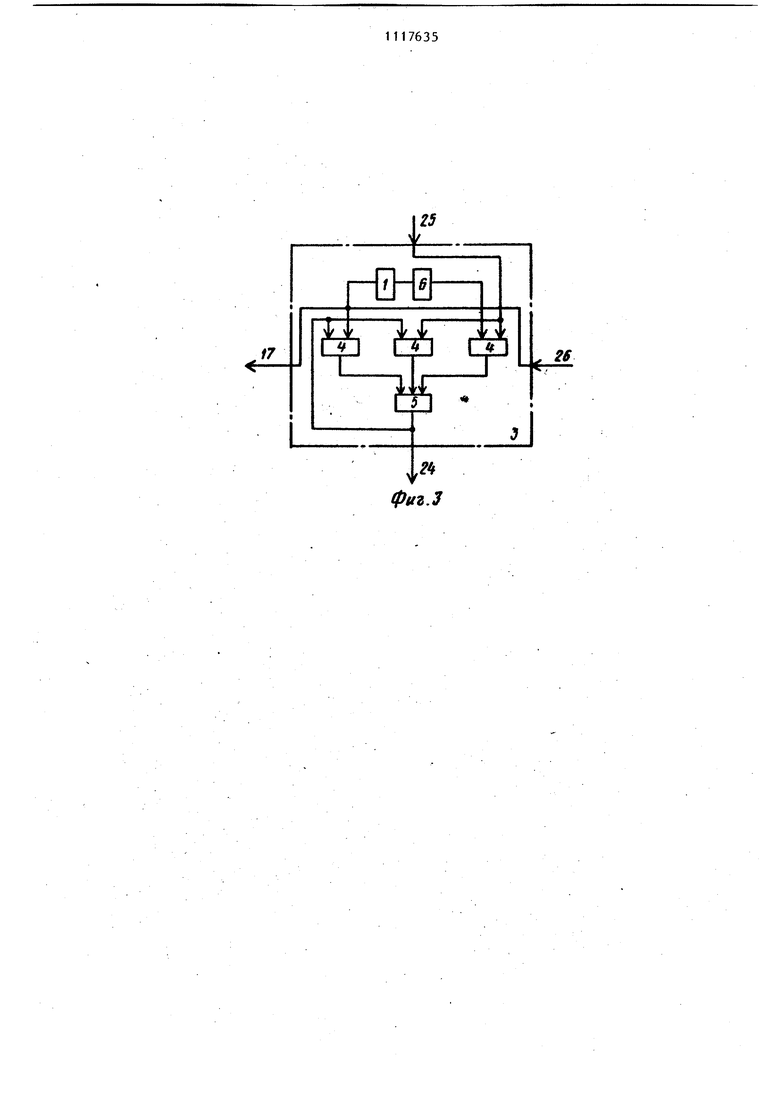

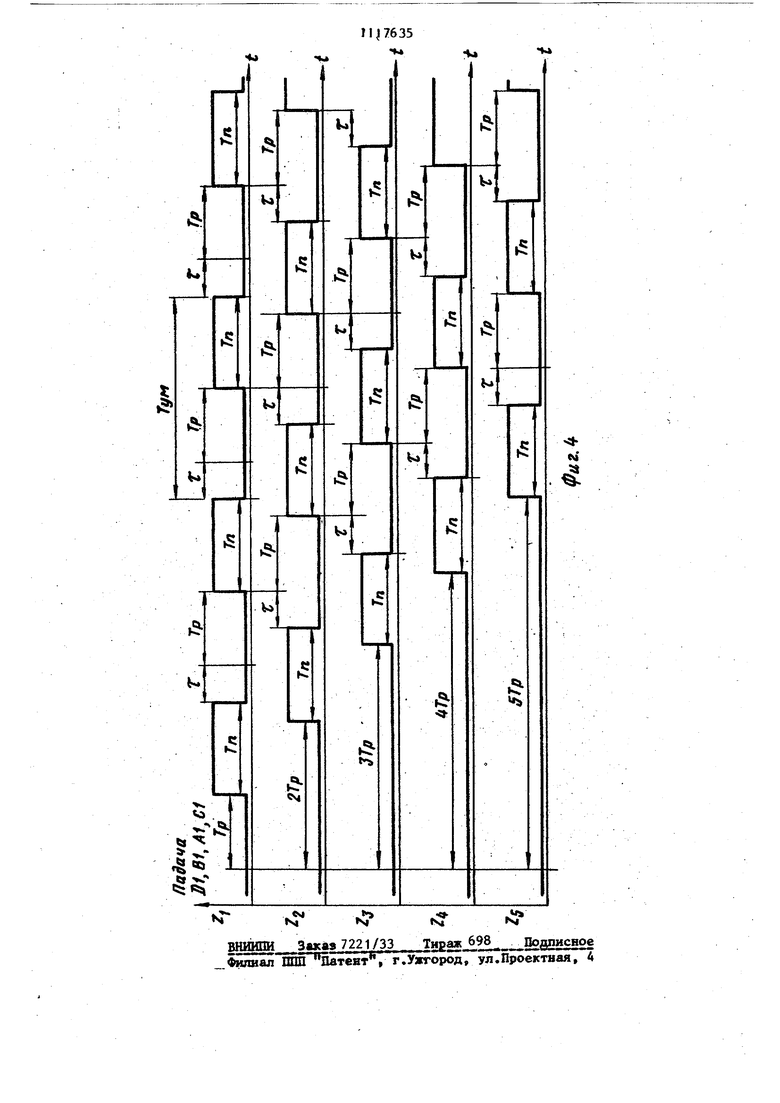

Поставленная цель достигается тем, что вычислительное устройство, содержащее матрицу вычислительных ячеек размерностью m«h где tn,n - разрядности соответственно множителя и множимого, каждая вычислительная ячейка содержит девять элементов И, четыре элемента НЕ, узел памяти и m групп по j узлов памяти (,...,m), где j - номер группы,причем каждый узел памяти сор,ержят три элемента И, элемент ИЛИ, элемент НЕ, причем первый вход первого элемента И узла памяти соединен с первым входом- второго элемента И, второй вход которого соединен с первым входом третьего элемента И к выходом элемента ИЛИ, первый, второй и третий входы которого соединены соответственно с выходами первого, второго и третьего элементов И узла памяти, второй вход первого элемента И которого соединен с выходом элемента НЕ узла памят разрядные входы первого слагаемого устройства соединены соответственно с входами первых элементов НЕ вычислительных ячеек первой строки матрицы, разрядные входы второго слагаемого устройства соединены соответственно со входами вторых элементов НЕ вычислительных ячеек первой строки матрицы, разрядные входы множителя соединены соответственно с входами третьих элементов НЕ вычислительных ячеек первого столбца матрицы, разрядные входы множимого устройства соединены соответственно с входами четвертых элементов НЕ вычислительных ячеек первой строки матрицы и первыми входами первых элементов И узлов памяти вычислительных ячеек первой строки матрицы вторые входы Третьих элементов И каждого узла памяти вычислительных ячеек i-й строки матрицы (,...,га) соединены с .i-M тактирующим входом устройства, первый вход первого элемента И каждой вычислительной ячейки матрицы соединен с первым входом второго, третьего, четвертого и пятого элемен тов И вычислительной ячейки матрицы, второй ВХОД первого элемента И которой соединен с первь№1 входом шестого и седьмого элементов И и вторым входом пятого элемента И вычислительной ячейки матрицы, третий вход первого I элемента И которой соединен с вторым входом шестого и седьмого элементов И и третьим входом пятого элемента. И вычислительной ячейки матрицы, вто рой вход третьего элемента И которой соединен с вторым входом четвертого элемента И и третьим входом седьмого элемента И вычислительной ячейки мат рицы, первый вход восьмого элемента И которой соеда1нвн с первым входом девятого элемента И и четвертым входом седьмого элемента И вычислительной ячейки матрицы, третий вход шестого элемента И которой соединен с вторым входом второго, восьмого и девятого элементов И и четвертым входом пятого элемента И вычислительной ячейки матрицы, третий вход девятого элемента И которой соединен с третьий входом четвертого элемента И вычислительной ячейки матрицы, третий вход восьмого элемента И которой соединен с третьим входом третьего элемента И вычислительной ячейки матрицы, выходы первого, второго и шестого элементов И которой соединены соответственно с первым, вторым и третьим входом первого элемента ИЛИ вычислительной ячейки матрицы, выходы третьего, четвертого, пятого, седьмого,, восьмого : и девятого элементов И которой сое- : динены соответственно с первым, вторым, третьим, четвертым, пятым и шестым входом второго элемента ИЛИ вычислительной ячейки матрицы, входы первых элементов НЕ вычислительных ячеек матрицы п-го столбца i-й строки соединены с шиной логического нуля устройства, вход первого элемента НЕ вычислительной ячейки S-й строки (,...,т) и г-го столбца (,..., п-1) матрицы соединены с выходом второго элемента ИЛИ вычислительных ячеек (8-1)-й строки и (г+1)-го .столбца матрицы, выход первого элемента ИЛИ вычислительной ячейки i-й строки и 1-го столбца (,...,п) матрицы соединен с входом второго элемента НЕ вычислительной ячейки i-й строки и (1+1)-го столбца.матрицы, выход элемента И узла памяти вычислительной ячейки к-й строки (,...,т-1) и 1-го столбца матри;ЦЫ соединен с входом четвертого элемента НЕ вычислительной ячейки (к+1)-и строки и 1-го столЬца матрицы,выходы первых и вторых элементов ИЛИ вы-, числительных ячеек т-й строки .q-ro столбца (,..,m) и выход первого элемента ИЛИ вычислительной ячейки первого столбца т-й строки матрицы соединены с соответствукщими весовы входами параллельного сумматора,п выходов которого соединены с выходами п старших разрядов устройства, m выходов младших разрядов устройства соединены соотв.етственно с выходами элементов ИЛИ т-й группы узлов памяти, вторые входы вторых элементов И которой соединены с (т+1)-м тактирующим входом устройства, первые входы элементов И (j-l)-x узлов памяти j-й группы соединены соответственно с выхода ш элементов ИЛИ (j-l)-ft группы, первый вход элемента И j-ro узла памяти j-й группы соединен с вы ходом второго элемента ИЛИ вычислительной ячейки j-й строки первого столбца матрицы вычислительных ячеек в каждую вычислительную ячейку устройства дополнительно введены десятый и одиннадцатый элементы И, пятый элемент НЕ и элемент задержки, в каждый узел памяти введен элемент задержки, причем первый вход десятого элемента И вычислительной ячейки соединен с выходом первого элемента ИЛИ вычислительной ячейки матрицы, второй вход которого соединен с соответствующим тактовым входом устрой ства и первым входом одиннадцатого элемента И вычислительной ячейки матрицы, второй вход которого соединен с выходом второго элемента ИЛИ вычислительной ячейки матрицы, пятый вход пятого элемента И которой соединен с пятьш входом седьмого элемента И, четвертыми входами первого, третьего, четвертого, шестого, восьмого и девятого элементов .И, с третьим входом второго .элемента И и выходом пятого элемента НЕ вычислительной ячейки матрицы, вход пятого элемента НЕ которой соединен с выходом элемента задержки вычислительной ячей ки матрицы, вход которого соединен с вторым входом третьего элемента И и входом элемента задержки узла памяти вычислительной ячейки матрицы, выход которого соединен с входом элемента НЕ узла памяти вычислительной ячейки матрицы, вход первого элемента НЕ вычислительной ячейки соединен с первым входом первого элемента И вычислительной ячейки матрицы, выход первого элемента НЕ которой соединен (С первым входом восьмого элемента И, выход второго элемента НЕ вычислител ной ячейки соединен с третьим входом седьмого элемента И, вход второго элемента НЕ вычислительной ячейки соединен с четвертым входом пятого элемента И, второй вход которого сое динен с входом третьего элемента НЕ вьиислительной ячейки матрицы, выход которого соединен с третьим входом : восьмого элемента И, вход четвертого элемента НЕ вычислительной ячейки соединен с третьим входом первого ёлемента И вычислительной ячейки матрицы, выход четвертого элемента НЕ которой соединен с третьим входом )евятого элемента И, вход элемента задержки каждого узла памяти соединен со вторым входом третьего элемента И узла памяти, выход элемента задержки koToporo соединен с входом элемента НЕ узла памяти. На фиг. t представлена функциональная схема .матричного умножителя для где m,n - разряднорть множимого и множителя; на .фиг. 2 - функциональная схема вычислительной ячейки} на фиг, 3 - функциональная схема ячейки памяти, на фиг. 4 - временная диаграмма подачи управляющих сигналов. Матричный умножитель содержит вычислительные ячейки 1, п-разрядный сумматор 2, ячейки 3 памяти. Вычислительные ячейки 1 и ячейки 3 памяти содержат элементы И 4, элементы ИЛИ 5, элементы НЕ 6, элементы 7 задержки. Входы Sg-Sj являются информационными входами умножителя, на которые подаются сигналы, соответствующие двоичному множимому D, где индексразряд множимого с учетом его веса. Входы 9о-9з - информационные входы умножителя, на которые подаются сиг- налы, соответствующие двоичному множителю В. Входы 10д-lOj и входы 11j - информационные входы, на которые подаются сигналы слагаемых соответственно А и С. Входы 12;,-125 - управляющие входы умножителя.Выходы So, 13р-13 - информационные вьжоды умножителя, с которых снимаются сигналы результата S. Матричный умножитель реализует функцию А + B-D + С Для вычисления произведения двух чисел В и D слагаемые А и С должны нулевыми. Реализация умножителем функции вида (1) расширяет его функциональные возможности. Каждая вычислительная ячейка 1 умножителя осуществляет такую же арифметическую функцию как весь умножитель, только для одноразрядных двоичных чисел а, Ь, с, d: S + с а + b-d + где a,b,c,d - сигналы на входах 14-17 вычислительной ячейки 1; 9 S,C- сигналы на выходах 18 и 19 вычислительной ячейки 1 . В формуле (2) S и С складываются с учетом веса. Вьиислительная ячейка 1 описывает ся следующей системой логических уравнений: S(t+1)(acb+acd+acb+acd+acbd+ +acbd)Z+S(t)Z; с(t+1)(abd+bdc+ac)Z+c(t)Z; d(t+1)dZ+dd(t)+d(t)Z; b b; Z Z, где S(t+1) и S(t) - значения выхода 18соответствен в последующий и предьздущий моме ты времени C(t+1) и C(t) - значения выхода 19соответствен но в последующи и предьщущий мо . менты времениJ d(t+1) и d(t) - значения выхода 20соответствен но в последующи и предьщуший мо менты времени; Ь - значения выхода 21вычислительной ячейки 1J Z и Z - соответственно значения входа и выхода 23 вычислительнойячейки 1. Ячейка 3 памяти описывается сист мой логических уравнений: Y(t+1)yZp+yY(t)+Y(t) Zp; 7 7 р р. |где y(t+1) и y(t) - значения выхода 24 ячейки 3 памяти соответственно в следующ и предьщущий мо менты времени, у - значение входа ячейки 3 памяти Z р и ZP -г соответственно значения входа и выхода 27 яче ки 3 памяти. Матричный умножитель работает Ъ конвейерном режиме следующим образом. 5о10 В исходном состоянии на управляющих входах . умножителя установлен сигнал О. Процессвычисления начинается с подачи на входы SQ83, 9„-9з, 10о-10з, 11о-11зпервых сомножителей D, В и слагаемых А, С,. В течение времени Тр (фиг. 4) вычисление проходит в вычислитель- . . ных ячейках 1 первого ряда. В момент времени Тр, когда вычисления в первом ряду закончились, на управляющий вход 12 подается сигнал 1, который осуществляет запоминание информации, установившейся на выходах вычислительных ячеек 1 первого ряда . При этом на выходах 20 вычислительных ячеек 1 первого ряда запоминается множимое D. Сигнал 1 на входе 12J запрещает также отработку вычислительными ячейками 1 первого ряда сигналов, которые будут появляться на их входах 8o-8.j, Юр-Ю, 11о 11з Единица на управляющем вхот де 12j сохраняется в течение времени Ту, (фиг. 4), что обеспечивает проведение вычислений на втором ряду вычислительных ячеек 1 и запоминание |информации в ячейке 3 памяти второго ряда. I Время, пока в первом ряду вычислительных ячеек 1 не производятся вычисления, используется для подачи на входы 80-85, 9о, Юо-Юз, 11о-11з нового множимого Dj младшего разряда множителя Bj и новых слагаемых А и С,Подача новой информации на вычислительные ячейки 1 первого ряда проводится в промежуток времени, начиная с момента времени I) после установления на входе к,1 и должна закончиться по истечении времени после появления О на входе к,. По окончании вычисления в первом.ряду вычислительных ячеек 1 и запоминания в ячейке 3 памяти ряда, в момент времени 2Тр после начала вычислений на управляющий вход к., подается сигнал 1, которьй осуществляет запоминание информации, установившейся на выходах вычислительных ячеек 1 второго ряда и на выходе у ячейки 3 памяти второго ряда, а также запрещает отработку вычислительными ячейками 1 второго ряда и ячейкой 3 памяти первого ряда сигналов, которые будут постзшать на их входы.

II

о момента времени (2-Те) вычисление продолжается в третьем ряду вычислительных ячеек 1 и происходит работа ячеек 3 памяти третьего ряда,

Поскольку первый ряд вычислительных ячеек 1 готов к работе, на его управлянлций вход 12 в момент врееени (Тр+Т) подается сигнал О, оторый разрешает обработку вновь поступившей информации вьиислитёльными ячейкаю 1 первого ряда. Сигнал О на управляющем входе 12 держится в течение времени (), что обеспечивает правильное вычисление.

Так как вычислительные ячейки 1 второго ряда не производят вычислений, то промежуток времени с (2Тр + +) до (2Тр + Т„ + ) используется-: для подачи разряда Ь второго множителя на вход 9ц матричного умножителя, подготавливая его тем самым к новому вычислению.

Аналогично конвейерный процесс вычисления продолжается дальше. По мере окончания вычисления в i-й ступени (,2,3,4,5) матричного умножителя в нее вводится новая информация с периодом

Тр + Т„ +,

(5)

ум

при этом Z 3 течение времени Т. находится в 1 и в течение времени (То +t ) в О. Подача новой информации на i-ую ступень с информаци1763512

онных входов умножителя, подсоединенных к i-й ступеци, разрешается в промежуток времени, начиная с момента времени после установления 5 Zj в 1 и до истечения времени

после установления в О. На информационных выходах 13o-13j с периодом Тм будут появляться результаты вычислений. Ячейки 3 памяти обеспеfO чивают синхронизацию появления п старших и m мпадших разрядов произведения на информационных выходах умножителя.

Элемент 7 задержки в вычислитель15 ньк ячейках 1 и ячейках 3 памяти

служит для обеспечения их правильной синхронной работы.

Частота, с .которой матричный ум20 ножйтель может обрабатывать информацию, зависит от быстродействия празрядного сумматора 2, поэтому целесообразно применять сумматоры с параллельным переносом. Матричный ум5 ножйтель содержит меньшее число логических уровней, через которые проходят сигналы, чем у известного. Так, у предлагаемого матричного ум- . ножителя количество логических уровQ ней. (с учетом элементов НЕ) в одном ряду вычислительных ячеек равно 3, в то время как у известного число логических уровней в одном ряду вычислительных ячеек равно 5, что увеличивает быстродействие. -Л- 53

Cs4 «N

фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Множительное устройство | 1979 |

|

SU817705A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Deverell I | |||

| Pipeline iterative arithmetic arrays | |||

| IEEE Transaction Computers, v | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

Авторы

Даты

1984-10-07—Публикация

1983-01-07—Подача