12

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих процессорах и специализированных вычислительных устройствах.

Целью изобретения является повьппе ние быстродействия.

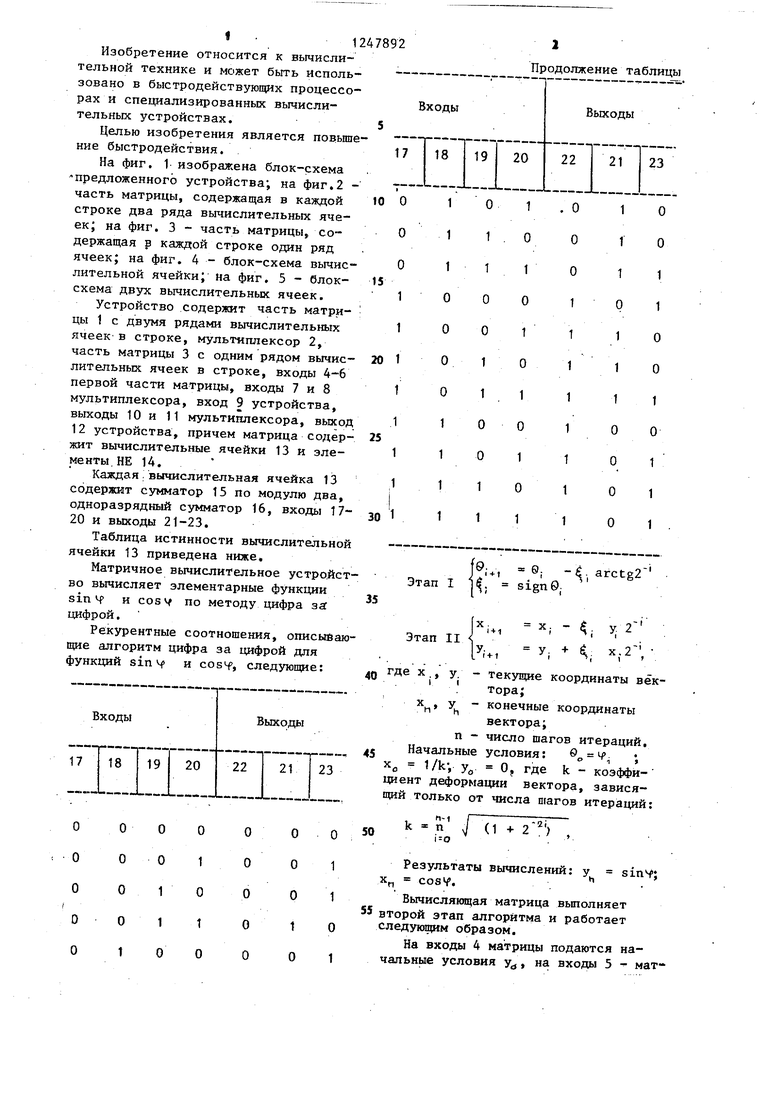

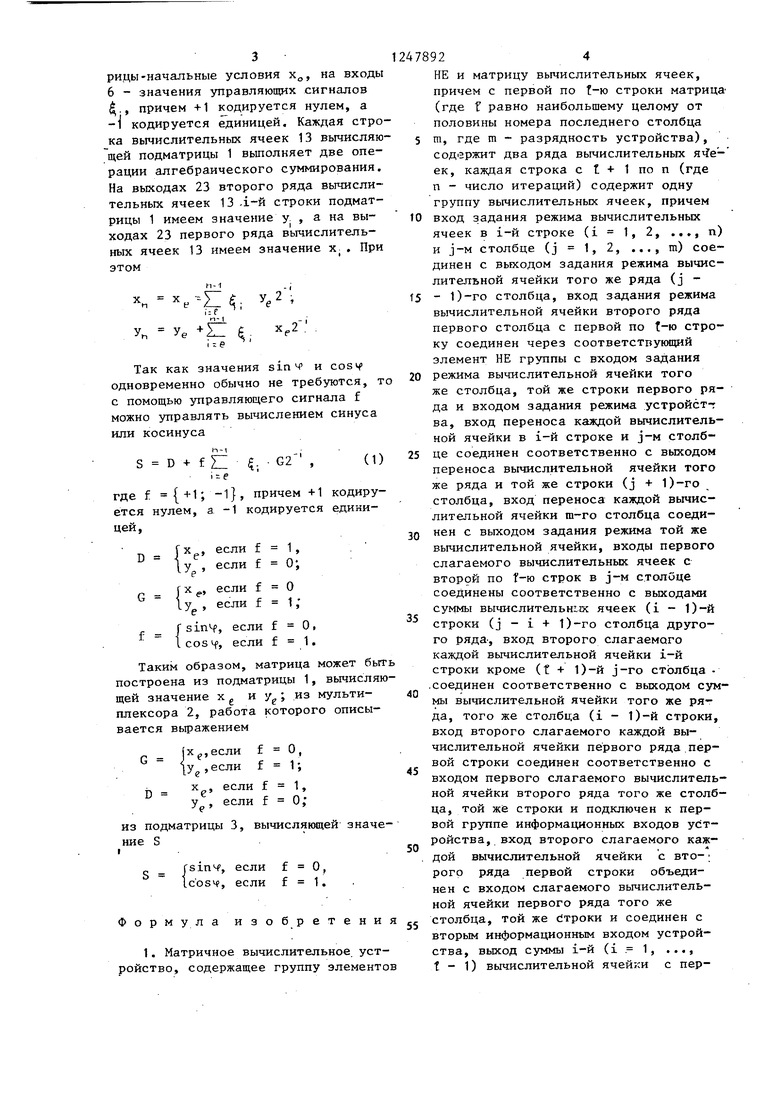

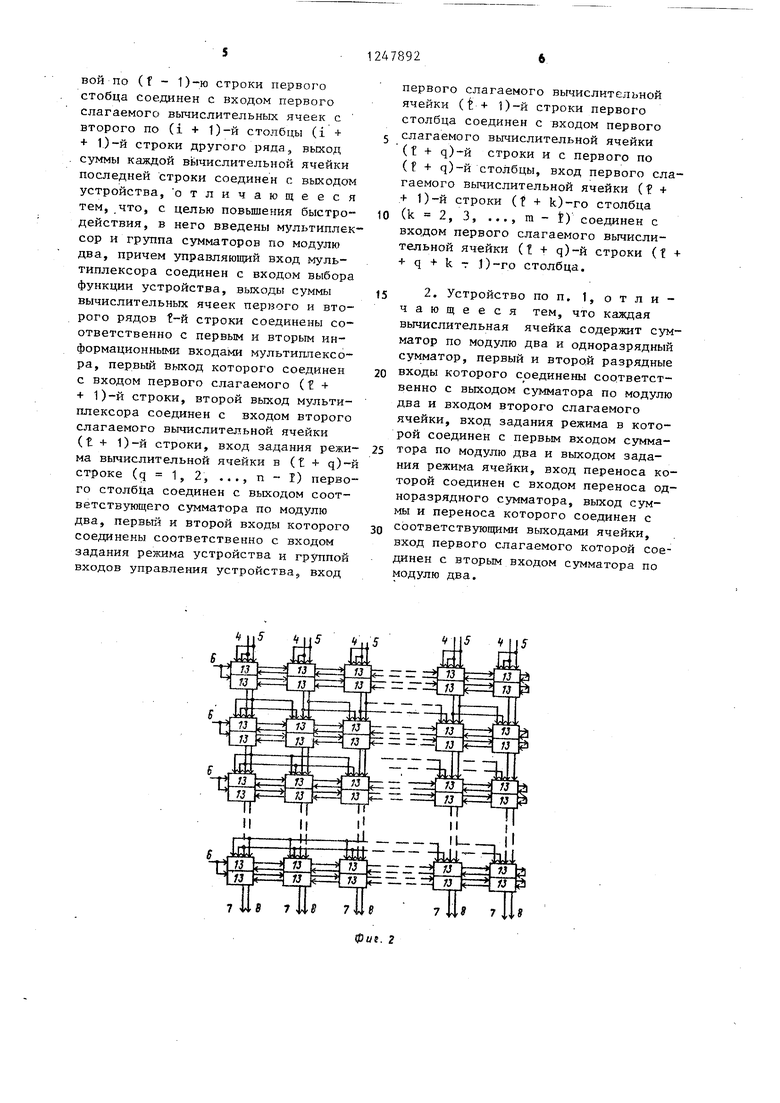

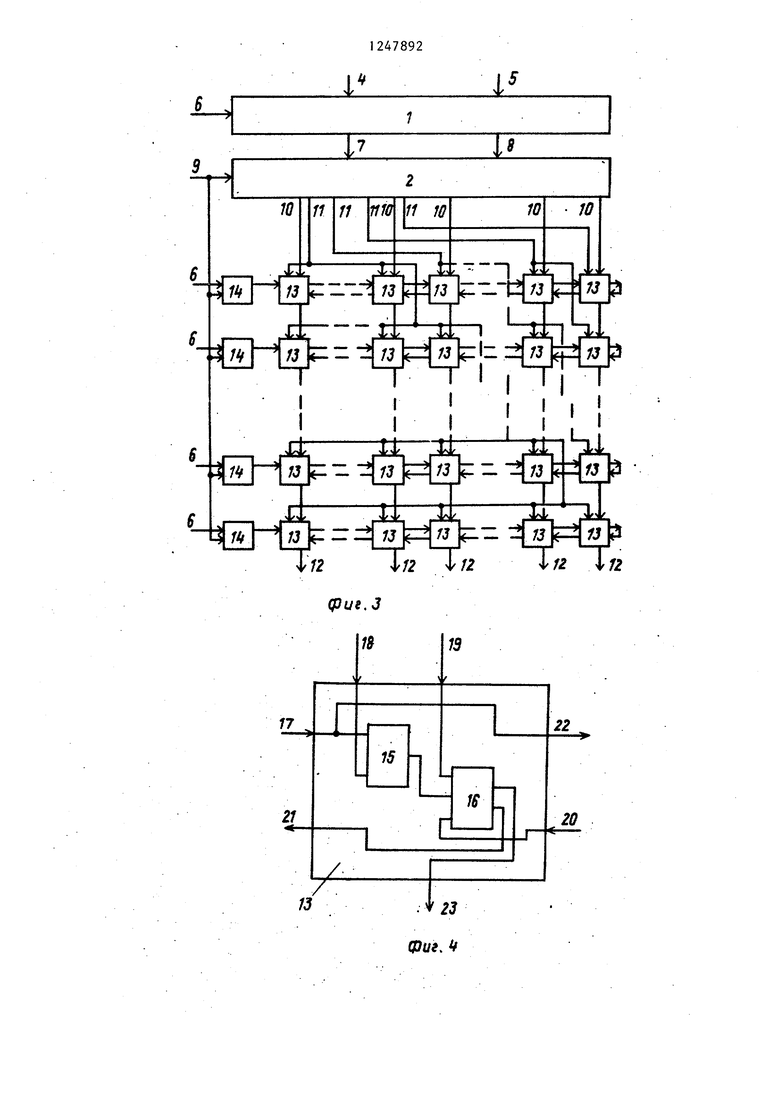

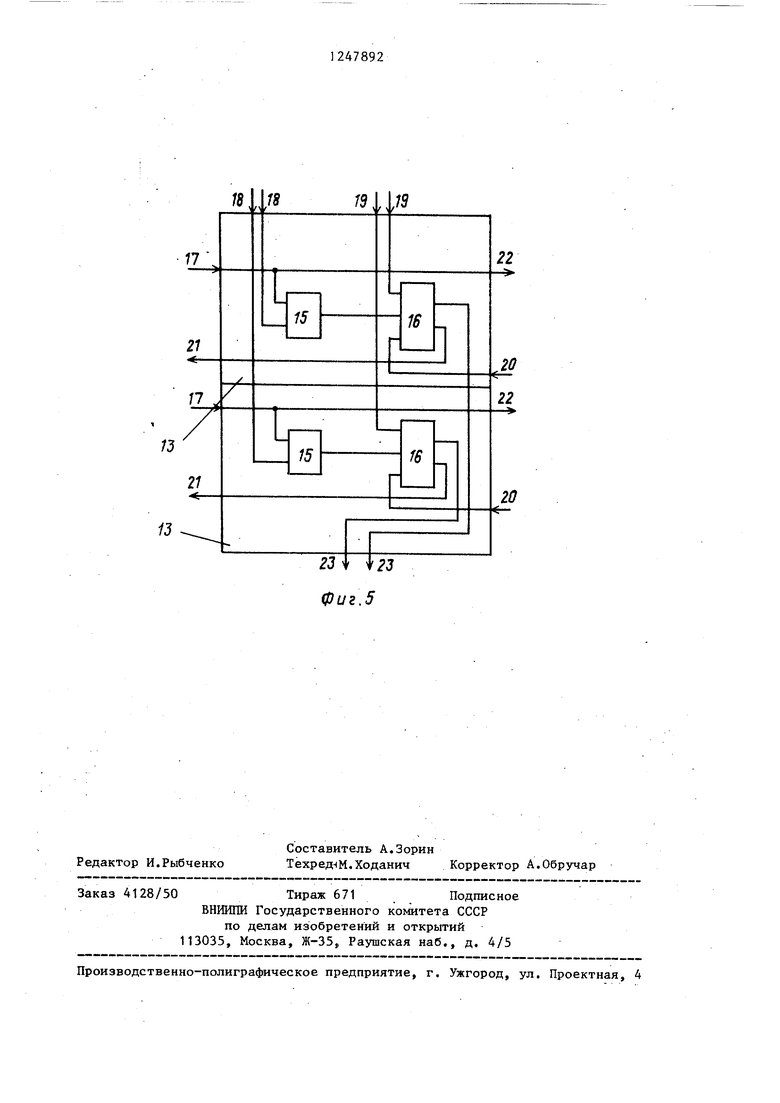

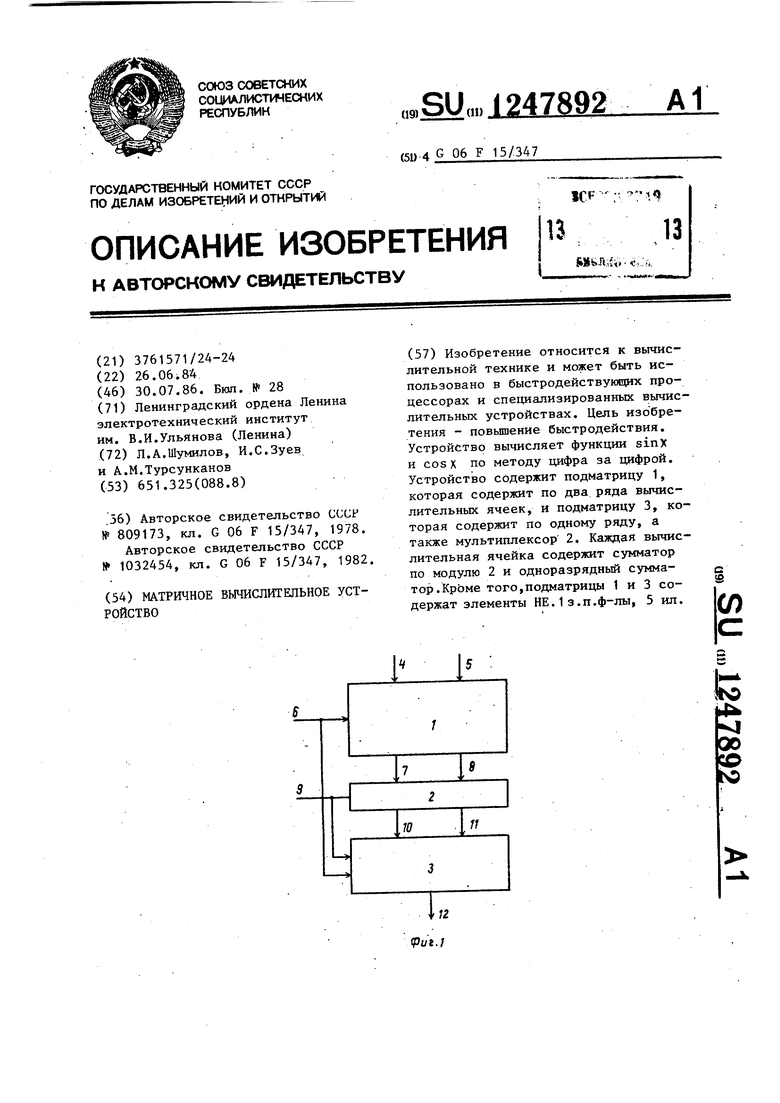

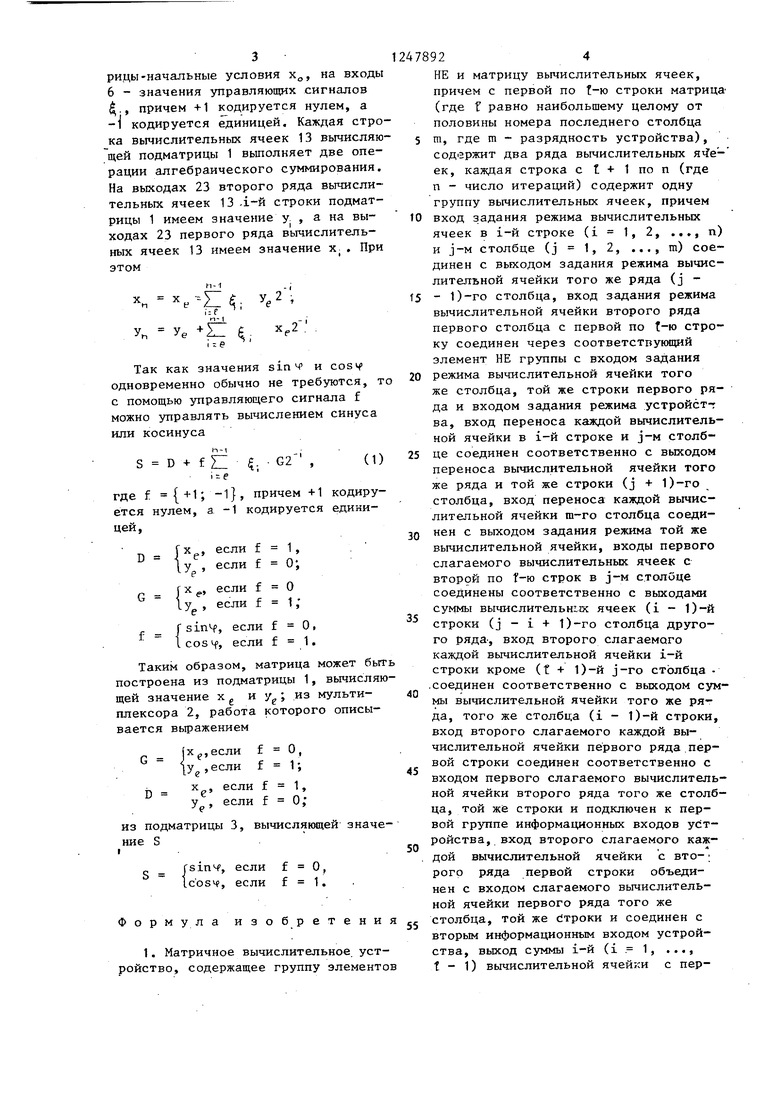

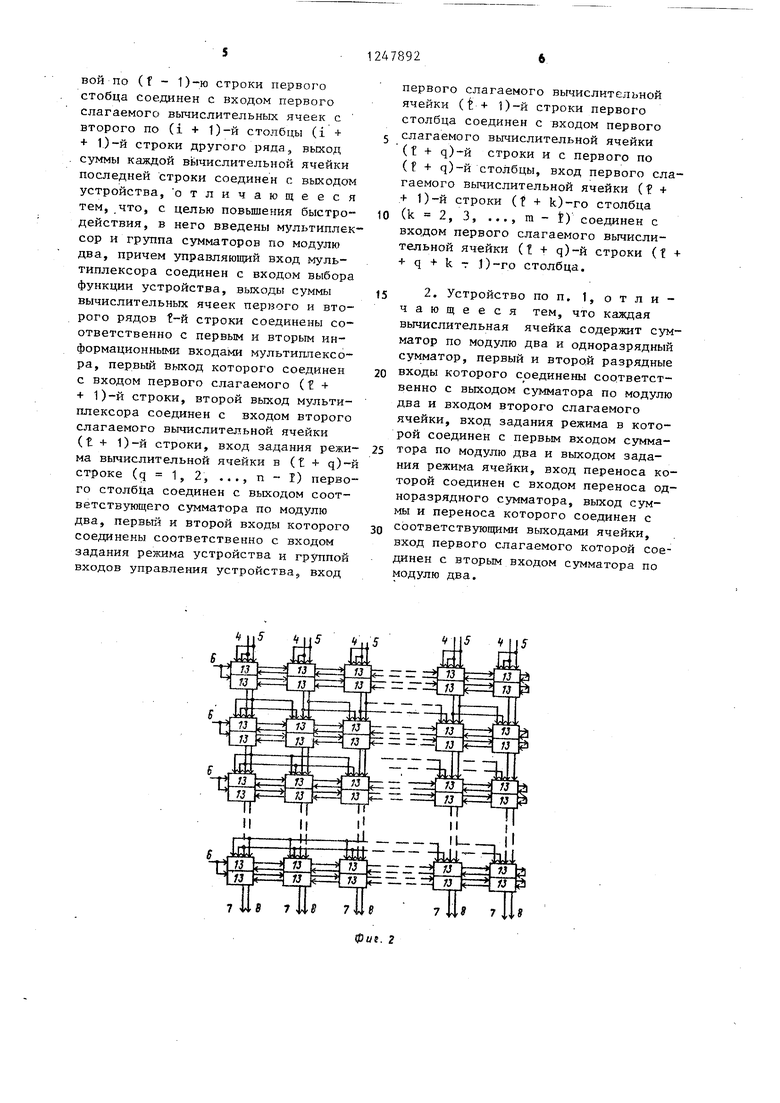

На фиг. 1 изображена блок-схема предложенного устройства; на фиг.2 - часть матрицы, содержащая в каждой строке два ряда вычислительных ячеек; на фиг. 3 - часть матрицы, со- держащая р каждой строке один ряд ячеек; на фиг. 4 - блок-схема вычис- лительной ячейки; на фиг. 5 - блок- схема двух вьиислительных ячеек.

Устройство содержит часть матри- цы 1 с двумя рядами вычислительных ячеек в строке, мультиплексор 2, часть матрицы 3 с одним рядом вычис- лительных ячеек в строке, входы 4-6 первой части матрицы, входы 7 и 8 мультиплексора, вход 9 устройства, выходы 10 и 11 мультиплексора, выход 12 устройства, причем матрица содер- жит вычислительные ячейки 13 и эле- менты.НЕ 14. °

Каждая.вычислительная ячейка 13 содержит сумматор 15 по модулю два, одноразрядный сумматор 16, входы 17- 20 и выходы 21-23.

Таблица истинности вычислительной ячейки 13 приведена ниже.

Матричное вычислительное устройство вычисляет элементарные функции sin Ч и COSV по методу цифра заг цифрой.

Рекурентные соотношения, описывающие алгоритм цифра за цифрой для функций sin Ч и cosy, следующие:

Продолжение таблицы

о 1 1 о о 1 1 о о 1 1

1 о 1

о 1 о 1

о 1 о 1

о о о 1 1 1 1 1 1 1 1

1 1

1 о 1 1 1 о о о о

о о 1 1

о о 1

о 1 1 1

1,4, 0; -.arctg2- Этап I 1. signQ;

II

) .41

,

-, - . у,

У; , 2-,

дд где X., у. - текущие координаты век тора; х, у - конечные координаты

вектора;

п - число шагов итераций. j Начальные условия: о , Хд 1/kv УО О, где k - коэффи- циент деформации вектора, зависящий только от юсла пгагов итераций:

50

п J (1 + )

l-O

Результаты вычислений: у sinУ; х cosV. .

Вычислякицая матрица выполняет 55 второй этап алгоритма и работает следующим образом.

На входы 4 матрицы подаются начальные условия у, на входы 5 мат3

РИДЫ-начальные условия х, на входы 6 - значения управляющих сигналов ., причем +1 кодируется нулем, а -1 кодируется единицей. Каждая строка вычислительньк ячеек 13 вычисляю щей подматрицы 1 вьшолняет две операции алгебраического суммирования. На выходах 23 второго ряда вычислительных ячеек 13 .i-й строки подматрицы 1 имеем значение у. , а на выходах 23 первого ряда вычислительных ячеек 13 имеем значение х-. При этом

п ; Уе.

УП Ур р

п-

е -11 ,.

х,2

Так как значения sin4 и cosy одновременно обычно не требуются, то с помощью управляющего сигнала f можно управлять вычислением синуса или косинуса

S D f ZI .

. G2

где f (+1; -1}, причем +1 кодируется нулем, а -1 кодируется единицей,

х, если f 1 , если f 0;

D pt Ь,.

« (У:: .. {

если f О если f 1,

sinV, если f 0. cos f, если f 1,

Таким образом, матрица может быт построена из подматрицы 1, вычисляющей значение х g и у ; из мультиплексора 2, работа которого описывается вьфажением

(Хр,если f О,

/ с 1 .

уJ,если f 1;

X , если f 1, у , если f О,

из подматрицы 3, вычисляющей ние S I

fsin4, если f О, tcosM , если f 1.

Форм у л а изобретения

1. Матричное вычислительное, устройство, содержащее группу элементов

1

-

о

ья

в

2478924

НЕ и матрицу вычислительных ячеек, причем с первой по 1-ю строки матрица (где f равно наибольшему целому от половины номера последнего столбца 5 т, где m - разрядность устройства), содержит два ряда вычислительных ек, каждая строка с t + 1 по п (где п - число итераций) содержит одну группу вычислительных ячеек, причем 10 вход задания режима вычислительных ячеек в i-й строке (i 1, 2, ..., п) и J-M столбце (J 1, 2, ..., т) соединен с выходом задания режима вычислительной ячейки того же ряда (j Г5 1)-го столбца, вход задания режима вычислительной ячейки второго ряда первого столбца с первой по t-ю строку соединен через соответствующий элемент НЕ группы с входом задания

20 режима вычислительной ячейки того

же столбца, той же строки первого ряда и входом задания режима устройстт ва, вход переноса каждой вычислительной ячейки в i-й строке и J-M столб25 це соединен соответственно с выходом переноса вычислительной ячейки того же ряда и той же строки (j + 1)-го столбца, вход переноса каждой вычислительной ячейки т-го столбца соеди30 нен с выходом задания режима той же вычислительной ячейки, входы первого слагаемого вычислительных ячеек с второй по t-ю строк в J-M столице соединены соответственно с выходами суммы вычислительное ячеек (i - 1)-й строки (j - i + 1)-го столбца другого ряда-, вход второго слагаемого каждой вычислительной ячейки i-й строки кроме (t + 1)-й j-ro столбца - .соединен соответственно с выходом суммы вычислительной ячейки того же ряда, того же столбца (i - 1)-й строки, вход второго слагаемого каждой вычислительной ячейки первого ряда.первой строки соединен соответственно с входом первого слагаемого вычислительной ячейки второго ряда того же столбца, той же строки и подключен к первой группе информационных входов устройства, вход второго слагаемого кажI

дои вычислительной ячейки с вто-; рогр ряда первой строки объединен с входом слагаемого вычислительной ячейки первого ряда того же столбца, той же строки и соединен с вторым информационным входом устройства, выход суммы i-й (i . 1, ..., t - 1) вычислительной ячейки с пер35

40

45

50

вой по (f - 1)-ю строки первого стобца соединен с входом первого слагаемого вычислительных ячеек с второго по (i + 1)-й столбцы (i + + 1)-й строки другого ряда, выход суммы каждой вЬ1числительной ячейки последней строки соединен с выходом устройства, отличающееся тем,.что, с целью повьшения быстро™ действия, в него введены мультиплексор и группа сумматоров по модулю два, причем управляющий вход мультиплексора соединен с входом выбора функции устройства, выходы суммы вычислительных ячеек пер)зого и второго рядов t-й строки соединены соответственно с первым и вторым информационными входами мультиппексо- ра, первый выход которого соединен с входом первого слагаемого (Е + + 1)-й строки, второй выход мультиплексора соединен с входом второго слагаемого вычислительной ячейки (t + 1)-й строки, вход задания режи ма вычислительной ячейки в (t q)строке (q 1, 2, ..., п - I) первого столбца соединен с выходом соответствующего сумматора по модулю два, первый и второй входы которого соединены соответственно с входом задания режима устройства и группой входов управления устройства, вход

первого слагаемого вычислительной ячейки (t + 1)-й строки первого столбца соединен с входом первого слагаемого вычислительной ячейки (f + q)-й строки и с первого по (f + q)-и столбцы, вход первого слагаемого вычислительной ячейки ( + + 1)-й строки (f + k)-ro столбца (k 2, 3, ,.., га - J) соединен с входом первого слагаемого вычислительной ячейки (t + q)-й строки (t + f- q - k т .1)-го столбца.

2. Устройство поп, 1, отличающееся тем, что каждая вычислительная ячейка содержит сумматор по модулю два и одноразрядный сумматор, первый и второй разрядные входы которого соединены соответственно с выходом сумматора по модулю два и входом второго слагаемого ячейки, вход задания режима в которой соединен с первым входом тора по модулю два и выходом задания режима ячейки, вход переноса которой соединен с входом переноса одноразрядного сумматора, выход суммы и переноса которого соединен с соответствующими выходами ячейки, вход первого слагаемого которой соединен с вторым входом сумматора по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство тригонометрических функций | 1984 |

|

SU1238060A1 |

| Вычислительное устройство | 1983 |

|

SU1164701A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Матричное вычислительное устройство | 1983 |

|

SU1092497A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Вычислительное устройство | 1981 |

|

SU1032454A1 |

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих процессорах и специализированных вычислительных устройствах. Цель изобретения - повьппение быстродействия. Устройство вычисляет функции sinX и COSX по методу цифра за цифрой. Устройство содержит подматрицу 1, которая содержит по два ряда вычислительных ячеек, и подматрицу 3, которая содержит по одному ряду, а также мультиплексор 2. Каждая вычислительная ячейка содержит сумматор по модулю 2 и одноразрядный сумматор. Кроме того, подматрицы 1 и 3 содержат элементы НЕ.1з.п.ф-лы, 5 ил. i (Л 1 5 : .ю п т: риг.}

« ||5

11-5

«iiS

Ж. .1.

(pue,J

17

21

13

/ A

IB

13

22

IS

1

20

23

Фиг. V

23 фиг.5

2

Редактор И.Рыбченко

Составитель А.Зорин

ТехреднМ.Ходанич Корректор А.Обручар

Заказ 4128/50Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

23

Авторы

Даты

1986-07-30—Публикация

1984-06-26—Подача