Фиг./

Изобретение относится к вычислительной технике и может быть исполь- эовано при построении однотактйых делителей матричного типа для вьшол- Нения операции деления в дополнительном двоичном коде.

Целью изобретения является сокращение аппаратурных затрат.

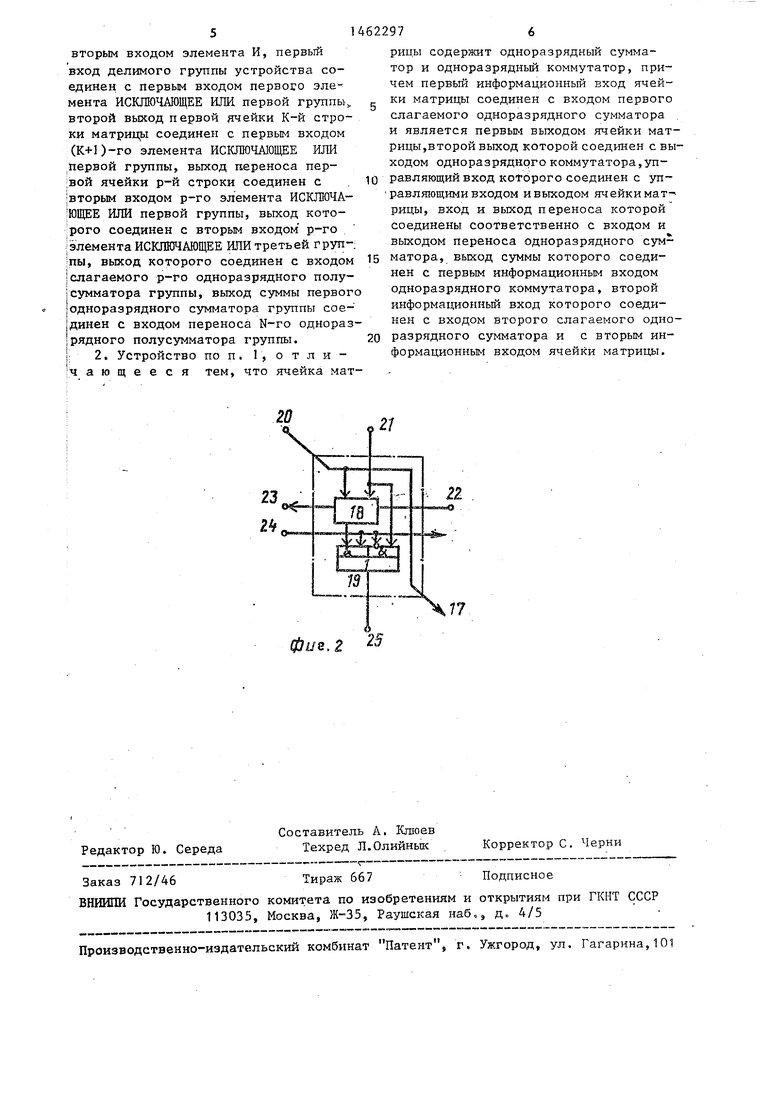

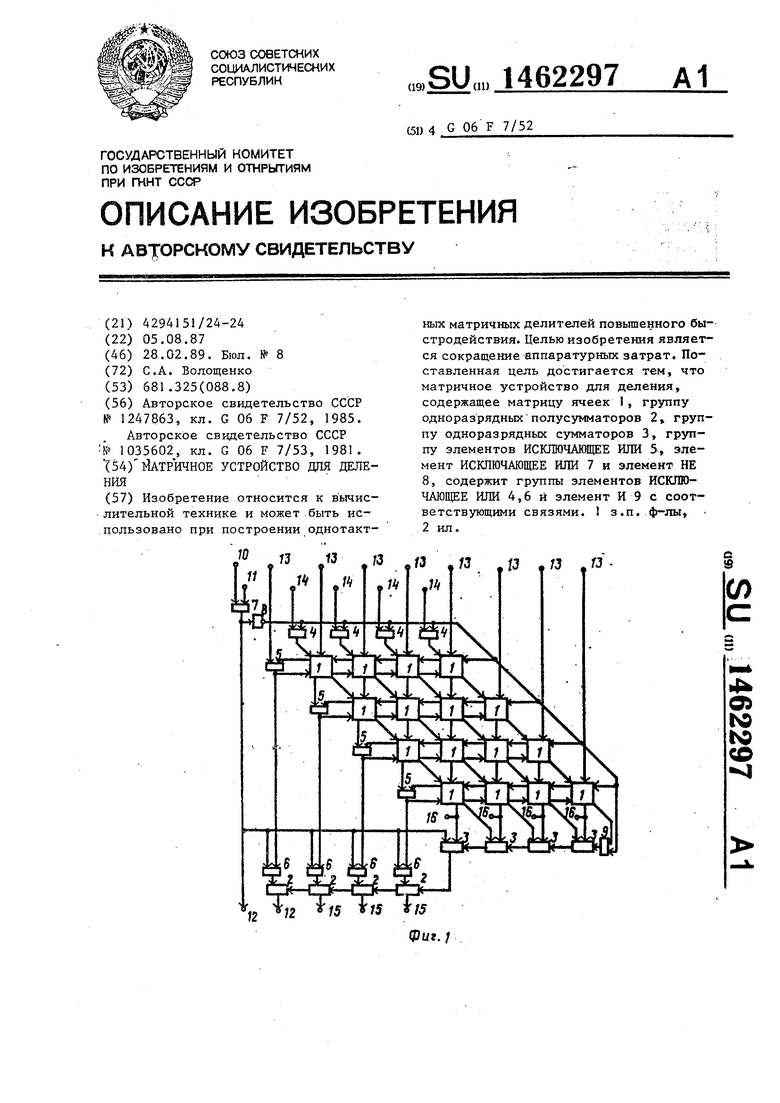

На фиг. I представлена схема пред Лагаемого матричного устройства для Деления (при разрядности равной че- 1|ырем) ) на фиг. 2 - схема ячейки мат 1|ицы.

Устройство (фиг. 1) содержит яче 1 матрицы, группы одноразрядных Полусумматоров 2, группу одноразряд- йых сумматоров 3, вторую группу злеМентов ИСКЛЮЧАЮЩЕЕ ИЛИ 4, первую itpynny элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5, третью группу элементов ИСКЛЮЧАЮЩЕЕ Или 6, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, Элемент НЕ 8, элемент И 9, входы 10 Ц 11 соответственно знаков делимого и делителя устройства, выход 12 зна- ka частного устройства, группы входов 13 и 14 соответственно делимого и делителя устройства, группу выходов 15 частного устройства, группу выходов 16 остатка устройстваi

Ячейки 1 матрицы (фиг. 2) содержат первый вькод 17 ячейки 1 матрицы фдноразрядньй сумматор 18, однораз- |)ядный коммутатор 19, первый и второй информационные входы 20 и 21 ячейки 1 матрицы, вход 22 переноса и выход 23 переноса ки 1 матрицы, управляющий Вход 24 1 матрицы, второй выход 25 Ячейки 1 матрицы.

. -г,

Номера строк в устройстве возрастают сй ерху вниз, а столбцов слева направо. Аналогична нумерация элементов в группах.

Устройство работает следующим образом.

Дополнительный код делимого X в разрядов (знаке 2N - разрядной - мантиссой) поступает на входы 10 и 13 устройства. Делитель у в N+ разрядов поступает на входы П и 14. Знак частного формируется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и поступает на выход 12 устройства, а N-разрядное частное, после завершения переходного процесса в устройстве - на выходах 15. Между величинами делимого

Q

5 0 5 0

5 0

5

0

5

и делителя должно соблюдаться соотношение / X If 1-у I. i

Вычисление цифр частного осуществляется итерационно, начиная со старших разрядов. Основными действиями итераций являются вычитание из очередного остатка делителя и формирование по знаку разницы следующего очередного остатка. Для выполнения вычитаний используются сумматоры 18 ячеек 1, а формирование очередных остатков осуществляется коммутаторами 19 этих же ячеек.

Для выполнения вычитания формируется такой код делителя, чтобы его знак был всегда противоположен знаку очередных остатков (у всех очередных остатков знак один и тот же и совпадает со знаком делимого), Формирование требуемого кода делителя выполняется группой элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4 ипередачей сигнала с выхода элемента НЕ 8 на входы переноса сумматоров последних ячеек каждой строки матрицы.

Лервая итерация выполняется в ячейках 1 первой строки матрицы. Здесь из сдвинутого на один разряд в сторону старших разрядов кода нулевого остатка Q, которым является код делимого, вычитается код делителя. Полученньй на выходах одноразрядных сумматоров этих ячеек код может быть первым очередным остатком Q, если его величина по модулю больше делителя. Если это так (проверка условия /Q о осуществляется nepBbiM элементом группы ИСКЛЮЧАЮЩЕЕ ИЛИ 5), то код с выходов сумматоров ячеек первой строки матрицы через первые входы коммутаторов этих же ячеек передается в ячейки второй строки без изменения. В противном случае, он восстанавливается путем передачи кода Q через вторые входы коммутаторов. Таким образом, на выходах коммутаторов ячеек первой строки матрицы формируется первый очередной остаток Q,.

Аналогичным образом происходит определение второго очередного остатка Q, вычисляемого в ячейках I второй строки матрицы, В сумматорах этих ячеек вычисляется разность и если, QI / / у (в этом случае на втором элементе ИСКЛЮЧА ОШЕЕ ИЛИ 5 - 1), на выходах коммутаторов ячеек форми31462297

в против- (К+1)-го одноразрядного полусумруется QJ, , равный Q,-y ном случае Q равен Q.

В последующих строках матрицы выполняются те же действия. Окончательный остаток от деления Q формируется на выходах I6 устройства .

Помимо функции управления коммутаторами ячеек при вычислении очередных остатков, каждый р-й элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5 группы совместно с р-ым элементом ИСКЛЮЧАЮПЩЕ ИЛИ 6 группы Участвует в формировании р-й цифры частного. Значение р-й цифры частного равно 1, если /Qg.i/7//y( 15

10

О, если/р., для случая.

iinii

20

или

когда знаки делимого и делителя равны. Когда знаки делимого и делителя не равны, то условие, по которому определяется р-я цифра частного, меняется на противоположное. Последнее обеспечивается инвертированием сигналов, проходящих через группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6, когда знак частного равен единице.

Полусумматоры 2 и .сумматоры 3 . групп обеспечивают коррекцию (округление) мантиссы частного. Необходимость округления обусловлена особенностью деления чисел в дополнительных кодах,требующей вычисления (Н+О-й цифры частного (что выполняется группой сумматоров 3 и элементом И 9), с последующим добавлением ее в младший разряд результата (выполняется в группе полусумматоров 2).. Формула изобретения

1. Матричное устройство для деления , содержащее матрицу ячеек, группу полусумматоров одноразрядных, группу одноразрядных сумматоров, пер- вую группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент НЕ, причем п арвый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к входам знаков делимого и делителя устройства, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом знака частного устройства, выходы одноразрядных полусумматоров группы являются соответствующими выходами частного группы устройства, выход переноса (К+1)-го (К 1-N-1, N- разрядность частного) одно-разрядного сумматора группы соединен с вхо- .дом переноса К-го одноразрядного сумматора группы, выход переноса

25

30

матера группы соединен с входом переноса К-го одноразрядного полусумматора группы, вход переноса К-й ячейки р-й строки матрицы соединен с выходом переноса (К+1)-й ячейки р-й строки матрицы (р 1-№) , управляющий вход (К+1)-й ячейки р-й строки матрицы соединен с управляющим выходом К-й ячейки р-й строки матрицы, первый выход р-й ячейки К.г-й строки матрицы соединен с первым информационным входом р-й ячейки (К+1)-й строки матрицы, второй выход (К+15-Й ячейки К-й строки матрицы со единен с вторым информационным входом К-й ячейки (К+1)-й строки матрицы, выход р-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединен с управляющим входом первой ячейки р-й строки матрицы, вторые выходы ячеек последней строки матрицы являются соответствующими выходами остатка группы устройства и соединены с вхо дами первых слагаемых соответствующих одноразрядных сумматоров группы входы, кроме первого, делимого Г|туп пы устройства соединены соответственно с вторыми информационными вхо дами р-ых ячеек первой строки и N-ы ячеек (К+О-й строки матрицы, отличающееся тем,что, с целью сокращения аппаратурных затрат, оно содержит вторую и третью группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, причем входы делителя группы уст ройства соединены с входами соответ ствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

40 второй группы, выходы которых соеди нены с первыми информационными входами соответствующих ячеек первой строки матрицы, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом вто45 рого слагаемого первого одноразрядного сумматора группы, с первыми вх дами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ трет ей группы и с входом элемента НЕ, в ход которого соединен с вторыми вхо

5о дами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, с входами переноса N-ых ячеек р-й строки матрицы и с первым входом элемента И, выход которого соединен с входом переноса N-ro

55 одноразрядного сумматора группы, первые выходы ячеек N-й строки матрицы соединены соответственно с вхо дами второго слагаемого (К+1)-го од норазрядного сумматора группы и с

35

5

0

5

0

матера группы соединен с входом переноса К-го одноразрядного полусумматора группы, вход переноса К-й ячейки р-й строки матрицы соединен с выходом переноса (К+1)-й ячейки р-й строки матрицы (р 1-№) , управляющий вход (К+1)-й ячейки р-й строки матрицы соединен с управляющим выходом К-й ячейки р-й строки матрицы, первый выход р-й ячейки К.г-й строки матрицы соединен с первым информационным входом р-й ячейки (К+1)-й строки матрицы, второй выход (К+15-Й ячейки К-й строки матрицы соединен с вторым информационным входом К-й ячейки (К+1)-й строки матрицы, выход р-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединен с управляющим входом первой ячейки р-й строки матрицы, вторые выходы ячеек последней строки матрицы являются соответствующими выходами остатка группы устройства и соединены с входами первых слагаемых соответствующих одноразрядных сумматоров группы, входы, кроме первого, делимого Г|туп- пы устройства соединены соответственно с вторыми информационными входами р-ых ячеек первой строки и N-ых ячеек (К+О-й строки матрицы, отличающееся тем,что, с целью сокращения аппаратурных затрат, оно содержит вторую и третью группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, причем входы делителя группы устройства соединены с входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

0 второй группы, выходы которых соединены с первыми информационными входами соответствующих ячеек первой строки матрицы, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом вто5 рого слагаемого первого одноразрядного сумматора группы, с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ третьей группы и с входом элемента НЕ, выход которого соединен с вторыми вхоо дами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, с входами переноса N-ых ячеек р-й строки матрицы и с первым входом элемента И, выход которого соединен с входом переноса N-ro

55 одноразрядного сумматора группы, первые выходы ячеек N-й строки матрицы соединены соответственно с входами второго слагаемого (К+1)-го одноразрядного сумматора группы и с

5

вторым входом элемента И, первый вход делимого группы устройства соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы второй выход первой ячейки К-й строки матрицы соединен с первым входом (К+1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, выход переноса перовой ячейки р-й строки соединен с . Ьторым входом р-го элемента ИСКЛЮЧА- ЮЩЕЕ ИЛИ первой группы, выход кото- рого соединен с вторым входом р-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ третьей труп-: ;пы, ВЫХОД которого соединен с входом I слагаемого одноразрядного полу- Iсумматора группы, выход суммы первого Iодноразрядного сз мматора грзшпы сое- |динен с входом переноса N-ro однораз- рядного полусумматора группы. 1: 2, Устройство по п. Г, о т л и - чающееся тем, что ячейка матрицы содержит одноразрядный сумматор и одноразрядньй коммутатор, причем первый информационный вход ячейки матрицы соединен с входом первого слагаемого одноразрядного сумматора и является первым выходом ячейки матрицы,второй выход которой соединен с выходом одноразрядного коммутатора,управляющий вход которого соединен с уп- равляющими входом и выходом ячейки матрицы, вход и выход переноса которой соединены соответственно с входом и вькодом переноса одноразрядного сумматора, выход суммы которого соединен с первым информационным входом одноразрядного коммутатора, второй информационный вход которого соединен с входом второго слагаемого одноразрядного сумматора и с вторым информационным входом ячейки матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ И ДЕЛЕНИЯ | 1991 |

|

RU2018932C1 |

| Матричное вычислительное устройство | 1983 |

|

SU1124284A1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Матричное устройство для деления | 1987 |

|

SU1511748A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1984 |

|

SU1171787A1 |

| Ячейка однородной структуры | 1990 |

|

SU1805461A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

Изобретение относится к в ычис- лительной технике и может быть ис- подьзовано при построении однотактных матричных делителей повьгаенного бы-- стродействия. Целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что матричное устройство для деления, содержащее матрицу ячеек 1, группу одноразрядных полусумматоров 2 группу одноразрядных сумматоров 3, группу элементов ИСКЛЮЧАЮЩЕЕ ШШ 5, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и элемент НЕ 8, содержит группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4,6 и элемент И 9 с соответствующими связями. 1 з.п..ф-лы, 2 ил.

ЧИ

23

о

2

J/ X

F

фие,2

2Z

О

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Матричное устройство для деления /его варианты/ | 1981 |

|

SU1035602A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1987-08-05—Подача