Изобретение относится к вычислительной технике и предназначено для выполнения быстрого преобразования Фуръе (БПФ), которое используется при цифровой обработке сигналово

Цепь изобретения - сокращение аппаратурных затрато

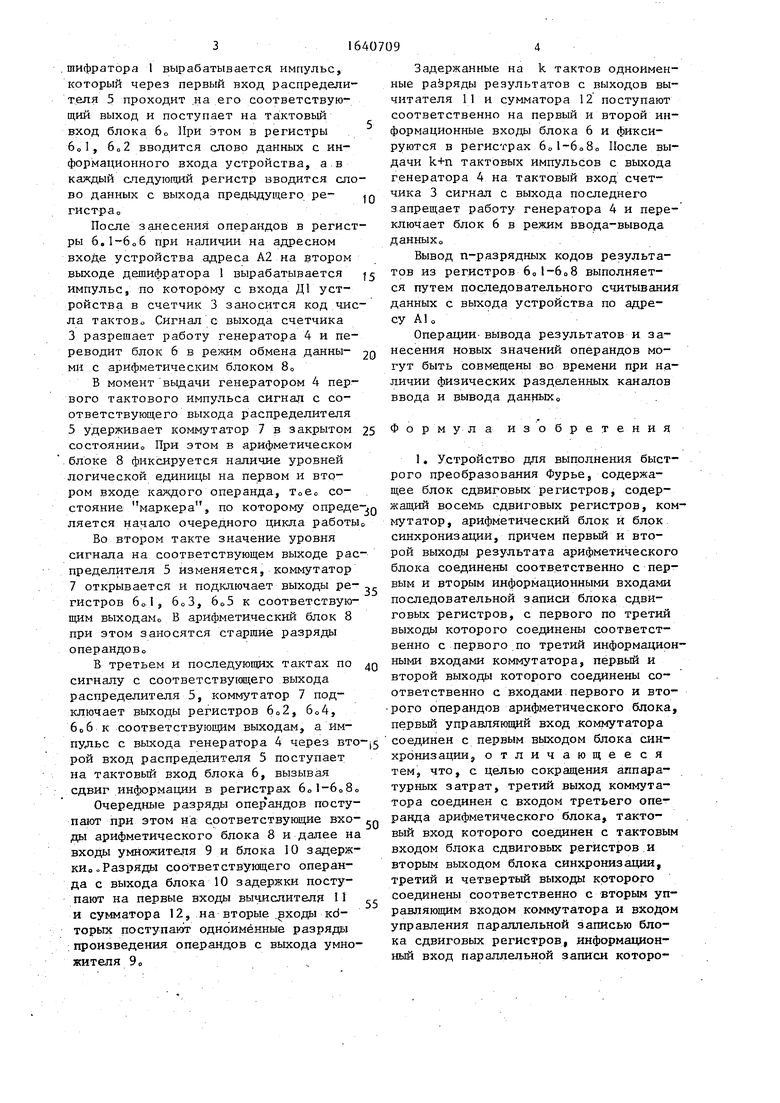

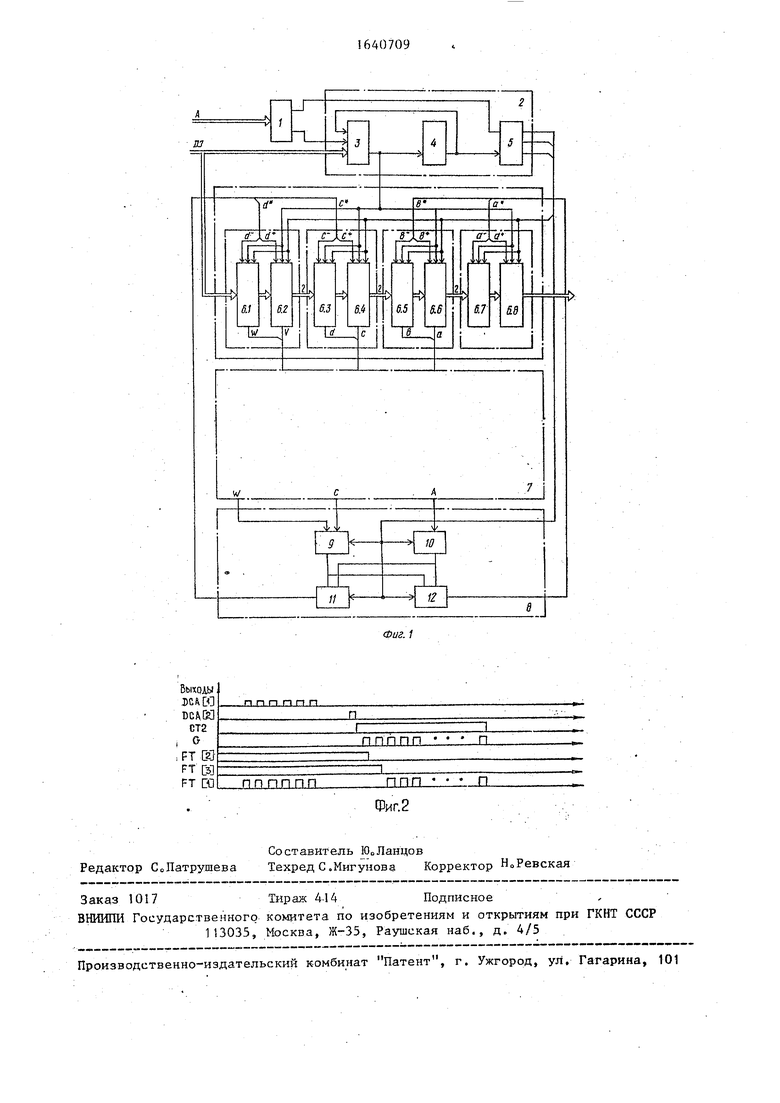

На фиг„1 представлена схема устройства; на фиг02 - временная диаграмма работы устройства,,

Устройство содержит дешифратор 1 адреса; блок 2 синхронизации, содержащий счетчик 3 тактов, управляемый генератор 4 и распределитель 5 синхросигналов, блок 6 сдвиговых регистров, содержащий восемь сдвиговых регистров 6Л-6..8, коммутатор 7, арифмети-.

ческий блок 8, содержащий конвейерный умножитель 9 комплексных последовательных знакоразрядных двоичных чисел 7, блок 10 задержки, конвейерный вычитатель 11 комплексных последовательных знакоразрядных двоичных чисел и конвейерный сумматор 12 комплексных последовательных знакоразряД ных двоичных чисел.

Устройство работает следующим об разом

Перед выполнением БПФ сигнал с выхода счетчика 3 запрещает работу генератора 4 и устанавливает блок 6 в режим ввода-вывода данных (фиг,, 2)0 При наличии адреса А1 на адресном i входе устройства на первом выходе де-

G5 Ј

шифратора 1 вырабатывается импульс, который через первый вход распределителя 5 проходит на его соответствующий выход и поступает на тактовый вход блока 6о При этом в регистры 6„1, 6„2 вводится слово данных с информационного входа устройства, а в каждый следующий регистр вводится слово данных с выхода предыдущего ре- J гистра„

После занесения операндов в регистры 6.1-6о6 при наличии на адресном входе устройства адреса А2 на втором выходе дешифратора 1 вырабатывается | импульс, по которому с входа Д1 устройства в счетчик 3 заносится код числа тактов Сигнал с выхода счетчика 3 разрешает работу генератора 4 и переводит блок 6 в режим обмена данны- 2 ми с арифметическим блоком 80

В момент выдачи генератором 4 первого тактового импульса сигнал с соответствующего выхода распределителя 5 удерживает коммутатор 7 в закрытом состоянии При этом в арифметическом блоке 8 фиксируется наличие уровней логической единицы на первом и втором входе каждого операнда, т0ес состояние маркера, по которому опреде-j ляется начало очередного цикла работы

Во втором такте значение уровня сигнала на соответствующем выходе распределителя 5 изменяется, коммутатор 7 открывается и подключает выходы регистров 601, 6оЗ, 605 к соответствующим выходамо В арифметический блок 8 при этом заносятся старшие разряды операндов

В третьем и последующих тактах по 4 сигналу с соответствующего выхода распределителя 5, коммутатор 7 подключает выходы регистров 602, 604, 606 к соответствующим выходам, а импульс с выхода генератора 4 через второй вход распределителя 5 поступает на тактовый вход блока 6, вызывая сдвиг информации в регистрах 601-608,

Очередные разряды опер андов поступают при этом на соответствующие вхо- „ ды арифметического блока 8 и далее на входы умножителя 9 и блока 10 задержки,, „Разряды соответствующего операнда с выхода блока 10 задержки поступают на первые входы вычислителя 11 „ и сумматора 12, на вторые входы ко1- торых поступают одноимённые разряды произведения операндов с выхода умножителя 90

2

3

Задержанные на k тактов одноименные разряды результатов с выходов вы- читателя 11 и сумматора 12 поступают соответственно на первый и второй информационные входы блока 6 и фиксируются в регистрах 6о1-6 8о После выдачи k+n тактовых импульсов с выхода генератора 4 на тактовый вход счетчика 3 сигнал с выхода последнего запрещает работу генератора 4 и переключает блок 6 в режим ввода-вывода данных

Вывод n-разрядных кодов результатов из регистров 6с,1-6о8 выполняется путем последовательного считывания данных с выхода устройства по адресу А о

Операции вывода результатов и занесения новых значений операндов могут быть совмещены во времени при наличии физических разделенных каналов ввода и вывода данных„

jQ

25 Формула изобретения

5

1. Устройство для выполнения быстрого преобразования Фурье, содержащее блок сдвиговых регистров, содержащий восемь сдвиговых регистров, коммутатор, арифметический блок и блок синхронизации, причем первый и второй выходы результата арифметического блока соединены соответственно с первым и вторым информационными входами последовательной записи блока сдвиговых регистров, с первого по третий выходы которого соединены соответственно с первого по третий информационными входами коммутатора, первый и второй выходы которого соединены соответственно с входами первого и второго операндов арифметического блока, первый управляющий вход коммутатора соединен с первым выходом блока синхронизации, отличающееся тем, что, с целью сокращения аппаратурных затрат, третий выход коммутатора соединен с входом третьего операнда арифметического блока, тактовый вход которого соединен с тактовым входом блока сдвиговых регистров и вторым выходом блока синхронизации, третий и четвертый выходы которого соединены соответственно с вторым управляющим входом коммутатора и входом управления параллельной записью блока сдвиговых регистров, информационный вход параллельной записи которо

го соединен с входом задания режима работы блока синхронизации и подключен к входу загрузки данных устройства, четвертый выход блока сдвиговых регистров является выходом устройства, вход запуска и вход задания режима загрузки устройства подключены соответственно к первому и второму входам задания режима блока син- хронизации, причем в блоке сдвиговых регистров информационный вход параллельной записи первого сдвигового регистра является информационным входом параллельной записи блока, выход параллельной информации 1-го сдвигового регистра (,7) соединен с информационным входом параллельной записи (i-H)-ro сдвигового регистра, выход параллельной информации восьмо го сдвигового регистра является четвертым выходом блока, тактовые входы всех сдвиговых регистров соединены между собой и подключены к тактовому входу блока, вход управления парал- лельной записью которого подключен к одноименным входам всех сдвиговых регистров, информационные входы послдовательной записи с первого по четпервый информационный вход последовательной записи блока, второй информационный вход которого образуют информационные входы последовательной записи с пятого по восьмой сдвиговых регистров, выходы последовательной информации первого и второго сдвиговых регистров образуют третий выход блока, первый и второй выходы которого образуют выходы последовательной информации третьего, четвертого и пятого, шестого сдвиговых регистров,,

20 Устройство по По 1, о т л и - чающееся тем, что арифметический блок содержит умножитель, сумматор, вычитатель и узел задержки, выход которого соединен с первыми входами сумматора и вычитателя, вторые входы которых соединены с выходом умножителя, тактовый вход которого соединен с тактовыми входами сумматора и вычитателя и является тактовым входом блока, выходы сумматора и вычитателя являются соответственно первым и вторым выходами результата блока, входы коэффициентов, первого и второго операндов являются соответственно первым входом умножителя, вторым входом

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1312611A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для трехточечного быстрого преобразования Фурье | 1983 |

|

SU1107132A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1013971A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для вычисления функций | 1987 |

|

SU1411775A1 |

Устройство предназначено для выполнения быстрого преобразования Фурье (БПФ), которое используется при цифровой обработке сигналов, и может применяться в качестве сопро- i цессора универсальной микроЭВМ для повышения ее производительности при вычислении спектра сигналов и их фильтрации в частотной области Цель изобретения - сокращение объема аппаратурных затрате Устройство содержит арифметический блок, блок сдвиговых регистров, содержащий восемь сдвиговых регистров, блок синхронизации и коммутатора Устройство выполняет базовую операцию БПФ над данными, Хранящимися в памяти микроЭВМ в виде таблицы элементов выборки и таблицы поворотных множителей о Выборка данных из таблиц, передача их в устройство и прием результатов вычислений выполняются под управлением микроэвм, 1 з о п. ф-лы, 2 ил о (О (Л

вертый сдвиговых регистров образуют 30 умножителя и входом узла задержкИо

| Микропроцессорные средства и системы, 1986, № 2, с 230 рис030 Авторское свидетельство СССР № 1312611, кло G 06 F 15/332, 1985, |

Авторы

Даты

1991-04-07—Публикация

1988-03-30—Подача