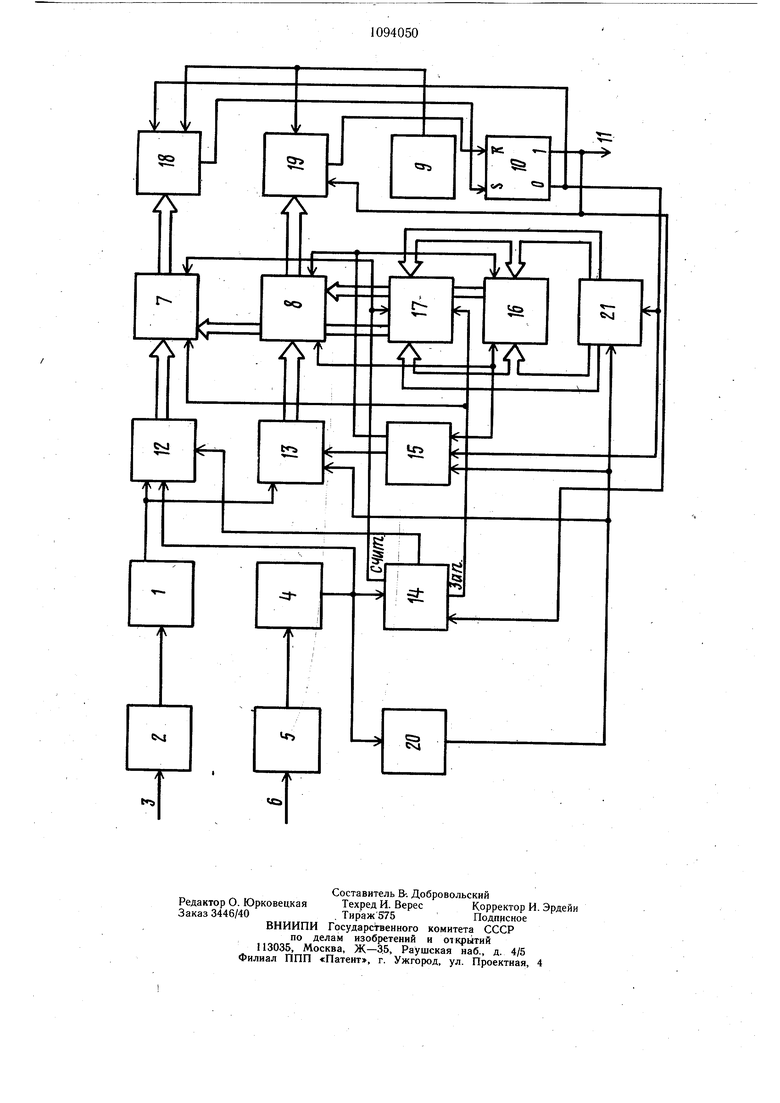

Изобретение относится к магнитной записи, а именно к устройствам для воспроизведения магнитной записи. Известно устройство для воспроизведения магнитной записи, содержащее соединенные между собой умножитель, формирователь импульсов перехода через ноль, блок памяти, генератор и формирователи импульсов 1 . Недостаток устройства состоит в значительной погрешности воспроизведения вследствие малого днапазона компенсации временных искажений. Известно также устройство для воспроизведения магнитной записи, содержащее последовательно соединенные генератор, формирователь импульсов, формирователь импульсов перехода через ноль и триггер, соединенный выходом с первым входом элемента И-НЕ, второй вход которого подключен к другому входу формирователя импульсов перехода через ноль, входу дополнительного формирователя импульсов перехода через ноль и входу умножителя, подсоединенного выходом через блок памяти к одному из входов триггера, а также содержащее дополнительные генератор, триггеры и корректирующий счетчик 2. Недостаток известного устройства состоит в большой погрешности воспроизведения вследствие низкого диапазона компенсации временных искажений из-за малого быстродействия устройства компенсации. Цель изобретения - снижение погрешности воспроизведения путем повь1шения быстродействия компенсации временных искажений. Для достижения цели в устройство для воспроизведения магнитной записи, содержащее умножитель, подключенный входом через первый формирователь импульсов к первой входной шине, формирователь импульсов перехода через ноль, входом подсоединенный через второй, формирователь импульсов к второй входной шине, первый и второй блоки памяти, генератор, триггер, прямым выходом соединенный с выходной шиной, введены первый и второй преобразователи кода, первый и второй блоки управления, первый и второй селекторы кода, первый и второй блоки сравнения, инвертор и формирователь кода, причем первые входы первого и второго преобразователей кода подключены к выходу умножителя, второй вход первого преобразователя кода подсоединен к выходу формирователя импульсов перехода через ноль и входам первого блока управления и инвертора, второй вход второго преобразователя кода соединен с выходом инвертора и с входами второго блока управления и формирователя кода, входы установки первоЩ и второго преобразователей кода подключены к установочным выходам соответственно первого и второго блоков управления, выходы считывания и записи первого блока управления подсоединены к входам соответственно считывания и записи первого блока памяти и второго селектора кода выхо ды считывания и записи второго блока управ ления соединены с входами соответственно считывания и записи первого селектора кода и второго блока памяти, выходы формирователя кода подключены к входам первого и второго селекторов кода, выходы которых подсоединены к адресным входам соответственно второго и первого блоков памяти, соединенных входами с выходами соответственно второго и первого преобразователей кода, при этом выходы первого и второго блоков памяти подключены к входам соответственно первого и второго блоков сравнения, счетными входами подсоединенных к выходу генератора, соединенных входами установки соответственно с инверсным и прямым выходами триггера и управляющими входами соответственно второго и первого блоков управления, входы-установки в «1 и в «О триггера подключены к выходам соответственно первого и второго блоков сравнения, а инверсный выход триггера - к управляющему входу формирователя кода. Это приводит к расширению диапазона компенсации временных искажений вследствие повышения быстродействия процесса обработки сигнала воспроизведения. На чертеже приведен один из возможных вариантов устройства для воспроизведения магнитной записи. Устройство содержит умножитель 1, подключенный входом через первый формирователь 2 импульсов к первой входной шине 3, формирователь 4 импульсов перехода через ноль, входом подсоединенный через второй формирователь 5 импульсов к второй входной шине 6, первый и второй блоки 7 и 8 памяти, генератор 9, триггер 10, прямым выходом соединенный с выходной шиной 11, первый и второй преобразователи 12 и 13 кода, первый и второй блоки 14 и 15 управления, первый и второй селекторы 16 и 17 кода, первый и второй блоки 18 и 19 сравнения, инвертор 20 и формирователь 21 кода, причем первые входы первого и второго преобразователей 12 и 13 подключены к выходу умножителя 1, второй вход первого преобразователя 12 кода - к выходу формирователя 4 импульсов перехода через ноль и входам первого блока 14 управления и инвертора 20, второй вход второго преобразователя 13 кода соединен с выходом инвертора 20 и входами второго блока 15 управления и формирователя 21 кода, входы установки первого и второго /

преобразователей 12 и 13 кода подключены к установочным выходам соответственно первого и второго блоков 14 и 15 управления, выходы считывания и записи первого блока 14 управления - к входам соответственно считывания и записи первого блока 7 памяти и второго селектора 17 кода, выходы считывания и записи второго блока 15 управления соединены с входами соответственно считывания и записи первого селектора 16 кода и второго блока 8 памяти, выходы формирователя 21 кода - с входами первого и второго селекторов 16 и 17 кода, выходы которых подсоединены к адресным входам соответственно второго и первого блоков 8 и 7 памяти, соединенных входами с выходами соответственно второго и первого преобразователей 13 и 12 кода, при этом выходы первого и второго блоков 7 и 8 памяти подключены к входам соответственно первого и второго блоков 18 и 19 сравнения, подсоединенных счетными входами к выходу генератора 9, соединенных входами установки соответственно с инверсным и прямым выходами триггера 10 и с управляющими входами соответственно второго и первого блоков 15 и 14 управления, входы установки в «1 и в «О триггера 10 подключены к выходам соответственно первого и второго блоков 18 и 19 сравнения, а инверсный выход триггера 10 - к управляющему входу формирователя 21 кода.

Информационный сигнал поступает на вторую входную шину 6, а сигналы контрольного канала - на первую входную щину 3. Частота импульсов контрольного канала определяется точностью компенсации, а скорость работы устройства задается умножителем 1. При положительном информационном импульсе работает первый преобразователь 12 кода, а при отрицательном информационном импульсе включается второй преобразователь 13 кода. По окорчании положительного импульса первый блок 14 управления разрешает запись в первый блок 7 памяти и во второй селектор 17 импульсов. При этом сигнал записывается в первый блок 7 памяти по адресу, который формируют формирователь 21 кода и первый селектор 16 импульсов. По окончании записи в первый блок 7 памяти первый блок 14 управления формирует сигнал сброса первого преобразователя 12 кода. Запись во второй блок 8 памяти происходит по окончании отрицательного импульса аналогично. Код адреса последовательно изменяется при поступлении каждого следующего отрицательного импульса. После

накопления в формирователе 21 кода адреса записи, соответствующего половине объема памяти, считывание производится до этого момента из одной и той же ячейки памяти первого и второго блоков 7 и 8 па-мяти при помощи сигналов, вырабатываемых первым и вторым блоками 14 и 15 управления. Первый и второй блоки 14 и 15 управления анализируют возможность считывания из первого и второго блоков 7 и 8 памяти без сбоя записи. По сигналу считывания из первого блока 14 управления производится считывание из первого блока 7 памяти по адресу считывания, вырабатываемому в формирователе 21 кода и проходящему через первый . селектор 16 кода. Код из первого блока 7 памяти считывается в первый блок 18 сравнения. При поступлении во второй блок 19 сравнения сигнала с инверсного выхода триггера 10 открывается счетный вход первого блока 18 сравнения, на который поступают импульсы стабильной частоты с генератора 9. В момент совпадения числа, накопленного в первом блоке 18 сравнения, и числа с выхода первого блока 7 памяти на выходе первого блока 18 сравнения формируется импульс, который устанавливает триггер 10 в единичное состояние, тем самым форми)уя сигнал для счета во втором блоке 19 сравнения и сигнал считывания в первом блоке 14 управления, а также сбрасывая в ноль накопленную по счетному входу информацию в первом блоке 18 сравнения. Аналогично происходит считывание из второго блока ,8 памяти. Выходной сигнал триггера 10, длительность которого определяется кодом чисел, записанных в первом и втором блоках 7 и 8 памяти, и кодом чисел, образованных в первом .и втором блоках 18 и 19 сравнения при счете импульсов с генератора 9, поступает на выходную шину 11. Так как при записи контрольного сигнала в процессе магнитной записи используется генератор 9, то происходит компенсация временных искажений, точность которой определяется нестабильностью генератора 9 и разрядностью первого и второго преобразователей 12 и 13 кода. При этом быстродействие определяется только быстродействием первого и второго преобразователей 12 и 13 кода и первого и второго блоков 18 и 19 сравнения.

Использование изобретения позволяет значительно снизить погрещность воспроизведения вследствие существенного расширения динамического диапазона при записи методом частотной модуляции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоканальной магнитной записи и воспроизведения | 1980 |

|

SU960926A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Устройство для управления автономным инвертором | 1990 |

|

SU1810973A1 |

| Устройство для обучения | 1983 |

|

SU1088053A1 |

| Способ записи - воспроизведения цифровой информации и устройство для его осуществления | 1990 |

|

SU1721630A1 |

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

| Аналого-цифровое вычислительное устройство | 1988 |

|

SU1501103A1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ МАГНИТНОЙ ЗАПИСИ, содержащее умножитель, . подключенный входом через первый формирователь импульсов к первой входной шине, формирователь импульсов перехода через ноль, входом подсоединенный через второй формирователь импульсов к второй входной шине, первый и второй блоки памяти, генератор, триггер, прямым выходом соединенный с выходной шиной, отличающееся тем, что, с целью снижения погрешности воспроизведения путем повышения быстродействия компенсации временных искажений, в него введены первый и второй преобразователи кода, первый и второй -блоки управления, первый и второй .селекторы кода, первый и второй блоки сравнения, инвертор и формирователь кода, причем первые входы первого и второго преобразователей кода подключены к выходу умножителя, второй вход первого преобразователя кода подсоединен к выходу формирователя импульсов перехода через ноль и входам первого блока управления и ин.вертора, второй вход второго преобразова. теля кода соединен с выходом инвертора и с входами второго блока управления и формирователя кода, входы установки первого и второго преобразователей кода подключены к установочным выходам соответственно первого и второго .блоков управления, выходы считывания и записи первого блока управления подсоединены к входам соответственно считывания и записи первого блока памяти и второго селектора кода, выходы считывания и записи второго блока управления соединены ,с входами соответственно считывания и записи первого селектора кода и второго блока памяти, выходы формирователя кода подключены к входам первого и второго селекторов кода, выходы § которых подсоединены к адресным входам соответственно второго и первого блоков памяти, соединенных входами с выходами соответственно второго и первого преобразователей кода, при этом выходы первого и второго блоков памяти подключены к входам соответственно первого и второго блоков сравнения, подсоединенных счетными входами к выходу генератора, соединенных входами установки соответственно с инСО N о сд версным и прямым выходами триггера и управляющими входами соответственно второго и первого блоков управления, входы установки в «1 и в «О триггера подключены к входам соответственно первого и второго блоков сравнения, a инверсный выход триггера - к управляющему входу формирователя кода.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США, № 3931639, кл | |||

| Способ приготовления искусственной массы из продуктов конденсации фенолов с альдегидами | 1920 |

|

SU360A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3938184, кл. | |||

| Способ приготовления искусственной массы из продуктов конденсации фенолов с альдегидами | 1920 |

|

SU360A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1984-05-23—Публикация

1983-04-26—Подача