Изобретение относится к вычислительной технике и может быть использовано для моделирования непрерывно-дискретных процессов и систем управления в реальном и ускоренном масштабах времени.

Целью изобретения является повышение быстродействия.

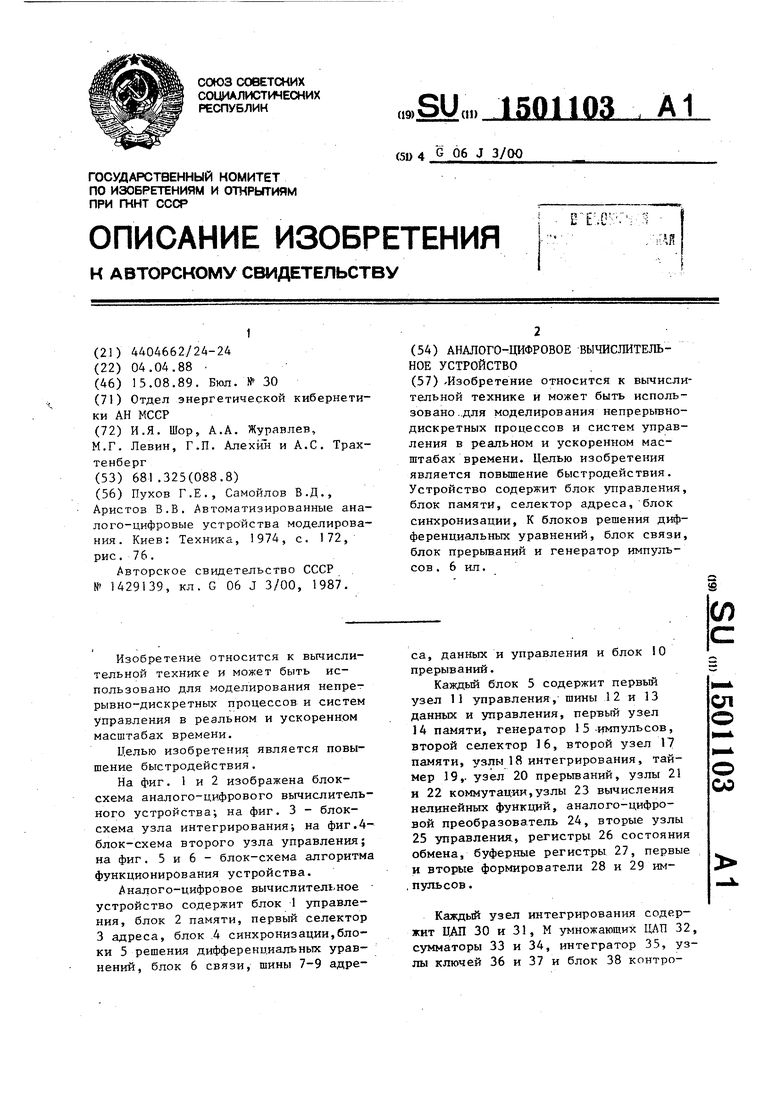

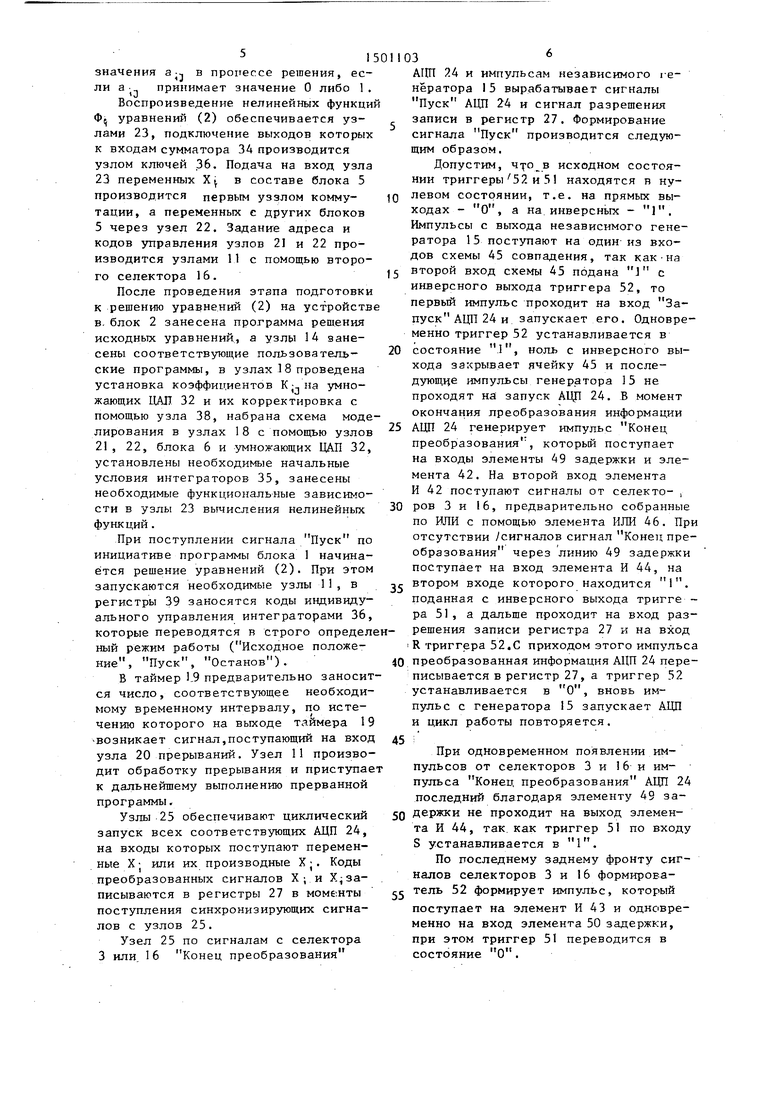

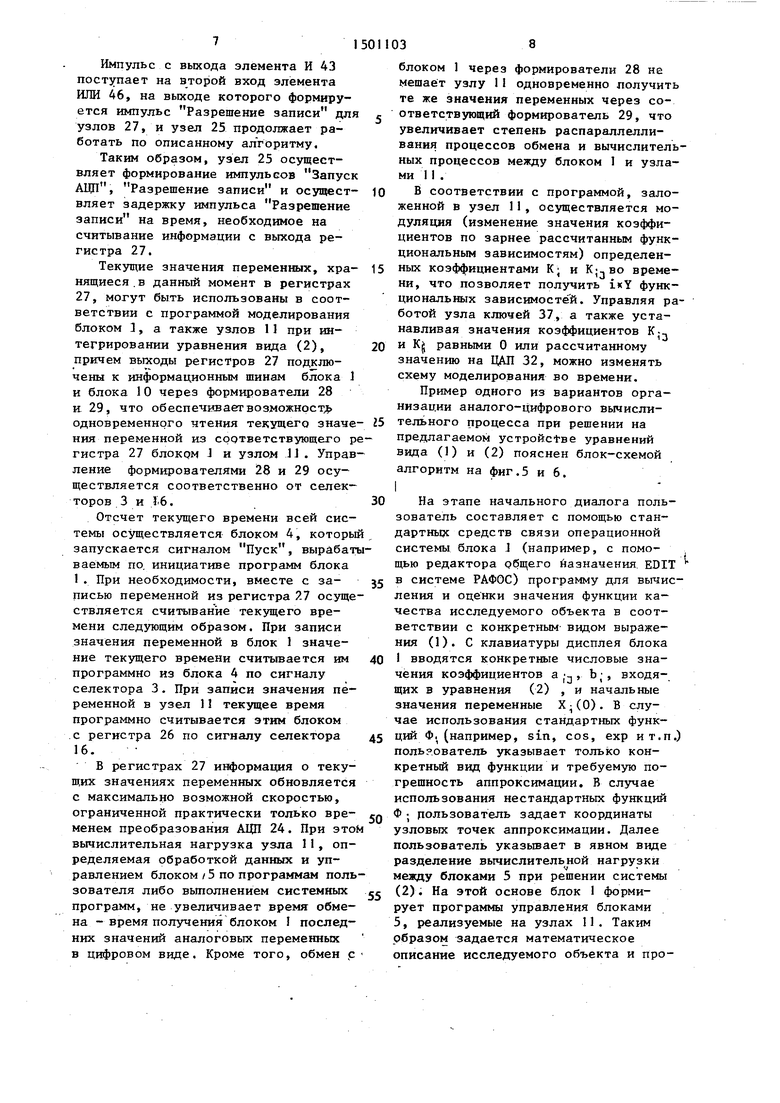

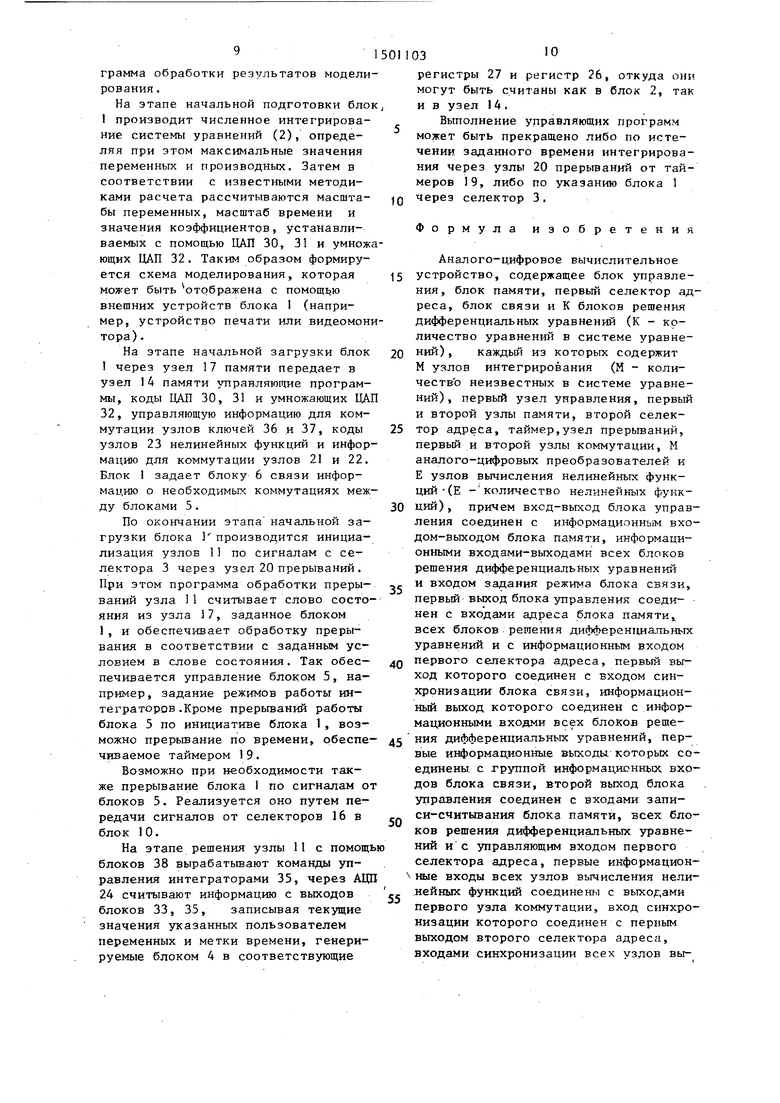

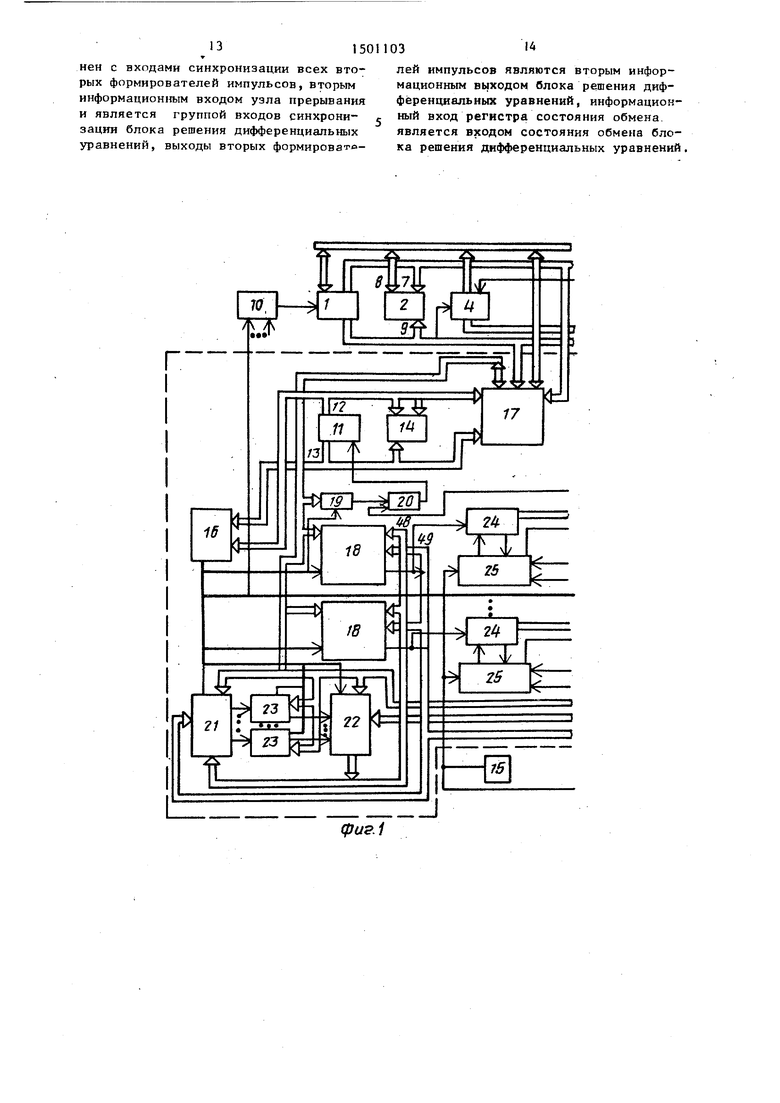

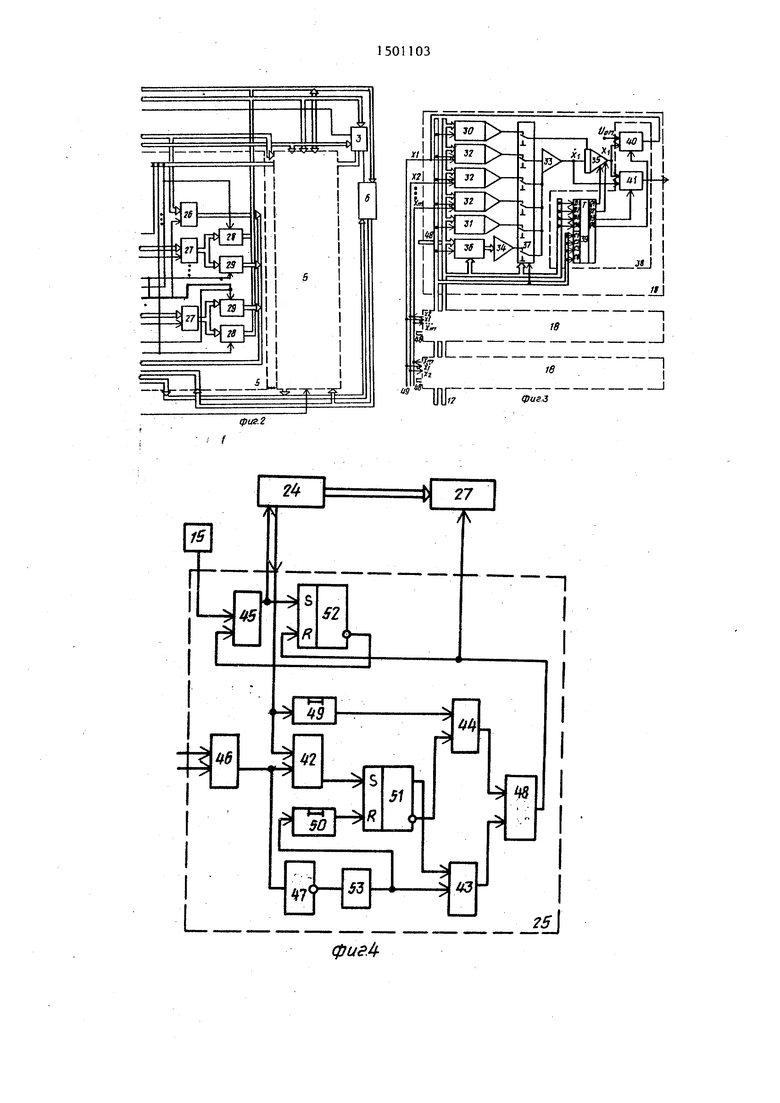

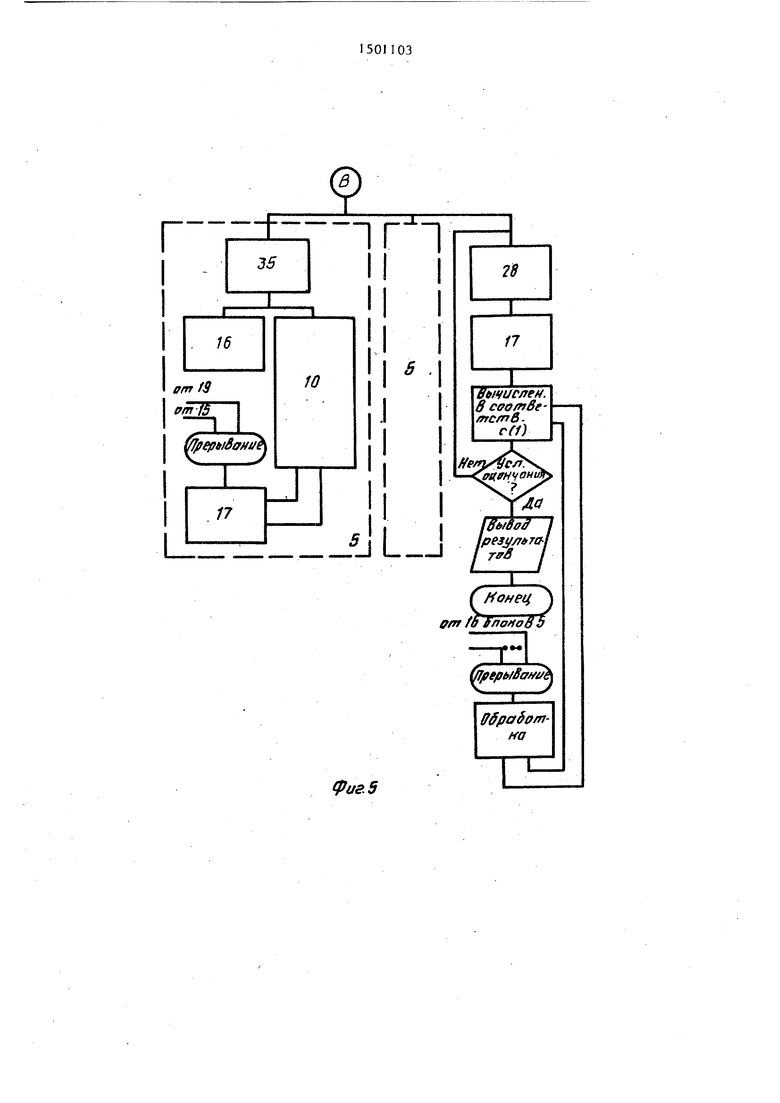

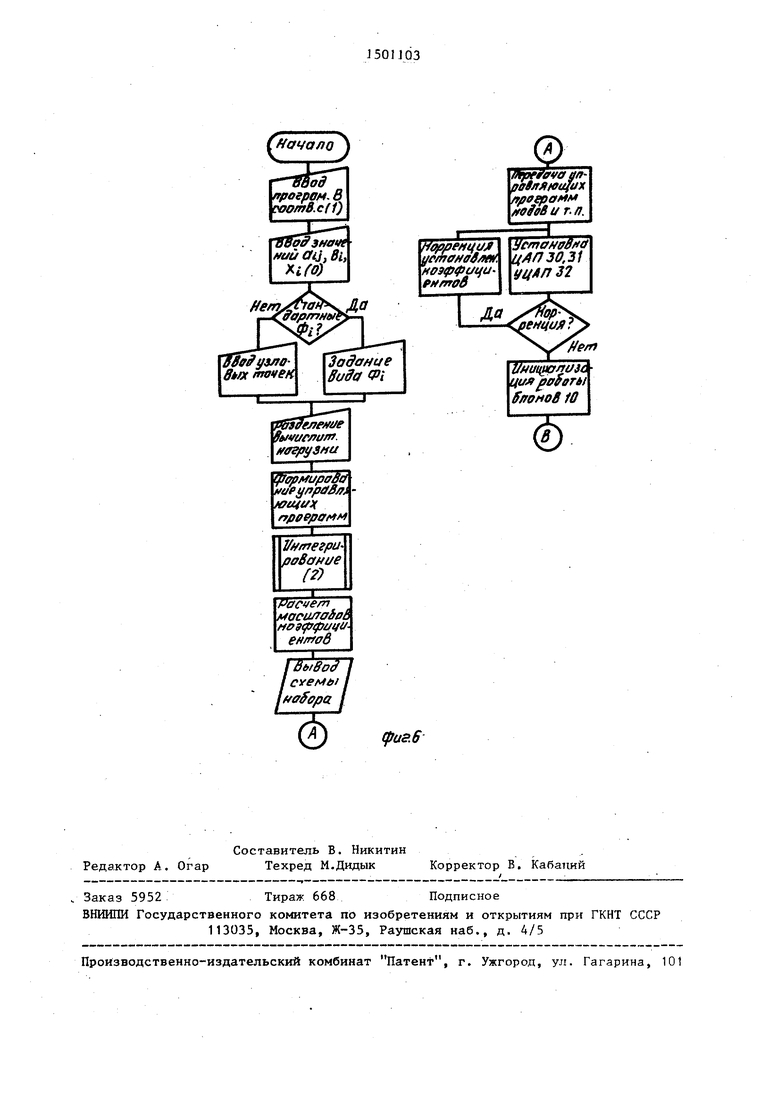

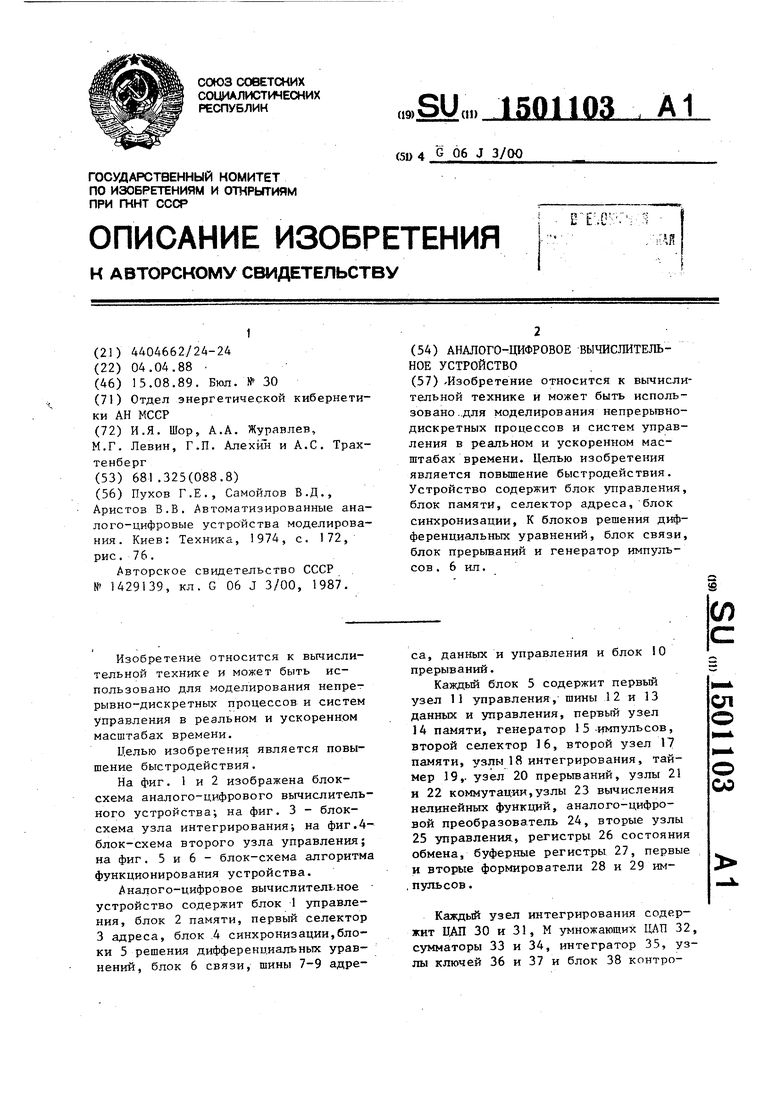

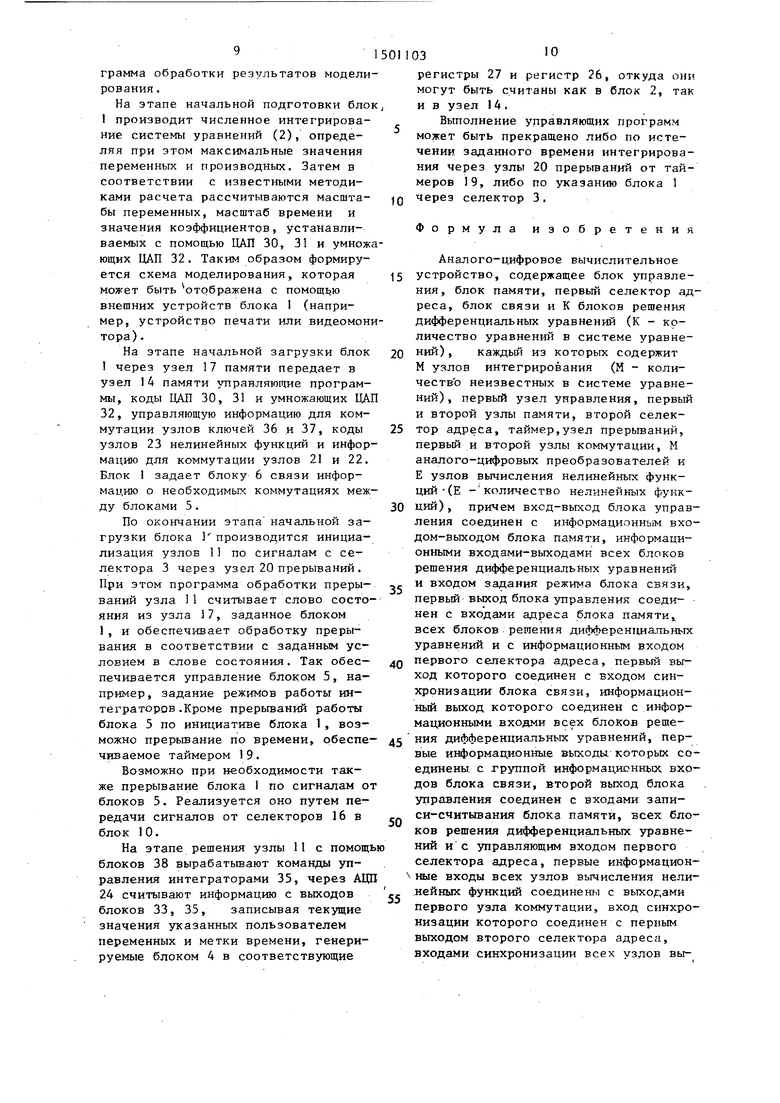

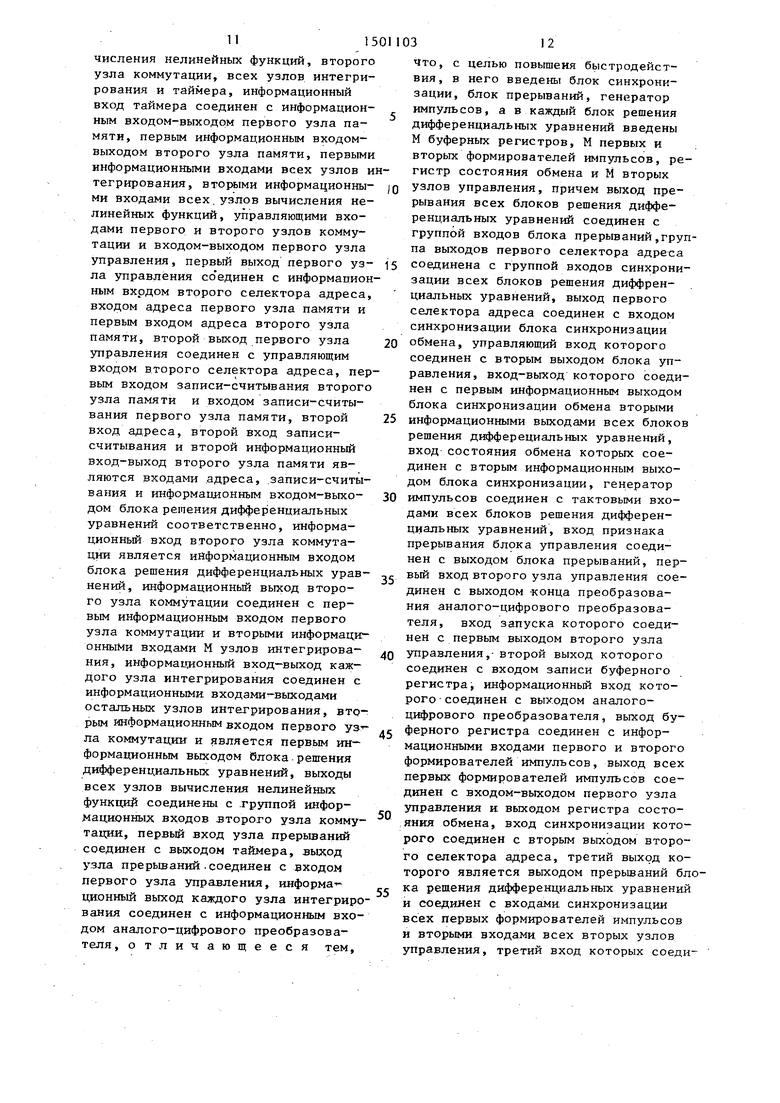

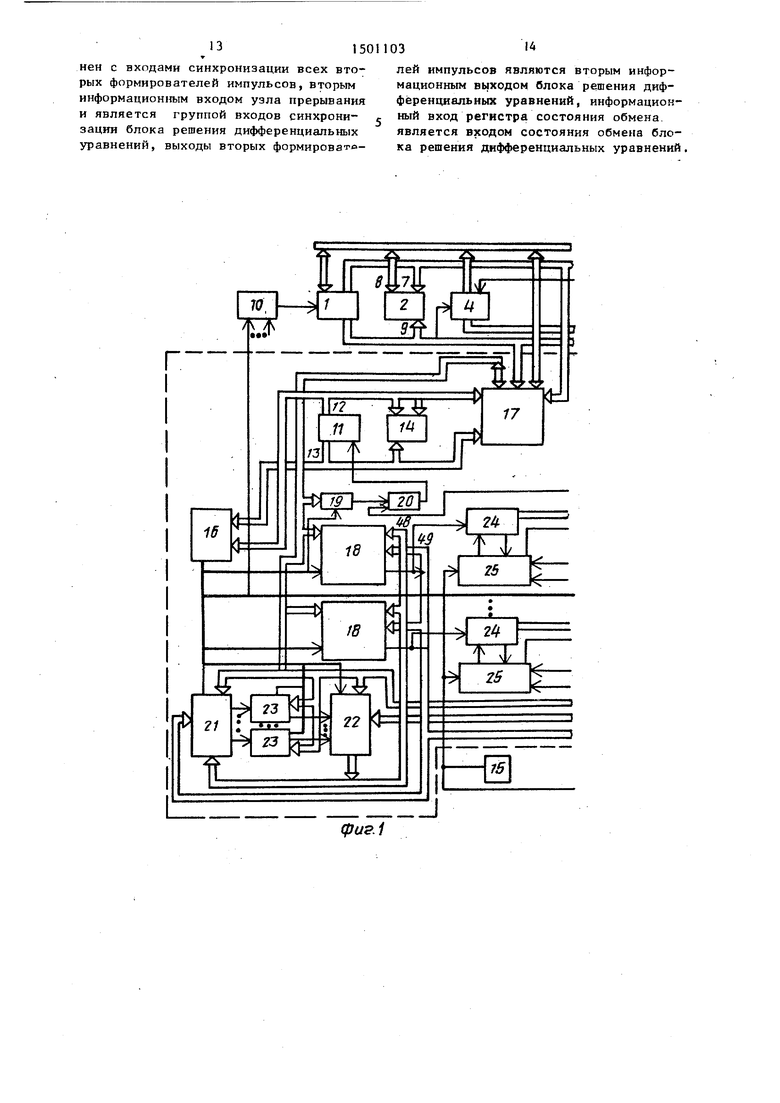

На фиг. 1 и 2 изображена блок- схема аналого-цифрового вычислительного устройства; на фиг. 3 - блок- схема узла интегрирования; на фиг.4- блок-схема второго узла управления; на фиг. 5 и 6 - блок-схема алгоритма функционирования устройства.

Аналого-цифровое вычислительное устройство содержит блок 1 управления, блок 2 памяти, первый селектор 3 адреса, блок .4 синхронизации,блоки 5 решения дифференциальных уравнений, блок 6 связи, шины 7-9 адреса, данных и управления и блок 0 прерываний.

Каждый блок 5 содержит первый узел 11 управления, шины 12 и 13 данных и управления, первьй узел 14 памяти, генератор 15 импульсов, второй селектор 16, второй узел П памяти, узлы 18 интегрирования, таймер 19,. узел 20 прерьгоаний, узлы 21 и 22 коммутации,узлы 23 вычисления нелинейных функций, аналого-цифровой преобразователь 24, вторые узлы 25 управления, регистры 26 состояния обмена, буферные регистры 27, первые и вторые формирователи 28 и 29 им- ,пульсов.

Каждый узел интегрирования содержит ЦДЛ 30 и 31, М умножающих ЦАТ1 32, сумматоры 33 и 34, интегратор 35, узлы ключей 36 и 37 и блок 38 контроел

со

ля. В состав блока 38 входят регистр 39 и коммутаторы 40 и 41.

Каждый узел 25 управления содержит элементы И 42-45, элементы ШШ 46-48, элементы 49 и 50 задержки, триггеры 51 и 52 и формирователь 53 импульсов.

Исходная задача сводится к определению значений

к. де

X

f(X

i i

1.2,

,,Х, , .. .,Х;,Х;, ...,Х„,Хи)(1)

функции качества исследуемого объекта,

.,п) - переменные состояния, получаемые при моделировании динамических процессов, заданных дифференци - альными уравнениями вида

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система | 1987 |

|

SU1429139A1 |

| Аналого-цифровое устройство для решения системы дифференциальных уравнений | 1987 |

|

SU1462378A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1134949A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

Изобретение относится к вычислительной технике и может быть использовано для моделирования непрерывно- дискретных процессов и систем управления в реальном и ускоренном масштабе времени. Целью изобретения является повышение быстродействия. Устройство содержит блок управления, блок памяти, селектор адреса, блок синхронизации, К блоков решения дефференциальных уравнений, блок связи, блок прерываний и генератор импульсов. 6 ил.

X,

П. X,

-...-t- а,.,Хз + ,..+ а,„Х„ + Ь,

X, а;,Х, +...+ a;.,.X.,4...-f , + Ь; + Ф,- Хп а-„,Х, -ь...+ а„-,Х., + ...+ + Ь„ ч- Ф,

при известных начальных условиях Хз(0), v

где Ф; т - нелинейные функции; a;.j- коэффициенты.

На этапе подготовки исходной задачи к решению производится распределение вычислительной нагрузки между процессорами системы таким образом, что уравнения вида (1) решаются блоком 1 , а решение уравнений (2) определяется блоками 5.

Узел I 1 в сост.аве блока 5 предназначен для реализации части алгоритма решения, изменения структуры схемы моделирования в процессе решения, управления коэффициентами в схеме моделирования, реализации ал20

ся коды рассчитанных на блоке 1 коэффициентов , коды узлов точек нели- нейных функцийi коды ухГравления узлов 21 и 22.

Работа программы управления блоками 5 происходит по инициативе программы блока 1, с обеспечнием набора 25 схемы моделирования с помощью блока 6, узлов 21, 22, установки коэффициентов в умножающих ЦАП 32, задания режима работы в процессе решения задачи интеграторов 35 каждого из блоков интегрирования 18. Установка коэффициентов умножающих ЦАП 32 и начальных условий интеграторрв 35 через ЦАП 30 по шине 12 производится с помощью второго селектора 16. В про

30

цессе установки значении коэффициенГОрИТМОВ контроля и диагностики уз- ог -.„.„ „

- - тов K;.jHa умножающих ЦАП 32 коммутатор 40 подключает к входу соответстлов 18 и ряда других функций.

Устройство работает следующим образом.

В исходном состоянии регистр 39 узла 38 обнуляется и на первом и втором входах регистра 39 формируется код 01, в соответствии с которым все 35 устанавливаются в режим Исходное положение. Исходное состоя ние остальных блоков призвольное.

На этапе подготовки загружается в - блок 1 составленная пользователем программа определения Y в соответ - ствии с (1) , вводятся значения коэф- фициентов Ь| и a--j и. описания функций f в уравнениях (2).

Под управлением блока J осуществляется загрузка через узел 1 7 с участием узла JJ и узел 14 программ управления блоками 5 реш,еиия диффе- ренциальных уравнений, а также пользовательских программ, реализующих логические зависимости и численные методы расчетов. В узел 14 передают40

вующего ЦАП 32 опорные напряжения U После записи значения коэффициента К;- в ЦАП 32 осуществляется контроль записанного значения с помощью АЦП 24, вход которого коммутатором 41 подключен к выходу сумматора 33.При этом управление коммутаторами 40 и 41 осуществляется с третьего и чет- вертого выходов регистра 39, информация в который поступает с узла 11.

50

55

Таким образом, с помощью узла 38 устраняется погрешность, вносимая внешними соединительными цепями, так как контроль коэффициентов К;-, осуществляется непосредственно на выходе сумматора 33. С помощью узла-37 ключей входы сумматора 33 узла 18 подключаеются к выходам ПАП 32 или к нулевой шине, причем управление каждым ключом осуществляется от узла 11, что позволяет параллельно менять

+ Ф

1 )

(2)

ся коды рассчитанных на блоке 1 коэффициентов , коды узлов точек нели- нейных функцийi коды ухГравления узлов 21 и 22.

Работа программы управления блоками 5 происходит по инициативе программы блока 1, с обеспечнием набора схемы моделирования с помощью блока 6, узлов 21, 22, установки коэффициентов в умножающих ЦАП 32, задания режима работы в процессе решения задачи интеграторов 35 каждого из блоков интегрирования 18. Установка коэффициентов умножающих ЦАП 32 и начальных условий интеграторрв 35 через ЦАП 30 по шине 12 производится с помощью второго селектора 16. В про

вующего ЦАП 32 опорные напряжения U После записи значения коэффициента К;- в ЦАП 32 осуществляется контроль записанного значения с помощью АЦП 24, вход которого коммутатором 41 подключен к выходу сумматора 33.При этом управление коммутаторами 40 и 41 осуществляется с третьего и чет- вертого выходов регистра 39, информация в который поступает с узла 11.

Таким образом, с помощью узла 38 устраняется погрешность, вносимая внешними соединительными цепями, так как контроль коэффициентов К;-, осуществляется непосредственно на выходе сумматора 33. С помощью узла-37 ключей входы сумматора 33 узла 18 подключаеются к выходам ПАП 32 или к нулевой шине, причем управление каждым ключом осуществляется от узла 11, что позволяет параллельно менять

значения а-, в процессе решения, если а принимает значение О либо 1.

Воспроизведение нелинейных функци Ф, уравнений (2) обеспечивается узлами 23, подключение выходов которых к входам сумматора 34 производится узлом ключей 36. Подача на вход узла 23 переменных Х в составе блока 5 производится первым уззлом коммутации, а переменных с других блоков 5 через узел 22, Задание адреса и кодов управления узлов 21 и 22 производится узлами 11 с помощью второго селектора 16.

После проведения этапа подготовки к решению уравнений (2) на устройств в. блок 2 занесена программа решения исходных уравнений, а узлы 14 занесены соответствующие пользовательские программы, в узлах 18 проведена установка коэффициентов Kj-na умножающих ЦАП 32 и их корректировка с помощью узла 38, набрана схема моделирования в узлах 18 с помощью узлов 21, 22, блока 6 и умножающих ЦАП 32, установлены необходимые начальные условия интеграторов 35, занесены необходимые функциональные зависимости в узлы 23 вычисления нелинейных функций.

При поступлении сигнала Пуск по инициативе программы блока 1 начинается решение уравнений (2). При этом запускаются необходимые узлы 11, в регистры 39 заносятся коды индивидуального управления интеграторами 36, которые переводятся в строго определный режим работы (Исходное положение, Пуск, Останов).

В таймер L9 предварительно заносится число, соответствующее необходимому временному интервалу, истечению которого на выходе таймера 19 -возникает сигнал,поступающий на вход узла 20 прерываний. Узел 11 производит обработку прерывания и приступае к дальнейшему выполнению прерванной программы.

Узлы 25 обеспечивают циклический запуск всех соответствующих АЦП 24, на входы которых поступают переменные X; или их производные X;. Коды преобразованных сигналов X; и X;записываются в регистры 27 в момб-нты поступления синхронизирующих сигналов с узлов 25.

Узел 25 по сигналам с селектора 3 или. 16 Конец преобразования

5

0

АЦП 24 и импульсам независимого генератора 15 вырабатывает сигналы Пуск АЦП 24 и сигнал разращения записи в регистр 27. Формирование сигнала Пуск производится следующим образом.

Допустим, исходном состоянии триггеры 52 и 5 находятся в нулевом состоянии, т.е. на прямых выходах - О, а на инверсных - . Импульсы с выхода независимого генератора 15 поступают на один из входов схемы 45 совпадения, так как-на второй вход схемы 45 подана 1 с инверсного выхода триггера 52, то первый импульс проходит на вход Запуск АЦП 24 и запускает его. Одновременно триггер 52 устанавливается в состояние I, ноль с инверсного выхода закрывает ячейку 45 и после- импульсы генератора 15 не проходят на запуск АЩТ 24. Б момент окончания преобразования информации

5 АЩТ 24 генерирует импульс Конец преобразования , который поступает на входы элементы 49 задержки и элемента 42. На второй вход элемента И 42 поступают сигналы от селекто- ,

0 ров 3 и 16, предварительно собранные по ИЛИ с помощью элемента ИЛИ 46. При отсутствии /сигналов сигнал Конец преобразования через линию 49 задержки

поступает на вход элемента И 44, на

tt 111

c втором входе которого находится

поданная с инверсного выхода тригге - ра 51, а дальше проходит на вход разрешения записи регистра 27 и на вход R триггера 52.С приходом этого импульса

0 преобразованная информация АЦП 24 переписывается в регистр 27, а триггер 52 устанавливается в О, вновь импульс с генератора 15 запускает АЦП и цикл работы повторяется.

5

При одновременном появлении импульсов от селекторов 3 и 16 и импульса Конец преобразования АЦП 24 последний благодаря элементу 49 заQ держки не проходит на выход элемента И 44, так. как триггер 51 по входу S устанавливается в 1.

По последнему заднему фронту сигналов селекторов 3 и 16 формировас тель 52 формирует импульс, который поступает на элемент И 43 и одновременно на вход элемента 50 задержки, при этом триггер 51 переводится в состояние О.

Импульс с выхода элемента И 43 поступает на второй вход элемента ИЛИ 46, на выходе которого формируется импульс Разрешение записи для узлов 27, и узел 25 продолжает работать по описанному алгоритму.

Таким образом, узел 25 осуществляет формирование импульсов Запуск АЦП, Разрешение записи и осуществляет задержку импульса Разрешение записи на время, необходимое на считывание информации с выхода регистра 27.

Текущие значения переменных, хра- 15 ных коэффициентами К; и К;,во временящиеся.в данный момент в регистрах 27, могут быть использованы в соответствии с программой моделирования блоком , а также узлов 11 при интегрировании уравнения вида (2), причем выходы регистров 27 подключены к информационным шинам блока 1 и блока 10 через формирователи 28 к 29, что обеспечивает ВОЗМОЖНОСТИ)

ни, что позволяет получить ixY функциональных зависимосте й. Управляя работой узла ключей 37, а также устанавливая значения коэффициентов К--,

1 j

20 и Kj равными О или рассчитанному значению на ЦАП 32, можно изменять схему моделирования во времени.

Пример одного из вариантов организации аналого-цифрового вычислиодновременного чтения текущего значе- 15 тельного процесса при решении на НИИ переменной из соответствующего ре- предлагаемом устройстве уравнений гистра 27 блокрм J и узлом Л . Управ- ление формирователями 28 и 29 осу- ществляется соответственно от селекторов 3 и } 6.30

Отсчет текущего времени всей системы осуществляется блоком 4, который запускается сигналом Пуск, вырабатываемым по. инициативе программ блока 1. При необходимости, вместе с за- 35 системе РАФОС) программу для вычис- писью переменной из регистра 27 осуще- ления и оценки значения функции ка- ствляется считывание текущего времени след5тощим образом. При записи значения переменной в блок 1 значение текущего времени считьгоается им программно из блока 4 по сигналу селектора 3. При записи значения переменной в узел 11 текущее время программно считывается этим блоком

вида (1) и (2) пояснен блок-схемой алгоритм на фиг.5 и 6.

I

На этапе начального диалога пользователь составляет с помощью стан- дартньрс средств связи операционной системы блока J (например, с помощью редактора рбщего йазначения. EDIT

40

честна исследуемого объекта в соответствии с конкретным- видом выражения (1). С клавиатуры дисплея блока 1 вводятся конкретные числовые значения коэффициентов а j-j, b;, входящих в уравнения (2) , и начальные значения переменные Х-(0). В случае использования стандартных функ- 45 ций Ф.Днапример, sin, cos, exp и т.п.) пользователь указывает только конкретный вид функции и требуемую погрешность аппроксимации. В случае использования нестандартных функций

честна исследуемого объекта в соот ветствии с конкретным- видом выражения (1). С клавиатуры дисплея блока 1 вводятся конкретные числовые значения коэффициентов а j-j, b;, входящих в уравнения (2) , и начальные значения переменные Х-(0). В случае использования стандартных функ- 45 ций Ф.Днапример, sin, cos, exp и т. пользователь указывает только конкретный вид функции и требуемую погрешность аппроксимации. В случае использования нестандартных функций

.с регистра 26 по сигналу селектора 16.

В регистрах 27 информация о текущих значениях переменных обновляется с максимально возможной скоростью, ограниченной практически только вре- 50 по ьзователь задает координаты менем преобразования АЦП 24. При этом узловых точек аппроксимации. Далее вычислительная нагрузка узла 11, определяемая обработкой данных и управлением блоком/5 по программам пользователя либо вьтолнением системных программ, не увеличивает время обмена - время получения блоком 1 последпользователь указьшает в явном внц разделение вычислительной нагрузки между блоками 5 при решении системы 55 (2). На этой основе блок 1 формирует программы управления блоками 5, реализуемые на узлах 1I. Таким образом задается математическое описание исследуемого объекта и про

них значений аналоговых переменных в цифровом виде. Кроме того, обмен р

блоком 1 через формирователи 28 не мешает узлу 11 одновременно получить те же значения переменных через со- ответствующий формирователь 29, что увеличивает степень распараплелли- вания процессов обмена и вычислительных процессов между блоком 1 и узлами 1 I .

В соответствии с программой, згшо- женной в узел 11, осуществляется модуляция (изменение значения коэффициентов по зарнее рассчитанным функциональным зависимостям) определенных коэффициентами К; и К;,во времени, что позволяет получить ixY функциональных зависимосте й. Управляя работой узла ключей 37, а также устанавливая значения коэффициентов К--,

1 j

и Kj равными О или рассчитанному значению на ЦАП 32, можно изменять схему моделирования во времени.

тельного процесса при решении на предлагаемом устройстве уравнений

системе РАФОС) программу для вычис- ления и оценки значения функции ка-

вида (1) и (2) пояснен блок-схемой алгоритм на фиг.5 и 6.

I

На этапе начального диалога пользователь составляет с помощью стан- дартньрс средств связи операционной системы блока J (например, с помощью редактора рбщего йазначения. EDIT

системе РАФОС) программу для вычис- ления и оценки значения функции ка-

честна исследуемого объекта в соответствии с конкретным- видом выражения (1). С клавиатуры дисплея блока 1 вводятся конкретные числовые значения коэффициентов а j-j, b;, входящих в уравнения (2) , и начальные значения переменные Х-(0). В случае использования стандартных функ- ций Ф.Днапример, sin, cos, exp и т.п.) пользователь указывает только конкретный вид функции и требуемую погрешность аппроксимации. В случае использования нестандартных функций

по ьзователь задает координаты узловых точек аппроксимации. Далее

по ьзователь задает координаты узловых точек аппроксимации. Далее

пользователь указьшает в явном внце разделение вычислительной нагрузки между блоками 5 при решении системы (2). На этой основе блок 1 формирует программы управления блоками 5, реализуемые на узлах 1I. Таким образом задается математическое описание исследуемого объекта и программа обработки результатов модели рования.

На этапе начальной подготовки блок 1 производит численное интегрирование системы уравнений (2), определяя при этом максимальные значения переменных и производных. Затем в соответствии с известными методиками расчета рассчитываются масштабы переменных, масштаб времени и значения коэффициентов, устанавливаемых с помощью ЦАП 30, 31 и умножающих ЦАП 32, Таким образом формируется схема моделирования, которая может быть отображена с помощью внешних устройств блока 1 (например, устройство печати или видеомонитора).

На этапе начальной загрузки блок 1 через узел 17 памяти передает в узел 14 памяти управляющие программы, коды ЦАП 30, 31 и умножающих ЦАП 32, управляющую информацию для коммутации узлов ключей 36 и 37, коды узлов 23 нелинейных функций и информацию для коммутации узлов 21 и 22. Блок 1 задает блоку 6 связи информацию о необходимых коммутациях между блоками 5.

По окончании этапа начальной загрузки блока производится инициализация узлов 11 по сигналам с селектора 3 через узел 20 прерываний. При этом программа обработки прерываний узла 11 считывает слово состояния из узла 7, заданное блоком 1, и обеспечивает обработку прерывания в соответствии с заданным условием в слове состояния. Так обеспечивается управление блоком 5, например , задание режимов работы интеграторов .Кроме прерьтаний работы блока 5 по инициативе блока 1, возможно прерьшание по времени, обеспечиваемое таймером 19.

Возможно при необходимости также прерывание блока 1 по сигналам от блоков 5. Реализуется оно путем передачи сигналов от селекторов 16 в блок 10,

На этапе ращения узлы 11 с помощь блоков 38 вырабатывают команды управления интеграторами 35, через АЦП 24 считывают информацию с выходов блоков 33, 35, записывая текущие значения указанных пользователем переменных и метки времени, генерируемые блоком 4 в соответствующие

0

5

0

5

0

5

0

5

0

5

регистры 27 и регистр 26, откуда они могут быть считаны как в блок 2, так и в уэел 14 ,

Выполнение управляющих программ моясет быть прекращено либо по истечении заданного времени интегрирования через узлы 20 прерываний от таймеров 19, либо по указанию блока 1 через селектор 3,

Формула изобретения

Аналого-цифровое вычислительное устройство, содержащее блок управления, блок памяти, первый селектор адреса, блок связи и К блоков решения дифференциальных уравнений (К - количество уравнений в системе уравнений), каждый из которых содержит М узлов интегрирования (М - коли- честв о неизвестных в системе уравнений), первый узел управления, первый и второй узлы памяти, второй селектор адреса, таймер,узел прерываний, первый и второй узлы коммутации, М аналого-цифровых преобразователей и Е узлов вычисления нелинейных функций -(Е - количество нелинейных функций) , причем вхсд-выход блока управления соединен с информационным входом-выходом блока памяти, информационными входами-выходами всех блоков решения дифференциальных уравнений и входом задания режима блока связи, первый выход блока управления соединен с входами адреса блока памяти всех блоков решения дифференциальных уравнений и с информационным входом первого селектора адреса, первый выход которого соединен с входом синхронизации блока связи, информационный выход которого соединен с информационными входми всех блоков реше ния дифференциальных уравнений, первые информаднонные выходы которых соединены, с труппой информационньк входов блока связи, второй выход блока управления соединен с входами записи-считывания блока памяти, всех блоков решения дифференциальных уравнений и с управляющим входом первого селектора адреса, первые информацион ные входы всех узлов вычисления нелинейных функций соединены с выходами первого узла коммутации, вход синхронизации которого соединен с перкым выходом второго селектора адреса, входами синхронизации всех узлов вы

1115

числения нелинейных функций, второго узла коммутации, всех узлов интегрирования и таймера, информационный вход таймера соединен с информационным входом-выходом первого узла памяти, первым информационным входом- выходом второго узла памяти, первыми информационными входами всех узлов итегрирования, вторыми информационны- ми входами всех,узлов вычисления нелинейных функций, управляющими входами первого и второго узлов коммутации и входом-выходом первого узла управления, первый выход первого уз- ла управления со единен с информационным входом второго селектора адреса, входом адреса первого узла памяти и первым входом адреса второго узла памяти, второй выход первого узла управления соединен с управляющим входом второго селектора адреса, первым входом записи-считывания второго узла памяти и входом записи-считывания первого узла памяти, второй вход адреса, второй вход записи- считывания и второй информационный вход-выход второго узла памяти являются входами адреса, записи-считывания и информационным входом-выходом блока решения дифференциальных уравнений соответственно, информационный вход второго узла коммутации является информационным входом блока решения дифференциальных уравнений, информационный выход второго узла коммутации соединен с первым информационным входом первого узла коммутации и вторыми информаци:- онныМи входами М узлов интегрирования, информационный вход-выход каждого узла интегрирования соединен с информационными входами выходами остальных узлов интегрирования, втр- рь1м информационным входом первого уз- ла коммутации и является первым информационным выходом блока решвния дифференциальных уравнений, выходы всех узлов вычисления нелинейных функщ1Й соединены с .группой информационных входов второго узла коммутации, первый вход узла прерьшаний соединен с вьссодом таймера, выход узла прерьшаний.соединен с входом первого узла управления, информа-г- цнонный выход каждого узла интегрирования соединен с информационным входом аналого-цифрового преобразователя, о тличающееся тем.

5

103

Q5

12

Что, с целью повышеия быстродействия, в него введены блок синхронизации, блок прерываний, генератор импульсов, а в каждый блок решения дифференциальных уравнений введены М буферных регистров, М первых и ; вторых формирователей импульсов, регистр состояния обмена и М вторых узлов управления, причем выход прерывания всех блоков решения дифференциальных уравнений соединен с группой входов блока прерываний,группа выходов первого селектора адреса соединена с группой входов синхронизации всех блоков решения диффрен- циальньос уравнений, выход первого селектора адреса соединен с входом синхронизации блока синхронизации 0 обмена, управляющий вход которого соединен с вторым выходом блока управления, вход-выход которого соединен с первым информационным выходом блока синхронизации обмена вторыми информационными выходами всех блоков решения дифферециальных уравнений, вход состояния обмена которых соединен с вторым информационным выходом блока синхронизации, генератор импульсов соединен с тактовыми входами всех блоков решения дифференциальных уравнений, вход признака прерывания блока управления соединен с выходом блока прерываний, первый вход второго узла управления соединен с выходом -конца преобразования аналого-цифрового преобразователя, вход запуска которого соединен с первьм выходом второго узла управления,- второй выход которого соединен с входом записи буферного регистра, информационный вход которого соединен с выходом аналого- цифрового преобразователя, выход буферного регистра соединен с информационными входами первого и второго формирователей импульсов, выход всех первых формирователей импульсов соединен с входом-выходом первого узла управления и выходом регистра состояния обмена, вход синхронизации которого соединен с вторым вьпсодом второго селектора адреса, третий выход которого является выходом прерьшаний блока решения дифференциальных уравнений и соединен с входами синхронизации всех первых формирователей импульсов и вторыми входами всех вторых узлов управления, третий вход которых соеди0

5

0

5

0

5

нен с входами синхронизации всех вторых формирователей импульсов, вторым информационным входом узла прерывания и является группой входов синхронизации блока решения дифференциальных уравнений, выходы вторых формироватефиг.1

лей импульсов являются вторым информационным выходом блока решения дифференциальных уравнений, информационный вход регистра состояния обмена является входом состояния обмена блока решения дифференциальных уравнений.

фиг. г

P

tf

L

фиг

S3

«3

d

Г

zt

35

J.I IBMBeJ I

5 Ibw/7 W -.1 I«J / j-ffS I

Гноне 4 Л от /Ь fnoffoBb

fpus.5

пгп

28

1

e i/UCfffH.

в соотВе- тс/пв. с(1)

I 1

mf UBaw/

ffSpa oinffO

Ufa4a/io

шор/ ираве/ uafyftpaSffji vutt/n ffflffeflOftM

Vff/neepU poBoftue

{2 )

fyacfffr

MaciUTo&oL

Moatjy fJt/tfeMirfoB

IBЫ8од I I I

Iffff ffflol

aiperffvegaffttinAtet UXMfffpff

/fo9eBuT.n.

±

ffHoBfia HAf 30.31 у НАЛ 32

f/e/n

Тмшуолизс цил gofforti

IfffOHoB 10

(pus.6

| Пухов Г.Е., Самойлов В.Д., Аристов В.В | |||

| Автоматизированные аналого-цифровые устройства моделирования | |||

| Киев: Техника, 1974, с | |||

| Приспособление для воспроизведения изображения на светочувствительной фильме при посредстве промежуточного клише в способе фотоэлектрической передачи изображений на расстояние | 1920 |

|

SU172A1 |

| Аппарат, предназначенный для летания | 0 |

|

SU76A1 |

| Аналого-цифровая вычислительная система | 1987 |

|

SU1429139A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1988-04-04—Подача