X

:о

Zfd

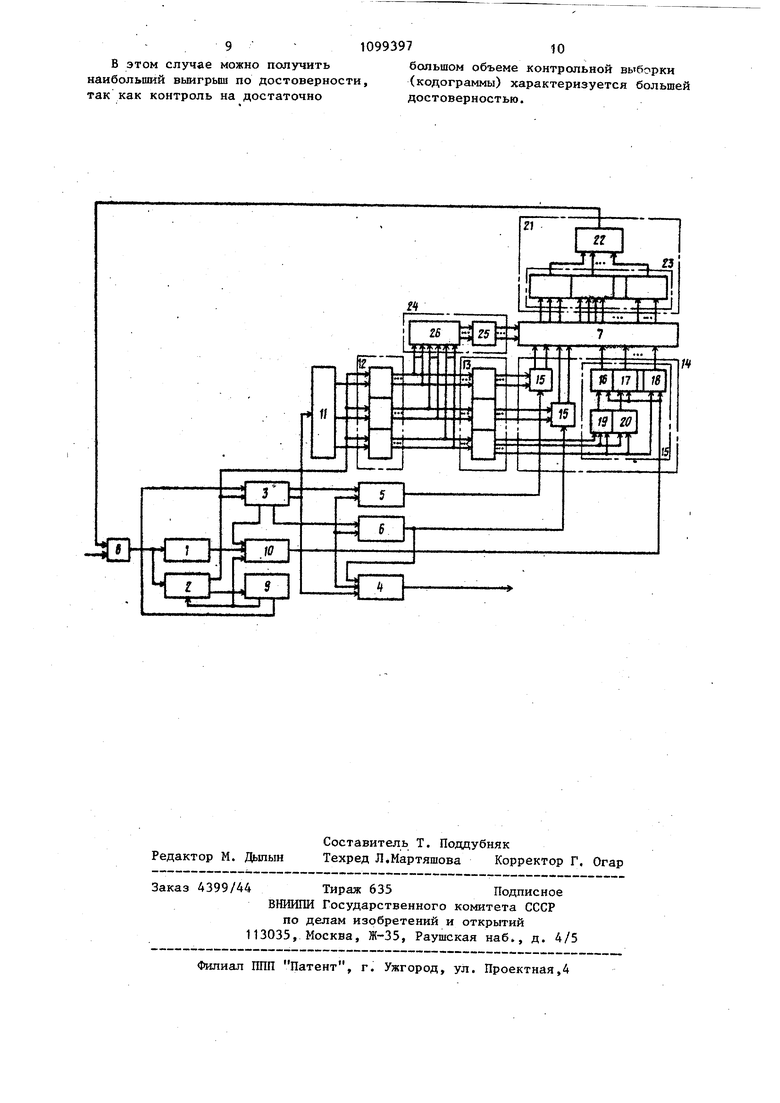

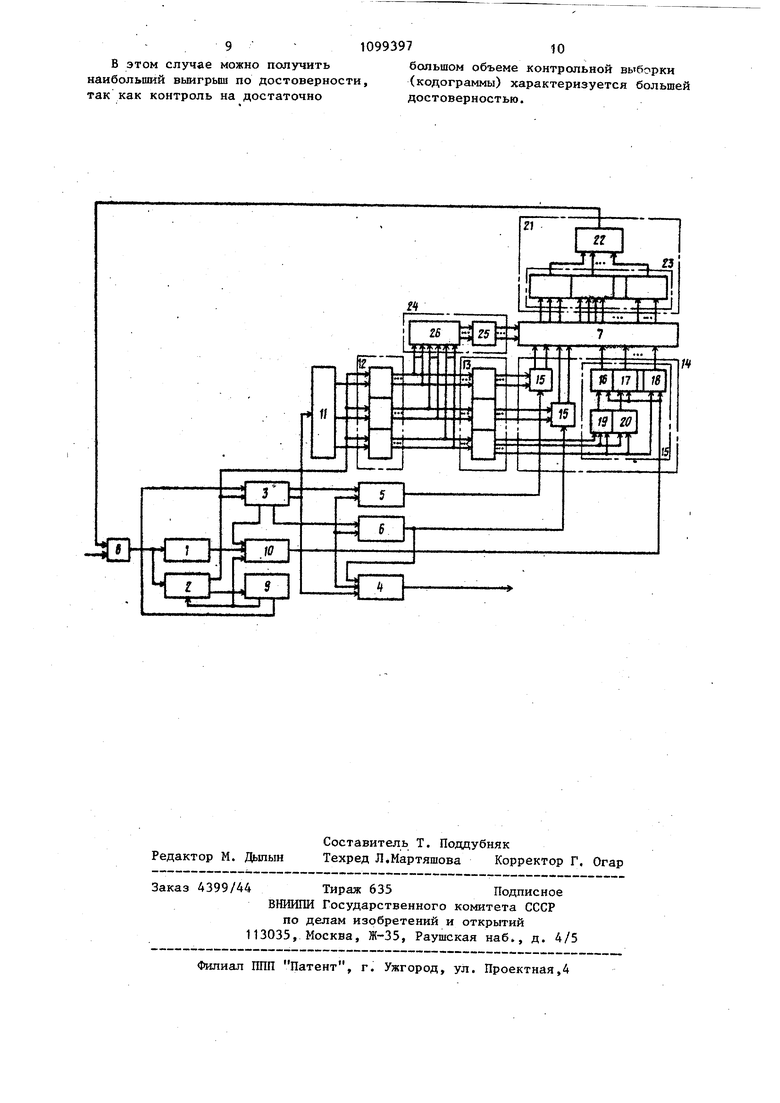

со | Изобретение относится к электросвязи и может быть использовано при прстроении аппаратуры передачи данных, в которой для обеспечения требуемой верности передачи применяют избыточньй KJЭД в дезкиме обнаружения и частичного исправления ошибок с непрерывной последовательной передачей кодовых комбинаций при работе на каналах.низкого качества. По основному авт.св. № 680189 известно устройство для приема дискретной информации, закодированной корректирующим кодом, содержащее объединенные по входу накопитель и декодирующий блок, выход которого подключен к входу блока управления, выходы которого соответственно подключены к управляющим входам выходного накопителя и первого и второго блоков памяти, информационные входы которых объединены с - первым инфор мационным входом выходного накопителя и с одним из входов блока мажоритарного сложения, к двум другим входам которого подключены соответственно выход первого блока памяти и выход второго блока памяти, объединенный с другим информационным входом выходного накопителя., а также последовательно соединенные селектор и сумматор по модулю два, и элемент ИЛИ, к одному из входов которого подключен выход блока мажоритарного ,сложения, а выход элемента ИЛИ подключен к входу накопителя, выход которого подключен к объединенным информационным входам первого и вто го блоков памяти через сумматор по модулю два, а вход селектора-подклю чен к дойолнительному выходу декоди рующего блока, выходы селектора под ключены к соответствующим входам декодирующего блока и блока управле ния , дополнительный выход которого подключен к другому входу сумматора по модулю два С11. Однако данное устройство для приема дискретной информации, закодированной корректирующим кодом,обладает невысокой достоверностью при ема информации, так как операция ма жоритарного сложения накопленных ко довых комбинаций производится без учета результатов контроля принятой информации. Цель изобретения - повышени дос товерности приема. 972 Цель достигается тем, что в устройство для приема дискретной информации, закодированной корректирующим кодом, содержащее объединенные по входу накопитель и декодирующий блок, выход которого подключен к входу блока управления, выходы которого соответственно подключены к управляющим входам выходного накопителя и первого и второго блоков памяти, информационные входы которых объединены с первым информационным входом выходного накопителя и с одним из входов блока мажоритарного сложения, к двум другим входам которого подключены соответственно выход первого блока памяти и выход второго блока памяти, объединенный с другим информационным входом выходного накопителя, а также последовательно соединенные ceлeкtop и сумматор по модулю два, и элемент ИЛИ, к одному из входов которого подключен выход блока мажоритарного сложения, а выход элемента ИЛИ подключен к входу накопителя , выход которого подключен к объединенным информационным входам первого и второго блоков памяти через сумматор по модулю два, а вход селектора подключен к дополнительному выходу, декодирующего блока, выходы селектора подключены к соответствующим входам декодирующего блока и блока управления. Дополнительный выход которого подключен к другому входу сумматора по модулю два, введены последовательно соединенные стартостопньй распределитель, блок счетчиков , блок дешифраторов, блок умножения и коммутатор, а также формирователь управляющих сигналов, выходы которого подсоединены к управляющим входам коммутатора, а входы - подключены к соответствующим выходам блока счетчиков, сигнальный вход которого подключен к выходу декодирующего блока, при этом выход блока управления подсоединен к входу стартстопного pacnpt;делителя, а выходы первого и второго блоков памяти и сумматора по модулю два Подключены к входам блока мажоритарного сложения через последовательно соединенные блок умножения и коммутатор. На чертеже представлена структурно-электрическая схема устройств. для приема дискретной информации, закодированной корректирующим кодом. Устройство для приема дискретной информации, закодированной корректирующим кодом, содержит накопитель 1, декодирующий блок 2, блок управления 3, выходной накопитель 4j блоки памяти 5 и 6, коммутатор 7, элемент ИЛИ 8, селектор 9, сумматор по модулю два 10, стартстопный распределитель 11, блок счетчиков 12, блок дешифраторов 13, блок умножения 14, содержащий три умножителя разрядов 15, каждьй из которых содержит элемент И 16-18 и элементы ИЛ 19 и 20, блок 21 мажоритарного сложения, содержащий элемент сборки 22 и блок 23 мажоритарных элементов, и формирователь управляющих сигналов 24, содержащий дешифратор 25 и сумматор 26, Устройство для приема дискретной информации, закодированной корректирукицим кодом, работает следующим образом. На вход элемента ШШ 8 поэлементн поступает последовательность кодовых комбинаций, которые с выхода подаются в накопитель 1 и декодирующий блок 2. При отсутствии ошибок или наличии необнаруженных ошибок комбинация через сумматор по модулю ва 10 перепи сьшается в выходной накопитель 4 и выдается потребителю в случае необнаружения ошибки в следующей кодовой комбинации. При обнаружении ошибки декодирующий блок 2 формирует сигнал ошибки в блок управления 3. Если ошибка исправляется, то кодовая комбинация с выхода накопителя 1 через сумматор по модулю два 10 вьщается в выходной накопитель 4. При этом селектор 9 формирует импульсы для исправления ошибки в сумматоре по модулю два 10 и устранения влияния исправляемых разрядов на содержимое декодирующего блока 2. Если ошибка не исправляется то с селектора 9 подается сигнал о невозможности исправления ошибки в блок управления 3, по которому последний блокирует выходной накопитель 4 и запускает стартстопный распределитель 11. При этом элементы комбинации, предшествующие ошибочной и хранящиеся в выходном накопителе 4, стираются блоком управления 3, открывается информационньй вход блока 1 74 памяти 6 и начинается этап приема участка кодовых комбинаций на длине блокировки, который характеризуется тем, что элементы кодовой комбинации с обнаруженной ошибкой и следующие за ней кодовые комбинации записьшаются в блок памяти 6, а их признаки запоминаются в блоке управления 3, причем принятым без ошибок (как и с исправляемыми ошибками) комбинациям присваивается признак О, а с обнаруженными ошибками - 1. Кроме того, стартстопный распределитель 11 осуществляет поочередное подключение счетчиков блока счетчиков 12 для подсчета числа комбинаций с обнаруженными ошибками на длине блокировки. Такой подсчет принимаемых с обнаруженными ошибками кодовых комбинаций необходим для дальнейшего использования результатов этого контроля в операции мажоритарной обработки. Цикл подключения каждого из счетчиков блока счетчиков 12 выбирается равным циклу блокировки выходного накопителя 4 блоком управления 3 и может быть выбран с учетом времени распространения сигнала в прямом и обратном каналах, длительности и времени анализа кодовой комбинации и сигнала обратной связи. При приеме кодовой комбинации с обнаруженной ошибкой блок управления 3 запускает стартстопный распределитель 11 , которьш на время первого приема участка блокировки осуществляет подключение одного из счетчиков блока счетчиков 12 для подсчета кодовых комбинаций, принятых с обнаруженными ошибками. Если при повторной передаче имеет место успешный прием, то стартстопный распределитель 11 устанавливается в первоначальное положение блоком управления 3 (сбрасывается) , в противном случае работа стартстопного распределителя 11 продолжается, он производит подключение следующего счетчика блока счетчиков 12 для подсчета числа кодовых комбинаций с обнаруженными ошибками, повторяемых во второй раз. В случае отсутствия или исправления ошибок в запрашиваемой комбинации при повторении на выходах блока управления 3 формируются сигналы, по которым повторяемые комбинации переписываются в выходной накопитель 4 непосредственно или с блока памяти 6. Если принятая при первом и повторных приемах комбинация содержит обнаруженные ошибки, то ее внов переспрашивают, цикл блокировки начинается сначала, а стартстопорньй распределитель 11 подключает очеред ной счетчик блока счетчиков 12 для подсчета кодовьк комбинаций с обнаруженными ошибками. Таким образом, выходной накопитель 4 блокируется вновь в случае невозможности исправления ошибок в запрашиваемой комбинации. При этом на выходе блока управления 3 после приема каждой комбинации формируются сигналы, в соответствии с которыми элементы правильно принятый повторяемых комбинаций и комбинаций с обнаруженными ошибками записываются в блок памяти 5, правильно принятые повторяемые комбинации записьгоаются в блок памяти 6 в соответствующие места, в которых первоначально принятые с об наруженными ошибками комбинации стираются (т.е. на их места записываются элементы повторяемых правиль но принятых комбинаций). В последнем случае блок управления 3 присваивает признак О правильно принятой комбинации вместо записанной первоначально 1 (когд имеет место прием с обнаруженной ошибкой). При приеме запрашиваемой комбина ции в третий раз, независимо от результатов приема, блокировка выходного накопителя 4 не производится. На выходах блока управления 3 формируются сигналы, в соответствии с которыми производится обработка накопленной на длине блокировки информации . Если кодовая комбинация принята правильно или с исправляемой ошиб.кой хотя бы один раз из трех, то она переписывается в выходной накопитель 4 непосредственно с сумма тора по модулю два 10 или с блока памяти 6. В случае приема с ошибкой и невозможности исправления все три ра за блок управления 3 формирует сиг налы, в соответствии с которыми де кодирующий блок 2 и селектор 9 при водятся в .исходное состояние, а эл менты этой комбинации с быходов бл ков памяти 5 и 6 и сумматора по мо дулю два 10 поступают в блок умножения 14. Блок счетчиков 12 подсчитывает число искаженных кодовых комбинаций, значения которых расшифровываются в блоке дешифратора 13 и используются для задания в блоке умножения 14 весовых коэффициентов, с которыми разряды принятых трехкратно искаженных комбинаций применяются в операции мажоритарной обработки. Выбор весовых коэффициентов производится с учетом качества канала связи, статистики ошибок и характера искажений в кодовых комбинациях. Причем искаженной кодовой комбинации, принятой с наибольшим числом комбинаций с обнаруженными ошибками на длине блокировки, присваивается наименьший весовой коэффициент в операции мажоритарной обработки, а искаженной кодовой комбинации, принятой с наименьшим числом кодовых комбинаций с обнаруженными ошибками на длине блокировки, - наибольший. Это позволяет в операции мажоритарной обработки учитывать более достоверную информацию (т.е. с меньшим числом обнаруженных ошибок) с большим весовым коэффициентом, а менее достоверную (т.е. с большим числом комбинаций с обнаруженными ошибками) не yчитывatь или ут итывать с минимальньм весовым коэффициентом. Задание весового коэффициента осуществляется дешифраторами блока дешифраторов 13, которые в зависимости от значений счетчиков блока счетчиков 12 подключают соответствующие выходы к управляющим входам блока умножения 14 i - Управлякмций сигнал с выходов дешифраторов блока дешифраторов 13 в зависимости от значений весовых коэффициентов открывает непосредственно или через элементы ИЛИ 19 . и 20, один, два и т.д. элементы И 16-18 умножителей разрядов 15 блока умножения 14, разрешая передачу разрядов трехкратно искаженных кодовых комбинаций через блок умножения 14. При этом блок умножения t4 производит умножение на соответствующие весовые коэффици енты обрабатываемых разрядов дпя последующей передачи их в блок мажоритарного сложения 2 через коммутатор 7.. В зависимости от значений весовых коэффициентов, на которые умножаются в блоке умножения 14 разряды обрабатываемых кодовых комбинаций, возможно получение для операции мажоритарной обработки одного из следующих правил (критериев голосования по принципу большинства): 2 из 3, 3 из 5, и т.д. Поэтому в обработке участвуют один из мажоритарных элементов блока 23. Выбор конкретного мажоритарного элемента блока 23 осуществляется фор мированием управляющих сигналов 24 следующим образом. Формирователь управляющих .сигнало 24осуществляет суммирование значени счетчиков блока счетчиков 12, опреде ляющих весовые коэффициенты, а затем расшифровку дешифратором 25 полученной суммы, соответствующей одному из критериев голосования. Дешифратор 25формирователя управляющих сигнало 24 подключает через коммутатор 7 маж ритарный элемент блока 23 с числом входов, определяемых Сумматором 26. Блок 21 путем поэлементного мажоритарного сложения формирует н.овые элементы комбинации, которые повторн выдаются через элемент ИЛИ 8 в накопитель 1 и декодирующий блок 2.При этом в накопителе 1 формируется комбинаци соответствующая отмажорированным эле ментам, которая, если не содержит обнарзживаемые корректирующим кодом ошибки, через сумматор по модулю два 10 вьщается в выходной накопитель 4. В противном случае процесс перезапроса повторяется. Коммутатор 7 представляет собой набор ключей. Количество мажоритарных элементов блока 23 выбирается с учетом аппаратурных затрат, различных критериев голосования (2 из 3, 3 из 5, 4 из 7, 6 из 11, 7 из 13 и т.д.) и других требований, однако максимальное число в блоке 23 ограничено,в первую очередь максимальным значением весового коэффициента а и может быть выбрано из условия (За-2)-мажоритарных элементов. Значения счетчиков блока счетчиков 12, подсчитывающих число комбинаций с обнаруженными ошиб-. ками, расшифровываются дешифраторами блока дешифраторов 13 и задают следующие весовые коэффициенты, а: для 1-го приема з астка блокировки а 1, для 2-го SL 2, для 3-го - aj 3. В этом случае соответствующие дешифраторы блока дешифраторов 3 подключают первый умножитель разряда 15 блока умножения 14 с одним выходом, осуществляя умножение обрабатываемого разряда на коэффициент а 1, второй умножитель разряда 15 - с двумя выходами (а2 2), третий умнолеитель разряда 15 - с тремя выходами (aj 3) следующим образом (рассмотрим это на примере умножения разряда на коэффициент . ). Выходной сигнал с соответствующего дешифратора блока дешифраторов 13поступает на элементы И 16-18 непосредственно и через элементы риш 19 и 20, разрешая прохождения разряда через блок умножения 14и производя умножение обрабатываемого разряда на соответствуюпщй коэффициент (аз 3). Формирователь управляющих сигналов 24 осуществляет суммирование значений весовых коэффициентов а счетчиков блока счетчиков 12 и определяет соответствующий мажоритарный элемент, который должен быть использован в мажоритарной обработке (в данном примере а а а + + аз 6) . Дешифратор 25 производит через коммутатор 7 подключение мажоритарного элемента блока 23 с 6 входами, который по определенному критерию голосования производит обработку разрядов трехкратно искаженной кодовой комбинации. Технико-экономическая эффективность устройства для приема дискретной информации, закодированной корректирующим кодом, заключается в обеспечении высокой достоверности приема за счет использования результатов контроля накопленных на длине блокировки кодовых комбинаций в операции мажоритарной обработки, причем выигрьш будет наибольший в устройствах с наибольшей длиной блокировки, в которых контроль осуществляется на большем объеме контролируемой выборки. Данный принцип можно реализовать в устройствах приема информации с передачей кодограммами и накоплением, когда контроль производится на всей длине кодограммы.

9109939710

В этом случае можно получить большом объеме контрольной выборки наибольший выигрыш по достоверности, (кодограммы) характеризуется большей так как контроль на достаточно достоверностью.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1984 |

|

SU1172022A2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1978 |

|

SU680189A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство анализа кодовых комбинаций | 1976 |

|

SU649152A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

УСТРОЙСТВО ДЛЯ ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ, ЗАКОДИРОВАННОЙ КОРРЕКТИРУНЩИМ КОДОМ по авт.св. № 680189, отличающееся тем, что, с целью повышения достоверности приема, введены последовательно соединенные стартстопный распределитель, блок счетчиков, блок дешифраторов, блок умножения и коммутатор , а также формирователь управляющих сигналов, выходы которого подсоединены к управляющим входам коммутатора, а входы подключены к соответствующим выходам блока счетчиков, сигнальный вход которого подключен к вьгкоду декодирующего блока, при этом выход блока управления подсоединен к входу стартстопного распределителя, а выходы первого и второго блоков памяти и сумматора по модулю два подключены к входам блока § мажоритарного сложения через последо-. вательно соединенные блок умножения и коммутатор.

21

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1978 |

|

SU680189A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-06-23—Публикация

1983-03-10—Подача