1

Изобретение относится к связи, а именно, к технике передачи дискретной информации и может использоваться в аппаратуре передачи данных с решающей обратной связью.

Известно устройство анализа кодовых комбинаций, содержащее блок декодирования, первый выход которого через последовательно соединенные регистр блокировки и блок управления подключен к первому входу первого блока памяти, второй вход которого соединен с первым входом второго блока памяти, с первым входом блока мажоритарного сложения, с первым входом выходного накопителя и с выходом приемного накопителя, вход которого соединен с входом блока декодирования, второй выход которого через блок сравнения подключен к второму входу блока управления и к первому входу запоминающего блока, выход которого подключен к другому входу блока сравнения, дополнительный вход которого соединен с вторым входом запоминающего блока, с вторым входом второго блока памяти и с выходом блока управления, а выходы первого и второго блоков памяти подключены к второму и третьему входам блока мажоритарного сложения, при этом выход второго блока памяти подключен к второму входу выходного накопителя, а также дополнительный блок декодирования, выход которого подключен к другому входу регистра блокировки 1.

Однако известное устройство имеет недостаточную скорость передачи информации, что приводит к увеличению времени анализа.

Целью изобретения является уменьщение времени анализа.

Для этого в устройство анализа кодовых комбинаций, содержащее блок декодирования, первый выход которого через последовательно соединенные регистр блокировки и блок управления подключен к первому входу первого блока памяти, второй вход которого соединен с первым входом второго блока памяти, с первым входом блока мажоритарного сложения, с первым входом выходного накопителя и с выходом приемного накопителя, вход которого соединен с входом блока декодирования, второй выход которого через блок сравнения подключен к

второму входу блока управлени5г и к первому входу запоминающего блока, выход которого подключен к другому входу блока сравнения, дополнительный вход которого соединен с вторым входом запоминающего блока, с вторым входом второго блока памяти и с выходом блока управления, а выходы первого и второго блоков памяти подключены к второму и третьему входам блока мажоритарного сложения, при этом выход второго блока памяти подключен к второму входу выходного накопителя, а также дополнительный блок декодированиия, выход которого подключен к другому входу регистра блокировки, введены последовательно соединенные счетчик числа стираний и блок исправления стираний, при этом первый вход счетчика числа стираний соединен с выходом блока мажоритарного сложения, четвертый вход которого соединен с вторым входом счетчика числа стираний, с вторым входом блока исправления стираний, с другим входом регистра блокировки,с дополнительным выходом блока управления и с третьим входом выходного накопителя, четвертый вход которого соединен с входом дополнительного блока декодирования и с выходом блока исправления стираний, третий вход которого соединен с первым входом блока мажоритарного сложения, при этом выход дополнительного блока декодирования подключен к третьему входу второго блока памяти.

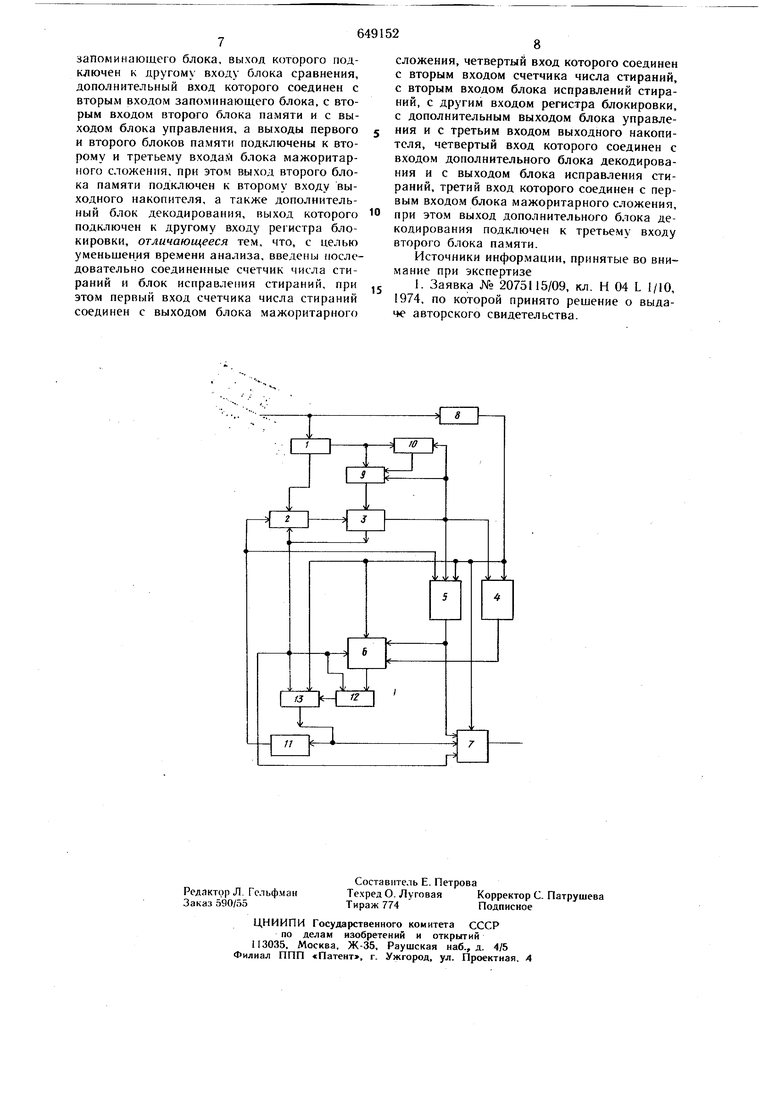

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство анализа кодовых комбинаций содержит блок декодирования 1, первый выход которого через последовательно соединенные регистр 2 блокировки и блок управления 3 подключен к первому входу первого блока памяти 4, второй вход которого соединен с первым в.ходом второго блока памяти 5, с первым входом блока 6 мажоритарного сложения, с первым входом выходного накопителя 7 и с выходом приемного накопителя 8, вход которого соединен с входом блока декодирования 1, второй выход которого через блок сравнения 9 подключен к второму входу блока управления 3 и к первому входу запоминающего блока 10, выход которого подключен к другому входу блока сравнения 9, дополнительный вход которого соединен с вторым входо.м запо.минающего блока 10, с вторым входом второго блока памяти бис выходом блока управления 3, а выходы первого и второго блоков памяти 4 и 5 подключены к второму и третьему входам блока 6, при этом выход второго блока памяти 5 подключен к второму входу выходного накопителя 7, а также дополнительный блок декодирования И, выход которого подключен к другому входу регистра 2. Устройство содержит также последовательно соединенные счетчик 12 числа стираний и блок 13 исправления стираний, при этом первый вход счетчика 12 соединен с выходом блока 6, четвертый вход которого соединен с вторым входом счетчика 12, с вторым входом блока 13, с другим входом регистра 2, с дополнительным выходом блока управления 3 и с третьим входом выходного накопителя 7, четвертый вход которого соединен с входом дополнительного блока декодирования 11 и с выходом блока 13, третий вход которого соединен с первым входом блока 6, при этом выход дополнительного блока декодирования 11 подключен к третьему входу второго блока памяти 5.

Устройство работает следующим образом.

На вход блока декодирования 1 и параллельно на вход приемного накопителя 8 поэлементно поступают п-элементные кодовые комбинации. В случае необнаружения ошибок в блоке декодирования 1 п элементов прИ пятой комбинации с выхода приемного накопителя 8 поступают на вход выходного накопителя 7, с выхода которого в случае необнаружения ошибки в следуюшей кодовой комбинации «К информационных элементов поступают на выход устройства.

При обнаружении ошибок в принятой комбинации сигналом с выхода блока декодирования 1 запускается регистр 2, а сигналом с выхода блока управления 3 блокируется выход выходного накогштеля 7 на время приема (h + 2) кодовых комбинаций. При этом «К элементов комбинации, предшествующей ошибочной, записанные в выходном накопителе 7, стираются. Одновременно сигналом с выхода блока управления 3 открывается информационный вход блока памяти 5 и вход запоминающего блока 10, л элементов принятой с ошибкой комбинации и (h-1) следующих за ней комбинаций записываются в соответствующие разряды блока памяти 5, а их признаки - в соответствующие разряды запоминающего блока 10. Во время повторного приема запрашиваемой комбинации регистр 2 сигналом с блока управления 3 запускается вновь независимо от исхода декодирования этой комбинации.

В случае отсутствия ошибок в запрашиваемой комбинации при повторении на выходе блока сравнения 9 после приема каждой комбинации, попавшей под блокировку, образуется соответствующий правильному приему сигнал. В соответствии с сигналом блока управления 3 повторяемые комбинации записываются на вход выходного накопителя 7 непосредственно с выхода приемного накопителя 8 или с выхода блока памяти 5.

В случае приема комбинации с ошибкой при первом и повторном приемах производится попь1тка ее восстановления в блоке 13 исправления стираний. Для этого сигналами с блока управления 3 производится поэлементное сравнение комбинации, хранящейся в блоке памяти 5 и записанной в приемном накопителе 8. Такое сравнение осуществляется в блоке 6 мажоритарного сложения, при этом комбинация с приемного накопителя 8 одновременно списывается в блок 13. Счетчик 12 подсчитывает число выявленных ошибок и одновременно фиксирует в памяти номера разрядов п-элементной комбинации с признаком ошибки - образец стираний. Если кратность стираний не превь шает установленного для используемого в системе кода порога, то блок 13, используя данные об ошибочно принятой кодовой комбинации, образце стираний и их количестве, производит исправление стертых позиций и выдает комбинацию на дополнительный блок декодирова1 ия 11. В случае правильного декодирования комбинации ее информационная часть через выходной накопитель 7 поступает на выход устройства. В фотивном случае комбинация запрашивается вновь. Если кратность стираний превосходит установленный в устройстве порог, то комбинация с блока 13 без процедуры исправления стираний поступает на вход дополнительного блока декодирования 11, что приводит к повторению запроса. При повторении запроса, в случае обнаружения ошибки в дополнительном блоке декодирования 11, комбинация с этого блока переписывается на первое место второго блока памяти 5, а цикл блокировки начинается сначала. При обнаружении ошибки в. запрашиваемой комбинации после первого запроса выход выходного накопителя 7 вновь блокируется на время прие.ма (h + 2) кодовых комбинаций. В этом случае на выходе блока сравнения 9 после приема каждой комбинации образуются соответствующие обнаружению ошибки сигналы. В соответствии с этими сигналами с помощью блока управления 3 правильно принятые п элементов повторяемой комбинации стираются, комбинации, в которых обнаружены ошибки, записываются в соответствуюише разряды первого блока памяти 4 с одновременной попыткой исправления стираний. В случае положительного исхода процедуры исправлениястираний комбинация в первом блоке памяти 4 по сигналу блока управления 3 стирается. В случае отрицательного исхода ко.мбинация хранится в первом и втором блоках памяти 4, 5. При образовании сигнала, соответствующего комбинации без ощибки, комбинация записывается в. соответствующие разряды второго блока памяти 5 вместо комбинации, ранее принятой с ощибкой, и одновременно в соответствующем разряде запоминающего блока 10 происходит смена признака. При приеме запрашиваемой комбинации третий раз независимо от исхода декодирования регистр 2 запускается вновь. Г1ри этом на выходе блока сравнения 9 после приема каждой комбинации образуются соответствующие второму повторению запрашивае.мой комбинации сигналы. В соответствии с этими сигналами комбинация, принятая хотя бы один раз из трех без ошибки, выдается на выход непосредственно с выхода приемного накопителя 8 или с выхода второго блока памяти 5. В случае приема с ошибкой все три раза и невосстановления комбинации по стираниям после первых двух приемов на входы блока 6 подаются элементы этой комбинации с выходов приемного накопителя 8 и обоих блоков па.мяти 4, 5. В этом случае формируется новая комбинация путем поэлементного мажоритарного сложения комбинаций, принятых и первый, второй и третий раз. С выхода блока 6 эта комбинация выдается на вход дополнительного блока декодирования И, .и в случае необнаружения ошибок во .вновь сформированной комбинации ее информационная часть с выходного накопителя 7 поступает на выход устройства, а в случае ошибки комбинация запрашивается вновь с одновременной записью в блок памяти о. и весь цикл работы устройства начинается сначала. Таким образом, при четном числе приемов комбинаций, попавших под блокировку с обнаруженной ошибкой, производится попытка их восстановления путем исправления стираний элементов, а при нечетном числе приемов -- по мажоритарному принцип},. Предложенное устройство наряду с мажоритарны.м принципом восстановлен1;я комбинаций при нечетном числе при.емов может производить восстановление комбинации плтем выявления и восстановления стираний при четн.ом Ч1;Сле приемов, что позволяет сократить число переспросов и, следовательно, уменьшить время анализа комбинаций. Формула изобретения Устройство анализа кодовых комбинаций, содержащее блок декодирования, первый выход которого через последовательно соединенные регистр блокировки и блок управления подключен к первому входу первого блока памяти, второй вход которого соединен с первым входо.м второго блока пa iяти, с первым входом блока мажоритарного сложения, с первым входом выходного накопителя и с выходом приемного накопителя, вход которого соединен с входом блока декодирования, второй выход которого через блок сравнения подключен к второму входу блока управления и к первому входу

запоминающего блока, выход которого подключен к другому входу блока сравнения, дополнительный вход которого соединен с вторым входом запоминающего блока, с вторым входом второго блока памяти и с выходом блока управления, а выходы первого и второго блоков памяти подключены к второму и третьему входам блока мажоритарного сложения, при этом выход второго блока памяти подключен к второму входу выходного накопителя, а также дополнительный блок декодирования, выход которого подключен к другому входу регистра блокировки, отличающееся тем, что, с целью уменьшения времени анализа, введены последовательно соединенные счетчик числа стираний и блок исправления стираний, при этом первый вход счетчика числа стираний соединен с выходом блока мажоритарного

сложения, четвертый вход которого соединен с вторым входом счетчика числа стираний, с вторым входом блока исправлений стираний, с другим входом регистра блокировки, с дополнительным выходом блока управления и с третьим входом выходного накопителя, четвертый вход которого соединен с входом дополнительного блока декодирования и с выходом блока исправления стираний, третий вход которого соединен с первым входом блока мажоритарного сложения, при этом выход дополнительного блока декодирования подключен к третьему входу второго блока памяти.

Источники информации, принятые во внимание при экспертизе

1. Заявка № 2075115/09, кл. Н 04 L 1/10, 1974, по которой принято рещение о выдач е авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| Устройство для мажоритарного декодирования при трехкратном повторении кодовой комбинации | 1985 |

|

SU1305876A1 |

| Устройство для повышения достоверности дискретной информации | 1975 |

|

SU588645A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1984 |

|

SU1172022A2 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1978 |

|

SU680189A1 |

| Декодер циклического кода с исправлением ошибок и стираний | 1980 |

|

SU1083387A1 |

| Приемник дискретной информации для симплексных каналов связи | 1980 |

|

SU862376A1 |

Авторы

Даты

1979-02-25—Публикация

1976-10-25—Подача