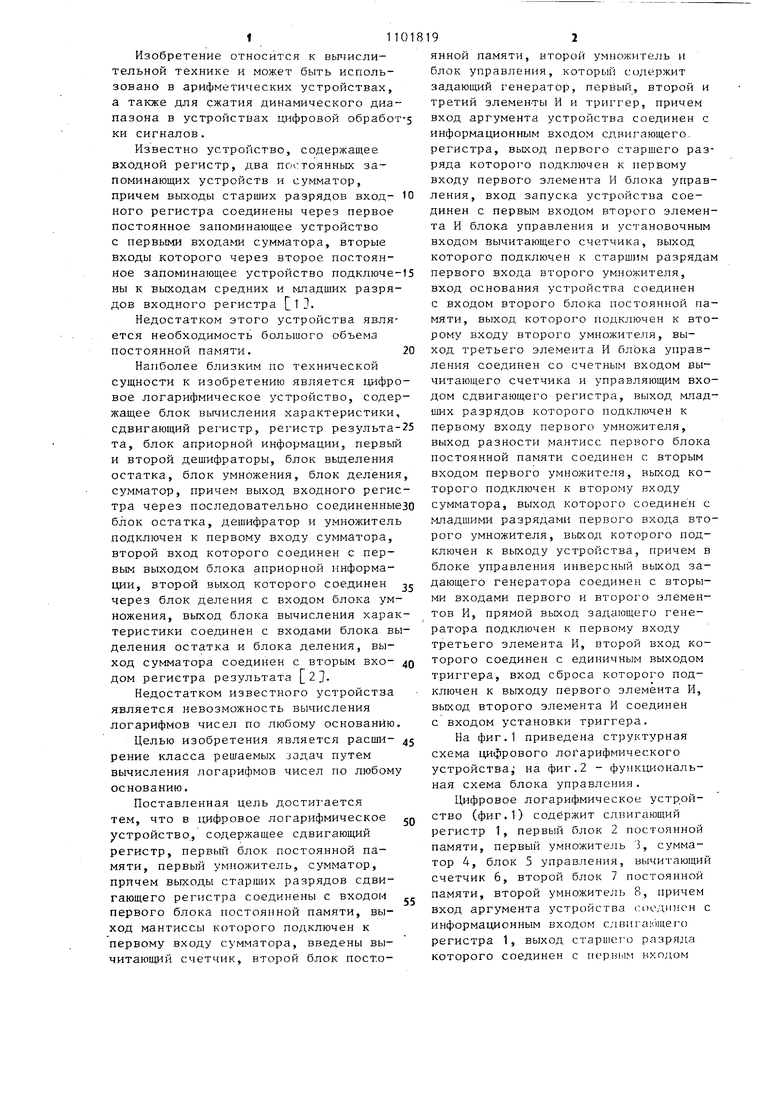

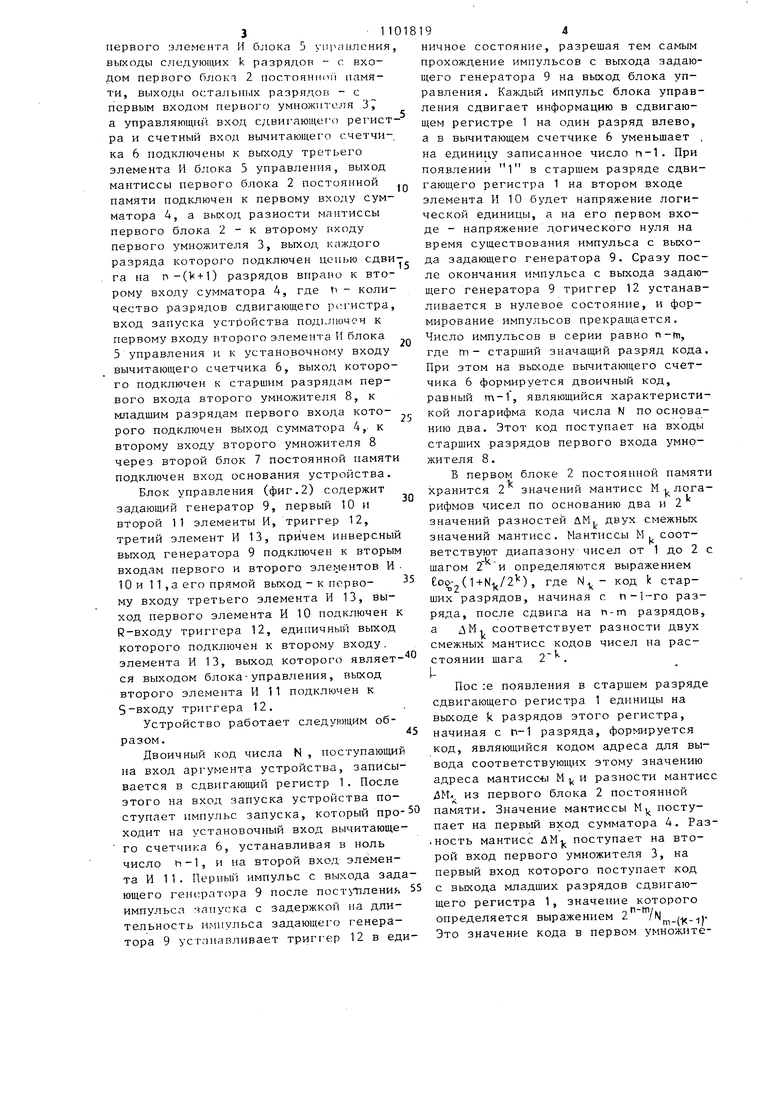

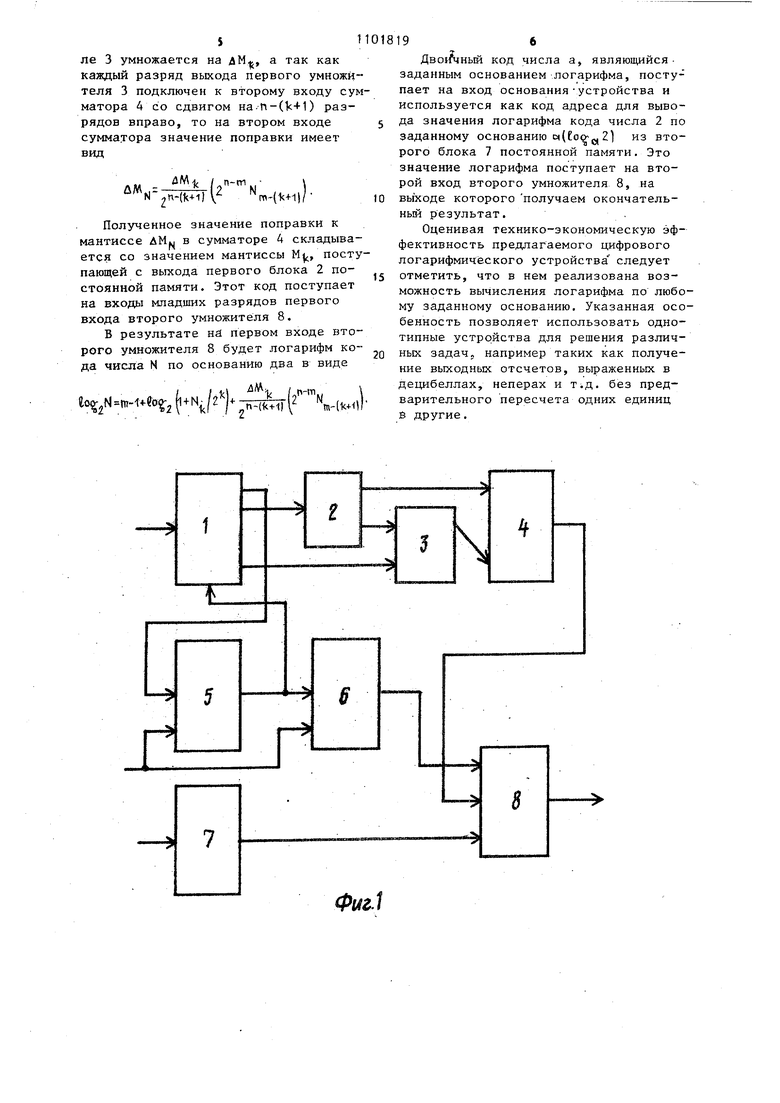

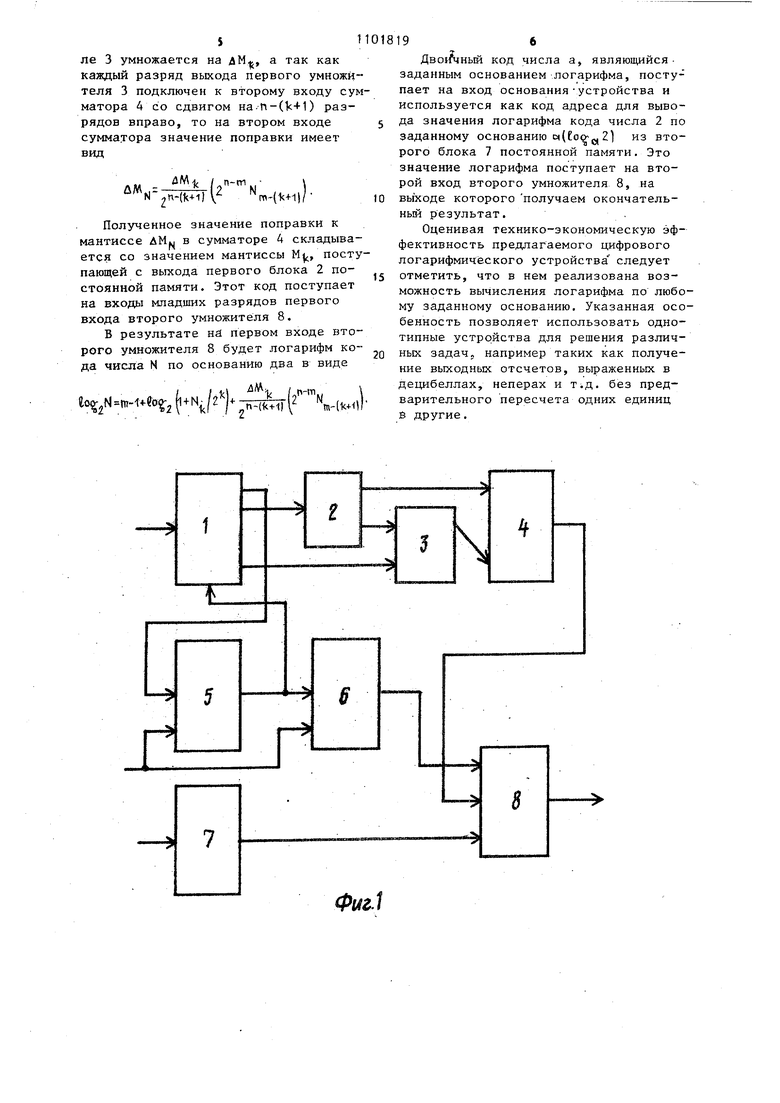

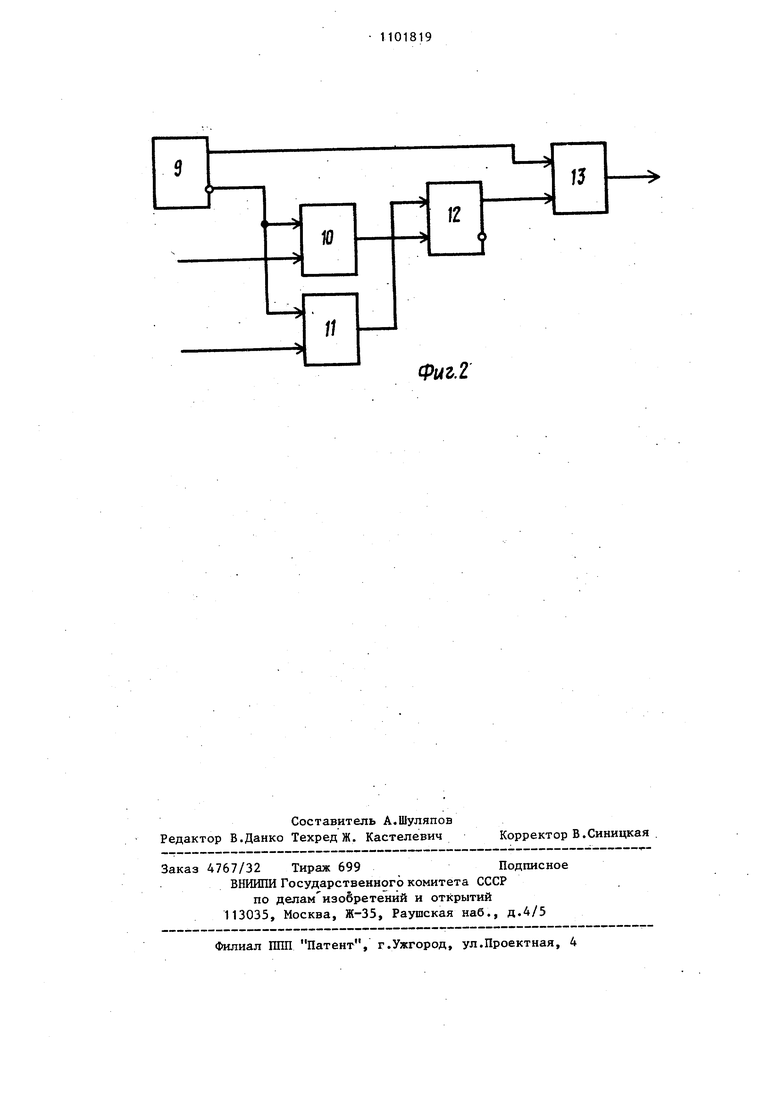

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах, а также для сжатия динамического диа пазона в устройствах цифровой обрабо ки сигналов. Известно устройство, содержаи ее входной регистр, два постоянных запоминающих устройств и сумматор, причем выходы старших разрядов входного регистра соединены через первое постоянное 3anoNfflHaroiMee устройство с первьЕми вxoдa ш сумматора, вторые входы которого через второе постоянное запоминающее устройство подключе ны к выходам средних и младших разря дов входного регистра l. Недостатком этого устройства является необходимость большого объема постоянной памяти. Наиболее близким по технической сущности к изобретению является вое логарифмическое устройство, содер жащее блок вычисления характеристики сдвигающий регистр, регистр результата, блок априорной информации, первый и второй дешифраторы, блок вьщеления остатка, блок умножения, блок деления сумматор, причем выход входного регис тра через последовательно соединеннь е блок остатка, дешифратор и умножитель подключен к первому входу сумматора, второй вход которого соединен с первым выходом блока априорной нформации, второй выход которого соединен через блок деления с входом блока умножения, выход блока вычисления харак теристики соединен с входами блока вы деления остатка и блока деления, выход сумматора соединен с вторым входом регистра результата 2. Недостатком известного устройства является невозможность вычисления логарифмов чисел по любому основанию Целью изобретения является расширение класса решаемых задач путем вычисления логарифмов чисел по любому основанию. Поставленная цель достигается тем, что Б цифровое логарифмическое устройство, содержащее сдвигающий регистр, первый блок постоянной памяти, первый умножитель, сумматор, прпчем выходы старших разрядов сдвигающего регистра соединены с входом первого блока постоянной памяти, выход мантиссы которого подключен к первому входу сумматора, введены вычитающий счетчик, второй блок пост.оявной памяти, второй ум)1ожитель и блок управления, который со/шржит задающий генератор, первый, второй и третий элементы И и триггер, причем вход аргумента устройства соединен с информационным входом сдвигающего, регистра, выход первого старшего разряда которого подключен к первому входу первого элемента И блока управления, вход запуска устройства соединен с первым входом второго элемента И блока управления и установочным входом вычитающего счетчика, выход которого подключен к старшим разрядам первого входа второго умножителя, вход основания устройства соединен с входом второго блока постоянной памяти, выход которого подключен к второму входу второго умножителя, выход третьего элемента И блока управления соединен со счетным входом вычитающего счетчика и управляющим входом сдвигающего регистра, кыхор, младших разрядов которого подключен к первому входу первого умножителя, разности мантисс первого блока постоянной памяти соединен с вторым входом первого умножителя, выход которого подключен к второму входу сумматора, выход которого соединен с младшими разрядами первого входа второго умножителя, выход которого подключен к выходу устройства, причем в блоке управления инверсный выход задающего генератора соединен с вторыми входами первого и второго элементов И, прямой выход задающего генератора подключен к первому входу третьего элемента И, второй вход которого соединен с единичным выходом триггера, вход сброса которого подключен к выходу первого элемента И, выход второго элемента И соединен с входом установки триггера. На фиг.1 приведена структурная схема цифрового логарифмического устройстваj на фиг.2 - функдаональная схема блока управле}1ия. Цифровое логарифмическое устройство (фиг.1) содержит сдвигающий регистр 1, первый блок 2 постоянной памяти, первый умножитель 3, сумматор 4, блок 5 управления, вычитающий счетчик 6, второй блок 7 постоянной памяти, второй умножитель 8, причем вход аргумента устройства (:с)едиисн с информационным входом сдвигакнцего регистра 1, выход старшето разряда которого соединен с nopi iiiiM HXOHONJ 31 первого элемента И блока 5 уиранления выходы следующих k разрядоп - с входом первого блокт 2 постояншм памяти, выходы остальных разрядов - с первым входом nepuoi-o умножителя 3 а управляющий, вход сдвшающето ретист ра и счетный вход вычитающего счетчика 6 подключены к выходу третьего элемента И блока 5 управления, выход мантиссы первого блока 2 постоянной памяти подключен к первому входу сумматора 4, а выход разности мантиссы первого блока 2 - к второму входу первого умножителя 3, выход к;1ждого разряда которого подключен цепью сдви га на п-(1 + 1) разрядов вправо к второму входу сумматора 4, где П - количество разрядов сдвигающего рсмистра вход запуска устройства подключен к первому входу второго элемента И блока 5 управления и к установочному входу вычитающего счетчика 6, выход которого подключен к старшим разрядам первого входа второго умножителя 8, к младшим разрядам первого входа котороге подключен выход сумматора 4 , к второму входу второго умножителя 8 через второй блок 7 постоянной памят подключен вход основания устройства. Блок управления (фиг.2) содержит задающий генератор 9, первый 10 и второй 11 элементы И, триггер 12, третий элемент И 13, причем инверсны выход генератора 9 подключен к вторы входам первого и второго элементов И 10 и 11, а его прямой выход - к первому входу третьего элемента И 13, выход первого элемента И 10 подключен R-входу триггера 12, единичный выход которого подключен к второму входу, элемента И 13, выход которого являет ся выходом блока-управления, выход второго элемента И 11 подключен к 5-входу триггера 12. Устройство работает следующим образом. Двоичный код числа N , поступающи на вход аргумента устройства, записы вается в сдвигающий регистр 1. После этого на вход запуска устройства поступает импульс запуска, который про ходит на установочный вход вычитающе го счетчика 6, устанавливая в ноль число h-1, и на второй вход элемента И 11. Первый импульс с выхода зад ющего генератора 9 после поступления импульса запуска с задержкой на длительность импульса задающего генератора 9 устанавливает трипер 12 в ед 194 ничное состояние, разрешая тем самым прохождение импульсой с выхода задающего генератора 9 на выход блока управления. Каждый импульс блока управления сдвигает информацию в сдвигающем регистре 1 на один разряд влево, а в вычитающем счетчике 6 уменьшает на единицу записанное число п-1. При появлении 1 в старшем разряде сдвигающего регистра 1 на втором входе элемента И 10 будет напряжение логической единицы, а на его первом входе - напряжение логического нуля на время существования импульса с выхода задающего генератора 9. Сразу после окончания импульса с выхода задающего генератора 9 триггер 12 устанавливается в нулевое состояние, и формирование импульсов прекращается. Число импульсов в серии равно n-m, где т- старший знача1ций разряд кода. При этом на вькоде вычитающего счетчика 6 формируется двоичный код, равный т-1, являющийся характеристикой логарифма кода числа N по основанию два. Этот код поступает на входы старших разрядов первого входа умножителя 8. В первом блоке 2 постоя1П1ой памяти хранится 2 значений мантисс М -, логарифмов чисел по основанию два и 2 значений разностей дМ, двух смежных значений мантисс. Мантиссы М . соответствуют диапазону чисел от 1 до 2 с щагом 2 и определяются выражением о1,( ), где код k старших разрядов, начиная с п-1-го разряда, после сдвипа на n-m разрядов, а iiM, соответствует разности двух смежных мантисс кодов чисел на расстоянии шага 2. Пос :е появления в старшем разряде сдвигающего регистра 1 единицы на вькоде k разрядов этого регистра, начиная с п-1 разряда, формируется код, являющийся кодом адреса для вывода соответствуюш,их этому значению адреса мантисс-ы М ( и разности мантисс ЛМх из первого блока 2 постоянной памяти. Значение мантиссы М поступает на первый вход сумматора 4. Раз.ность мантисс ДМг. поступает на второй вход первого умножителя 3, на первый вход которого поступает код с выхода младших разрядов сдвигающего регистра 1, значение которого определяется выражением 2 /N л, i. / Это значение кода в первом умножите$ 1

ле 3 умножается на лм,, а так как каждый разряд выхода первого умножителя 3 подключен к второму входу сум матора 4 со сдвигом Ha.n-() разрядов вправо, то на втором входе сумматора значение поправки имеет вид

йМ.г- /.п-т М 2П-( .

Полученное значение поправки к мантиссе ДМ|ц в сумматоре 4 складывается со значением мантиссы М, поступающей с выхода первого блока 2 постоянной памяти. Этот код поступает на входы младших разрядов первого входа второго умножителя 8.

В результате на первом входе второго умножителя 8 будет логарифм кода числа N по основанию два в виде

to 2 №-l4-eo 2 )

018196

ДвоАный код числа а, являющийсязаданным основанием логарифма, поступает на вход основания-устройства и используется как код адреса для выво5 да значения логарифма кода числа 2 по заданному основанию с(( 2 из второго блока 7 постоянной памяти. Это значение логарифма поступает на второй вход второго умножителя 8, на вьгходе которого получаем окончательный результат.

Оценивая технико-экономическую эффективность предлагаемого цифрового лoгapифмичiecкoгo устройства следует отметить, что в нем реализована возможность вычисления логарифма по любому заданному основанию. Указанная особенность позволяет использовать однотипные устррйства для решения различных задач,, например таких как получение выходных отсчетов, выраженных в децибеллах, неперах и т.д. без предварительного пересчета одних единиц в другие.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Цифровое логарифмирующее устройство | 1985 |

|

SU1262490A1 |

| Устройство для логарифмирования чисел | 1980 |

|

SU926655A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Устройство трансляции | 1986 |

|

SU1390629A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Устройство для спектрального анализа | 1984 |

|

SU1241256A1 |

| Устройство для вычисления логарифмов | 1972 |

|

SU479110A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

ЦИФРОВОЕ ЛОГАРИФМИЧЕСКОЕ УСТРОЙСТВО, содержащее сдвигающий регистр, первьй блок постоянной памяти, первый умножитель, сумматор, причем выходы старших разрядов сдвигающего регистра соединены с входом первого блока постоянной памяти, выход мантиссы которого подключен к первому входу сумматора, отличающееся тем, что, с целью расширения класса решаемых задач путем вычисления логарифмов чисел по любому основанию, в нега дополнительно введен вычитающий счетчик, второй блок постоянной памяти, второй умножитель и блок управления, который содержит задающий генератор, первый, второй и третий элементы И и триггер, причем вход аргумента устройства соединен с информационным входом сдвигающего регистра, выход первого старшего разряда которого подключен к первому входу первого элемента И блока управления, вход запуска устройства соединен с первым входом второго элемента И блока управления и установочным входом вычитающего счетчика, выход которого подключен к старшим разрядам первого входа второго умножителя, вход основания устройства соединен с входом второго блока.постоянной памяти, выход которого подключен к второму входу второго умножителя, выход третьего элемента И блока управления соединен со счетным входом вычитающего счетчика и управляющим входом сдвига- § ющего регистра, выход младших разря(Л дов которого подключен к первому входу первого умножителя, выход разности мантисс первого блока постоянной памяти соединен с вторым входом первого умножителя, выход которого подключен к второму входу сумматора, выход которого соединен с младшими разрядами первого входа второго умножителя, выход которого подключен к выходу устройства, причем в блоке уп00 равления инверсный выход задающего ге нератора соединен с вторыми входами со первого и второго элементов И, прямой выход задающего генератора подключен к первому входу третьего элемента И, второй вход которого соединен с единичным выходом триггера, вход сброса которого подключен к выходу первого элемента И, -выход второго элемента соединен с входом установки триггера.

Ф14г.1

15

Фмг.2

Авторы

Даты

1984-07-07—Публикация

1983-02-08—Подача