Изобретение относится к вычислительной технике, может быть использовано в цифровых и вычислительных комплексах, работающих в системах управления с высокими требованиями к скорости выполнения вычислений и является усовершенствованием устройства по авт. св. № 744654.

Цель изобретения - расширение функциональных возможностей за счет вычисления аппроксимирзтощих полиномов без предварительной нормализации.

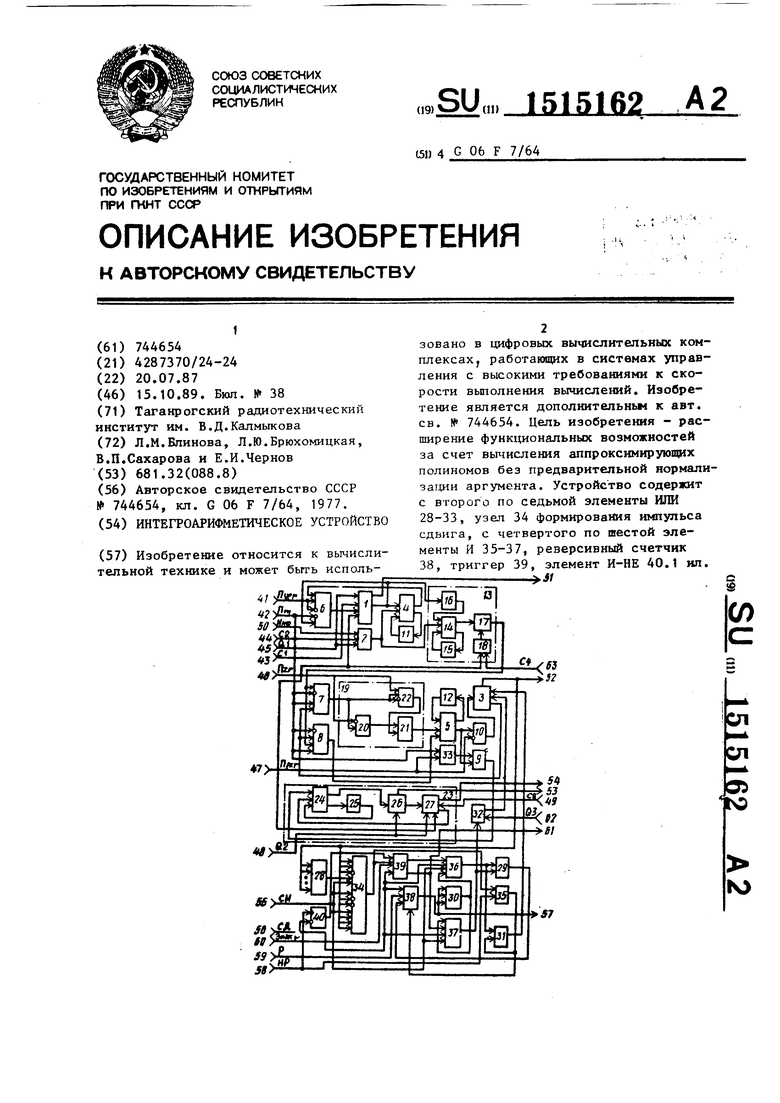

На чертеже изображена структурная

порядка, вход 58 HP признака нормализации, вход 59 Р порядка, вход 60 Знак Р знака порядка, выходы 61 знака порядка, вход 62 Q3 управления сдвигом в сторону младших разрядов третьего сдвигающего регистра, вход 63 С4 синхронизации занесения в четвертый регистр.

Интегроарифметическое устройство работает следующим образом.

В зависимости от значений входных признаков в устройстве могут вьшолнять ся 8 модификаций операций интегриро

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных комплексах, работающих в системах управления с высокими требованиями к скорости выполнения вычислений. Изобретение является дополнительным к авт.св. N 744654. Цель изобретения - расширение функциональных возможностей за счет вычисления аппроксимирующих полиномов без предварительной нормализации аргумента. Устройство содержит со второго по седьмой элементы ИЛИ 28-33, узел 34 формирования импульса сдвига, с четвертого по шестой элементы И 35-37, реверсивный счетчик 38, триггер 39, элемент И-НЕ 40. 1 ил.

схема интегроарифметического устройст-15 вания по формуле трапеций, определяемых сочетанием признаков П , П , nLjKr (при П О, СД-0, ), операции умножение-сложение (при , П О, ,0, , , ), умножение-вычитание (при , , , П|.|,0, , ), нормалива.

Интегроарифметическое устройство содержит первый 1 - третий сдвигающие регистры 1-3, первый 4 и второй 5 сумматоры, первьй - третий элементы 2И- 20 ИЛИ 6-8, первый 9, второй 10 элементы И, первый 11, второй 12 элементы задержки, формирователь 13 приращений в составе третьего сумматора 14, третьеЙР зация (при , , , ,

П , логический сдвиг (при , , , , . П

ykr

ikr

го 15 и четвертого 16 элементов задерж 5 0) ,

П ,

ки, умножителя 17, четвертого регистра 18, преобразователь 19 кода, содержащий третий элемент И 20, первый элемент ИЛИ 21, преобразователь 22 доОперации нормализации и логического сдвига выполняются над операндом R, представленном в дополнительном коде с фиксированной запятой, причем

полнительного кода, экстрйполятор 23, 30 / R/ 1, являющимся результатом пре- состоящий из четвертого сумматора 24, дьщущей опера1щи, который к началу распятого элемента 25 задержки, пятого 26 и щестого 27 сдвигающих регистров, второй - седьмой элементы ИЛИ 28-33, узел 34 формирования импульса сдвига, четвертый - шестой элементы И 35-37 реверсивный счетчик 38, триггер 39, элемент И-НЕ 40, вход 41 П р признака вычисления подынтегральной функции, вход 42 П признака умножения, вход 43 С1 синхронизации занесения в первый сдвигающий регистр, вход 44 С2 синхронизации занесения во второй сдвигающий регистр, вход 45 Q управления сдвигом в сторону младших разрядов первого и второго сдвигающих регистров, вход 46 П признака инверсии кода, вход 47 П, признака квантования приращения интеграла.

сматриваемых операций хранится в сдвигающем регистре 3. При вьтолнении операций нормализации осуществляется зс СДВИГ в сторону старших разрядов содержимого сдвигающего регистра 3 до появления в старшем (первом справа пос (пе знакового) разряде 1 мантиссы значащей единицы и формирование значения двоичного порядка, который явля40

ется всегда отрицательным, т.к. / R/ 1 . Если

О и достаточньм условием сдвига для нормализации является наличие д5 нуля в первом старшем разряде мантиссы, т.е.

р. гДг, .

1) необходимо рассмот

При R . О (Гд

вход 48 Q2 управления сдвигом в сторо- д реть два случая.

ну младших разрядов пятого и шесто-Если / R / 2 1 k N-1 где

го сдвигающих регистров, вход 49 С81 k «i N-1 - целочисленная величина;

синхронизации занесения в шестой сдви- гаюш;ий регистр, входная информацион- ная шина 50 Инф, выходы 51 подын- тегральной функции, выходы 52 мантиссы, выходы 53 приращения, выходы 54 остатка, вход 55 СИ синхронизации, вход 56 СД признака сдвига, выходы 57

N - разрядность R с учетом знака и, соответственно, количество разрядов регистра 3, то условием сдвига для нормализации является наличие единиц в двух старших разрядах мантиссы, т.е

р1

вания по формуле трапеций, определяемых сочетанием признаков П , П , nLjKr (при П О, СД-0, ), операции умножение-сложение (при , П О, ,0, , , ), умножение-вычитание (при , , , П|.|,0, , ), нормали 0) ,

ЙР зация (при , , , ,

П , логический сдвиг (при , , , , . П

ykr

ikr

Операции нормализации и логического сдвига выполняются над операндом R, представленном в дополнительном коде с фиксированной запятой, причем

сматриваемых операций хранится в сдвигающем регистре 3. При вьтолнении операций нормализации осуществляется СДВИГ в сторону старших разрядов содержимого сдвигающего регистра 3 до появления в старшем (первом справа пос- (пе знакового) разряде 1 мантиссы значащей единицы и формирование значения двоичного порядка, который явля

ется всегда отрицательным, т.к. / R/ 1 . Если

О и достаточньм условием сдвига для нормализации является наличие д5 нуля в первом старшем разряде мантиссы, т.е.

р. гДг, .

1) необходимо рассмот (Гд

N - разрядность R с учетом знака и, соответственно, количество разрядов регистра 3, то условием сдвига для нормализации является наличие единиц в двух старших разрядах мантиссы, т.е.

р1

Если ;R| 5 2- и /R/,2-, то это условие не является достаточным для правильной нормализации таких чисел, т.к. всегда будет недоставать 1-го такта сдвига и для этого случая,кроме данного условия, нужно анализировать состояние, когда в первом старшем разряде единица, во втором - ноль и в оставшихся 3-(N-1) раз-10 на входных шинах 59, 60 соответственрядах мантиссы есть хотя бы одна значащая единица, т.е. для случая

f5

Р

г.

Формирование сигналов сдвига при нормализации осуществляется элементом ИЛИ 28, узлом 34, элементами И 35, 20 ИЛИ 31, синхронизация сдвига производится синхронизирующими импульсами СИ, поступающими в устройство по входной шине 55. Формирование двоичного порядка осуществляется путем подсчета им- 25 прохождение импульсов СИ с входной пульсов сдвига реверсивным счетчикомшины 55 через один из элементов И 36,

38, знак порядка фиксируется в Д-триг- если р О, или И 37, если р ;0. При гер 39. При этом формирование условий сдвига р, , ро , РФ и сдвигающих импульр О сдвиг содержимого сдвигающего регистра осуществляется в сторону

сов производится узлом 34, аналия ус1- 4ловия V Г реализует элемент ИЛ}1 28.

1-3

Импульсы сдвига при нормализации, снимаемые с выхода узла 34, поступают на элемент 35, и т.к. на входной шине 58 признак , проходят через элементы И 35, ила 31 на вход сдвига в сторону старших разрядов регистра 3. Кроме того, импульсы сдвига с выхода элемента И 35 поступают на вход суммирования реверсивного счетчика 38, насчитывающего величину порядка. Выход узла 34 заводится и на S-вход D-триггера 39, и первый же импульс сдвига при нормализации взводит В-три1тер в единичное состояние, фиксируя знак минус порядка. Значение нормализованной мантиссы со знаком порядка и знака порядка поступают соответственно на выходные шины устройства 52, 57, 61 с пара1тлельного выхода сдвигающего регистра 3, с выхода реверсивного счетчика 38, с единичного выхода триг30 стар лмх разрядом, при р О в сторону г-1Падшнх разрядов, .аля этого выход эле- г-;ен7 а И 36 через элемент ШШ 31 заводится на вход управления сдвигом в с.торону старших разрядов сдвигающего

-j регистра 3, выход элемента И 37 через Э7;емент ИЛИ 32 на вход сдвига в сторону младпшх разрядов сдвигающего регистра 3. Кроме того, каждый и глульс сдвига с выходов aneMei-foe И 36 или

40 37 через элемент 1ШИ 29 заводится на вычитающий вход реверсивного счетчика 38 и приход каж,ого нового импульса вызывает уменьпекие содержимого счетчика 38 на единицу. Операция сдвига

45 оканчивается после установки ревпрсив- ного счетчика 38 в нупеБпс состояшю. При этом на выходе элемента И, Ш 30 устанавливается нулевой сигнал, закрывающий элементы И 36, 37 для прохож50 дения СИ. D-триггер 39 по R-входу пос- ле окончания операции сдвига (CD-0) через элемент 40 устанавливается в нулевое состояние.

Выполнение операций умноженяя гера 39. После окончания операнда нор- сложение z yx+R, умножение - вычимализации триггер 39 через элемент 40, выход которого заводится на его R- вход, сбрасывается в нулевое состояние. При выполнении операции логичестание Z -R+yx начинается после поступления по входной информаггионной щине 50 Инф множимого у, множ; теля X, заносимых паралле 1Ь}1ые входы

1626

кого сдвига осуществляется сдвиг содер жимого сдвигающего регистра 3 на ко- , личество разрядов / н сторону млад- ших разрядов, еслир :0, т.е. знак р - 1 или, в сторону старших разрядов, если , т.е. знак р 0.

К моменту начала операции значения Р и Знак Р должны быть выставлены

5

0

но. Операция начинается после подачи ка входную шину 56 устройства признака , поступающего на С-входы D- триггера 39 и реверсивного счетчика 38, и синхронизир тощего занесения в D-триггер 39 через вход D знака порядка с входной шины 60 Знак Р и в реверсивньй счетчик через параллельный вход значения порядка с входной шины 59 Р. Если р О, на выходе элемента ИЛИ 30, количество входов которого равно количеству разрядов реверсивного счетчика 38, устанавливается единичный сигнал, который разрешает

если р О, или И 37, если р ;0. При

р О сдвиг содержимого сдвигающего регистра осуществляется в сторону

если р О, или И 37, если р ;0. При

стар лмх разрядом, при р О в сторону г-1Падшнх разрядов, .аля этого выход эле- г-;ен7 а И 36 через элемент ШШ 31 заводится на вход управления сдвигом в с.торону старших разрядов сдвигающего

регистра 3, выход элемента И 37 через Э7;емент ИЛИ 32 на вход сдвига в сторону младпшх разрядов сдвигающего регистра 3. Кроме того, каждый и глульс сдвига с выходов aneMei-foe И 36 или

37 через элемент 1ШИ 29 заводится на вычитающий вход реверсивного счетчика 38 и приход каж,ого нового импульса вызывает уменьпекие содержимого счетчика 38 на единицу. Операция сдвига

оканчивается после установки ревпрсив- ного счетчика 38 в нупеБпс состояшю. При этом на выходе элемента И, Ш 30 устанавливается нулевой сигнал, закрывающий элементы И 36, 37 для прохождения СИ. D-триггер 39 по R-входу пос- ле окончания операции сдвига (CD-0) через элемент 40 устанавливается в нулевое состояние.

Выполнение операций умноженяя тание Z -R+yx начинается после поступления по входной информаггионной щине 50 Инф множимого у, множ; теля X, заносимых паралле 1Ь}1ые входы

сдвигающего регистра 2 и регистра 18 в моменты времени, соответствующие поступающим по входным шинам 44, 63 сигналам синхронизации занесения в регистр 2 (С2) и в регистр 18 (С4). Операнд R является результатом предыдущей операции и к началу рассматриваемых операций хранится в сдвигаюЕсли сомножители у,х имеют разряд- нос ть N с учетом знака двоичных разрядов, произведение их имеет разрядность 2N-1. Принимая, что исполнение

щам регистре 3. После занесения в ин- JQ операций умножение-сложение, умножение-вычитание начинается в 1-м такте после считывания операндом, сигналы Q1, Q3 управления сдвигом регистра 2,3 в сторону младших разрядов должны содержать N и 2N-1 тактов с 1-го по 1+N-1, в (1+2N-1)-M также результат операции может считываться через выходную шину 52 устройства.

Величина 1 (в количестве тактов) выбирается достаточной для записи в интегроарифметическое устройство сомножителей х,у.

Устройство может вычислять интегралы стильтеса.

Алгоритм реализации г-й опера4 и й

интегрирования по формуле трапе1Ц1й в итегроарифме п чесгком устройстве имеет .

V

20

25

тегроарифметическое устройство для операций умножения - сложение, умножение - вычитание информации на входы управления сдвигом в сторону младших разрядов сдвигающих регистров 15 2,3 подаются соответствен но сигналы Q1 с входной шины 45, Q3 с входной шины 62 через элемент ИЛИ 32. При этом код множимого у с последовательного выхода сдвигающего регистра 2 через сумматор 14, на второй вход которого поступает нулевая информация с последовательного выхода регистра 1, без изменения проходит на вход множимого параллельно-последовательного умножителя 17, на вход множителя ко-- торого поступает параллельньш код множителя с выхода регистра 18. С выхода умножителя 17 снимается последовательный код произведения, имеющего удвоенную разрядность по сравнению с разрядностью сомножителей у, х, который через второй элемент И элемента 2И-ИЛИ 8 заводится на второй вход сумматора 5, на первый вход сумматора 5 5 при вьтолнении операции умножение - сложение (П,, 1, И 0) через первый элемент И элемента 2И-ИЛИ 7, элементы И 20, ИЛИ 21 поступает неизменное значение R с последовательного вы-40 хода сдвигающего регистра 3 при сдвиге в сторону мпадших разрядов. При выполнении операции умножение -вьии30

Ург(им ypf iitji

VS

+ (U,))Vypr(i

)7

рг (Ui) (Ург 4(UO 8(r-0(uoПik(..) V(.

y( %kr S(;..)

VyK(;,,i PiV-if Mi O ,

Оущн.) P NnlvyM o +оУк; / J

где знак -J над функцией или приращением означает ограничение разрядности мантиссы до N-1 разрядов (от 1 до N-1), разряд О - знак, Р z - оператор вьщеления из переменной z разрядов от а до Ь, О ,j - остаток квантования переменной у в точке (i+1).

тание (П

m

Uy 1) последовательньй код операнда R через первый элемент И элемента 2И-ИПИ 7 поступает в преобразователь 22 дополнительного кода, где осуществляется его инвертирование с преобразованием в дополнительный код, и величина (-R)9on элемент ИЛИ 21 заводится на перньш вход сумматора 5. Результат операции умножение-сложение z yx+R или ум- Ножение-вычитание z yx-R с выхода сумматора 5 через элемент И 10, открытый, т.к. на входной пшне 47 признак Пд( 0, заводится на последовательный вход сдвигающего регистра 3 при сдвиге в сторону младших разрядо

Результат вьполнения операции умножение - сложение, умножение - вычитание остается в регистре 3 и поступает на входную шину 52.

Если сомножители у,х имеют разряд- нос ть N с учетом знака двоичных разрядов, произведение их имеет разрядность 2N-1. Принимая, что исполнение

операций умножение-сложение, умножение-вычитание начинается в 1-м такте после считывания операндом, сигналы Q1, Q3 управления сдвигом регистра 2,3 в сторону младших разрядов должны содержать N и 2N-1 тактов с 1-го по 1+N-1, в (1+2N-1)-M также результат операции может считываться через выходную шину 52 устройства.

V

ypf iitji

+ (U,))Vypr(i

)7

(Ург 8(r-0(uoПik(..) V(.

y( %kr S(;..)

VyK(;,,i PiV-if Mi O ,

Оущн.) P NnlvyM o +оУк; / J

где знак -J над функцией или приращением означает ограничение разрядности мантиссы до N-1 разрядов (от 1 до N-1), разряд О - знак, Р z - оператор вьщеления из переменной z разрядов от а до Ь, О ,j - остаток квантования переменной у в точке (i+1).

Рассмотрим вычислительный процесс выполнения одной операции интегрирования в (i+1)-M шаге решения.

Выполнение операции начинается после поступления через входную ин- формационную шину 50 приращений

&Ур(1+1), Уор(1+1) подынтегральной

функции у

рг;

соответственно на входы

параллельного занесения регистров 2, 18, 1, синхронизация занесения в которые осуществляется сигналами С2, С4, С1, поступающими на входы С регистров 1, 18, 2 с входных шин 44, 63, 43. Кроме того, для операций, выпол- няемых с квантованием приращений (П(1), в регистр 27 через вход параллельного занесения по сигналу Сб с BKoflHOH шины 49 осуществляется занесение остатка Су,; , поступающего по шине 50 ИФ. По ршнам 41, 46, 47 в устройство поступают признаки Ui.. zh -fkr определяющие тип операции интегрирования: с инверсией прираще- ния V Spnp(;4,)( 1) нпи без инвер- сии П2 О, с образованием Урр(;41) (Пщ,1) или без изменения у.

,

(Пирр 0), с квантованием результата ( 1) или без квантования (n,L 0).

Признаки Пурр , П2.ГП , Пц. должны сохранять свои значения в течение всей длительности вьтолнения операции

После занесения в интегрсарифмети чаское устройство необходимой для начала вычислений информации и установления на шинах 41, 46, 47 признаков операций интегрирования на входы управления сдвигом в сторону младших разрядов регистров 1 и 2, 3 и 26 и 27 с входных шин 45, 62, 48 соответственно поступают сигналы сдвига Q1, Q2, Q3, причем количество тактов сдвига Q1 равно N+1, Q3 и 02-2N. Значения приращение УУрг(;ч.)И подын- тегральной функции с последовательных выходов регистров 1,2 поступают на входы сумматора 4, формирующего ypr(i+1) и формирователя 13 приращений Бгтчисляющего значение VS (i+1).

Если . О, то содержимое регистра 1 (урр; ) при сдвиге перезаписывается через первьш элемент И эле- дЗ мента 2И-ИЛИ 6. При Пцрп 1 в регистр 1 через второй элемент И элемента 2И- ИПИ 6 записьшается новое значение y pp(i+l) с выхода сумматора 4. В формирователе 13 приращений урр; перед Q поступлением на сумматор 14 задерживается элементом 16 задержки на 1 такт, и таким образом обеспечивается сдвиг в в сторону младших разрядов приращения V У prt отношению к подынтеграль- з ной функции Ур,; на один такт, необходимый для вычисления величины +

1 + У ) реализуемой сумматором

г 10 15

20

35

0

З Q , з

На выходе умножителя 17 формируется чпадшими разрядами вперед 2К-разряд- ное приращение 7 Spn г (Uib которое через второй элемент И элемента 2И-ИЛИ 7 проходит на преобразователь 19 кода, где при Пг.- О проходит без изменения через элементы И 20,Р1ПИ 21 на первьп вход сумматора 5, а при

1 инвертируется с преобразова.- тёлем в дополнительный код в преобразо- вателе 22 дополнительного кода и через элемент ИЛИ 21 также поступает на первый вход сумматора 5. Если при выполнении предьщущей (г-1)-й операции интегрирования оканчивалось вычисление очередной строки РСЗТП Пг,.( 1, содержимое регистра 3 очистилось при сдвиге, в г-й операции на второй вход сумматора 5 поступает нулевая информация из регистра 3 и приращение без изменения записывается в регистр 3 через элемент И 10, если Пг|, О, :щи через элемент И 9 noCTiTiaeT в блок эксграполяции 23, если , 1. О, го после (г-1)-й операции интегрирования в регистр 3 через элемент И 10 записалось значеш1е

br(i+i) в г операции складывается в сумматоре 3 с приращем1ем

Spqr(i + i) Полученное значение у S,,-, записывается в регистр 3 при Hri 0 или проходит в блок экстраполяции 23, если П.)р 1. В блоке экстрапачяции 23 приращение ,,,,, 4kr- У(,, суммируется в сумматоре 24 с остатком , поступающим с последовательного выхода сдвигающего регистра 27. Полученная в сумматоре 24 сумма У(/,4|) - У kI записывается ; регистры 26, 27. После вьтолнения операции новое значение остатка О у, .записывается в регистры 27, ,)ванное приращение ;гу(1+1) в регистры 27, квантованное пpиpaщeнIie P y(i+1) в регистр 26 и через параллельные выходы регистров 26, 27 приращение v Vvis i) и остаток О у, через выходные шины 53, 54 соответственно выдаются на выход устройства.

Формула изобретения

Интегроарифметическое устройство по авт. св. № 744654, отличаюния функциональных возможностей за счет вычисления аппроксимируизщих полиномов без предварительной нормали- зации аргумента, оно содержит с второго по седьмой элементы ШШ, узел формирования импульсов сдвига, с четвертого по шестой элементы И, реверсивный счетчик, триггер и элемент И-НЕ, причем выходы трех старших разрядов третьего сдвигакщего регистра соединены с первыми тремя управляющими входами узла формирования импульсов сдвига соответственно, а остальные выходы этого регистра подключены к входами второго элемента ИЛИ, выход которого соединен с четвертым управляющим входом угла формирования импульсов сдвига, выход которого соединен с входом установки в 1 триггера и первым входом четвертого элемента И, вход которого соединен с входом сложения реверсивного счетчика, прямой выход триггера соединен с первым входом пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ выход которого соединен с входом вычислителя реверсивного счетчика, выходы которого соединены с выходами по- рядка устройства и входами четвертого элемента ИЛИ, выход которого соединен с вторым входом пятого элемента И и первым входом шестого элемента И, выход пятого элемента И соединен с первым входом пятого элемента ИЛИ, выход которого соединен с входом управления сдвигом в сторону старших разрядов третьего сдвигающего регист

Составитель А.Чеканов Редактор М.Циткина Техред Л.ОлийныкКорректор М.Васильева

Заказ 6277/46

Тираж 668

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

50

5

ра, а второй вход подключен к выходу четвертого элемента И, вход признака сдвига устройства соединен с первым входом элемента И-НЕ, третьим входом пятого элемента И, управляющим входом реверсивного c leтчикa, входом синхронизации триггера и вторым входом шестого элемента И, выход которого соединен с вторым входом третьего элемента ШШ и первым входом шестого элемента ИЛИ, выход которого соединен с входом управления сдвигом в сторону младших разрядов третьего сдвигающего регистра, инверсный выход триггера соединен с третьим входом шестого элемента И и выходом знака порядка устройства, вход признака нормализации устройства соединен с вторыми входами элемента И-НЕ и четвертого элемента И, выход элемента И-НЕ соединен с входом установки в О триггера, вход синхроимпульсов устройства соединен с входом синхроимпульсов узла формирования импульса сдвига, четвертым входом пятого элемента И и третьим входом шестого элемента И, вход знака порядка устройства соединен с D-входом триггера, входы порядка устройства соединены с инфо1 мационными входами реверсивного счетчика, входы признака умножения и признака квантования приращений интеграла соединены соответственно с первым и вторым входами седьмого элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, вход управления сдвигом устройства соединен с вторым входом шестого элемента ИЛИ.

Подписное

| Интегро-арифметическое устройство | 1977 |

|

SU744654A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-15—Публикация

1987-07-20—Подача