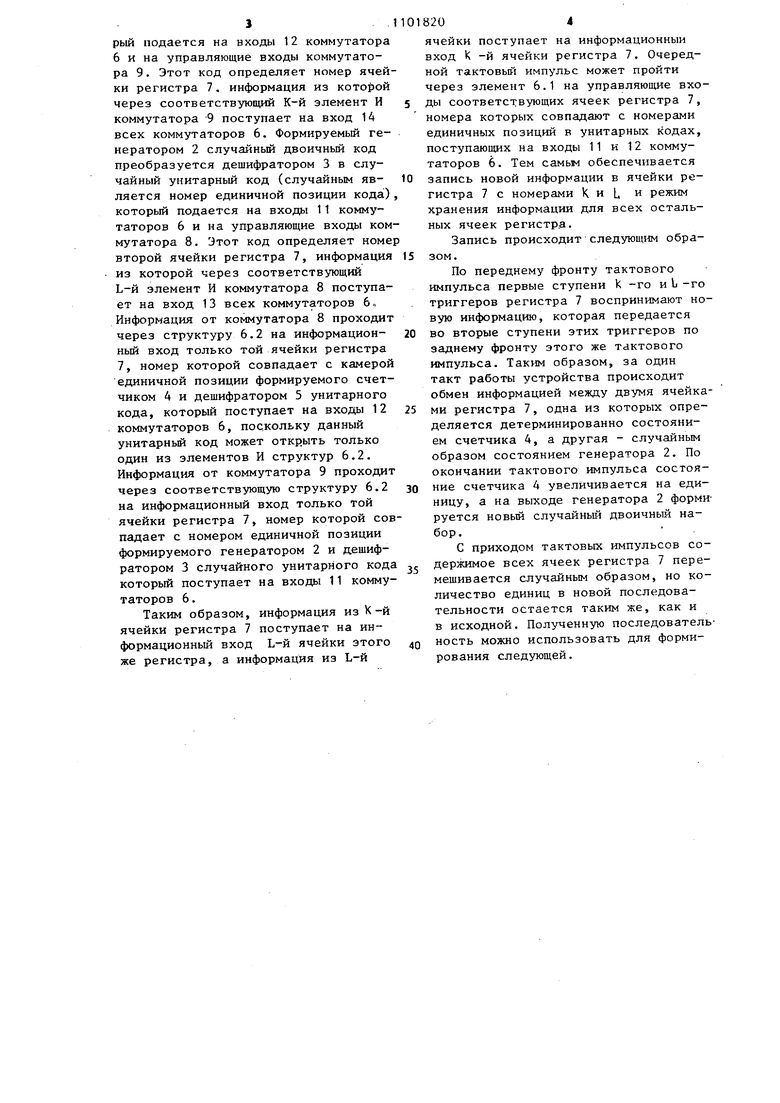

11 Изобретение относится к автоматике и вычислительной технике и может быть использовано при математическом моделировании сетей связи,систем управления, в системах формирования ключевых кодов, устройствах формирования специальных сигналов, в составе автоматизированных систем управле ния и контроля. В указанных областях возникает не обходимость формирования всех случай ных кодов, содержащих гп позиций, на равно h из которых располагаются еди ницы, а на остальных № - И - нули. Известны устройства, обеспечивающие получение последовательности кодов, содержащих m позиций, на п из которых располагаются единицы, а на остальных m - п - нули 1 j , Недостатком этих устройств являет ся их сложность. Наиболее близким к изобретению яв ляется датчик случайных последовательностей, содержащий генератор так товых импульсов, выход которого соединен со счетным входом счетчика и с входом Опрос генератора случайных кодов, первый и второй блоки сравнения, первый, второй и третий су2«}маторы, первый и второй вычитател первый и второй делители, умножитель компаратор, ключ, элементы ИЛИ и И-НЕ 2 . Недостатком известного устройства является низкое быстродействие за счет необходимости выполнения опера дий деления и .умножения двоичных чисел. Целью изобретения является повышение быстродействия устройства. Для достижения поставленной цели в датчик случайных последовательное тей, содержащий генератор тактовьп г-мпульсов, выход которого соединен со счетным входом счетчика и с входом Опрос генератора случайных кодов, введены два дешифратора, группа коммутаторов 5 регистр памяти и два коммутатора, выходы которых соединены соответственно с первым и вто рЪми информационными входами коммутаторов группы, синхронизирующие входы которых подключены к выходу генератора тактовых импульсов, вькюдь первого дешифратора соединены с группой управляющих входов первого коммутатора соответственно и с первы ми управляющими входами соответстную 0 щих коммутаторов группы, выходы второго дешифратора соединены с группой управляющих входов второго-коммутатора соответственно и с вторыми управляющими входами соответствующих коммутаторов группы, первый и второй выходы каждого из которых соединены соответственно с информационным и синхронизирующим входами соответствующего разряда регистра памяти, выходы которого соединены с группами информационных входов первого и второго коммутаторов соответственно. jНа фиг. 1 приведена структурная схема генератора; на фиг. 2 - схема одного коммутатора из группы коммутаторов. Предлагаемый датчик содержит генератор 1 тактовых импульсов, генератор 2 случайных кодов, дешифратор 3, счетчик 4, дешифратор 5, коммутаторы 6, регистр 7 памяти, коммутаторы 8 и 9, входь 10 - 14 коммутаторов 6. Все блоки предложенного устройства могут быть выполнены на основе серийных интегральных схем. Работа датчика основана на методе случайных перестановок, который заключается в следующем. Дана произвольная т-разрядная двоичная последовательность, в которой находится И равных единице разрядов. Берется первый разряд последовательности и его значение обменивается со значением случайно выбранного ра:зряда этой же последовательности. Затем берется второй разряд данной последовательности и его значение обменивается со значением другого случайно выбранного разряда этой же последовательности. Указанная процедура повторяется in ра.з. В результате получается последовательность, отличающаяся от исходной позициями единичных разрядов, но количество единиц при этом не изменяется . В исходном положении счетчик 4 находится в нуле, а в регистре 7 хранится произвольное т-разрядное двоичное число, ц произвольных позиций которого заняты единицами. Рассмотрим работу датчика в течение одного такта. Пусть состояние счетчика 4 равно k, а состояние генератора 2 - h Состояние счетчика 4 преобразуется дешифратором 5 в унитарный код,, кото3

рый подается на входы 12 коммутатора 6 и на управляющие входы коммутатора 9. Этот код определяет номер ячейки регистра 7. информация из которой через соответствующий К-й элемент И коммутатора 9 поступает на вход 14 всех коммутаторов 6. Формируемый генератором 2 случайный двоичный код преобразуется дешифратором 3 в случайный унитарный код (случайным является номер единичной позиции кода) который подается на входы 11 коммутаторов 6 и на управляющие входы коммутатора 8. Этот код определяет номер второй ячейки регистра 7, информация из которой через соответствующий L-Й элемент И коммутатора 8 поступает на вход 13 всех коммутаторов 6, Информация от коммутатора 8 проходит через структуру 6.2 на информационный вход только той ячейки регистра 7, номер которой совпадает с камерой единичной позиции формируемого счетчиком 4 и дешифратором 5 унитарного кода, который поступает на входы 12 коммутаторов 6, поскольку данный унитарный код может открыть только один из элементов И структур 6.2. Информация от коммутатора 9 проходит через соответствующую структуру 6.2 на информационный вход только той ячейки регистра 7, номер которой совпадает с номером единичной позиции формируемого генератором 2 и дешифратором 3 случайного унитарного кода который поступает на входы 11 коммутаторов 6.

Таким образом, информация из К-й ячейки регистра 7 поступает на информационный вход L-й ячейки этого же регистра, а информация из L-й

8204

ячейки поступает на информационный вход К -и ячейки регистра 7. Очередной тактовый импульс может пройти через элемент 6.1 на управляющие входы соответствующих ячеек регистра 7, номера которых совпадают с номерами единичных позиций в унитарных кодах, поступгиощих на входы 11 и 12 коммутаторов 6. Тем самьм обеспечивается запись новой информации в ячейки регистра 7 с номерами К и L, и режим хранения информации для всех остальных ячеек регистра.

Запись происходит следующим образом.

По переднему фронту тактового импульса первые ступени k -го и Ь-го триггеров регистра 7 воспринимают новую информацию, которая передается во вторые ступени этих триггеров по заднему фронту этого же тактового импульса. Таким образом, за один такт работы устройства происходит обмен информацией между двумя ячейками регистра 7, одна из которых определяется детерминированно состоянием счетчика 4, а другая - случайным образом состоянием генератора 2. По окончании тактового импульса состояние счетчика 4 увеличивается на единицу, а на выходе генератора 2 форми руется новьй случайный двоичный набор.

С приходом тактовых импульсов содержимое всех ячеек регистра 7 перемешивается случайным образом, но количество единиц в новой последовательности остается таким же, как и в исходной. Полученную последовательность можно использовать для формирования следующей.

-1 ::Я

N

ка

Vr,

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| УСТРОЙСТВО ДЛЯ ОБЪЕДИНЕНИЯ ЛЕКСИЧЕСКИХ МНОЖЕСТВ | 1990 |

|

RU2022354C1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| УНИВЕРСАЛЬНЫЙ ГЕНЕРАТОР ЕРМАКОВА-КАЖДАНА СПЕКТРА КУСОЧНО-ПОСТОЯННЫХ ФУНКЦИЙ (ВАРИАНТЫ) | 2001 |

|

RU2213996C2 |

| СИСТЕМА УЧЕТА ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 2003 |

|

RU2247994C1 |

| УСТРОЙСТВО ДЛЯ ПОВЕРКИ ИЗМЕРИТЕЛЕЙ ЧАСТОТЫ И ПЕРИОДА | 2009 |

|

RU2392633C1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Имитатор дискретного канала связи | 1989 |

|

SU1755293A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1166120A1 |

ДАТЧИК СЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащий генератор тактовых импульсов, выход которого соединен со счетным входом счетчика и с входом Опрос генератора случайных кодов, отличающийся тем, что, с целью повьшения быстроде1- ствия, он содержит два дешифратора,, группу коммутаторов, регистр памяти и два коммутатора, выходы которых соединены соответственно с первыми и вторыми информационными входами коммутаторов группы, синхронизирующие входы которых подключены к выходу генератора тактовых импульсов, выходы первого дешифратора соединены с группой управляющих входов первого коммутатора соответственно и с первыми управляющими входами соответствующих коммутаторов группы, выходь второго дешифратора соединены d группой управляющих входов второго коммутатора соответственно и с вторыми управляющими входами соответствующих коммутаторов группы, первый и второй выходы каждого из которых соединены (Л соответственно с информационным и синхронизирующим входами соответствующего разряда регистра памяти, выходы которого соединены с группами информационных входов первого и второго коммутаторов соответственно.

Cvl

Ь

It

TT

.i

Авторы

Даты

1984-07-07—Публикация

1982-12-24—Подача