Изобретение относится к радиотехнике и может быть использовано для анализа помехоустойчивости систем передачи дискретной информации.

Известен имитатор дискретного канала связи, содержащий сумматор по модулю два, блок синхронизации, генератор марковской последовательно,датчик случайных чисел, блок промежуточной памяти, пороговый сумматор и элемент И,

Недостатком известного устройства является отсутствие возможности моделировать поток ошибок в несимметричных каналах связи.

Наиболее близким к заявляемому является имитатор дискретного канала связи, содержащий сумматор по модулю два, блока синхронизации, генератор марковской последовательности, датчик случайных чисел, блок промежуточной памяти, пороговый сумматор и элемент И.

Недостатком прототипа являются узкие функциональные возможности, не позволяющие моделировать недвоичные дискретные каналы связи.

Целью изобретения является расширение функциональных возможностей устройства за счет моделирования недвоичных дискретных каналов связи.

Поставленная цель достигается тем, что в имитатор дискретных каналов связи, содержащий блок синхронизации, генератор марковской последовательности, первый пороговый сумматор, датчик случайных чисел, причем выход блока синхронизации соединен с входом синхронизации генератора марковской последовательности, выход тактовых импульсов которого подключен к тактовому входу блока синхронизации, первый выход синхроимпульсов генератора марковской последовательности подключен к входу синхронизации датчика случайных чисел,

группа выходов которого соединена с первой группой соответствующих информационных входов первого порогового сумматора, вторая группа информационных входов которого подключена к группе соответствующих выходов первого блока памяти, вход запуска блока синхронизации является входом запуска устройства, введены К-2 блоков памяти, К-2 пороговых сумматоров, где К-основание кода сигнала, первый и второй анализаторы кода, шифратор, сумматор, преобразователь унитарного ода в двоичный, регистр, причем вход первого анализатора кода и выход второго анализатора кода и выход второго анализатора кода являются соответственно информационных входом и выходом устройства, группа выходов первого анализатора кода соединена с группой соответствующих информационных входов шифратора, группа выходов которого подключена к первой группе соответствующих информационных входов сумматора и к первым группам соответствующих информационных входов ссех блоков памяти, к вторым группа информа- Ц1 -иных входов каждого из которых подключена группа соответствующих выходов генератора марковской последовательности, группа выходов каждого из 2 до К-1 блоков памяти соединена с второй группой информационных входов соответствующих пороговых сумматоров, к первым группам информационных входов которых подключена группа соответствующих выходов датчика случайных чисел, выход каждого из пороговых сумматоров подключен к соответствующему информационному входу преобразователя унитарного кода в двоичный, группа выходов которого соединена с второй группой соответствующих информационных входов сумматора, группа выходов которого подключена к соответствующим информационным входам регистра, группа выходов которого подключена к группе соответствующих информационных входов второго анализатора кода, второй выход синхроимпульсов генератора марковской последовательности соединен с управляющим входом регистра.

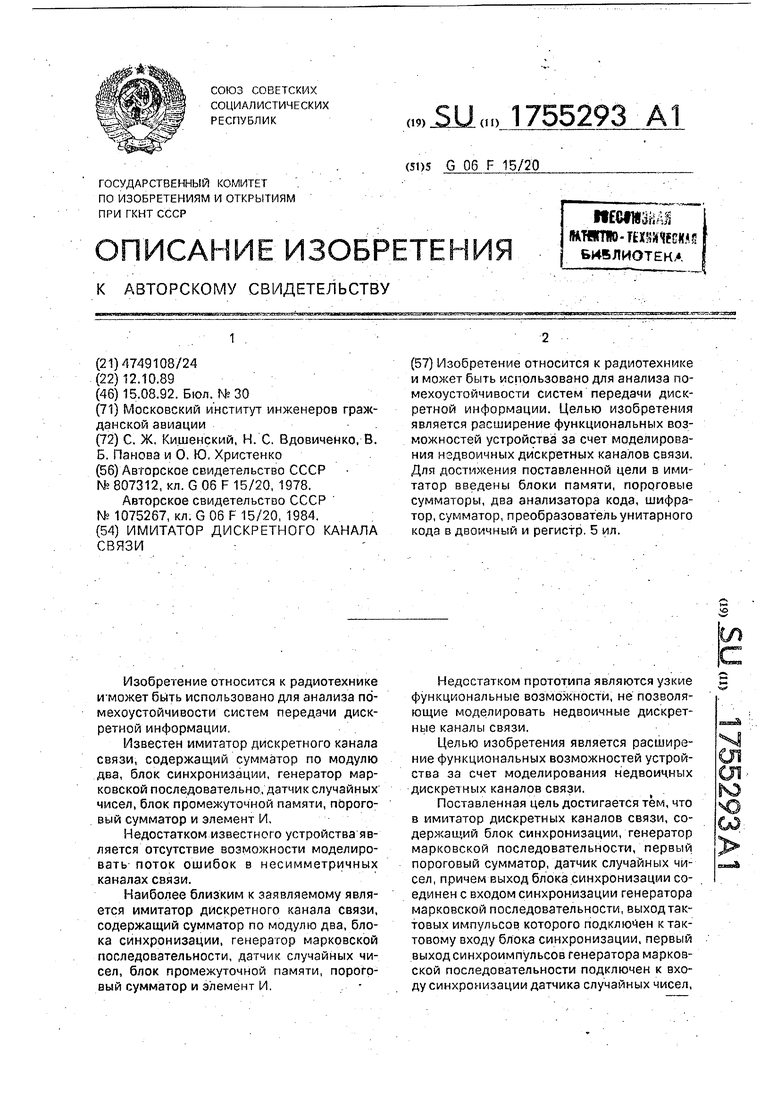

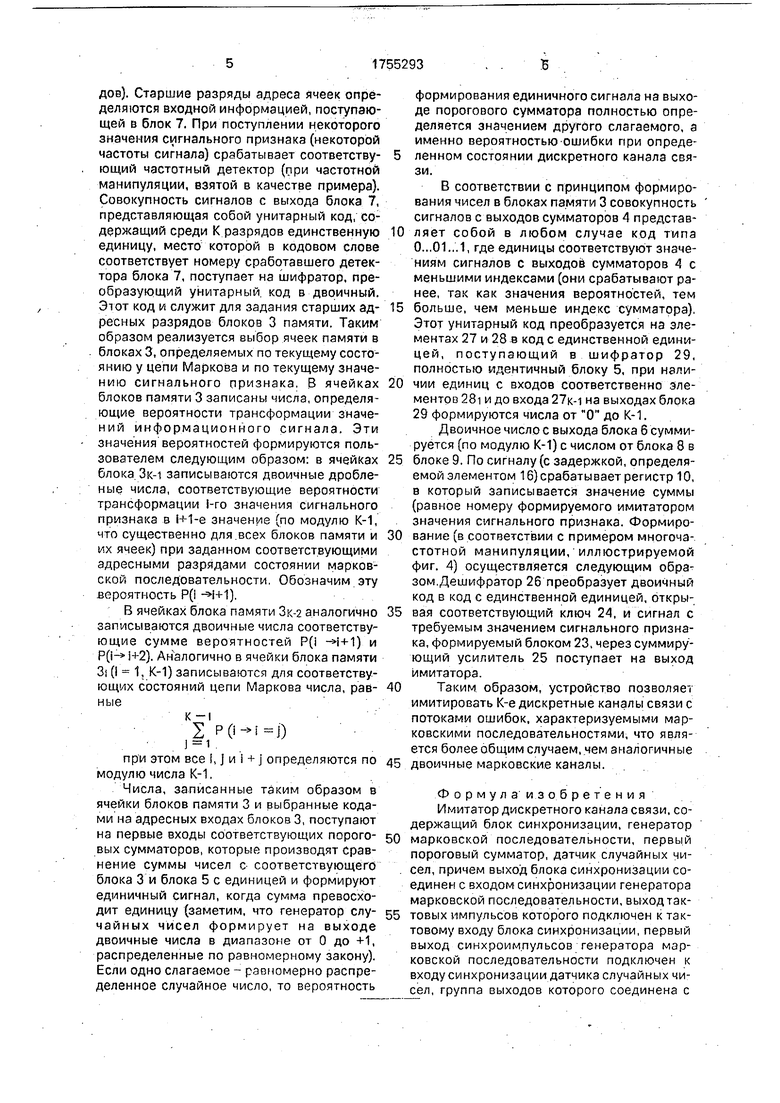

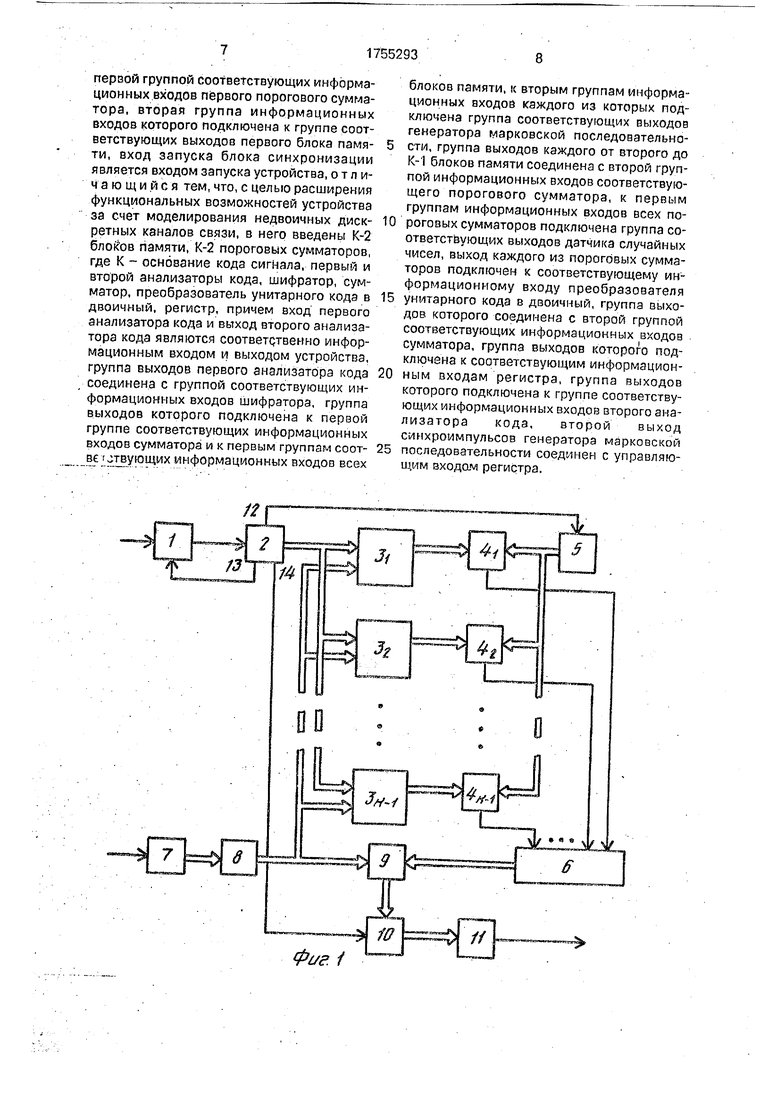

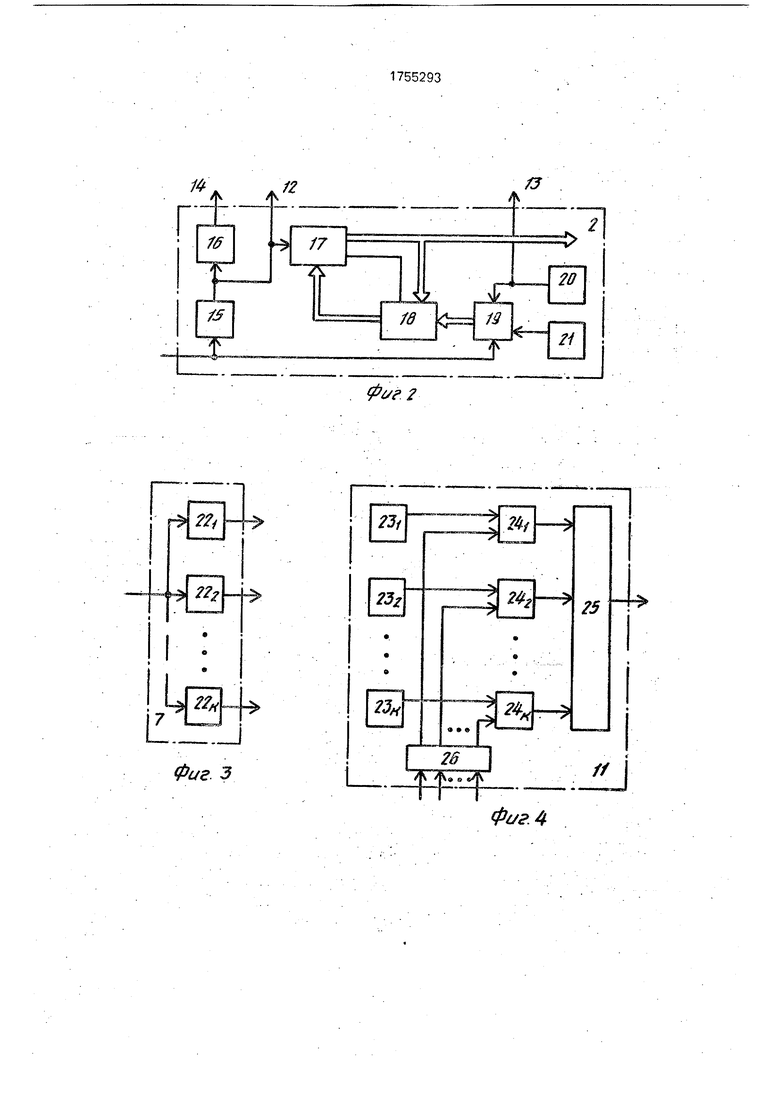

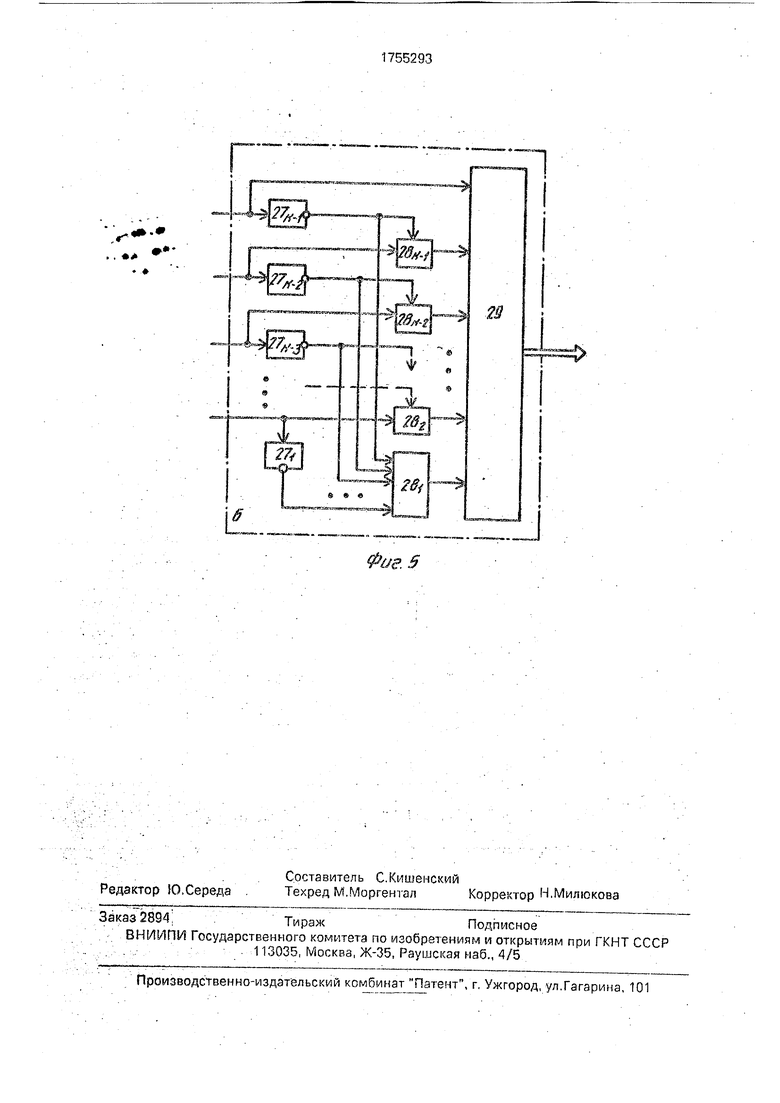

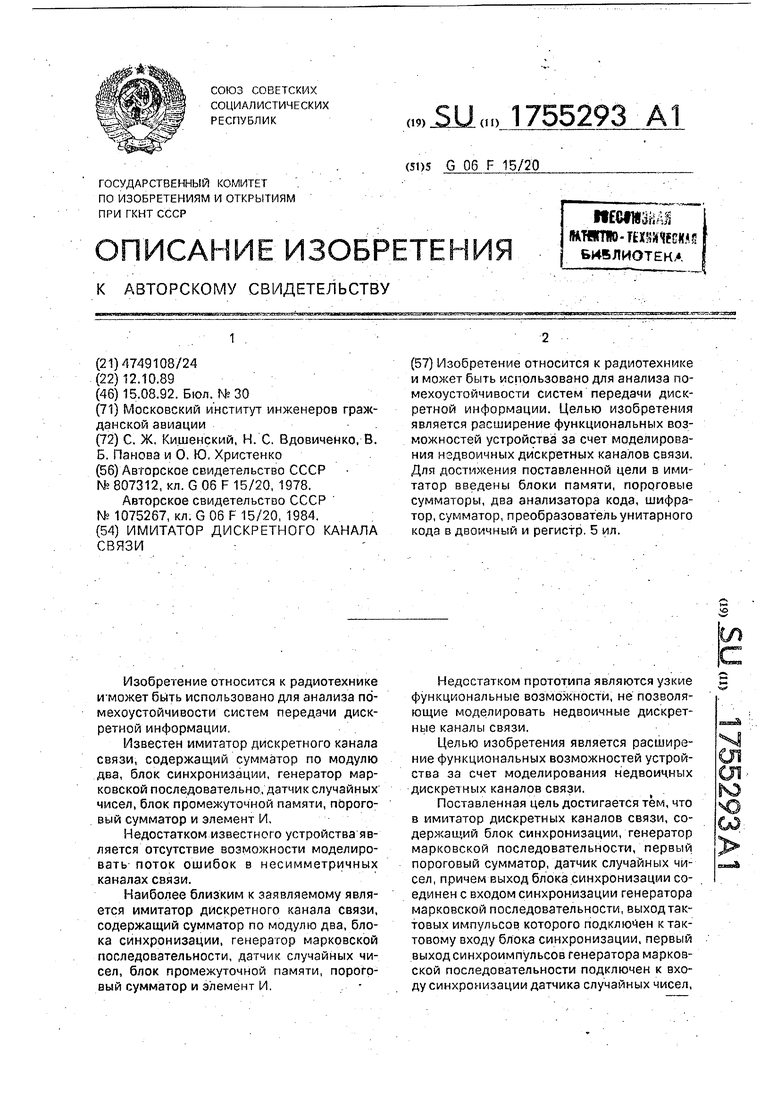

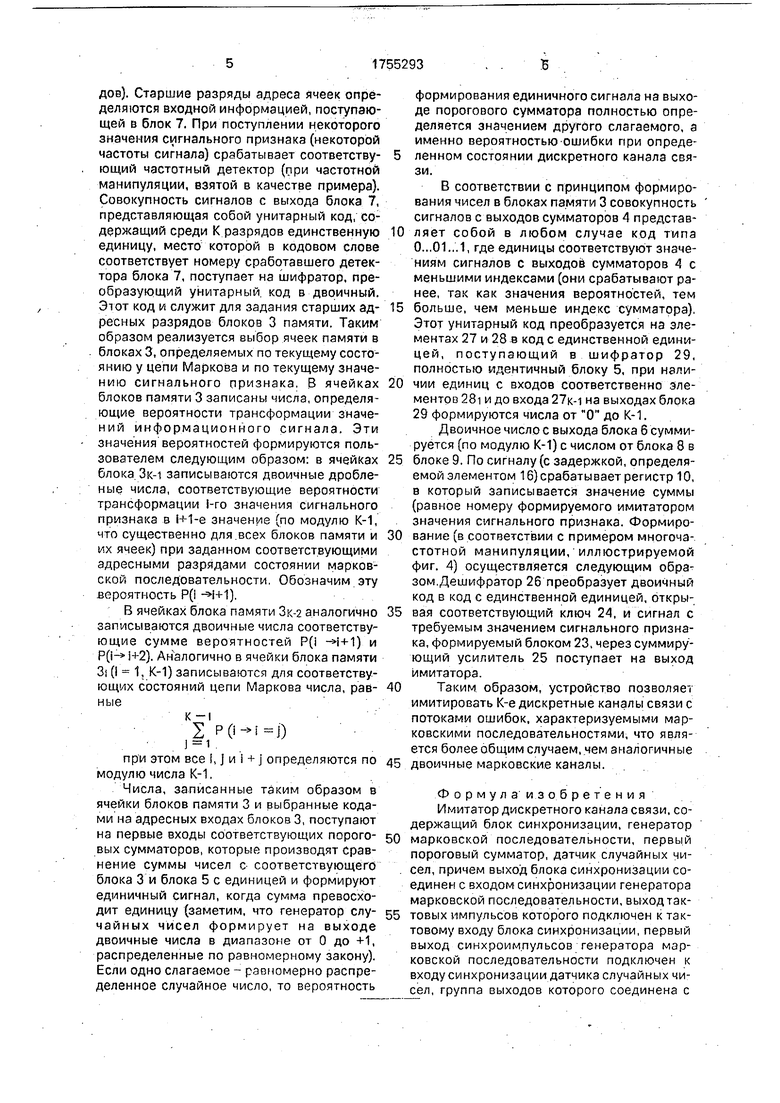

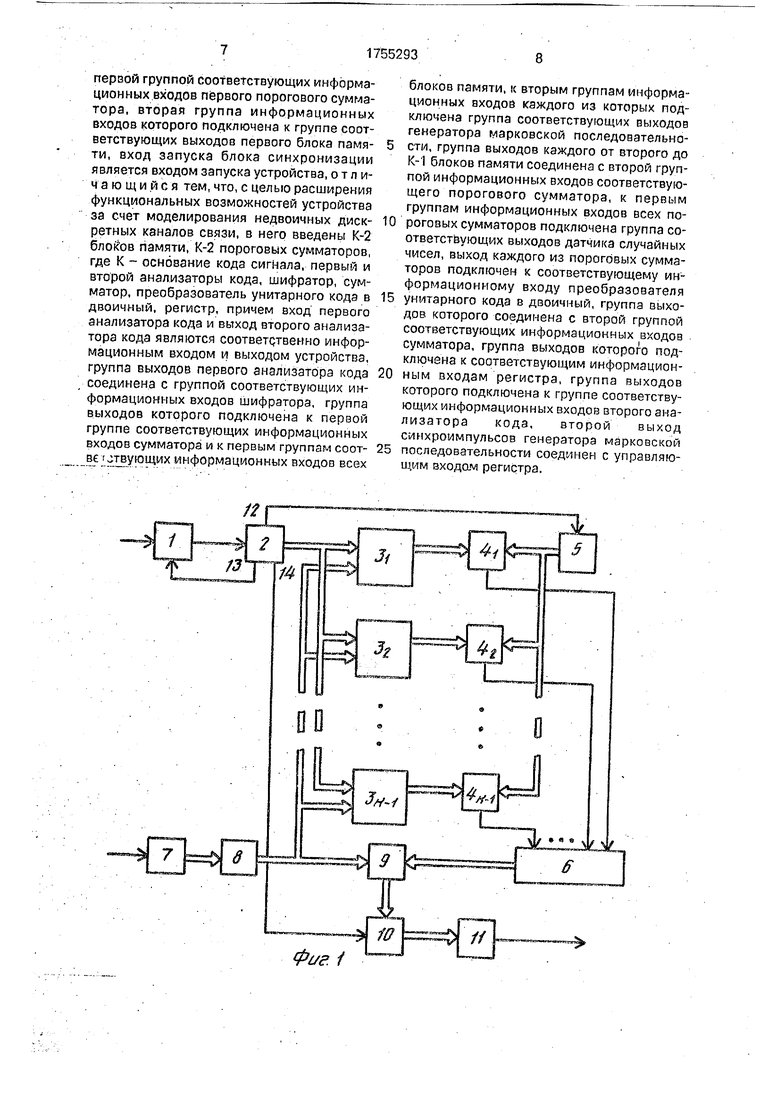

На фиг. 1 приведена структурная схема имитатора дискретного канала связи; на фиг. 2 - структурная схема генератора марковской последовательности; на фиг. 3 - структурная схема первого анализатора кода; на фиг. 4 - структурная схема второго анализатора кода; на фиг. 5 - структурная схема преобразователя унитарного кода в двоичный.

Имитатор дискретного канала связи содержит блок 1 синхронизации генератор 2

марковской последоватепьности, блока 3i Зк-1 памяти, пороговые сумматоры 4i-4«-i, датчик 5 случайных чисел, преобразователь б двоичного кода в унитарный, первый анализатор 7 кода, шифратор 8, сумматор 9, регистр 10 и второй 11 анализатор кода, первый выход 12 синхроимпульсов, выход 13 тактовых импульсов и второй выход 14 синхроимпульсов генератора 2.

0 Генератор марковской последовательности 2 (фиг. 2) содержит первый и второй элементы 15 и 16 задержки, регистр 17, сумматор 18, аналого-цифровой преобразователь 19, генератор 20 тактовых импульсов и

5 генератор 21 случайного сигнала. Первый анализатор 7 кода (фиг. 3} содержит мастот- ные детекторы 22-|-22к. Второй анализатор 11 кода содержит (фиг, 4) генераторы 231+23к, ключи 241-24к, суммирующий уси0 литель 25 и дешифратор 26. Преобразователь 6 унитарного кода в двоичный содержит (фиг. 5) элементы HF 27-|-27к-1, элементы И 28i-28x-i и шифратор 9.

Ус тройство работает следующим обра5 зом.

В его основе лежит имитация К-го дискретного канала связи (в качестве примера фиг. 3 и 4 иллюстрируют вариант реализации частотно-манипулированного миогоос0 новного сигнала). Сигнальный признак на входе имитатора с заданным стохастическими закономерностями преобразуется на выходе в тог или иной признак сигнала, чем имитируется погок ошибок разного типа в

5 К-м канале связи.

После запуска начинает работать блок 1, который периодически запускает генератор 2, работающий следующим образом (фиг. 2). По сигналу запуска с блока 1 и

0 тактовым импульсам с блока 20 в блоке 19 формируется цифровой эквивалент сигнала, формируемого блоком 21. Блоки 19 и 2 I настроены так, что формируемые чиста лежат в диапазоне от -1 до -М, причем старший

5 разряд числа, формируемого в блоке 19, является знаковым. Сформированное число алгебраически суммируется с содержимым регистра 17 в блоке 18 и некоторой задержкой, определяемой элементом 15 вновь за0 носится в регистр 17. Таким образом реализуется генерация марковской последовательности чисел, в которой каждое последующее число зависит от предыдущего Отдельный выход из блока 17 в блок 19 5 выход знакового разряда.

После определения очередного состояния цепи Маркова генератор 2 формирует на выходах регистра код состояния, который задает младшие разряды ячеек в блоках памяти 3 (группу младших адресных разрядов). Старшие разряды адреса ячеек определяются входной информацией, поступающей в блок 7. При поступлении некоторого значения сигнального признака (некоторой частоты сигнала) срабатывает соответствующий частотный детектор (при частотной манипуляции, взятой в качестве примера). Совокупность сигналов с выхода блока 7, представляющая собой унитарный код, содержащий среди К разрядов единственную единицу, место которой в кодовом слове соответствует номеру сработавшего детектора блока 7, поступает на шифратор, преобразующий унитарный код в двоичный. Этот код и служит для задания старших адресных разрядов блоков 3 памяти. Таким образом реализуется выбор ячеек памяти в блоках 3, определяемых по текущему состоянию у цепи Маркова и по текущему значению сигнального признака, В ячейках блоков памяти 3 записаны числа, определяющие вероятности трансформации значений информационного сигнала. Эти значения вероятностей формируются пользователем следующим образом: в ячейках Блока Зк-1 записываются двоичные дробленые числа, соответствующие вероятности трансформации 1-го значения сигнального признака в И-1-е значение (по модулю К-1, что существенно для всех блоков памяти и их ячеек) при заданном соответствующими адресными разрядами состоянии марковской последовательности. Обозначим эту вероятность P(i ).

В ячейках блока памяти Зк-2 аналогично записываются двоичные числа соответствующие сумме вероятностей P(i -H+1) и P(i- i+2). Аналогично в ячейки блока памяти 3) (I 1, К-1) записываются для соответствующих состояний цепи Маркова числа, равные

К -I

I ) J i

при этом все i, j и i + j определяются по модулю числа К-1,

Числа, записанные таким образом в ячейки блоков памяти 3 и выбранные кодами на адресных входах блоков 3, поступают на первые входы соответствующих пороговых сумматоров, которые производят сравнение суммы чисел с соответствующего блока 3 и блока 5 с единицей и формируют единичный сигнал, когда сумма превосходит единицу (заметим, что генератор случайных чисел формирует на выходе двоичные числа в диапазоне от 0 до +1, распределенные по равномерному закону). Если одно слагаемое - равномерно распределенное случайное число, то вероятность

формирования единичного сигнала на выходе порогового сумматора полностью определяется значением другого слагаемого, а именно вероятностью ошибки при определенном состоянии дискретного канала связи.

В соответствии с принципом формирования чисел в блоках памяти 3 совокупность сигналов с выходов сумматоров 4 представляет собой в любом случае код типа 0...01...1, где единицы соответствуют значениям сигналов с выходов сумматоров 4 с меньшими индексами (они срабатывают ранее, так как значения вероятностей, тем

больше, чем меньше индекс сумматора), Этот унитарный код преобразуется на элементах 27 и 28 в код с единственной единицей, поступающий в шифратор 29, полностью идентичный блоку 5, при наличии единиц с входов соответственно элементов 28i и до входа 27к-ч на выходах блока 29 формируются числа от О до К-1.

Двоичное число с выхода блока 6 суммируется (по модулю К-1) с числом от блока 8 в

блоке 9. По сигналу (с задержкой, определяемой элементом 16}срабатывает регистр 10, в который записывается значение суммы (равное номеру формируемого имитатором значения сигнального признака. Формирование (в соответствии с примером многочастотной манипуляции, иллюстрируемой фиг. 4) осуществляется следующим образом.Дешифратор 26 преобразует двоичный код в код с единственной единицей, открывая соответствующий ключ 24, и сигнал с требуемым значением сигнального признака, формируемый блоком 23, через суммирующий усилитель 25 поступает на выход имитатора.

Таким образом, устройство позволяет имитировать К-е дискретные каналы связи с потоками ошибок, характеризуемыми марковскими последовательностями, что является более общим случаем, чем аналогичные

двоичные марковские каналы.

Формула изобретения Имитатор дискретного канала связи, содержащий блок синхронизации, генератор

марковской последовательности, первый пороговый сумматор, датчик случайных чисел, причем выход блока синхронизации соединен с входом синхронизации генератора марковской последовательности, выход тактовых импульсов которого подключен к тактовому входу блока синхронизации, первый выход синхроимпульсов генератора марковской последовательности подключен к входу синхронизации датчика случайных чисел, группа выходов которого соединена с

первой группой соответствующих информационных входов первого порогового сумматора, вторая группа информационных входов которого подключена к группе соответствующих выходов первого блока памяти, вход запуска блока синхронизации является входом запуска устройства, отличающийся тем, что, с целью расширения функциональных возможностей устройства за счет моделирования недвоичных дискретных каналов связи, в него введены К-2 блоков памяти, К-2 пороговых сумматоров, где К - основание кода сигнала, первый и второй анализаторы кода, шифратор, сумматор, преобразователь унитарного кода в двоичный, регистр, причем вход первого анализатора кода и выход второго анализатора кода являются соответственно информационным входом и выходом устройства, группа выходов первого анализатора кода соединена с группой соответствующих информационных входов шифратора, группа выходов которого подключена к первой группе соответствующих информационных входов сумматора и к первым группам соот- ве г твующих информационных входов всех

блоков памяти, к вторым группам информационных входов каждого из которых подключена группа соответствующих выходов генератора марковской последовательности. группа выходов каждого от второго до K-l блоков памяти соединена с второй группой информационных входов соответствующего порогового сумматора, к первым группам информационных входов всех пороговых сумматоров подключена группа соответствующих выходов датчика случайных чисел, выход каждого из пороговых сумматоров подключен к соответствующему информационному входу преобразователя

унитарного кода в двоичный, группа выходов которого соединена с второй группой соответствующих информационных входов сумматора, группа выходов которого подключена к соответствующим информэционным входам регистра, группа выходов которого подключена к группе соответствующих информационных входов второго анализатора кода, второй выход Синхроимпульсов генератора марковской

последовательности соединен с управляющим входам регистра.

17

Г

t

Я

А

Ј

71

я

1

il

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор дискретного канала связи | 1989 |

|

SU1755292A1 |

| Имитатор дискретных каналов связи | 1979 |

|

SU842827A1 |

| Имитатор дискретного канала связи с ошибками синхронизации | 1980 |

|

SU934479A2 |

| Имитатор дискретного канала связи | 1981 |

|

SU964651A2 |

| Имитатор дискретного канала связи | 1980 |

|

SU951318A2 |

| Имитатор дискретного канала связи | 1978 |

|

SU807312A1 |

| Имитатор дискретного канала связи | 1988 |

|

SU1562926A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ СВЯЗИ | 2005 |

|

RU2286597C1 |

| Имитатор дискретного канала связи | 1986 |

|

SU1348853A2 |

| Имитатор дискретного канала связи | 1986 |

|

SU1425702A1 |

Изобретение относится к радиотехнике и может быть использовано для анализа помехоустойчивости систем передачи дискретной информации. Целью изобретения является расширение функциональных возможностей устройства за счет моделирова- ния нодвоичных дискретных каналов связи. Для достижения поставленной цели в имитатор введены блоки памяти, пороговые сумматоры, два анализатора кода, шифратор, сумматор, преобразователь унитарного кода в двоичный и регистр. 5 ил.

г.

Фиг Э

pv 2

IA .arj Ш..вЖ

//

Фиг. 4

zi

n

L, 41ад

Богатея.

| Имитатор дискретного канала связи | 1978 |

|

SU807312A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Имитатор дискретного канала связи | 1982 |

|

SU1075267A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-15—Публикация

1989-10-12—Подача