к входу блока синхронизации, соответ ствующие выходы которого соединены с управляющими входами ключей и первого запоминающего элемента, с треть им входом схемы вьщеления сигнала ошибки и с управляющим входом дополнительного счетчика, дополнительный выход блока синхронизации подключен к управляющему входу реверсивного счетчика, выходы реверсивного счетчи ка являются цифровым выходом устройства . 2. Устройство по пЛ, отличающееся тем, что, о целью повьшения помехозащищенности, в него введен сдвигаиш ий регистр, входы 74 которого соединены с выходами реверсивного счетчика соответствующий выход блока синхронизации подключен к управляющему входу сдвигающего регистра, выходы которого являются цифровым выходом устройства. 3. Устройство по пп. 1 и 2, отличающееся тем, что, с целью расширения диапазона входных сигналов, в него введен триггер знака, один вход которого подключен к выходу компаратора, а другой вход соединен с соответствук1щим выходом блока синхронизации, выход триггера знака подключен к соответствующему входу блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112375A1 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112373A1 |

| Устройство для логарифмирования отношения сигналов | 1985 |

|

SU1300506A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Интегратор | 1986 |

|

SU1401485A2 |

| Устройство для вычисления алгебраических выражений | 1979 |

|

SU864298A1 |

| Вычислительное устройство и запоминающий масштабно-суммирующий блок | 1980 |

|

SU1043670A1 |

| Цифровой измеритель температуры | 1985 |

|

SU1278621A1 |

| Логарифмический преобразователь (его варианты) | 1982 |

|

SU1078442A1 |

1. УСТРОЙСТВО ДЛЯ ЛОГАРИФМИРОВАНИЯ ОТНОШЕНИЯ СИГНАЛОВ, содержащее операционный усилитель,между инвертирующим входом и выходом которого включен интегрирующий конденсатор, к инвертирующему входу операционного усилителя подключен первый вывод масштабного резистора, второй вывод которого через первый ключ подключен к выходу источника опорного напряжения, выход операционного усилителя подключен к первому входу компаратора, генератор импульсов, реверсивный счетчик, блок синхронизации, первый выход которого подключен к управляющему входу первого ключа, о тличающееся тем, что, с целью повьшения точности в работе в условиях помех и -получения результата преобразования в цифре, в него введены второй, третий, четвертый, пятый, шестой и седьмой ключи, делитель напряжения, схема выделения сигнала оишбки, первый и второй запоминающие элементы и дополнительный счетчик, причем первые выводы второго, третьего и четвертого ключей соединены с вторым выводом масштабного резистора, вторые выводы второго и третьего ключей являются соответственно первым и вторым входами устройства, второй вьшод четвертого ключа подключен к выходу операционного усилителя, между инвертирующим входом и выходом операционного.усилителя включен пятый ключ, к выходу операционного усилителя подключены вход делителя напряжения и первый вывод шестого ключа, к выходу делителя напряжения подключен первый вывод седьмого ключа, вторые выводы шестого и седьмого ключей подключены к входу первого запоминающегд элемента, выход которого соединен с вторым Ю входом компаратора, выход которого СО подключен к первому входу схемы вы деления сигнала ошибки и к управляю «k щему входу реверсивного счетчика, к тактовому входу которого подключен выход генератора импульсов, выход схемы вьщеления сигнала ошибки через второй запоминающий элемент соединен с управляющим входом генератора импульсов, выход которого подключен к тактовому входу дополнительного счетчика, выход которого соединен с вторым входом схемы вьщеления сигнала ошибки, выход реверсивного счетчика подключен

Изобретение относится к устройствам преобразования отношения сигналов по логарифмическому закону и может быть использовано в аналоговых вычислительных машинах. Известно устройство для логарифми рования отношения сигналов, содержащее генераторы экспоненциальных напряжений , компаратор, запоминающее устройство, счетчик, генератор импульсов и блок управления lj . Однако устройство имеет низкую помехозащищенность, малый диапазон изменения входных сигналов, низкую точность работы. Наиболее близким к предложенному является устройство для логарифмирования отношения сигналов, содержащее операционный усилитель, между инвертирую1191м входом и выходом которого включен интегрирующий конденсатор к инвертирующему входу операционного усилителя подключен первый вьгоод пер вого масштабного резистора, второй вывод которого соединен с выходом ключа, вход которого подключен к выходу источника напряжения, выход опе рационного усилителя подключен к входу компаратора, выход которого подключен к входу генератора импульсов, выход которого соединен через второй масштабный резистор с инвертирующим входом операционного усилителя, выход блока синхронизации подключен к управляющему входу кЛюча и к первому входу элемента И, второй вход которого соединен с выходом генератора импульсов, выход элемента И подключен к входу счетчика, выходы которого являются цифровым выходом устройства, второй вход компаратора подключен к выходу источника опорного напряжения 2J. Однако известное устройство характеризуется низкой помехозащищенностью, имеет малый диапазон отношения сигналов и обладает низкой точностью работы. Целью изобретения является повьш1ение точности в работе в условиях помех и получение результата преобразования в цифре, а также повышение помехозащищенности и расширение диапазона входных сигналов. Поставленная цель достигается тем, что в устройство для логарифмирования отношения сигналов, содержащее операционный усилитель, между инвертирующим входом и выходом которого включен интегрирующий конденсатор, к инвертирующему входу операционного усилителя подключен первый вывод масштабного резистора, второй вывод которого через первый ключ подключен к выходу источника опорного напряжения, выход операционного усилителя подключен к первому входу компаратора, генератор

импульсовj реверсивный счетчик,блок синхронизации, первый выход которого подключен к управляющеме входу первого ключа, введены второй,трети четвертый, пятый, шестой и седьмой ключи, делитель напряжения, схема вьщелёния сигнала ошибки, первый и второй запоминающие элементы и дополнительный счетчик, причем первые выводы второго, третьего и четвертого ключей соединены с вторым выводом масштабного резистора,вторые выводы второго и третьего ключе являются соответственно первым и вторым входами устройства, второй вывод четвертого ключа подключен к выходу операционного усилителя,межд инвертирующим входом и выходом операционного усилителя включен пятый ключ, к выходу операционного усилителя подключены вход делителя напряжения и первый вывод шестого ключа, к выходу делителя напряжения подключен первый вывод седьмого ключа, вторые выводы шестого и седьмого ключей подключены к входу первого запоминающего элемента, выход которого соединен с вторым входом ко 4паратора, выход которого подключен к первому входу схемы выделения сигнала ошибки и к управляющему входу реверсивного счетчика, к тактовому входу которого поключен выход генератора импульсов, выход схемы вьщелёния сигнала ошибки через второй запоминающий элемент соединен с управляющем входом генератора импульсов, выход которого подключен к тактовому входу додополнительного счетчика, выход которого соединен с вторым входом схемы вьщелёния сигнала ошибки,выход реверсивного счетчика подключен к входу блока синхронизации, соответствующие выходы которого соедине вы с управляющими входами ключей и первого запоминающего элемента, с третьим входом схемы вьщелёния сигнала ошибки и с управляющим входом дополнительного счетчика, дополнительный выход блока синхронизации подключен к управляющему входу реверсивного счетчика, выходы реверсивного счетчика являются цифровым выходом устройства.При этом в устройство введен сдвигающий регистр, входы которого соединены с выходами реверсивного

счетчика, соответствующий выход блока синхронизации подключен к управляющему входу сдвигающего регистра, выходы которого являются цифровым выходом устройства.

Кроме того, в устройство введен триггер знака, один вход которого подключен к выходу компаратора,а другой вход соединен с соответствующим выходом блока синхронизации, выход триггера знака подключен к соответствующему входу блока синхронизации.

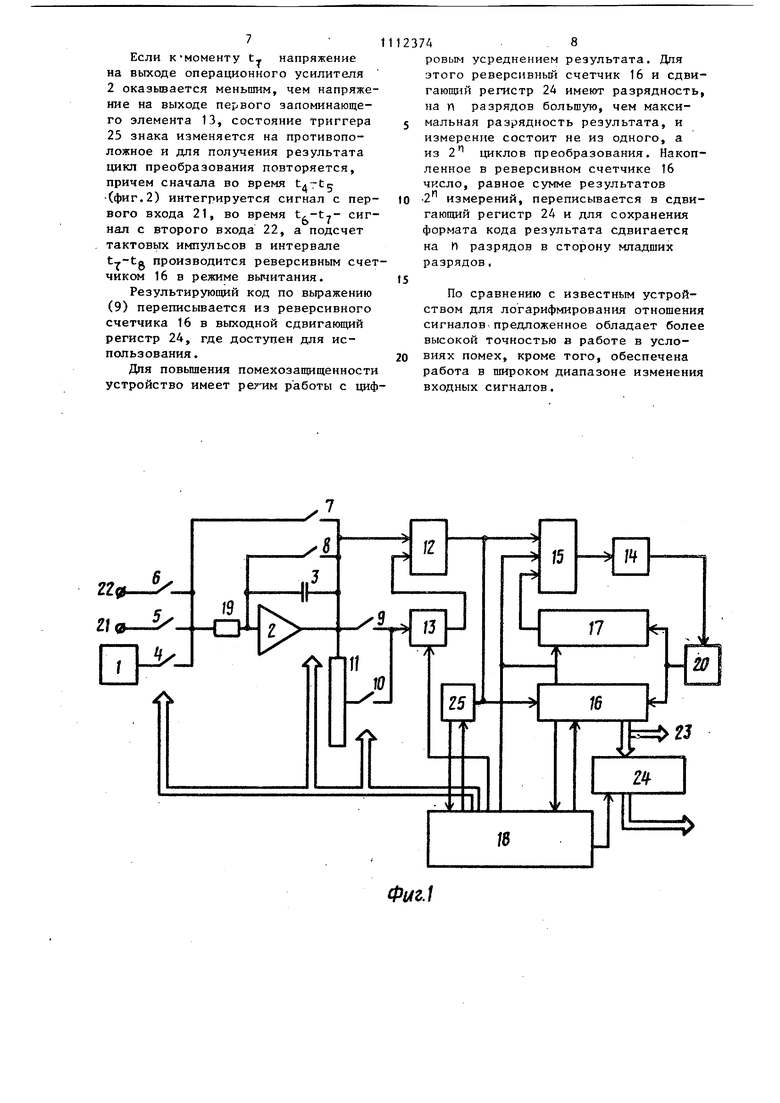

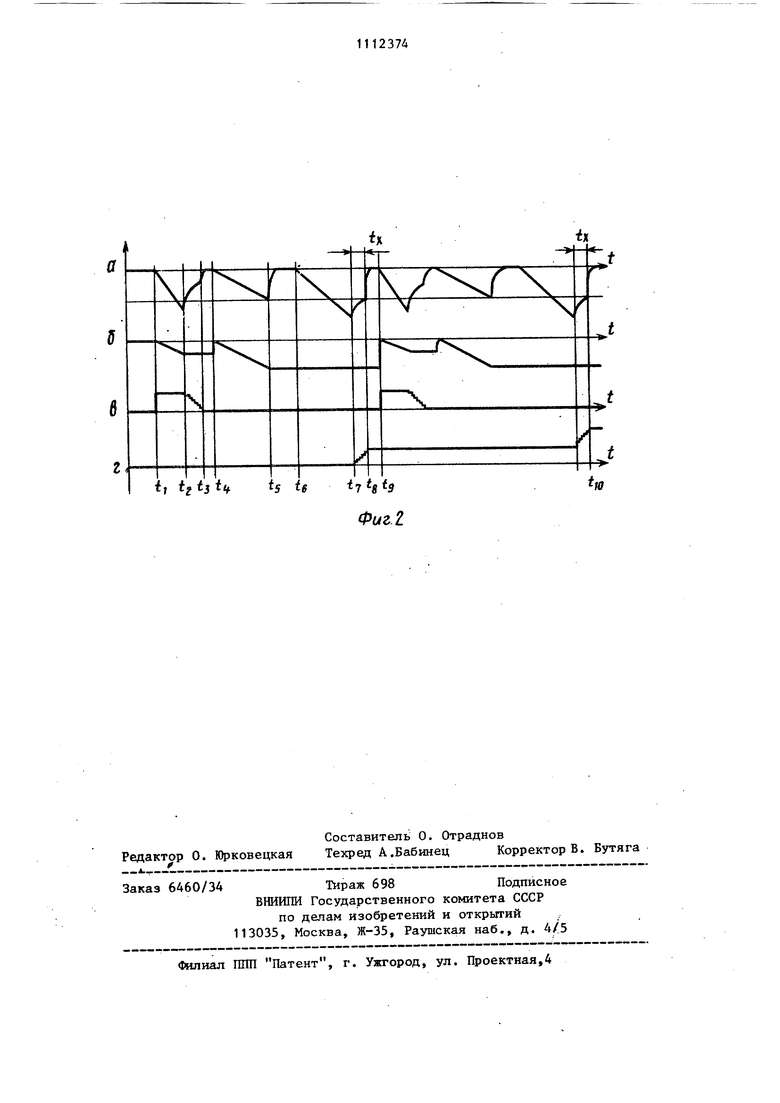

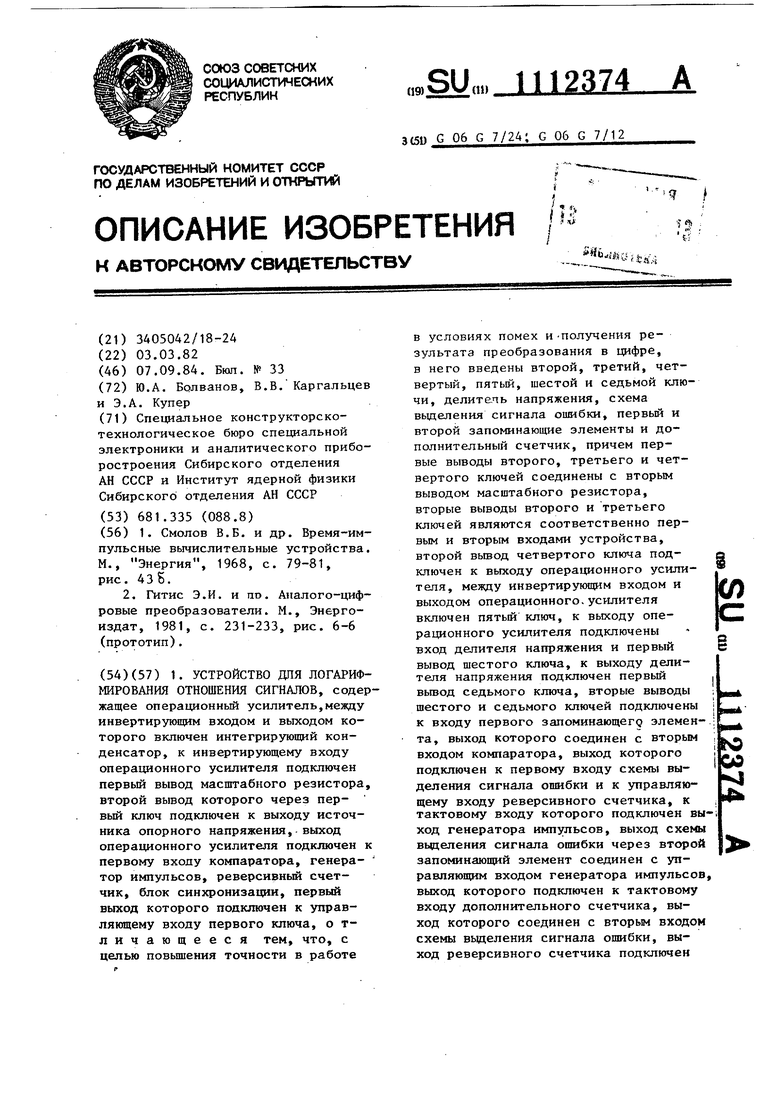

На фиг.1 изображена функциональн схема устройства для логарифмирования отношения сигналов; на фиг.2 - временные диаграммы сигналов.

Устройство содержит источник 1 опорного напряжения, операционный усилитель 2, интегрирующий конденсатор 3, первый, второй, третий, четвертый, пятый, шестой и седьмой ключи 4-10, делитель 11 напряжения, компаратор 12, первый и второй запоминающие элементы 13 и 14, схему 15 вьщелёния сигнала ошибки, реверсивный счетчик 16, дополнительный счетчик 17, блок 18 синхронизации, масштабный резистор 19, генератор 20 импульсов, первый и второй входы 21 и 22, выход 23, сдвигающий регистр 24 и триггер 25 знака.

На фиг.2 изображены временные диаграммы; d - сигналов на выходе операционного усилителя - сигналов на выходе первого запоминающего элемента 13; g, - условного состояния дополнительного счетчика 17, 2. условного состояния реверсивного счетчика 16.

Устройство работает следующим образом.

Во время (фиг.2) замкнуты первый и седьмой ключи 4 и 10, остальные ключи разомкнуты, на интегрирующем конденсаторе 3 накапливается напряжение от источника 1 опорного напряжения, первый за, поминаю1Щ1й элемент 13 отслеживает, определенную часть выходного напряжения операционного усилителя 2.

К моменту to (фиг.2) напряжение на выходе операционного усилителя 2 равно

(4-t,), S - напряжение источника опорного напряжения, R и С - сопротивление и емкост соответственно масшта ного резистора 19 и интегрирующего конден сатора 3. В момент tp (фиг.2) первый запоминаюпщй элемент 13 переводится в режим хранения, на его выходе фи сируется напряжение и,, и,..А где А - коэффициент передачи делите ля 11 напряжения. Одновременно с этим размыкается первый ключ 4, замыкается четверты ключ 7, обеспечивающий разряд интегрирующего конденсатора 3 по экспоненциальному закону, и включается на вычитание дополнительньм счетчик 17, имеющий цифровую уставку, пропорциональную логарифм коэффициента передачи делителя.11 напряжения. Момент времени t Хфиг.2) определяется компаратором 12, когда на пряжение на выходе операционного усилителя 2 сравнивается с напряже нием на первом запоминающем элемен те 13. Интервал времени to-to равен t-j-t -КС-бп А .. К моменту времени t (фиг.2) до полнительный счетчик 17 подсчитьша ет количество импульсов N -К-гп А, где К - постоянная. Время счета от числа (4) до нуля равно -Т. К. Еп А, где Т - период следования импульсов генератора 20. Схема |5 наделения сигнала ошибки сравнивает времена по вьфажениям (3) и (5), полученную разность преобразует в напряжение и через второй запоминающийэлемент 14 подает сигнал на управляющий вход генератора 20 импульсов. Частота его меняется так, чтобы разность уменьшалась. Пос 74 ле нескольких циклов автоподстройки времена сравниваются -Т. К-бп А -RC.en-A(6) RC, к -:г- COn5t . И Таким образом, результатом калибровки является сохранение постоянства отношения параметров, согласно выражению (7), при воздействии дестабилизирующих факторов. В интервале - обнуления интегрирующего конденсатора 3 замкнут пятый ключ 8. Далее в интервале (фиг.2) интегрируется сигнал с второго входа 22, замкнут шестой ключ 9, первый запоминающий элемент 13 находится в режиме слежения . В момент tc (фиг.2) первый запоминающий элемент переводится в режим хранения. В интервале tg-tg (фиг.2) интегрирующий конденсатор 3 снова обнуляется замыканием пятого ключа 8, а во время -, интегрируется сигнал с первого входа 21. В момент t (фиг.2) включается четвертый ключ 7 и интегрирующий конденсатор 3 разряжается через масштабный резистор 19. Компаратор 12 определяет время,когда напряжение на выходе операционного усилителя 2 сравнивается с запомненным напряжением, пропорциональным напряжению с второго входа 22. Время tg-t (фиг.2) равно , где Uj - напряжение на втором входе 22, Un - напряжение на первом входе 21. Реверсивный счетчик 16 в течение времени по выражению (8) ведет подсчет тактовых импульсов. К моменту t« (фиг.2) количество импульсов равно К, ..,«.вД JT;- в интервале tgt () интегрирующий конденсатор 3 снова обнуляется замыканием пятого ключа 8. 7 Если кмоменту t, напряжение на выходе операционного усилителя 2 оказьгоается меньшим, чем напряжение на выходе первого запоминающего элемента 13, состояние триггера 25 знака изменяется на противоположное и для получения результата цикл преобразования повторяется, причем сначала во время (фиг.2) интегрируется сигнал с первого входа 21, во время t, сиг нал с второго входа 22, а подсчет тактовых импульсов в интервале производится реверсивным счет чиком 16 в режиме вычитания. Результирующий код по выражению (9) переписывается из реверсивного счетчика 16 в выходной сдвигающий регистр 24, где доступен для использования. Для повышения помехозащищенности устройство имеет ре7-им работы с циф

.1 48 ровым усреднением результата. Для этого реверсивный счетчик 16 и сдвигающий регистр 24 имеют разрядность, на п разрядов большую, чем максимальная разрядность результата, и измерение состоит не из одного, а из 2 циклов преобразования. Накопленное в реверсивном счетчике 16 число, равное сумме результатов 2 измерений, переписывается в сдвигающий регистр 24 и для сохранения формата кода результата сдвигается на И разрядов в сторону младших разрядов. По сравнению с известным устройством для логарифмирования отношения сигналов предложенное обладает более высокой точностью в работе в условиях помех, кроме того, обеспечена работа в широком диапазоне изменения входных сигналов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Смолов В.Б | |||

| и др | |||

| Время-импульсные вычислительные устройства | |||

| М., Энергия, 1968, с | |||

| Цилиндрический сушильный шкаф с двойными стенками | 0 |

|

SU79A1 |

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Гитис Э.И | |||

| и по | |||

| Аналого-цифровые преобразователи | |||

| М., Энергоиздат, 1981, с | |||

| Машина для удаления камней из почвы | 1922 |

|

SU231A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-07—Публикация

1982-03-03—Подача