4

lOO

сд со

Изобретение относится к запоминающим устройствам.

Поосновному авт. св. № 963107 известно устройство для контроля блока памяти, содержащее входной егистр, регистр адреса, дешифратор адреса, схему сравнения, первый элемент ИЛИ, выход которого подключен к входу регистра адреса, одни из выходов которого соединены с первыми выходами устройства,.а ругой выход подключен к входу ешифратора адреса, одни из выхоов которого соединены с вторыми выходами устройства, выходы входного регистра подключены к третьим ыходам устройства и к одним из. ходов схемы сравнения, другие вхоы которой соединены с первыми . входами устройства, второй элеент ИЛИ, пять элементов И, два триггера, формирователь импульсов, ричем второй вход устройства подключен к первым входам первого и пятого эле.ментов И, выход первого элемента И соединен с первыми входами второго и третьего элементов И и счетным входом первого триггера, нулевой выход которого подключей к второму входу третьего элеента И и первому входу второго элемента ИЛИ, выход которого соединен с. вторым входом первого элемента И, единичный, выход первого триггера подключен к первому входу четвертого элемента И и второму входу второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ и входом формирователя импульсов, выход которого подклйчен к одному из входов входного регистра, другие входы которого соединены с шинами ввода информации, выход схемы сравнения подключен к второму входу четвертого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, другой выход дешифратора адреса подключен к счетному входу второго триггера, нулевой и единичный выходы которого соединены соответственно с третьим входом первого и вторым входом пятого элементов И, выход пятого элемента И подключен к второму входу первого элемента ИЛИ, дополнительный элемент ИЛИ, первый вход которого подключен к выходу третьего элемента И, а выход дополнительного элемента ИЛИ является четвертым выходом устройства и первый дополнительный элемент И, первый вход которого подключен к первому входу первого элемента И, второй вход - к единичному выходу первого триггера, а третий вход первого дополнительного элемента И подключен к выходу CXJBMH сравнения и счетчик импульсов, первый вход которого подключен к выхоЛУ первого дополнительного элемента И и к второму входу дополнительного элемента ИЛИ, второй вход .- к выходу формирователя импульсов j а. выход счетчика импульсов подключен к четвертому входу первого дополнительного элемента И fl .

Недостатком этого устройства является то, что запись прекращается при неисправности единичной ячейки памяти в блоке памяти и. нет возможности обойти адрес неисправности ячейки. Это снижает надежностьустройства. При довольно большом объеме блока памяти (4К, 16К )производить его ремонт из-за неисправности одной ячейки неэкономично, выгоднее исключить адрес неисправной ячейки из обращения, задавшись определенным объемом допустимого количества неисправных ячеек блоке памяти.

Целью изобретения является повы шение надежности устройства за счет исключения из обращения адреса неисправной ячейки в блоке памяти . при одновременном исключении -воз- можности выхода ложной информации с устройства.

Поставленная цель достигается тем , что в устройство для контроля блока памяти введены ключи,дополнительный счетчик импульсов и дополнительные второй, третий и четвертый элементы И и накопитель одни из входов которого подключены соответственно к выходам регистра адреса и дешифратора адреса, другие входы являются информационными, а выходы соединены с входами второго дополнительного элемента И, выход которого подключен к одним из входов ключей и третьего дополнительного элемента И, другой вход которого является одним из управляющи входов устройства, а выход соединен с одним из входов первого элемента ИЛИ и третьим входом счетчика импульсов , выход которого подключен к входу дополнительного счетчика импульсов, выход которого является одним из выходов устройства, и к одному из выходов четвертого дополнительного элемента И, другой вход которого является другим управляющим входом устройства, а выход соединен с управляющим входом накопителя, другие входы ключей соединены с первыми входами устройства, а выходы являются другими входами устройства.;

9

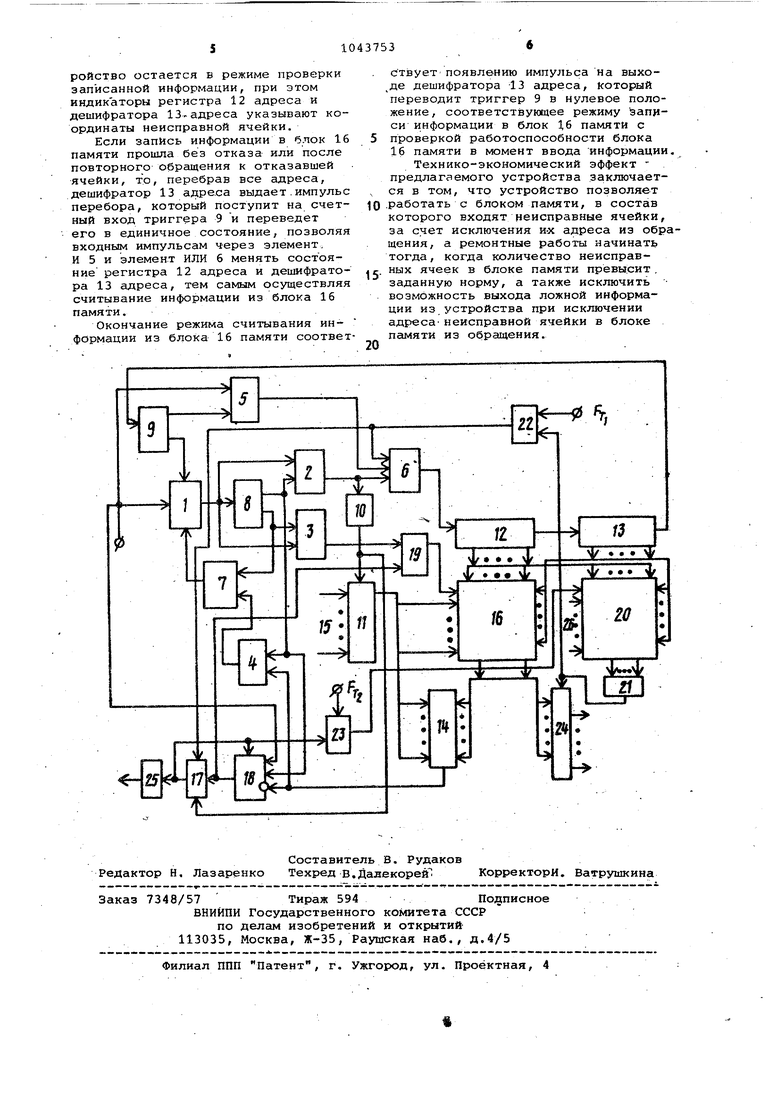

На чертеже представлена структурная схема устройства для контроля блока памяти.

Устройство содержит элементы И 1-5 с первого по пятый, первый б и второй 7 элемента ИЛИ, первый 8 и второй 9 триггеры, формирователь 10 импульсов, входной регистр 11, регистр 12 адреса, дешифратор 13 адреса, схему 14 сравнения, шины 15 ввода информации. Входы и выходы устройства соединяются с выходами и входами контролируемого блока 16 памяти.. Устройство также .. . содержит счетчик ,17 импульсов/ первый дополнительный .элемент И 1-8 первый дополнительный, элемент ИЛИ . 19, накопитель 20, первый 21, вто- рой 22 и третий 23 дополнительные элементы И, ключи, объединенные, в ;. блок 24, и дополнительный счетчик 25 импульсо.

Устройство работает следующим образом.,;

В исходном состоянии триггеры 8 и 9 установлены: в нулевое состояние. Регистр адреса 12 и-дешифра - . тор 13 адреса устанавливают адресисходных ячеек блока 16 памяти. Во входной регистр 11 введена исходная информация для записи в блоке 16 памяти. На вход устройства . поступает первый импульс, который проходит через элемент И,1 на счетный вход триггера 8 и через, элементы И 3 и ИЛИ 19 на управляющий вход записи информации блока 16памяти; записывая в него информацию с выходов входного регистра 11. Задний фронт первого, входного им- : пульса переврдит триггер 8 в единичное состояние. Отсутствие сиг- нала на управляющем входе записи информации блока 16 памяти при наличин выбранных адресов с регистра 12 адреса и дешифрато а 13 адреса соответствует режиму выдачи информации для блока 16 памяти. Информация с блока 16 памяти поступает на вход схемы 14 сравнения, где сравнивается с информацией на входном регистре 11 и, в случае их совпадения, -с выхода схемы 14 сравнения.Через элемент И -4 и элемент ИЛИ 7 : поступает потенциал разрешения на элемент И 1 для прохождения.второго входного импульса. Этот импульс поступает на счетный вход триггера 8 через элемент И 2 на вход формиро-. вателя 10 импульсов и через элемент ИЛИ 6 на вход регистра 12 адреса . Задний фронт этого импульса изменяет адрес в регистре 12 ешре- са и переводит триггер 8 в нулевое состояние. Теперь во входной регистр 11 вводится новая информация для записи в блок .16 памяти. Далее работа, устройства проходит по алгоритму, описанному выше. .

В случае разового отказа ячейки в блоке 16 памяти информация на.входах схемы 14 сравнения не будет совпадать, и на ее выходе будет Отсутствовать разрешающий потенциал, в следствие чего очередной вход ной импульс не пройдет на вход трипсра 8. Отсутствие сигнала на выходе схемы 14 сравнения позволяет входным импульсам пройти через элементы И 18 и ИЛИ 19 на управляющий вход записи информации в блок 16 памяти, .позволяя повторить запись информации с входного регистра 11 в. блок 16 памяти..

Такое повторение обращения к отказавшей, ячейке позволяет устра- . нить сбой блока 16 памяти,.который наступил вследствие влияния помехи : в момецт подачи команды Запись, количество импульсов повторного об ращения к от казавшей ячейки бло, ка 16 памяти фиксируется счетчиком 17 импульсов. Переполнение счетчика 17 свидетельствует об неирправ- ности ячейки по данному адресу блока 16. памяти.. Количество переполнений счетчика 17 накапливается счетчиком 25. Сигнал переполнения счетчика 17 является запрещающим для элемента И 18 и разрешает, про.хождение чмпульсов с тактовой -частотой ,Ру2черёз элемент И 23 на управляющий вход записи, информации накопителя 2.0, по входам 26 которот-о в него Записываются единичные потенциалы. Таким образом, по адресу .неиспраВНой ячейки блока 16 памяти в накопитель .20 были записаны единичные потенциалы. Исчезновение импульса по., входу управления накопителя 20 переводит его в режим выдачи информации Единичные noTJe.Hциалынакопителя 20, пройдя элемент И 21, закрывают ключи 24 на время, смены адреса в блоке 16 памяти импульсами с тактовой: частотой -F через элемент И 22 и элемент ИЛИ 6с помощью регистра 12 адреса . Это исключает появлен.ие ложной информации на выходе. Одновременно импульс с выхода элемента И. 22 сбрасывает счетчик 17..в исходное положение.. Запись информации продолжается в блок 16 по новому адресу, а во время считывания информации из блока 16 памяти таким же образом буде.т, исключаться адрес неисправной ячейки.

Объем с«1етчика 25 определяет допустимое количество неисправных ячеек в блоке 16 памяти. Переполнение счетчика 25 свидетельствует о том, что отведенный объём исключенных адресов неисправных ячеек исчерпан и блок 16 .следует ремонтировать.

. Ремонт блока 16 памяти ведется при огклю 1енной шине тактовых импульсой с частотой РТ-Ч, тогда по заполнению счетчика 17 импульсов снимается разрешение с соответстsytocqero входа элемента И 18, и устройство остается в режиме проверки записанной информации, при этом индикаторы регистра 12 адреса и дешифратора 13-адреса указывают координаты неисправной ячейки.

Если запись информации в блок 16 памяти прошла без отказа или после повторного обращения к отказавшей ячейки, то, перебрав все адреса, дешифратор 13 адреса выдает.импульс перебора, который поступит на счетный вход триггера 9 и переведет его в единичное состояние, позволяя входным импульсам через элемент, И 5 и элемент ИЛИ 6 менять состояние регистра 12 адреса и дешифратора 13 адреса, тем самым осуществляя считывание информации из блока 16 памяти.

Окончание режима считывания информации из блока 16 памяти соответствует появлению импульса на выхо де дешифратора 13 адреса, koтopый переводит триггер 9 в нулевое положение, соответствующее режиму записи информации в блок 1,6 памяти с проверкой работоспособности блока 16 памяти в момент ввода информации.

Технико-экономический эффект предлагаемого устройства заключается в том, что устройство позволяет .работать с блоком памяти, в состав которого входят неисправные ячейки, за счет исключения и-х адреса из обращения, а ремонтные работы начинать тогда, когда количество неисправных ячеек в блоке памяти превысит заданную норму, а также исключить возможность выхода ложной информации из устройства при исключении адресанеисправной ячейки в блоке памяти из обращения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блока памяти | 1983 |

|

SU1137539A2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1108511A1 |

| Устройство для контроля блока памяти | 1980 |

|

SU963107A2 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1262575A1 |

| Устройство для контроля блокапАМяТи | 1979 |

|

SU801106A1 |

| Устройство для контроля блока памяти | 1981 |

|

SU1040525A2 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКА ПАМЯТИ по авт.св. 963107, о т-л и. .ча го щ е е с я тем, что, , с целью повышения надежности устройства, в него введены ключи, дополнительный счетчик HMnyjjbcoB (И. дополнительные второй, третий и четвертый элементы И и накопитель, одни из входов которого подключены соответственно к выходс1М регистра адреса и дешифратора адреса, другие входы являются информационными-, а выходы соединены с входами второго дополнительного элемента И, выход которого-подключен к одним из входов ключей и третьего дополнительного элемента И, другой вход кот-орого является одним из управлякядих входов устройства,а вы ход соединен с одним из входов первого элемента ИЛИ и третьим входом счетчика импульсов, выход крторого подключен к входу дополнительного счетчика импульсов, выход которого является одним из выходов устройства, и к одному из входов четвертого дополнительного элемента И, другой вход которого является другим управляющим входом устройства, i а выход соединен с управляющим входом накопителя, другие, входы клю(Л чей соединены с первыми входами устройства, а выходы являются другими входами устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля блока памяти | 1980 |

|

SU963107A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-09-23—Публикация

1981-06-04—Подача