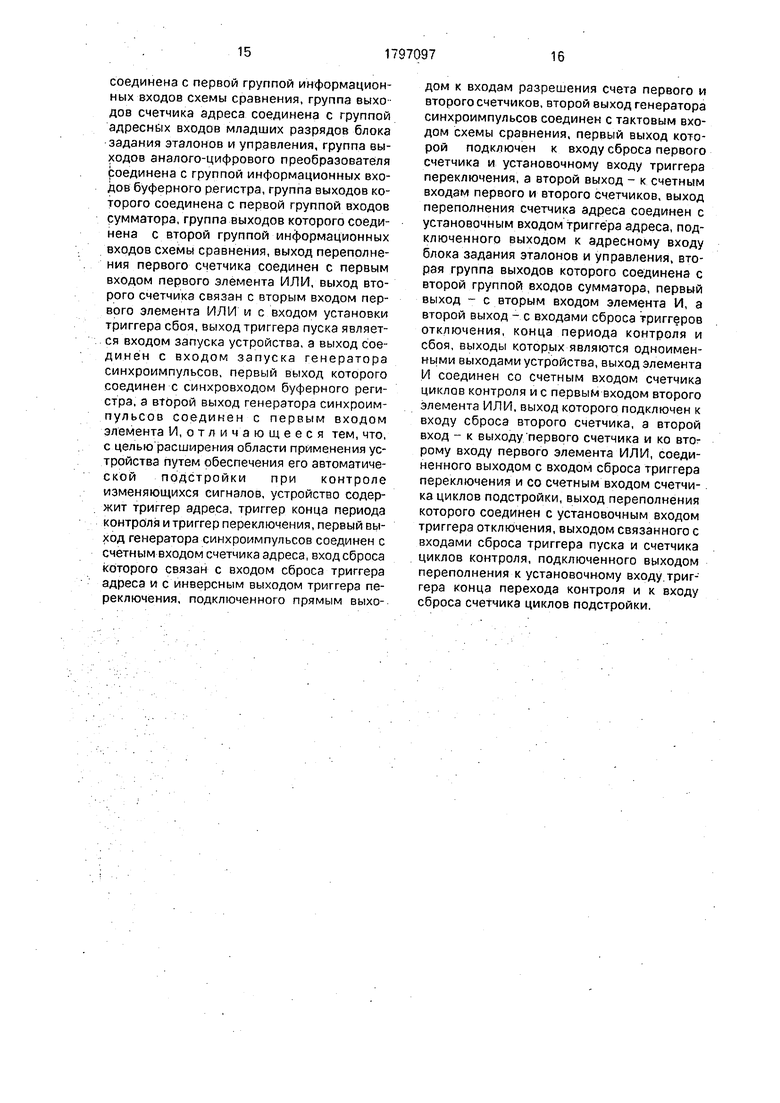

.Изобретение относится к автоматике и вычислительной технике и может быть использовано для идентификации аналоговых сигналов, поступающих на вход устройства от различных объектов, а также в средствах контроля диагностирования и отладки сис- .тем..

Известно устройство для контроля последовательности импульсов, содержащее одновибратор, селектор, счетчики, элементы НЕ, элементы И.

Известно также устройство, содержа- . щее счетчики, постоянное запоминающее устройство, блок сумматоров по модулю два, регистры, триггеры, генератор синхроимпульсов, элементы И, одновибраторы.

Недостатком этих устройств является невозможность контроля пачек импульсов с

произвольным количеством импульсов в пачке и отсутствие возможности контроля одной из нескольких возможных последовательностей импульсов, т.е. узкая область применения.

. . Наиболее близким к предлагаемому является устройство для контроля аналоговых сигналов, содержащее постоянное запоминающее устройство, оперативное запоминающее устройство, семь счетчиков, сумматор, аналого-цифровой преобразователь, регистр, сравнивающее устройство, три триггера, генератор синхроимпульсов, группу ЗИ-ИЛИ, два элемента И, два элемента ИЛИ, причем группа выходов первого счетчика соединена с группой входов постоянного запоминающего устройства, первый выход которого соединен с разрешающим

VJ

Ю Ч О

ю

XI

входом первого счетчика, вторая группа выходов постоянного запоминающего устройства соединена с группой информационных входов третьего счетчика и группой информационных входов пятого счетчика, третья группа выходов постоянного запоминающего устройства соединена с группой информационных входов четвертого счетчика и группой информационных входов пятого счетчика, четвертый выход постоянного запоминающего устройства соединен с первым разрешающим входом пятого счетчика, пятый выход постоянного запоминающего устройства соединен с вторым разрешающим входом пятого счетчика, инверсным разрешающим входом третьего счетчика, инверсным рарешающим входом четвертого счетчика и первым входом первого элемента И группы ЗИ-ИЛИ, шестая группа выходов постоянного запоминающего уст- ройства соединена с первой группой входов сравнивающего устройства, выход третьего счетчика соединен с первым входом второго элемента И группы ЗИ-ИЛИ, выход четвертого счетчика соединен со счетным входом пятого счетчика, группа выходов которого соединена с группой первых входов сумматора, первый выход постоянного запоминающего устройства также соединен с вторым инверсным входом первого элемента И группы ЗИ-ИЛИ, вторым инверсным входом второго элемента И группы.ЗИ-ИЛИ, первым входом третьего элемента И группы ЗИ-ИЛИ, группа выходов аналого-цифрово- го преобразователя соединена с группой информационных входов регистра, группа выходов которого соединена с второй группой входов сравнивающего устройства и первой группой информационных входов оперативного запоминающего устройства, второй выход сравнивающего устройства соединен с вторым информационным входом оперативного запоминающего устройства, группа выходов первого счетчика также соединена с третьей группой информационных входов оперативного запоминающего устройства, разрешающий инверсный вход подключен к корпусу, группа выходов второго счетчика подключена к группе адресных входов оперативного запоминающего устройства, выход шестого сигнала соединен с входом первого триггера, выход седьмого счетчика соединен с входом второго триггера, выход триггера пуска соединен с входом генератора синхроимпульсов, первый выход которого соединен с третьим входом первого элемента И группы ЗИ-ИЛИ, вторым входом третьего элемента И группы ЗИ-ИЛИ и синхровходом третьего счетчика, второй выход генератора синхроимпульсов соединен с синхровходами регистра четвертого и пятого счетчиков, третий выход генератора синхроимпульсов соединен с первым входом первого элемента И,

первый выход сравнивающего устройства соединен с первым входом второго элемента И, второй выход сравнивающего устройства соединен с вторым входом первого элемента И, выход которого соединен со

счетными входами шестого и седьмого счетчиков, управляющим входом оперативного запоминающего устройства и первым входом первого элемента ИЛИ, выход которого соединен со счетным входом второго счет5 чика, третий выход генератора синхроимпульсов также соединен с вторым входом второго элемента И, выход которого соединен с входом установки в ноль шестого счет- чика, выход шестого счетчика также

0 соединен с первым входом второго элемента ИЛИ, выход седьмого счетчика также соединен с вторым входом второго элемента ИЛИ, выход которого соединен с входом установки в ноль триггера пуска, выход

5 группы ЗИ-ИЛИ соединен с синхровходом первого счетчика, группа информационных входов первого счетчика является входом устройства, группа входов анзлого-цифро- вого преобразователя является входом уст0 ройства, группа информационных входов и синхровход второго счетчика является входом устройства, второй вход первого элемента ИЛИ является входом устройства, вход триггера пуска является входом уст5 ройства, третий вход второго элемента ИЛИ является входом устройства, группа входов оперативного запоминающего устройства является входом устройства, выход первого триггера является входом устройства, выход

0 второго триггера является выходом устройства.

Недостатком этого устройства является невозможность подключения к входу, на который поступают контролируемые сигналы,

5 в любой момент времени, а также невозможность автоматической подстройки и организации контроля. Указанная причина значительно сужает область применения устройства. Если на его основе попытаться

0 реализовать автоматическую подстройку, то потребуется для этого ввести в память все возможные варианты значений аналогового сигнала и сравнивать их с теми значениями, которые приходят на вход устройства.

5 Это потребует значительного увеличения объема памяти устройства.

Целью изобретения является расширение области применения устройства путем обеспечения его автоматической подстройки при контроле изменяющихся сигналов.

Поставленная цель достигается тем, что в устройство для контроля аналогового сигнала, содержащее блок задания эталонов и управления, сумматор, счетчик адреса, первый и второй счетчики, счетчик циклов контроля, счетчик циклов подстройки, схему сравнения, буферный регистр, аналого- цифровой преобразователь, триггер пуска, генератор синхроимпульсов, триггер сбоя, триггер отключения, первый и второй элементы ИЛИ, элемент И, причем первая группа выходов блока задания эталонов и управления соединена с первой группой информационных входов схемы сравнения, группа выходов счетчика адреса соединена с группой адресных входов младших разрядов блока задания эталонов и управления, группа выходов аналого-цифрового преобразователя соединена с группой информационных входов буферного регистра, группа выходов которого соединена с первой группой входов сумматора, группа выходов которого соединена с второй группой информационных входов схемы сравнения, выход переполнения первого счетчика соединен с первым входом первого элемента ИЛИ, выход второго счетчика связан с вторым входом первого элемента ИЛИ и вхо- .дом установки триггера сбоя, вход триггера пуска является входом запуска устройства, а выход соединен с входом запуска генератора синхроимпульсов, первый выход которого соединен с синхровходом буферного регистра, а второй выход генератора синхоимпульсов соединен с первым входом элемента И, введены триггер адреса, триггер конца периода и триггер переключения, первый выход генератора синхроимпульсов соединен со счетным входом счетчика адреса, вход сброса которого связан с входом сброса триггера адреса и инверсным выходом триггера переключения, подключенного прямым выходом к входам разрешения счета первого и второго счетчиков, второй выход генератора синхроимпульсов соединен с тактовым входом схемы сравнения, первый выход которого подключен к входу сброса первого счетчика и установочному входу триггера переключения, а второй выход - к счетным входам первого и второго счетчиков, выход переполнения счетчика адреса соединен с установочным входом триггера адреса, подключенного выходом к адресному входу блока задания эталонов и управления, вторая группа выходов которого соединена с второй группой входов сумматора, первый выход - с вторым входом элемента И, а второй выход - с входами сброса триггеров отключения конца периода контроля и сбоя,

выходы которых являются одноименными выходами устройства, выход элемента И соединен со счетным входом счетчика циклов контроля и первым входом второго элемен- 5 та ИЛИ, выход которого подключен к входу сброса второго счетчика, а второй вход - к выходу первого счетчика и второму входу первого элемента ИЛИ, соединенного выходом с входом сброса триггера переключе- 0 ния и счетным входом счетчика циклов подстройки, выход переключения которого, соединен с установочным входом триггера отключения, выходом связанного с входами сброса триггера пуска и счетчика циклов 5 контроля, подключенного .выходом переполнения к установочному входу триггера конца периода контроля и входу сброса счетчика циклов подстройки.

Сущность изобретения заключаеся в 0 расширении области применения устройства за счет обеспечения возможности произвольного включения устройства в работу и осуществления автоматической подстройки процесса контроля без значительного уве- 5 личения объема памяти,

Введение триггера адреса необходимо для обеспечения двух режимов работы устройства: подстройки и контроля.

Введение триггера конца периода конт- 0 роля необходимо для выдачи сигнала пользователя устройством об окончании цикла контроля.

Введение триггера переключения необходимо для организации автоматической 5 подстройки к контролируемому сигналу.

При использовании предлагаемого устройтва может быть получен положительный

эффект, состоящий в расширении области

применения и уменьшении объема оборудо0 вания на 70-80%.

На фиг. 1 представлена функциональная схема устройства для контроля аналогового сигнала; на фиг. 2 - временная диаграмма функционирования устройства. 5 на фиг. 3 - модель процесса контроля; на фиг. 4 - алгоритм контроля; на фиг. 5 - прошивка памяти.

Устройство для контроля аналогового сигнала содержит блок задания эталонов и 0 управления 1, сумматор 2, счетчик адреса 3, первый 4 и второй 5 счетчики, счетчик циклов контроля 6, счетчик циклов подстройки 7, схему сравнения 8, буферный регистр 9, аналого-цифровой преобразователь 10, 5 триггер пуска 11, генератор синхроимпульсов 12, триггер 13, триггер сбоя 14, триггер конца периода контроля 15, триггер отключения 16, триггер переключения 17, первый t8 и второй 19 элементы ИЛИ, элемент И 20, входпуска21 устройства, информационный

вход 22 устройства, первыми 23, второй 24 и третий 25 выходы устройства. Группа вторых выходов 12 блока задания эталонов и управления 1 соединена с группой первых входов схемы сравнения 8, группа выходов счетчика адреса 3 соединена с группой входов А2 блока задания эталонов и управления 1, группа выходов эналого-цифрового преобразователя 10 соединена с группой информационных входов буферного регистра 9, группа выходов которого соединена с первой группой входов сумматора 2, группа выходов которого соединена с группой информационных входов схемы сравнения 8, выход переполнения первого счетчика 4 соединен с первым входом первого элемента ИЛИ 18, выход второго счетчика 5 соединен с вторым входом первого элемента ИЛИ 18 и входом установки триггера сбоя 14, вход триггера пуска 11 является входом запуска, а выход соединен с входом генератора синхроимпульсов 12, первый выход 12.1 которого соединен с синхровходом буферного регистра 9, а второй выход генератора синхроимпульсов 12 соединен с первым входом элемента И 20, первый выход генератора импульсов 12 соединен со счетным входом счетчика адреса 3. вход сброса которого связан с входом сброса триггера адреса 13 и с инверсным выходом триггера переключения 17, подключенного прямым выходом к входам разрешения счета первого 4 и второго 5 счетчиков, второй выход генератора синхроимпульсов 12 соединен с тактовым входом сравнения 8, первый выход которой подключен к входу сброса первого счетчика 4 и установочному входу триггера переключения 17, а второй выход - к счетным входам первого 4 и второго 5 счетчиков, выход переполнения счетчика адреса 3 соединен с установочным входом триггера адреса 13, подключенного выходом к адресному входу блока задания эталонов и управления 1 /вторая группа выходов которого соединена с второй группой входов сумматора 2, первый выход - с вторым входом элемента И 20, а второй выход - с входами сброса триггеров отключения 17, конца периода контроля 15 и сбоя 14, выходы которого являются одноименными выходами устройства, выход элемента И 20 соединен со счетным входом счетчика циклов б контроля и с первым входом второго элемента ИЛИ 19, выход которого подключен к входу сброса второго 5 счетчика, а второй вход - к выходу первого счетчика 4 и второму входу первого элемента ИЛИ 18, соединенного выходом с входом сброса триггера переключения 17 и счетным входом счетчика циклов подстройки 7, выход переполнения которого соединен с ycj

тановочным входом триггера отключения 1.6, входом связанного с входами сброса триггера пуска 11 и счетчика циклов контроля б, подключенного выходом переполнения к установочному входу триггера конца периода контроля 15 и входу сброса счетчика циклов подстройки 7.

Назначение основных функциональных элементов устройства для контроля анало0 говых сигналов состоит в следующем.

Блок задания эталонов и управления 1 предназначен для хранения и выдачи значений аналогового сигнала в контрольные моменты времени в двоичном коде, а также для

5 хранения информации о величине допустимого отклонения аналогового сигнала от заданного значения.

Сумматор 2 предназначен для получения разности между сигналом (кодом), пода0 ваемым на вход устройства и хранящимся в памяти блока задания эталонов и управления. Он может быть выполнен на основе обычного двоичного сумматора (микросхема К155ИМ1) (Цифровые устройства систем

5 связи и управления/Под ред. А.Е.Амбросо- ва.-МО СССР. 1985, с. 63-64, пример 1.12), на первый вход которого подается код эталона, а на второй вход- код контролируемого сигнала в дополнительном коде.

0 Преобразование в дополнительный код может быть осуществлено на основе известных микросхем (тот же иточник, с. 46-56).

Счетчик адреса 3 предназначен для адресации блока задания эталонов и управле5 ния. Первый счетчик 4 предназначен для адресации блока задания эталонов и управления 1. Второй счетчик 5 предназначен для подсчета тактов за один цикл контроля, в течение которых входной сигнал отличается

0 от заданного значения. Счетчик циклов контроля 6 предназначен для организации цикла контроля. Счётчик циклов подстройки 7 предназначен для подсчета циклов, в течение которых происходила подстройка уст5 ройства. Схема сравнения 8 предназначена для сравнения отклонения от заданного значения .аналогового сигнала с допустимым отклонением. Буферный регистр 9 предназначен для записи значения величи0 ны аналогового сигнала в двоичном коде в контрольные моменты времени, Аналрго- цифровой преобразователь 10 предназначен для преобразования аналогового- : сигнала в двоичный код. Триггер пуска 11

5 предназначен для пуска постановки устройства. Генератор синхроимпульсов 12 предназначен для синхронизации работы устройства. Триггер адреса 13 предназначен для перевода устройства из режима подстройки в режим контроля. Триггер сбоя 14

предназначен для записи и выдачи на выход сигнала о превышении длительности сбоя в периоде. Триггер конца периода контроля 15 предназначен для выдачи информации на выход устройства об окончании цикла контроля. Триггер отключения 16 предназначен для отключения устройства при превышении циклов подстройки и выдачи информации на выход устройства. Триггер переключения 17 предназначен для уста- новки устройства в исходное состояние, для организации автоматической подстройки, а также для управления работой счетчиков 4 и 5. Первый 18 и второй 19 элементы ИЛИ и элемент И 20 предназначен для управления работой устройства.

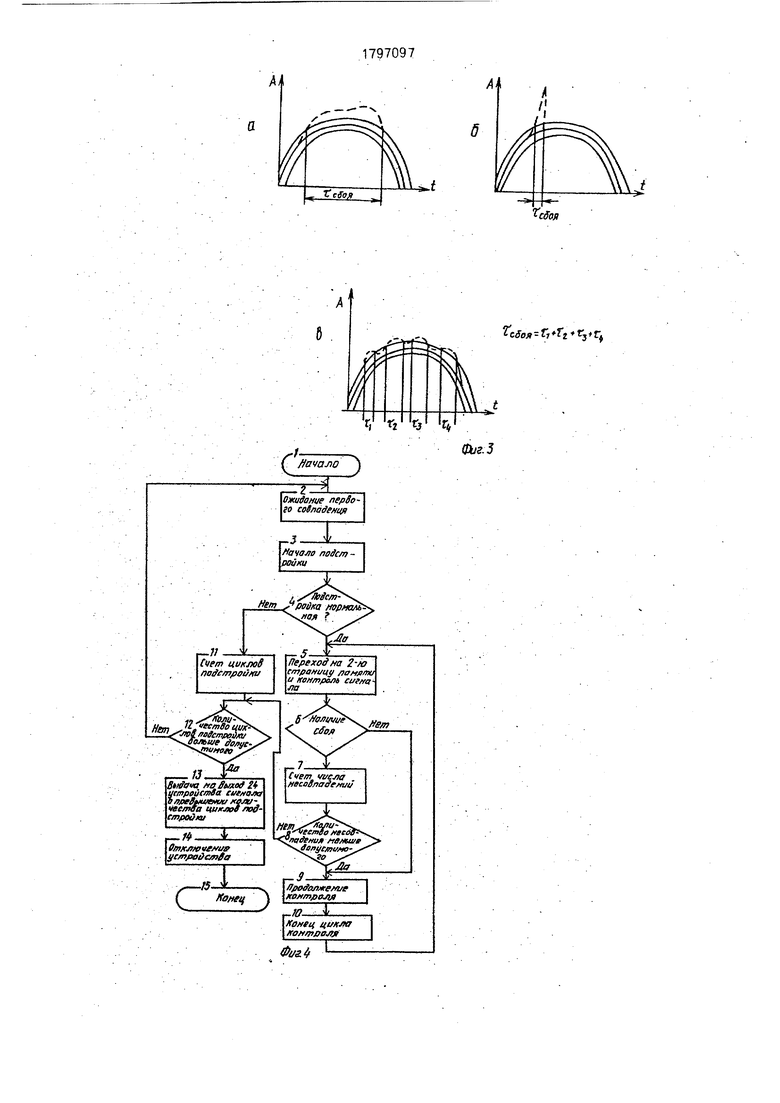

Модель процесса контроля показана на фиг 3. Устройство может реаги-ровать на различные виды отклонений сигнала от нормы. В случае а до начала отрезка времени т сбоя проходил нормальный контроль аналогового сигнала. Сигнал находился в допустимых пределах. Начиная с момента времени to, сигнал вышел за допустимые пределы. Устройство организует отсчет вре- мени относительно, в течение которого сигнал отличается от заданного. Если время т сбоя превысит допустимое время, то происходит установка устройства в исходное состояние, и цикл подстройки и контроля повторяется заново. В том случае, если количество циклов подстройки превышает допустимое число, то произойдет останов устройства и на выход будет выдан сигнал ненорма.

В случае б в моменты времени ti, t2, t3 произошли сбои. Сигнал вышел за границы допуска. Устройство подсчитывает суммарную длительность сбоев за период, и, если она превышает допустимую для таких видов сбоев, то происходит установка в исходное состояние, и циклы подстройки и контроля повторяются. Если количество циклов превысит допустимое значение, то на выходе устройства формируется сигнал ненорма и происходит отключение устройства.

В случае в происходит сбой, длительность которого меньше допустимого, однако превышает допуск по амплитуде. Его значение хранится в устройстве в течение одного цикла, а затем стирается.

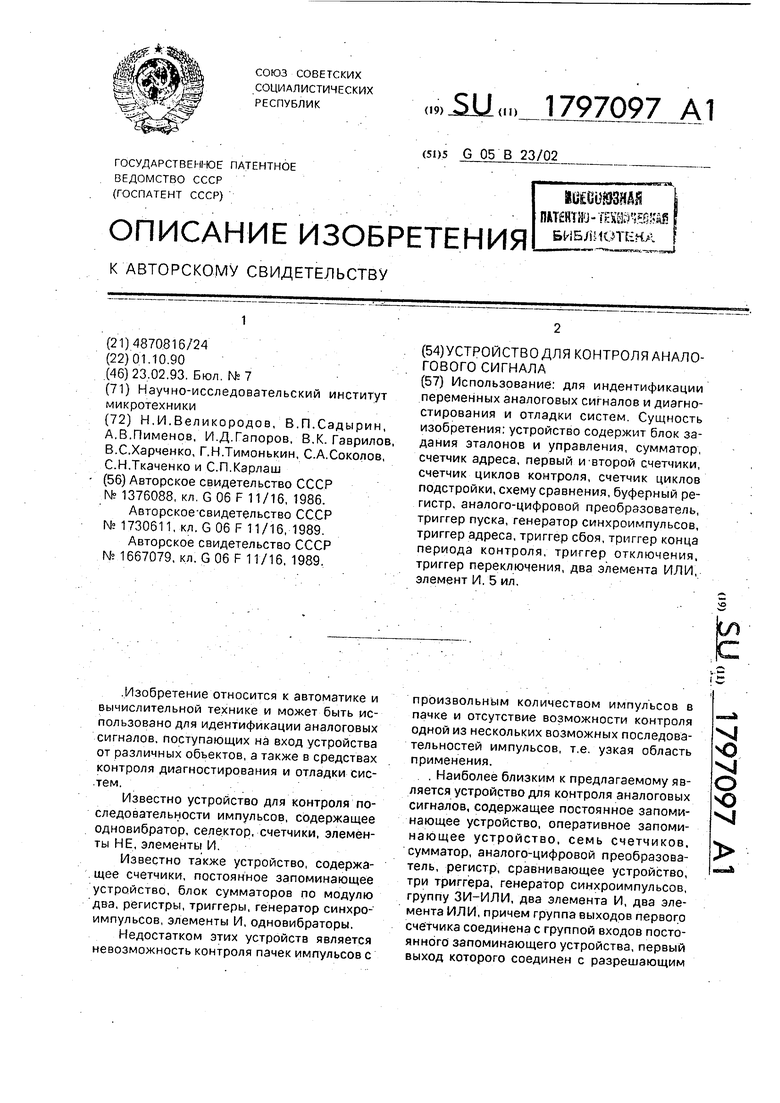

Принцип действия устройства для контроля аналогового сигнала заключается в следующем. Алгоритм контроля показан на фиг. 4.

В начальный момент времени счетчики адреса 3, первый 4, второй 5, циклов контроля 6. циклов подстройки 7, триггеры пуска 11. адреса 13. сбоя 14, конца периода контроля 15, отключения 16, переключения 17, буферный регистр 9 находятся в нулевом состоянии. Цепи установки исходного состояния условно не показаны.

По пусковому импульсу, подаваемому на вход 21, триггер пуска 11 переходит в единичное состояние. По единичному сигналу с выхода триггера пуска 11 запускается генератор синхроимпульсов 12.

По единичному сигналу с инверсного выхода триггера переключения 17 запрещается счет импульсов в счетчике адреса 3 и удерживается в нулевом состоянии триггер адреса 13. Нулевым сигналом с прямого выхода триггера переключения 17 запрещается счет импульсов в первом 4 и ватором 5 счетчиках.

Так как счетчик адреса 3 находится в нулевом состоянии, то на выходах 1.1 блока задания эталонов и управления 1 .присутствует значение сигнала в первой контрольной точке аналогового сигнала, на выходах 1.2-значение допустимого отклонения аналогового сигнала от заданного значения, а на выходе 1.4 в первой микрокоманде присутствует сигнал единичного уровня, который подается на входы установки в ноль триггеров сбоя 14, конца периода контроля 15, отключения 16.

На вход аналого-цифрового преобразователя (АЦП) 10 подается аналоговый сигнал, который преобразуется в двоичный код и с выхода АЦП 10 подается на группу информационных входов буферного регистра 9. По каждому синхроимпульсу с выхода 12.1 генератора синхроимпульсов 12, подаваемому на вход синхронизации буферного регистра 9, в буферный регистр 9 в параллельном коде записывается информация о значении аналогового сигнала в контрольных точках. Информация о заданном значении аналогового сигнала в перв.ой контрольной точке подается с группы выходов блока задания эталонов и управления 1 на первую группу входов сумматора 2. На вторую группу входов сумматора 2 подается информация с группы выходов буферного регистра 9. Так как сумматор 2 вычитающий, то на выходе сумматора выдается разность между значениями аналогового сигнала и его заданным значением,

С выхода 12,2 генератора синхроимпульсов 12 импульсы подаются на первый вход элемента И 20 и на разрешающий вход схемы сравнения 8. В схеме сравнения 9 происходит сравнение отклонения аналогового сигнала от заданного, поступающего с группы выходов сумматора 2, и допустимого отклонения, поступающего с группы выходов 1.2 блока задания эталонов и управления 1..

Как только на выходе А схемы сравнения 8 появится единичный сигнал, это свидетельствует о том, что значение аналогового сигнала вошло в допустимую трубку и устройство поймало начало отсчета. По сигналу с выхода А схемы сравнения 8 триггер переключения 17 устанавливается в единичное состояние. По единичному сигналу с прямого выхода триггера переключателя 17, который подается на разрешающие входы первого 4 и второго 5 счетчиков, разрешается счет импульсов в первом 4 и втором 5 счетчиках. Нулевой сигнал с инверсного выхода триггера переключения 17 поступает на вход установки в ноль счетчика адреса 3, разрешая счет импульсов; и на вход установки в ноль триггера адреса 13. Далее работа устройства происходит следующим образом. По следующему импульсу с выхода 12.1 генератора синхроимпульсов 12 в буферный регистр 9 записывается значение аналогового сигнала в следующей точке, а счетчик адреса 3 переадресуется, и на выходах 1.1 блока задания эталонов и управления 1 появляется заданное значение аналогового сигнала во второй контрольной точке, а на выходах 1.2 блока задания эталонов и управления 1 появляется значение допустимого отклонения значения аналогового сигнала от заданного для данной контрольной точки. В сумматоре 2 получают разницу между значением аналогового сигнала и его заданным значением. На входы схемы сравнения 8 подаются значения отклонения аналогового сигнала от нормы и допустимое отклонение сигнала, и происходит их сравнение. Если отклонение не превышает допустимого, то данный цикл повторяется.

В последней микрокоманде на выходе 1.3 блока задания эталонов и управления 1 появляется сигнал единичного уровня. По синхроимпульсу с выхода 12.2 с генератора синхроимпульсов 12 сигнал с выхода 1.3 блока задания эталонов и управления 1 подается на счетный вход счетчика числа циклов контроля 6 через элемент И 20 и переадресует его. По прошествии заданного числа циклов контроля, определяемого разрядностью счетчика циклов контроля б, на выходе переполнения счетчика появляется единичный сигнал, который подается на вход триггера конца периода контроля 15 и. устанавливает его в единичное состояние. На выходе 24 устройства появляется единичный сигнал, что свидетельствует о завершении очередного цикла Если на выходе 23 устройства отсутствует сигнал, то сбоев в

периоде не было. При переполнении счетчика адреса 3 на выходе переполнения появляется единичный сигнал, который устанавливает триггер адреса 13 в единичное состояние. Единичный сигнал с выхода триггера 13 поступает на вход А1 блока задания эталонов и управления 1 и переводит его на подпрограмму контроля (см,прошивку памяти на фиг;5). Обнуление триггеров

сбоя 14, конца периода контроля 15 и отключения 1 б происходит по единичному сигналу с выхода 1,4 блока задания эталонов и управления 1, который присутствует в первой микрокоманде.

В случае, если после разрешения счета в счетчиках адреса 3, первом 4 и втором 5 отклонение сигнала начнет превышать допустимое значение, на выходе А схемы сравнения 8 появится единичный сигнал,

который поступит на счетные входы первого счетчика 4 и второго 5 и переадресует их. Если сбой непрерывен (см. фиг.За), то оба счетчика будут продолжать отсчет тактов, в течение которых будет идти сбой. По превышении допустимого числа тактов на выходе переполнения первого счетчика 4 и второго 5 появятся единичные сигналы. Единичный сигнал с выхода второго счетчика 5 попадает на вход триггера сбоя 14 и устанавливает

его в единичное состояние. Единичный сигнал на выходе первого входа 23 будет сви- детельствовать о том, что в периоде произошел сбой. Единичный сигнал с выхо- да первого счетчика 4, пройдя через элемент

ИЛИ 18, установит в ноль триггер переключения 17 и переадресует счетчик циклов подстройки 7. По единичному сигналу с выхода первого счетчика 4 через второй элемент ИЛИ 19 второй счетчик 5

устанавливается в нулевое положение. По нулевому сигналу с прямого выхода триггера переключения 17 происходит запрещение счета импульсов в первом 4 и втором 5 счетчиках. Единичным сигналом с инверсного выхода триггера переключения 17 счетчик адреса 3 и триггер адреса 13 устанавливаются в нулевое положение. С этого момента времени устройство переходит в следящий режим и снова готово к

осуществлению подстройки.

Если число сбоев не превысило допустимое число тактов, то при появлении единичного сигнала на выходе А схемы сравнения 9 первый счетчик 4 устанавливается в нулевое положение..

Если в течение периода контроля сбои не повторяются, то по окончании периода контроля сигналом с выхода 1.3 блока задания эталонов и управления 1 через элемент

И 20 и второй элемент ИЛИ 19 второй счетчик 5 устанавливается в нулевое положение.

Если в течение периода сбои повторяются (см. фиг, 3 6) и их суммарное число превысило допустимое значение, то нз выходе переполнения второго счетчика 5 появляется единичный сигнал, котрый подается на вход триггера сбоя 14 и устанавливает его в единичное положение, а также через первый элемент ИЛИ 18 поступает на вход установки в ноль триггера переключения 17 и обнуляет его. Устройство переходит в исходное состояние. Единичный сигнал с выхода первого элемента ИЛИ 18 также поступает на счетный вход счетчика циклов подстройки 7 и переадресует его.

Если в течение цикла контроля (величина цикла определяется разрядностью счетчика циклов контроля 6) количество циклов подстройки превысит допустимое значение, то на выходе счетчика циклов подстройки 7 появляется сигнал единичного уровня, который поступает на вход триггера отключения 16 и устанавливает его в единичное состояние. Единичный сигнал с выхода триггера отключения 16 поступает на вход установки в ноль триггера пуска 11 и обнуляет его, т.е. происходит отключение устройства. Также единичный сигнал с выхода триггера отключения 16 поступает на вход установки в ноль счетчика циклов контроля 6 и обнуляет его, поступает на третий информационный выход 25 устройства и сигнализирует пользователю устройством об отключении устройства контроля. Обнуление триггера отключения 16 производится при последующем включении устройства единичным сигналом с выхода 1.4 блока задания эталонов и управления 1.

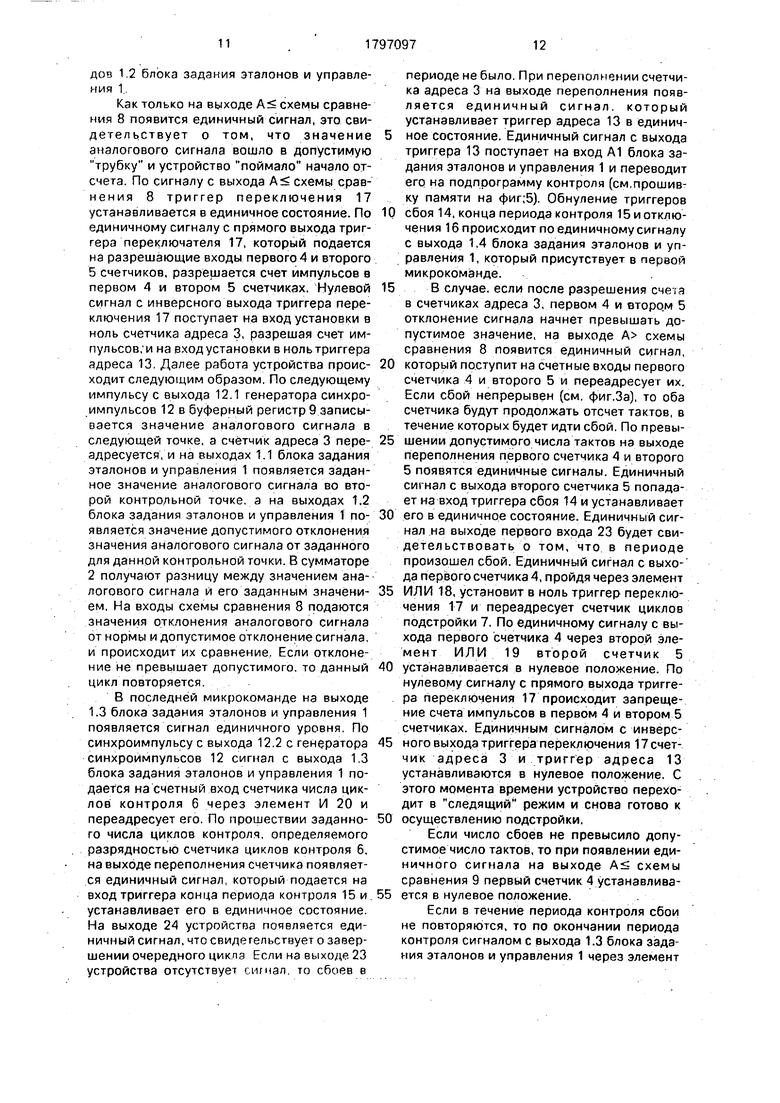

На фиг. 2 показан пример работы устройства.

В первом и втором тактах после запуска устройства идет подстройка, Так как в первом такте разность между программным значением аналогового сигнала и значением аналогового сигнала, который пришел на вход 22 устройства, больше допустимой, то на выходе схемы сравнения 8 А присутствует нулевой сигнал, удерживающий в нулевом состояии триггер переключения 17. который в свою очередь запрещает переадресовку счетчика адреса 3 и запрещает счет первому 4 и второму 5 счетчикам. Во втором 5 такте разность между программным значением и значением аналогового сигнала, пришедшего на вход 22 устройства, становится допустимой, и на выходе 8.А появляется единичный сигнал, который переводит триг0 гер переключения 17 в единичное состояние. Триггер переключения разрешает переадресовку счетчика адреса 3, а также разрешает счет первому 4 и второму 5 счетчикам.

5 При переполнении счетчика адреса 3 (этот отрезок работы на временной диаграмме не показан) единичным сигналом с выхода переполнения триггер адреса 13 переводится в единичное состояние. Единич0 ный сигнал с выхода триггера адреса 13 переводит блок задания эталонов и управления 1 на вторую страницу памяти (см.фиг; 5). Далее идет режим контроля. В тридцать пятом такте происходит сбой. Значениеэна5 лотового сигнала вышло за рамки допустимого (значения на выходах 1.2 блока задания эталонов и управления 1 и выходах сумматора 2). На выходе 8.А схемы сравнения 8 появляется нулевой сигнал, который

0 прекращает обнуление первого счетчика 4. На выходе 8.А появляется единичный сигнал. В последующих тактах сбой не прекращается. Счетчики продолжают считать длительность сбоя. В тридцать восьмом так5 те происходит переполнение счетчиков первого 4 и второго 5. На их выходах появляются единичные сигналы, которые, пройдя через пятый элемент ИЛИ 18, обнуляют триггер переключения 17. Единичный сиг0 нал с инверсного выхода триггера переключения 17 подается на входы установки в ноль счетчика адреса 3 и триггера адреса 13 и обнуляет их. Устройство снова переходит в режим подстройки.

5 Техническое преимущество заявленного устройства состоит в расширении области применения устройства за счет возможности произвольного включения и автоматической подстройки.

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для идентификации аналоговых сигналов | 1991 |

|

SU1789985A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1334139A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536388A1 |

Использование: для индентификации переменных аналоговых сигналов и диагностирования и отладки систем. Сущность изобретения: устройство содержит блок задания эталонов и управления, сумматор, счетчик адреса, первый и второй счетчики, счетчик циклов контроля, счетчик циклов подстройки, схему сравнения, буферный регистр, аналого-цифровой преобразователь, триггер пуска, генератор синхроимпульсов, триггер адреса, триггер сбоя, триггер конца периода контроля, триггер отключения. триггер переключения, два элемента ИЛИ, элемент И. 5 ил.

Формула изобретения Устройство для контроля аналогового сигнала, содержащее блок задания эталонов и управления, сумматор, счетчик адреса, первый и второй счетчик, счетчик циклов контроля, счетчик циклов подстройки, схему

сравнения, буферный регистр, аналого-циф- ровой преобразователь, триггер пуска, генератор синхроимпульсов, триггер сбоя, триггер отключения, первый и второй элементы ИЛИ и элемент И, первая группа выходов блока задания эталонов и управления

соединена с первой группой информационных входов схемы сравнения, группа выхо дов счетчика адреса соединена с группой адресных входов младших разрядов блока задания эталонов и управления, группа выходов аналого-цифрового преобразователя соединена с группой информационных входов буферного регистра, группа выходов которого соединена с первой группой входов сумматора, группа выходов которого соединена с второй группой информационных входов схемы сравнения, выход переполнения первого счетчика соединен с первым входом первого элемента ИЛИ, выход второго счетчика связан с вторым входом первого элемента ИЛИ и с входом установки триггера сбоя, выход триггера пуска является входом запуска устройства, а выход соединён с входом запуска генератора синхроимпульсов, первый выход которого соединен с синхровходом буферного регистра, а второй выход генератора синхроимпульсов соединен с первым входом элемента И, отличающееся тем, что, с целью расширения области применения устройства путем обеспечения его автоматической подстройки при контроле изменяющихся сигналов, устройство содержит триггер адреса, триггер конца периода контроля и триггер переключения, первый выход генератора синхроимпульсов соединен с счетным входом счетчика адреса, вход сброса которого связан с входом сброса триггера адреса и с инверсным выходом триггера переключения, подключенного прямым выходом к входам разрешения счета первого и второго счетчиков, второй выход генератора синхроимпульсов соединен с тактовым входом схемы сравнения, первый выход которой подключен к входу сброса первого счетчика и установочному входу триггера переключения, а второй выход - к счетным входам первого и второго счетчиков, выход переполнения счетчика адреса соединен с установочным входом триггера адреса, подключенного выходом к адресному входу блока задания эталонов и управления, вторая группа выходов которого соединена с второй группой входов сумматора, первый выход - с вторым входом элемента И, а второй выход - с входами сброса триггеров отключения, конца периода контроля и сбоя, выходы которых являются одноименными выходами устройства, выход элемента И соединен со счетным входом счетчика циклов контроля и с первым входом второго элемента ИЛИ, выход которого подключен к входу сброса второго счетчика, а второй вход - к выходу первого счетчика и ко втог рому входу первого элемента ИЛИ, соединенного выходом с входом сброса триггера переключения и со счетным входом счетчика циклов подстройки, выход переполнения которого соединен с установочным входом триггера отключения, выходом связанного с входами сброса триггера пуска и счетчика циклов контроля, подключенного выходом переполнения к установочному входу.триггера конца перехода контроля и к входу сброса счетчика циклов подстройки.

Фиг.1

/- ---- -ч

Г //мало )

С&г.З

Г

страница А

ц страница А

5ЙГЛ-5

| Устройство для контроля двух последовательностей импульсов | 1986 |

|

SU1376088A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для идентификации бинарных сигналов | 1989 |

|

SU1730611A1 |

| «л | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля сигналов | 1989 |

|

SU1667079A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| П.Садырин, В.К | |||

| Гаврилов, С.А.Соколов, | |||

Авторы

Даты

1993-02-23—Публикация

1990-10-01—Подача