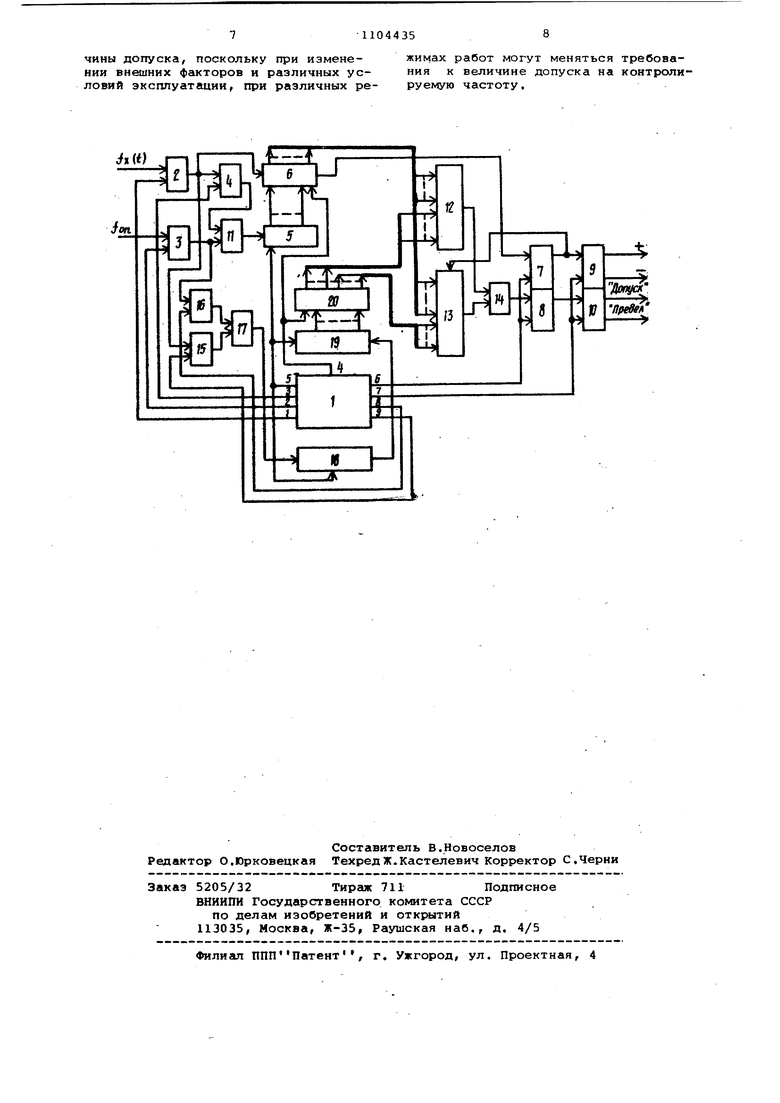

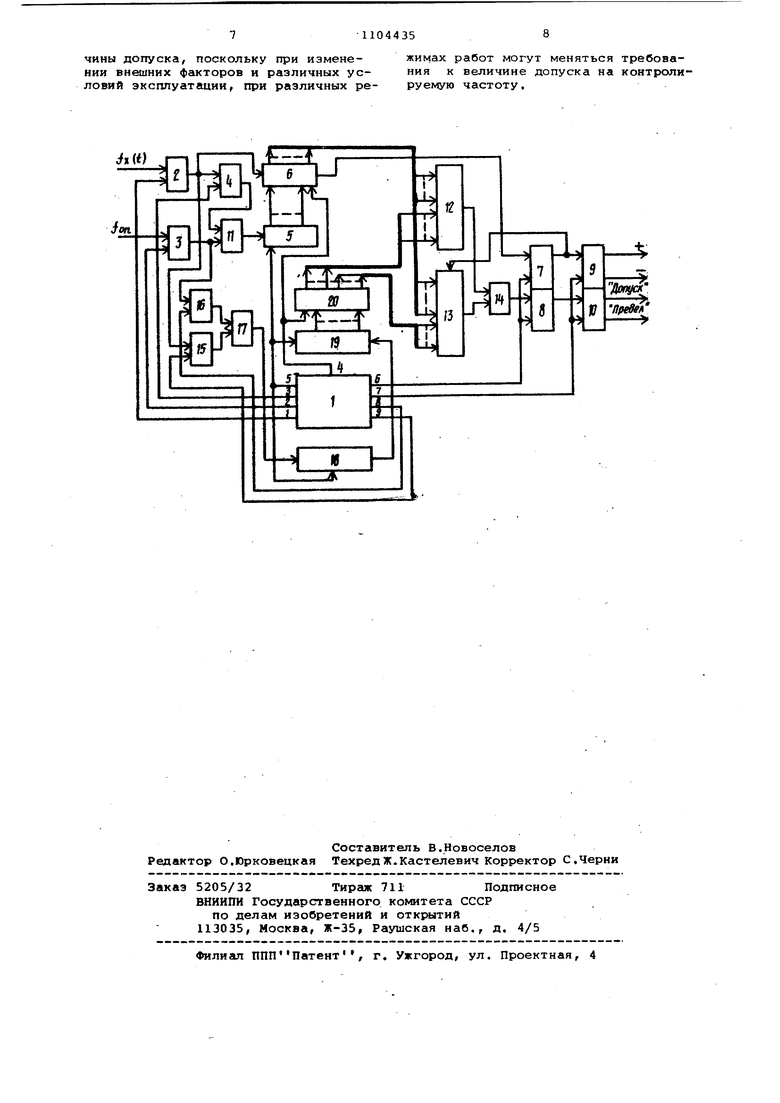

Изобретение относится к измерител ной технике и предназначено для применения в автоматизированных системах Контроля технологических параметров и контрольно-измерительных систем различного назначения, . Известно устройство допускового контроля частоты, содержащее два счетчика импульсов, две линии задерж ки, шесть триггеров предела, элементов У, индикаторов и элемент ИЛИ Однако устройством невозможно про водить допусковый контроль заранее неизвестных значений частоты исследуемого сигнала, кроме того, невозможно автоматическое изменение величины допуска на контролируемую частоту. , Наиболее близким к изобретению по технической сущности является устройство допускового контроля частоты содержащее четыре триггера, три элемента И, два элемента ИЛИ, два счетчика, два дешифратора, входы которых подключены соответственно к выходам первого счетчика, блок управления, первый, второй и третий выходы которого соответственно подключены к первым входам элементов И, выход первого элемента И объединен с вторым входом третьего элемента И и со счетным входом первого счетчика выход третьего элемента И подключен к первому входу первого г.элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, выход пе -вого элемента ИЛИ подключен к счетному входу второго счетчика, выходы разрядов которого подключены соответ ственно к входам разрядов первого счетчика, синхронизирующий вход которого соединен с четвертым выходом блока управления, пятый выход которого подключен к установочному входу второго счетчика, шестой выход второго счетчика, шестой выход блока управления объединен с первыми установочными входами первого и второго триггеров, выходы которых подключены соответственно к информационным входам третьего и четвертого триггеров, синхронизирующие входы которых объединены и подключены к седьмому выход блока управления, второй установочный вход первого триггера соединен c выходом старшего дополнительного раз ряда первого счетчика, счетный вход второго триггера подключен к выходу второго элемента ИЛИ, входы которого соединены с выходами дешифраторов 2J Известное устройство работает априорной известности величины отклонения контролируемой частоты от опорной. В устройстве не предусмотрена воз можность автоматического изменения величины допуска, крокю того, оно не позволяет проводить допусковый контроль частоты исследуемого сигнала, когда она является некоторой функцией времени при постоянной относительной величине допуска. Цель изобретения - расширение функциональных возможностей устройства - обеспечение возможности автоматического изменения величины допуска и обеспечение допускового контроля частоты исследуемого сигнала, когда она является некоторой функцией времени. Поставленная цель достигается тем, что в устройство, содержащее четыре триггера, три элемента И, два элемента ИЛИ, два счетчика, блок управления, первый, второй и третий выходы которого соответственно подключены к первым входам первого, второго и третьего элементов И, выход первого элемента И объединен с вторым входом третьего элемента И и со счетным входом первого счетчика, выход третьего элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, выход первого элемента ИЛИ подключен к счетному входу второго счетчика, выходы разрядов которого подключены соответственно к входам разрядов первого счетчика, синхронизирующий вход которого соединен с четвертым выходом блока управления, пятый выход которого подключен к установочному входу второго счетчика, шестой выход блока управления объединен с первыми установочными входами первого и второго триггеров, выходы которых подключены соответственно к а информационным входам третьего и четвертого триггеров, синхронизирующие входы которых объединены и подключены к седьмому выходу блока управления, второй установочный вход первого триг гера соединен с выходом старшего дополнительного разряда первого счетчика, счетный вход второго триггера подключен к выходу второго элемента ИЛИ, введены четвертый и пятый элементы И, третий элемент ИЛИ, управ- пяемый делитель частоты, третий счетчик, регистр памяти, первый и второй блоки сравнения кодов, выходы которых подключены соответственно к входам второго элемента ИЛИ, первые цходы первого и второго блоков сравнения кодов соединены с выходами первого счетчика, вторые входил первого блока сравнения кодов соединены с выходами дополнительного кода регистра памяти, выходал прямого кода которого подключены соответственно к Ьторым входам второго блока сравне-. ния кодов, вход блокировки которого соединен с выходом первого триггера, входы регистра памяти подключены соответственно к выходам третьего счетчика, счетный вход которого под-ключен к выходу управляемого делителя частоты, установочный вход которого объединен с установочным входом третьего счетчика и с пятым выходом блока управления, синхронизиру щий вход регистра памяти подключен к четвертому выходу блока управления, вход делителя частоты соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с выходом четвертого элемента И, второй вход третьего элемента .ИЛИ соединен с выходом пятого элемента И, первый вход которого соединен с восьмым выходом блока управления, девятый -выхо которого подключен к первому входу четвертого элемента И, второй вход которого соединен с выходом- первого элемента И, а выход второго элемента И соединен с вторым входом пятого элемента И, На чертеже приведена функциональная схема предлагаемого устройства. Устройство содержит блок 1 управления, элементы И 2-4, счетчики 5 и 6, триггеры 7-10, элемент,;ИЛИ 11, блоки 12 и 13 сравнения кодов, элемент ИЛИ 14, элементы И 15 и 16, элемент ИЛИ 17, управляемый делитель 18 частоты, счетчик 19 и регистр 20 памяти. Первый, второй и третий выходы блока 1 управления соответственно по ключены к первым входам элементов И 2-4, выход первого элемента И 2 объе динен с вторым входом третьего элемента И 4 и со;счетным входом первого счетчика 6, выход третьего элемен та И 4 подключен к первому входу пер вого элемента ИЛИ 11, второй вход ко торого соединен с выходом второго элемента И 3. Выход первого элемента ИЛИ 11 подключен к счетному входу второго счетчика 5, выходы разрядов которого подключены соответственно к входам раэрядов первого счетчика 6, синхронизирующий вход которого соединен с четвертым выходом блока управления, пятый выход которого под ключен к установочному входу второго счетчика 5, шестой выход блока упра ления объединен с первыми установоч ными входами первого и второго триг герой 7 и 8, выходл которых подключены соответственно к информационны входам третьего и четвертого тригге ров 9 и 10, синхронизирующие входы которых объединены илежду собой и по ключены к седьмому выходу блока управления. Второй установочный вход первого триггера соединен с выходом старшего дополнительного разряда пе вого счетчика 6, счетный вход второ го триггера 8 подключен к выходу вт рого элемента ИЛИ 14. Выходы блоков 12 и 13 сравнения кодов подключены соответственно к входам второго эле мента ИЛИ 14, первые входы первого и второго блоков сравнения кодов co инены с выходами первого счетчика б, вторые входы первого блока 12 сравнения кодов соединены с выхода:мм дополнительного кода регистра 20 памяти , выходы прямого кода которого подключены соответственно к вторым входам второго блока 13 сравнения кодов, вход блокировки которого соединен с выходом первого триггера 7, входы регистра памяти подключены соответственно к выходам третьего счетчика, счетный вход которого подключен к выходу управляемого делителя 18 частоты, установочный вход которого объединен с -установочным входом третьего счетчика 19 и с пятым выходом блока управления. Синхронизирующий вход регистра 20 памяти подключен к четвертому выходу блока управления, вход делителя 18 частоты соединен с выходом третьего элемента ИЛИ 17, первый вход которого соединен с выходом четвертого элемента И 15, второй вход третьего элемента ИЛИ 17 соединен с выходом пятого элемента И 16, первый вход которого соединен с BOCbNWM выходом блока управления, девятый выход которого подключен к первому входу четвертого элемента И 15, второй вход которого соединен с выходом первого элемента И 2, а выход второго элемента И 3 соединен с вторым входом пятого элемента И 16. При этом первый вход элемента И 2 соединен с входной шиной контролируемой частоты f (t), первый вход элемента И 3 соединен с входной шиной опорной частоты f , первый выход триггера 9 является выходом+ второй выход триггера 9 - выходом -, первый выход триггера 10 является выходом Допуск, а второй Предел. В качестве блока 1 управления может быть использован простой распределитель импульсов совместно с формирователем временных интервалов. Устройство работает в двух режимах: Врежиме контроля отклонения частоты f-,((t) исследуемого сигнала относительно опорной частоты f др и в режиме контроля часуоты отклонения частоты исследуемого сигнала относительно ранее определенного значения, В обоих режимах предусмотрена возможность изменения величины допуска &f. Работа устройства в первом режиме происходит следующим образом.. В момент начала нового измерительного интервала элементы И 2,3 и 16 открывгиотся сигналами с первого, второго и восьмого выходов блока 1 управления на время измерительного интервала TO. На счетный вход счетчика 6 поступает частота ) с выхода элемента И 2, на счетный вход счетчика 5 - частота f „ с выхода элемента И 3 через элемент ИЛИ 11, навход делителя 18 поступает частота fp с в хода элемента И 16 через дополнител ный элемент ИЛИ 17, а на счетный вход счетчика 19 - частота f /К с выхода делителя 18 с коэффициентом ления К., Счетчик 6 суммирует поступающие импульсы. В момент перехода сигналом f(t) нижнего допуска срабатывает блок 12 сравнения, с выхода которого сигнал через элемент ИЛИ 14 поступает на счетный вход триггера 8 и устанавливает его в . Данное состояни триггеров 7 и 8 соответствует тому, что контролируемый сигнал f (t) на хадится в пределах допуска и частот f (t) меньше f , , т.е. f „ f ,(t) f on - Л. в случае отсутствия сигнала на выходе блока 12 сравнения кодов три гер 8 своего состояния не меняет, и ходное состояние триггеров 7 и 8 со ответствует выходу контролируемого сигнала за пределы нижней границы допуска. Если частота контролируемого сиг нала выше опорной, устаройство ра ботает следующим образом. В момент равенства кода счетчика 6 нулю на выходе его старшего допол нительного разряда формируется сигнал, который поступает на установоч ный вход триггера 7 и устанавливает его в , сигнал с выхода тригге ра 7 деблокирует блок 13 сравнения кодов, при этом триггер 8 находится в состоянии , состояние триггеров 7 и 8 соответствует тому, что f(t) находится в допуске и f( больше f on / т.е. Мэмент выхода частоты f(t) за пределы верхнего допуска выделяется блоком 13 сравнения кодов, на первые входы которого поступает прямой код с выходов счетчика 6, а на вторые входы - прямой код величины допуска й с выходов прямого кода регистра 20 памяти. Сигнаш с выхода блока 13 сравнения кодов через элемент ИЛИ 14 поступает на счетный вход триггера 8 и устанавливает его О, при этом триггер 7 находится в . Данное состояние триггеров 7 и 8 соответствует тому, что контролируемая частота выше опорной и выше верхней границы допуска, т.е f,(t) f „„ +tuf. к концу измерительного интервгша в счетчике 6 формируется код рассогласования контролируемой fj(t) и ono ной fgp частот, причем, если f(,p f(t) f on fi TO на выходах счет-i чика б формируется дополнительный код рассогласования, если f + df f(t) f on , то формируется прямой код рассогласования. Информация о рассогласовании по сигналу с седьмого выхода блока 1 управления в момент окончания измерителвного интервала переписывается из триггеров 7 и 8 в триггеры 9 и 10 соответственно . Цикл работы устройства заканчиваетЬя, причем по сигналу с г1ятого выхо да блока 1 управления содержимое счетчика 5 переписывается в счетчик 6 в в дополнительном коде, а содержимое счетчика 19 в прямом и дополинетльном кодах переписывается в регистр 20 памяти. Сигналом с шестого выхода блока 1 управления обнуляются триггеры 7 и 8, а счетчики 5 и 19 и делитель 18 обнуляются сигналом с пятого выхода блока управления, элементы И 2 и 3 закрываются. Устройство готовок новому циклу контроля. Подавая различный код из блока 1 управления на управляющие входы делителя 18 частоты, можно менять коэффициент к деления частоты, при этом изменяется количество импульсов, подсчитывае1иых сметчиком 19 эа измерительный интервал Тд, т.е. изменяется величина допуска Л. Таким образом, изменяя коэффициент деления делителя частоты, можно устанавливать необходимую величину допуска. Режим контроля частоты исследуемого сигнала по предыдущему отсчету обеспечивается при закрытии элемента И 3 с второго выхода блока 1 управления и открывании элемента И 4 на время измерительного интервала Т сигналом с третьего выхода блока 1 .управления. В этом режиме устройство работает аналогично режиму контроля исследуемого сигнала относительно опорной частоты. Роль опорной частоты в этом случае играет частота ,-) в измерительном интервале относительно частоты ,- + ) в Тр измерительном интервале. Поскольку при изменении частоты f(t) изменяется величина допуска д, и коэффициент деления К делителя 18 частоты постоянен, то относительная величина допуска остается постоянной на всем диапазоне контролируемых частот , Предлагаемое устройство позволяет осуществить допусковый контроль частоты и измерения отклонения частоты от границ допуска при изменении величины допуска, поскольку при изменении внешних факторов и различных условий эксплуатации, при различных режимах работ могут меняться требования к величине допуска на контролируемую частоту.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ЧАСТОТЫ | 1991 |

|

RU2008759C1 |

| Устройство допускового контролячАСТОТы | 1979 |

|

SU840755A1 |

| Анализатор колебаний напряжения | 1981 |

|

SU1013863A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1001098A1 |

| Устройство допускового контроля частоты | 1987 |

|

SU1458835A1 |

| Устройство для контроля линейных динамических объектов | 1990 |

|

SU1795422A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Генератор случайного импульсного процесса | 1982 |

|

SU1094032A1 |

| Система управления технологическими процессами | 1982 |

|

SU1104561A2 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

УСТРОЙСТВО ДЛЯ ДОПУСКОВОГО КОНТРОЛЯ ЧАСТОТЫ, содержащее четыре триггера, три элемента И, два элемента ИЛИ, два счетчика, блок управления, первый, второй, третий выходы которого соответственно подключены к первым входам первого, второго и третьего элементов И, выход первого элемента И объединен с вторым входом третьего элемента И и со счетным входом первого счетчика, выход третьего элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, выход первого элемента ИЛИ подключен к счетному входу второго счетчика, выходца разрядов первого счетчика, синхрониэирующий вход которого соединен с четвертым выходом блока управления, пятый выход которого подключен к установочному входу второго счетчика, шестой выход блока управления объединен с первыми установочными входами первого и второго триггеров, выходы которых подключены соответственно к информационным входам третьего и четвертого т{5иггеров, синхронизирующие входы которых объединены и подключены к седьмому выходу йлока управления, второй установочный вход первого триггера соединен с выходом старшего дополнительного разряда первого счетчика, счетный вход второго триггера

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля частоты | 1973 |

|

SU519643A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство допускового контролячАСТОТы | 1979 |

|

SU840755A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-07-23—Публикация

1982-08-27—Подача