Изобретение относится к вычислительной технике и может быть использовано в быстродействующих цифровых вычислительных устройствах, работающих в остаточных системах счисления, для выполнения немодульных операций .над числами невысокой разрядности (до 24 бит). Известно устройство для формирования позиционных признаков непозици онного кода, содержащее входной регистр, блок памяти для хранения конс тант, входы которого подключены к выходам входного регистра, а выходык соответствумцим входам блока после довательносоединенных двоичных сумматоров и дополнительного двоичного сумматора, по выходу подключенного к входу блока сумматоров, сумматор ранга числа, входы которого соединены с выходами переносов двоичных сум маторов, выходной сумматор, входы которого соединены с соответствующими выходами блока двоичных сумматоров, соединенными также через схему формирования переносов с входом сумматора ранга, выходной регистр и схе му анализа содержимого старших разря дов результата, входы которых соединены с выходом выходного сумматаpa И. Недостатком данного устройства является низкое быстродействие вслед ствие использования последовательного, алгоритма формирования поправки Амербаева. Наиболее близким к изобретению по технической сущности является устройство для определения ранга числа, содержащее tl регистров, блоки памяти, сумматор ранга, п блоков суммирования, П -1 элемент сравнения, блок задания знака и дополнительный блок памяти, причем выход j -го регистра ( j 1 , . . , , ti ) соединен с и ( ,k,К +2)-го входом ( j ,1 , k +1) блоков памяти (k .j-1,...n) входы VI -го блока суммирования (k 3,.,. я) соединены соответственно с выходами (i,k +2,k )-го (,k 1-К, )-го и (k,k -1, k )-го блоков памяти ( i 1, .. ., k -1X, -и вход первого блока суммирования соединен с выходом (i,n,n )-го блока памяти (i 1, ..., и ), первый и второй входы второ го блока суммирования соединены соот ветственно с выходами (1,0,2) и (2, 1,2) блоков памяти, выходы -го и (ч -)-1)-го блоков суммирования подключены соответственно к первому о и второму входам i -го элемента сравнения (i 2,...,h-1), выходы первого и и-го блоков суммирования подключены соответственно к первому и второму входам дополнительного блока памяти, выход которого подключен к первому входу сумматора ранга, выходы элементов сравнения соединены с соответствующими входами блока задания знака, выход которого соединен с вторым входом сумматора ранга, выход которого является выходом устройства 2 J. Недостатками известного устройст}ва являются большой объем оборудования и низкое быстродействие. Цель изобретения - сокращение аппаратурных затрат и повышение быстродействия устройства. Поставленная цель достигается тем, что устройство для определения ранга числа, содержащее k регистров, k блоков памяти, причем входы регистров являются входами устройства, выход каждого регистра соединен с входом соответствующего блока памяти, содержит (k+1) групп элементов И, группу элементов ИЛИ, группу элементов НЕ, k вспомогательных регистров и регистр ранга, причем входы каждого элемента ИЛИ группы соединены с выходами элементов И соответствующей группы, входы вспомогательных регистров являются установочными входами устройства, выход которого соединен с выходом регистра ранга, входы которого соединены с выходами соответствующих вспомогательных регистров, входы разрешения чтения которых соединены соответственно с выходами соответствующих элементов И (k+1)-и группы и выходом k -го элемента ИЛИ группы, первые входы элементов И (k+1)-и группы соединены с вьпсодами соответствующих элементов ИЛИ группы, выходы элементов ИЛИ группы с второго nok -и соединены соответственно с входами элементов НЕ группы, входы каждого из элементов И (k+1)-и группы начиная со второго, соединены соответственно с выходами элементов НЕ группы с номерами не меньшими номера элемента И, S -и выход р -и группы -го блока памяти подк.лючены к 1 -му входу В -го элемента И Р -и

группы (Е 1,

о.

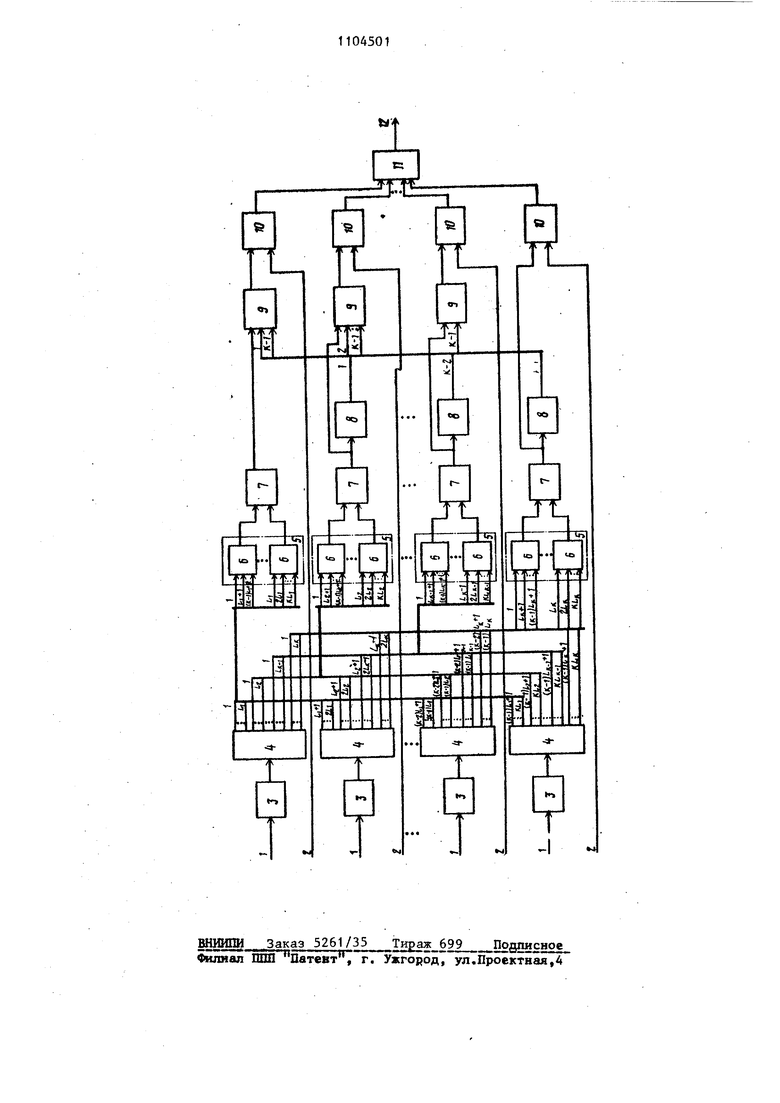

На чертеже приведена структурная схема устройства для определения ранга числа.

Устройство для определения ранга числа содержит входы 1 устройства, установочные входы 2 устройства, регистры 3, блоки 4 памяти, группы 5 элементов И 6, группу элементов ИЛИ 7 группу элементов НЕ 8, группу элементов И 9, вспомогательные регистры 10, регистр 11 ранга, выход 12 устройства.

Устройство для определения ранга числа работает следующим образом.

Остаточный код (ijf,|,n(;2x,...,oixK исходного целого числа А через входы 1 устройства поступает во входные регистра 3, после чего i -я цифра а,; кода подается на адресньй вход -го блока 4 памяти и из него считываются -е компоненты Лд логических шкал -Ле ( ,. ... ,о/, кк ) . С 1,2,... L), где

О, если 0, - о6

ApkO

11, если ui,; ot L - число наборов вычетов -«..,. ,ct,).

Посредством установочных вводов 2 параллельно во вспомогательные регистры 10 устройства записываются константы 0,1,..,k -1 соответственно.

Компоненты, считанные из блока 4 памяти поступают на входы элемента И 6, и на его выходе формируется Булова величина . Л ui-eC ; кV Величины, полученные на выходах элементов И 6 1 -и группы 5, подаются на соответствующие входы i -го элемента ИЛИ 7, в результате чего на его выходе сформируется признак

k

i,Л eUj.O 2::

(,) V

LVn1 Если W; 1, ТО ЧИСЛО i -1 рассматривается в качестве значения нормированного ранга р (А) исходного числа А.

Полученные величины ((/, поступают на первые входы элементов ИЛИ 7, на вторые входы которых через элементы НЕ 8 поступают проинвертированные значения Ц), . В результате на выходе I -го элемента И 9 имеем

(,,--VK,

который подается на вход разрешения

чтения информации -го вспомогательного регистра 10. На вход разрешения чтения информации k -го вспомогательного регистра 10, с выхода -го элемента ИЛИ 7 подается сигнал 2 .

Среди сигналов t, ,(-2 , ...,Сц. ненулевым является лишь о; , поэтому чтение информации происходит только из одного 1 -го вспомогательного регистра. Содержимое i -1 этого регистра, представляющее собой информационньй ранг р (А) исходного числа А, передается в регистр 11 ранга числа, откуда он поступает на выход 12 устройства, на этом операция формирования нормированного ранга числа заканчивается.

Время работы предлагаемого устройства не зависит от числа модулей системы .счисления и определяется временем срабатывания блоков памяти и логических элементов. Быстродействие известного устройства уменьшается пропорционально P. и уже при | 4 примерно в 2 раза меньше, чем у предлагаемого устройства.

Аппаратурные затраты предлагаемого устройства для k 4 примерно в полтора раза меньше, чем у известного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел в системе остаточных классов | 1983 |

|

SU1149254A1 |

| Устройство для масштабирования чисел в остаточной системе счисления | 1983 |

|

SU1140114A1 |

| Устройство для формирования интегральных характеристик модулярного кода | 1984 |

|

SU1216777A1 |

| Устройство для обработки видеоинформации | 1990 |

|

SU1732354A1 |

| ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2028665C1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1837293A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| УСТРОЙСТВО ДЛЯ РАНГОВОЙ ФИЛЬТРАЦИИ | 1990 |

|

RU2015551C1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1981 |

|

SU1042028A1 |

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ РАНГА ЧИСЛА, содержащее k регистров, k блоков памяти, причем входы регистров являются входами устройства, выход каждого регистра соединен с входом соответствующего блока памяти, отличающееся тем, что, с целью сокращения аппаратных затрат, оно содержит (k+1) групп элементов И, группу элементов ИЛИ, группу элементов НЕ, |( вспомогательных регистров и регистр ранга, причем входы каждого из элементов ИЛИ группы соединены с выходами Элементов И соответствующей группы, входы вспомогательных, регистров являются установочными входами устройства, выход которого соединен с выходом регистра ранга, входы которого соединены с выходами соответствующих вспомогательных регистров, входы разрешения чтения которых соединены соответственно с выходами соответствующих элементов И (k+1)-и группы и выходом k -го элемента ИЛИ группы, первые входы элементов И (}; + 1)-й группы соединены с выходами соответствующих элеменi тов ИЛИ группы, выходы элементов ИЛИ группы с второго по k -исоединены соответственно с входами элементов НЕ группы, входы каждого из элементов И (+1)-й группы, начиная со второго, соединены соответственно с выходами элементов НЕ группы с номерами не меньшими номера элемента И, t-й выходр-и группы 1 -го блока памяти подключен к i -му входу 6 -го элемента И р -и группы (С 1,Lp, СП 1,0 1...k , где Lp - количество наборов вычетов).

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ВСЕСОЮЗНАЯ iтЙЁ tft . ^>&^" - i-=---- | 0 |

|

SU365701A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для определения рангачиСлА | 1979 |

|

SU800989A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-23—Публикация

1983-04-04—Подача