Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей.

Известен преобразователь двоичнодесятичного кода в двоичный код, содержащий регистр числа, блок управлеимя, переключатель эквивалентов, распределитель импульсов, блок памяти, формирователь двоичного эквивалента тетрады, регистр сдвига и двоичный сумматор

Недостаток этого устройства состоит в том, что оно преобразует либо смешанные, либо дробные числа и не преобразует десятичные числа с отрицательным порядком.

Наиболее близким к предлагаемому по технической сущности и схемному решению является преобразователь двоично-десятичной дроби в двоичную дроб, содержащий первый, второй и третий регистры, накапливающий сумматор, первую, вторую и третью группу

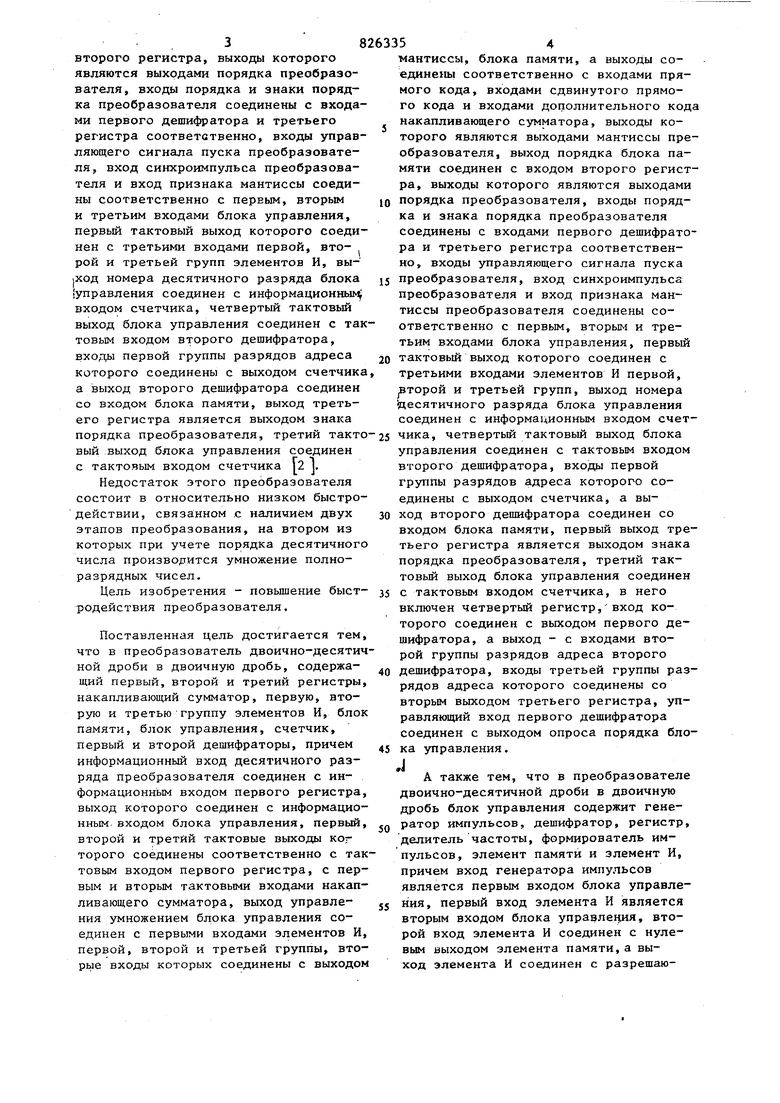

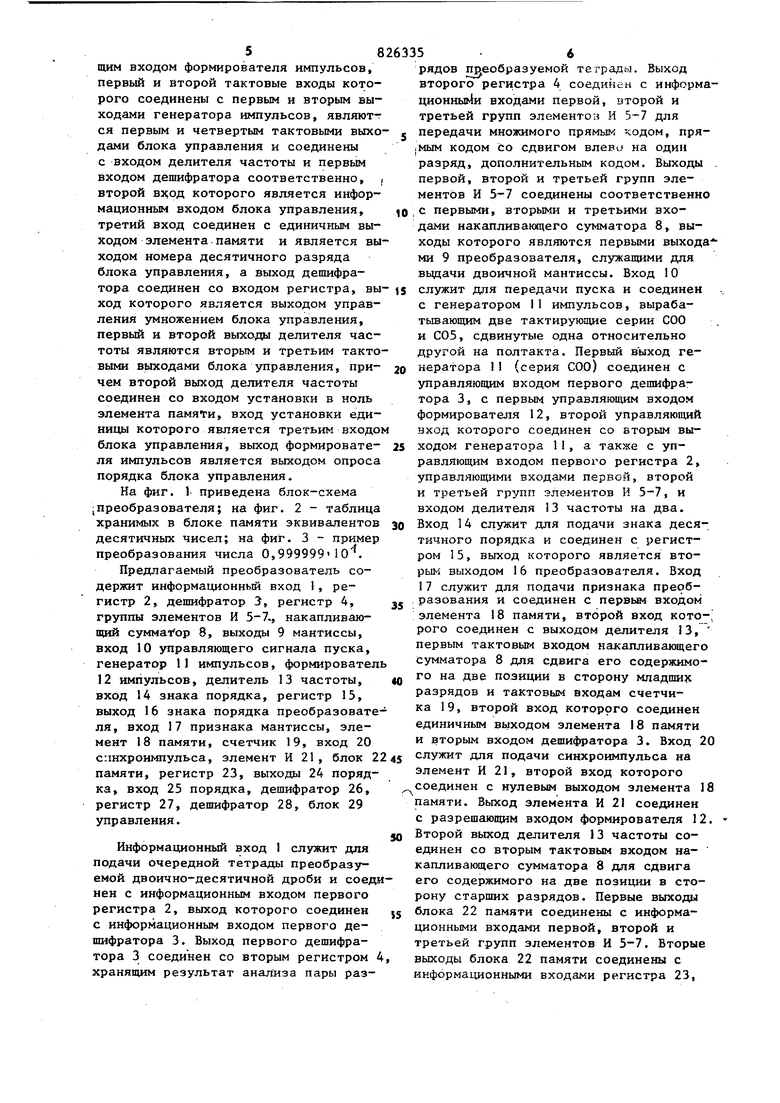

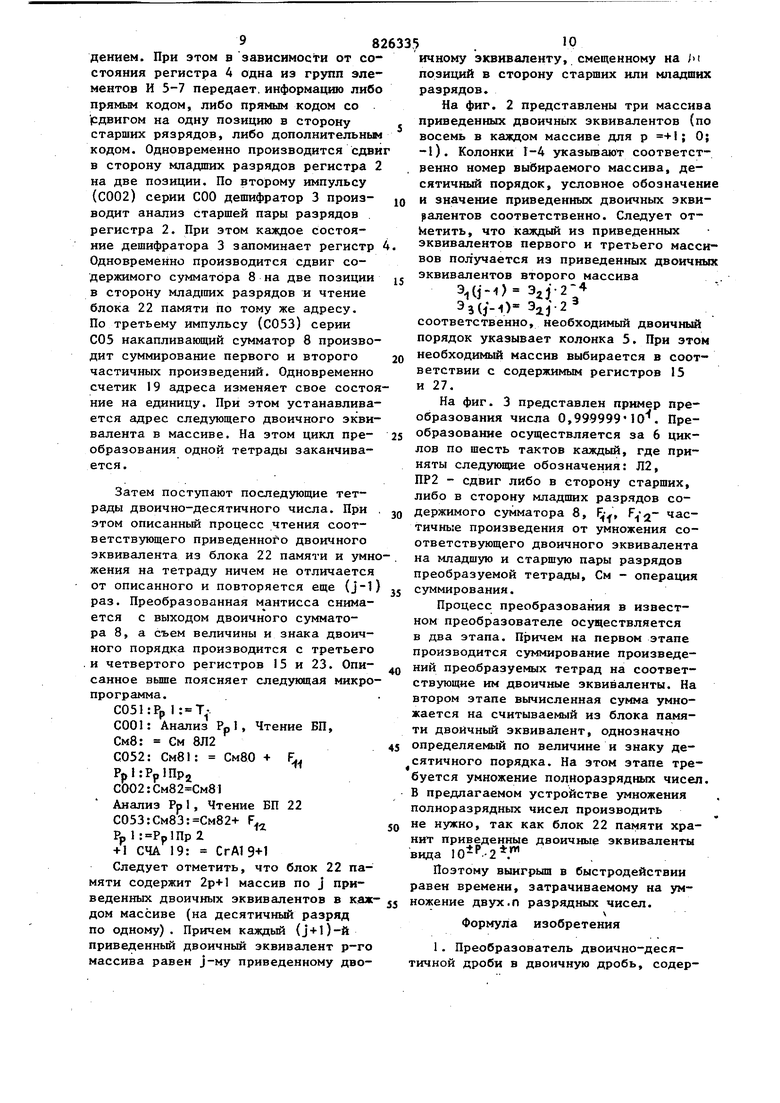

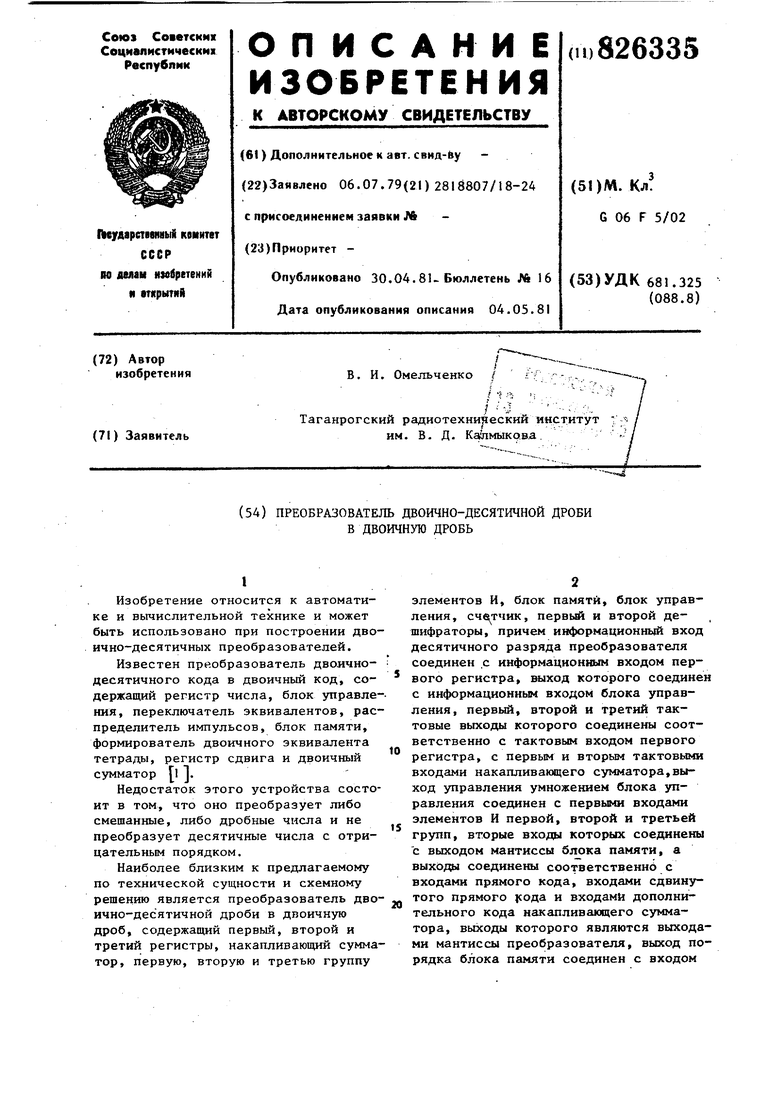

элементов И, блок памяти, блок управления, счетчик, первьЕЙ и второй дешифраторы, причем информационный вход десятичного разряда преобразователя соединен с информационным входом первого регистра, выход которого соедине с информационным входом блока управления, первый, второй и третий тактовые выходы которого соединены соответственно с тактовым входом первого регистра, с первым и вторым тактовыми входами накапливакяцего сумматора,выход управления умножением блока управления соединен с первы1 ш входами элементов И первой, второй и третьей групп, вторые входы которых соединены с выходом мантиссы блока памяти, а выходы соединены соответственно с входами прямого кода, входами сдвинутого прямого 1сода и входами дополнительного кода накапливающего сумматора, выходы которого являются выходами мантиссы преобразователя, выход порядка блока памяти соединен с входом второго регистра, выходы которого являются выходами порядка преобразователя, входы порядка и знаки порядка преобразователя соединены с входами первого дешифратора и третьего регистра соответственно, входы управляющего сигнала пуска преобразователя, вход синхроимпульса преобразователя и вход признака мантиссы соедини соответственно с первым, вторым и третьим входами блока управления, первый тактовый выход которого соединен с третьими входами первой, второй и третьей групп элементов И, вы|Ход номера десятичного разряда блока (управления соединен с информационны входом счетчика, четвертый тактовый выход блока управления соединен с так товым входом второго дешифратора, входы первой группы разрядов адреса которого соединены с выходом счетчика а выход второго дешифратора соединен со входом блока памяти, выход третьего регистра является выходом знака порядка преобразователя, третий такто вый выход блока управления соединен с тактовым входом счетчика 2 . Недостаток этого преобразователя состоит в относительно низком быстродействии, связанном с наличием двух этапов преобразования, на втором из которых при учете порядка десятичного числа производится умножение полноразрядных чисел. Цель изобретения - повышение быстродействия преобразователя. Поставленная цель достигается тем, что в преобразователь двоично-десятич ной дроби в двоичную дробь, содержащий первый, второй и третий регистры, накапливающий сумматор, первую, вторую и третью группу элементов И, блок памяти, блок управления, счетчик, первый и второй дешифраторы, причем информационный вход десятичного разряда преобразователя соединен с информационным входом первого регистра, выход которого соединен с информационным входом блока управления, первый, второй и третий тактовые выходы которого соединены соответственно с так товым входом первого регистра, с первым и вторым тактовыми входами накапливающего сумматора, выход управления умножением блока управления соединен с первыми входами злементов И, первой, второй и третьей группы, вторые входы которых соединены с выходом 8 54 мантиссы, блока памяти, а выходы соедине ш соответственно с входами прямого кода, входами сдвинутого прямого кода и входами дополнительного кода накапливающего сумматора, выходы которого являются выходами мантиссы преобразователя, выход порядка блока памяти соединен с входом второго регистра, выходы которого являются выходами порядка преобразователя, входы порядка и знака порядка преобразователя соединены с входами первого дешифратора и третьего регистра соответственно, входы управляющего сигнала пуска преобразователя, вход синхроимпульса преобразователя и вход признака мантиссы преобразователя соединены соответственно с первым, вторым и третьим входами блока управления, первый тактовый выход которого соединен с третьими входами элементов И первой. второй и третьей групп, выход номера (десятичного разряда блока управления соединен с информационным входом счетчика, четвертый тактовый выход блока управления соединен с тактовым входом второго дешифратора, входы первой группы разрядов адреса которого соединены с выходом счетчика, а выход второго дешифратора соединен со входом блока памяти, первый выход третьего регистра является выходом знака порядка преобразователя, третий тактовьй выход блока управления соединен с тактовым входом счетчика, в него включен четвертый регистр,вход которого соединен с выходом первого дешифратора, а выход - с входами второй группы разрядов адреса второго дешифратора, входы третьей группы разрядов адреса которого соединены со вторым выходом третьего регистра, управляющий вход первого дешифратора соединен с выходом опроса порядка блока управления. А также тем, что в преобразователе двоично-десятичной дроби в двоичную дробь блок управления содержит генератор импульсов, дешифратор, регистр, делитель частоты, формирователь импульсов, элемент памяти и элемент И, причем вход генератора импульсов является первьм входом блока управления, первый вход элемента И является вторым входом блока управления, второй вход элемента И соединен с нулевым выходом элемента памяти,а выход элемента И соединен с разрешающим входом формирователя импульсов, первый и второй тактовые входы которого соединены с первым и вторым выходами генератора импульсов, являют-г ся первым и четвертым тактовыми выхо дами блока управления и соединены с входом делителя частоты и первым входом дешифратора соответственно, второй которого является информационным входом блока управления, третий вход соединен с единичным выходом элемента памяти и является вы ходом номера десятичного разряда блока управления, а выход дешифратора соединен со входом регистра, вы ход которого является выходом управления умножением блока управления, первый и второй выходы делителя частоты являются вторым и третьим такто выми выходами блока управления, причем второй выход делителя частоты соединен со входом установки в ноль элемента памяти, вход установки единицы которого является третьим входо блока управления, выход формирователя импульсов является выходом опроса порядка блока управления. На фиг. 1- приведена блок-схема ;преобразователя; на фиг. 2 - таблица хранимых в блоке памяти эквивалентов десятичных чисел; на фиг. 3 - пример преобразования числа 0,99999910. Предлагаемый преобразователь содержит информационный вход 1, регистр 2, дешифратор 3, регистр 4, группы элементов И 5-7., накапливающий сумматор 8, выходы 9 мантиссы, вход 10 управляющего сигнала пуска, генератор 11 импульсов, формировател 12 импульсов, делитель 13 частоты, вход 14 знака порядка, регистр 15, выход 16 знака порядка преобразовате ля, вход 17 признака мантиссы, элемент 18 памяти, счетчик 19, вход 20 синхроимпульса, элемент И 21, блок 2 памяти, регистр 23, выходы 24 порядка, вход 25 порядка, дешифратор 26, регистр 27, дешифратор 28, блок 29 управления. Информационный вход I служит для подачи очередной тетрады преобразуемой двоично-десятичной дроби и соеди нен с информационным входом первого регистра 2, выход которого соединен с информационным входом первого дешифратора 3. Выход первого дешифратора 3 соединен со вторым регистром хранящим результат анализа пары разрядов преобразуемой тетрады. Выход второго регистра 4 соединен с информационныйи входами первой, второй и третьей групп элементез И 5-7 для передачи множимого прямым кодом, прямым кодом fco сдвигом влево на один разряд, дополнительным кодом. Выходы . первой, второй и третьей групп элементов И 5-7 соединены соответственно с первыми, вторыми и третьими входами накапливающего сумматора В, выходы которого являются первыми выхода ми 9 преобразователя, служащими для вьщачи двоичной мантиссы. Вход 10 служит для передачи пуска и соединен с генератором II импульсов, вырабатывающим две тактирующие серии СОО и С05, сдвинутые одна относительно другой на полтакта. Первый выход генератора 11 (серия СОО) соединен с управляющим входом первого дешифратора 3, с первым управляющим входом формирователя 12, второй управляющий вход которого соединен со вторым выходом генератора 1, а также с управляющим входом первого регистра 2, управляющими входами первой, второй и третьей групп элементов И 5-7, и входом делителя 13 частоты на два. Вход 14 служит для подачи знака десятичного порядка и соединен с регистром 15, выход которого является вторым выходом 16 преобразователя. Вход 17 служит для подачи признака преобразования и соединен с первым входом элемента 18 памяти, второй вход кото-j рого соединен с выходом делителя 13, первым тактовым входом накапливающего сумматора 8 для сдвига его содержимого на две позиции в сторону младшизс разрядов и тактовым входам счетчика 19, второй вход которого соединен единичным выходом элемента I8 памяти и вторым входом дешифратора 3. Вход 20 служит для подачи синхроимпульса на Элемент И 21, второй вход которого соединен с нулевым выходом элемента 18 памяти. Выход элемента И 21 соединен с разрешающим входом формирователя 12. Второй выход делителя 13 частоты соединен со вторым тактовым входом накапливающего сумматора 8 для сдвига его содержимого на две позиции в сторону старших разрядов. Первые выходы блока 22 памяти соединены с информационными входами первой, второй и третьей групп элементов И 5-7. Вторые выходы блока 22 памяти соединены с информа1Ц1онными входами регистра 23, выходы которого являются выходами 24 порядка преобразователя. Вход 25 соединен с информационным входом дешифратора 26, управляющий вход которого соединен с выходом формирователя 12. Выход дешифратора 26 соединен с регистром 27, выход которого соединен с информационным входом дешифратора, другие входы которого соединены соответственно с выходом регистра 15, входом формирователя 12 и выходом счетчика 19 адреса. Выход дешифратора 28 соединен с входом бло ка 22 памяти. Элементы 3, 4, 11 - 13 18 и 21 входят в состав блока управления 29 (см. фиг. 1). Лю0ое число в двоично-десятичной системе счисления можно представить в форме с плавающей запятой как где а. - мантисса преобразуемого десятичнОго числа, определяемая соотно шением i-j 2-10 , р г десятичный порядок; 10 основание десятичной системы счисления в соответствующей степени. Выражение (.1) можно представить в развернутом виде д - tp 1 tp -fi-l) 2-1о 1 2. Ю т -Л -Л +р П.0 JO . 1 Сложив степени с одинаковым основанием, получим следующее выражение (-t .-«-, 10 Выражение (3) в двоичной системе сч ления имеет следующий вид , 5frw tw А,-.ST. (10-), 2- 2 ,tM . (« приведенныйдв где i10- kr ичный эквивалент - двоичный порядок, определяемый соотношением , -гр , 5 Из выражения (4) следует, что процесс преобразования двоично-десятичного числа с плавающей запятой заключается в суммировании приведенных дво ичньпс эквивалентов тетрад и присвоении результату двоичного порядка. Приведенные двоичные эквиваленты тетрад получаются путем умножения преобразуемой тетрады на соответствующий приведенный двоичный эквивалент разряда, считываемый из блока памяти. Предлагаемый преобразователь реализует выражение (4) в следующей последовательности. По входу 10 на генератор I1 импульсов поступает сигнал Пуск, который вырабатывает две такт тирующих серии СОО и С05, сдвинутых одна относительно другой на полтакта. Затем по входу 14 поступает знак десятичного порядка. Одновременно по входу 20 на элемент И 21 поступает синхроимпульс, разрешающий пуск формирователя 12. При этом знак десятичного порядка записывается на третий регистр 15. Вслед за этим по входу 25 поступает д-есятичный порядок в двоичном коде. Одновременно запускается формирователь 12, вырабатывающий тактирующие импульсы и по первому из них производится расшифровка десятичного порядка на дешифраторе 26. Расшифрованный десятичный порядок с дешифратора 26 поступает на регистр 27. Затем по входу 17 поступает признак преобразования, которьш устанавливает элемент 21 памяти в единичное состояние, одновременно с записью старшей тетрады с первого входа 1 на регистр 2 по первому импульсу (С05 1) серии С05, поступающей со второго выхода генератора 11. При этом нулевое состояние счетчика 19 соответствует адресу двоичного эквивалента старшей тетрады в массиве. Затем по первому импульсу (cool) серии СОО дешифратор 3 производит анализ младшей пары разрядов содержимого регистра 2. Состояние дешифратора 3 записывается на регистр 4. Одновременно производится чтение блока 22 памяти по адресу, устанавливаемому дешифратором 28. При этом адрес массива .определяется содержимым регистров 15 и 27, а адрес двоичного эквивалента в массиве определяет счетчик адреса 19. По второму импульсу (С052) серии С05 производится суммирование содержимого сумматора 8 с первым частичным произведением. При этом в зависимости от со стояния регистра 4 одна из групп эле ментов И 5-7 передает, информацию либ прямым кодом, либо прямым кодом со . рдвигом на одну позицию в сторону старших разрядов, либо дополнительны кодом. Одновременно производится сдв в сторону младших разрядов регистра на две позиции. По второму импульсу (С002) серии СОО дешифратор 3 производит анализ старшей пары разрядов регистра 2. При этом каждое состояние дешифратора 3 запоминает регистр Одновременно производится сдвиг содержимого сумматора 8 на две позиции в сторону младших разрядов и чтение блока 22 памяти по тому же адресу. По третьему импульсу (С053) серии С05 накапливающий сумматор 8 произво дит суммирование первого и второго частичных произведений. Одновременно счетик I9 адреса изменяет свое состо ние на единицу. При этом устанавлива ется адрес следующего двоичного экви валента в массиве. На этом цикл преобразования одной тетрады заканчивается. Затем поступают последующие тетрады двоично-десятичного числа. При этом описанный процесс чтения соответствующего приведенного двоичного эквивалента из блока 22 памяти и умн жения на тетраду ничем не отличается от описанного и повторяется еще (j-l раз. Преобразованная мантисса снимается с выходом двоичного сумматора 8, а съем величины и знака двоичного порядка производится с третьего и четвертого регистров 15 и 23. Описанное вьшге поясняет следукидая микро программа. С051:Рр I : Т| Анализ Рр1 Чтение См 8Л2 См81 : См80 + F Рр1:РрШр2 С002:См82 См81 Анализ Рр1, Чтение БП 22 С053:См83: См82+ р1Пр2 СЧА 19: СгА19+1 Следует отметить, что блок 22 памяти содержит 2р+1 массив по j приведенных двоичных эквивалентов в каж дом массиве (на десятичный разряд по одному) . Причем каждый (j + l)-й приведенный двоичный эквивалент р-го массива равен j-му приведенному дво8 . 10 ичному эквиваленту, смещенному на М позиций в сторону старших или младших разрядов. На фиг. 2 представлены три массива приведенных двоичных эквивалентов (по восемь в каждом массиве для р +1; 0; -I). Колонки 1-4 указьгоают соответственно номер выбираемого массива, десятичный порядок, условное обозначение и значение приведенных двоичных эквивалентов соответственно. Следует ответить, что каждый из приведенных эквивалентов первого и третьего массивов получается из приведенных двоичных эквивалентов второго массива 3,(j.i) Эг1-2;4 Эз(г1) Чу соответственно, необходимый двоичный порядок указывает колонка 5. При этом необходимый массив выбирается в соответствии с содержимым регистров 15 и 27. На фиг. 3 представлен пример преобразования числа 0,99999940. Преобразование осуществляется за 6 циклов по шесть тактов каждый, где приняты следующие обозначения: Л2, ПР2 - сдвиг либо в сторону старших, либо в сторону младших разрядов содержимого сумматора 8, (у, частичные произведения от умножения соответствующего двоичного эквивалента на младшую и старшую пары разрядов преобразуемой тетрады. См - операция суммирования. Процесс преобразования в известном преобразователе осуществляется в два этапа. Причем на первом этапе производится суммирование произведений преобразуемых тетрад на соответствующие им двоичные эквиваленты. На втором этапе вычисленная сумча умножается на считываемый из блока памяти двоичный эквивалент, однозначно определяемый по величине и знаку десятичного порядка. На этом этапе требуется умножение полноразрядных чисел. В предлагаемом устройстве умножения полноразрядных чисел производить не нужно, так как блок 22 памяти хранит приведенные двоичные эквиваленты вида Поэтому выигрыш в быстродействии равен времени, затрачиваемому на умножение двух.п разрядных чисел. Формула изобретения 1. Преобразователь двоично-десяичной дроби в двоичную дробь, содержащий первый, второй и третий регист ры, накапливающий сумматор, первую, вторую и т-ретью группу элементов И, блок памяти, блок управления, счетчи первьш и второй дешифраторы, причем информационный вход десятичного разряда п-реобраэователя соединен с информационным входом первого регистра выход которого соединен с информациOHfftiM входом блока управления, первый, второй и третий тактовые выходы которого соединены соответственно с тактовым входом первого регистра, с первым к вторым тактовыми входами . накапливающего сумматора, выход управления умножением блока управления соединен с первыми входами элементов И первой, второй и третьей групп вторые входы которых соединены с выходом мантиссы блока памяти, а выХОД.Ы соединены соответственно с входами прямого кода, входами сдвинутого прямого кода и входами дополнительного кода накапливающего сумматора, выходы которого являются выходами мантиссы преобразователя, выход порядка блока памяти соединен с входом второго регистра, выходы кото рого являются выходами порядка преобразователя, входы порядка и знака порядка п геобразоватеггя соединены с йходамк первого дешифратора и третьего регистра соответственно входы управляющего сигнала пуска преобразователя, вход синхроимпульса преобразователя и вход признака мантиссы преобразователя соединены соответственно с nepBbiM, вторым и третьим вхо дами блока управления, первый тактовый выход которого соединен с третьи входами элементов И первой, второй и третьей групп, выход номера десяти ного разряда блока управления соединен с информациондам входом счетчика четвертый тактовый выход блока управ ления соединен с тактовым входом вто рого дешифратора,..входы первой групп разрядов адреса которого соединены с выходом счетчика, а Е;ЫХОД второго де шифратора соединен со входом блока памяти,первый выход третьего ре гистра является выходом знака порядка преобразователя, третий тактовый выход блока управления соединен с та - товым входом счетчика, отличаю щ и и с я тем, что, с целью повышен быстродействия, в него включен четвертый регистр, вход которого соединен с выходом первого дешифратора, а выход - с входами второй группы разрядов адреса, второго дешифратора, входы третьей группы разрядов адреса которого соединены со вторым выходом третьего регистра, управляющий вход первого дешифратора соединен с выходом опроса порядка блока управления. 2. Преобразователь по п. 1, отличающийся тем, что, в нем блок управления содержит генератор импульсов, дешифратор, регистр, делитель частоты, формирователь импульсов, элемент памяти и элемент И, причем вход генератора импульсов является первым входом блока управления, первьш вход элемента И является вторым входом блока управления, второй вход элемента И соединен с нулевым выходом элемента памяти, а выход элемента И соединен с разрешающим входом формирователя импульсов, первый и второй тактовые входы которого соединены с первым и вторым выходами генератора импульсов, являются первым и четвертым тактовыми выходами блока управления и соединены с входом делителя частоты и первьи входом дешифратора соответственно, второй вход которого является информационным входом блока управления, третий вход соединен с единичным выходом элемента памяти и является выходом номера десятичного разряда блока управлеьшя, а выход дешифратора соединен со входом регистра, выход которого является выходом управления умножением блока управления, первый и второй выходы делителя частоты являются вторым и третьим тактовыми выходами блока управления, причем второй выход делителя частоты соединен со входом установки в ноль элемента памяти, вход установки единицы которого является третьим входом блока управления, выход формирователя импульсов является выходом опроса порядка блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 473179, кл.б 06 F 5/02, 1970. 2.Авторское свидетельство СССР по заявке № 2649587/18-24, кл. G 06 F 5/02, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

Авторы

Даты

1981-04-30—Публикация

1979-07-06—Подача