I

Изобретение относится к вычислительной технике и предназначено для использования в цифровых устройствах реализующих немодульные операции над числами, представленными в модулярной системе счисления.

Цель изобретения - расширение функциональных возможностей устройства путем формирования ранга, ядра и коэффициентов пагшадического представления чисел.

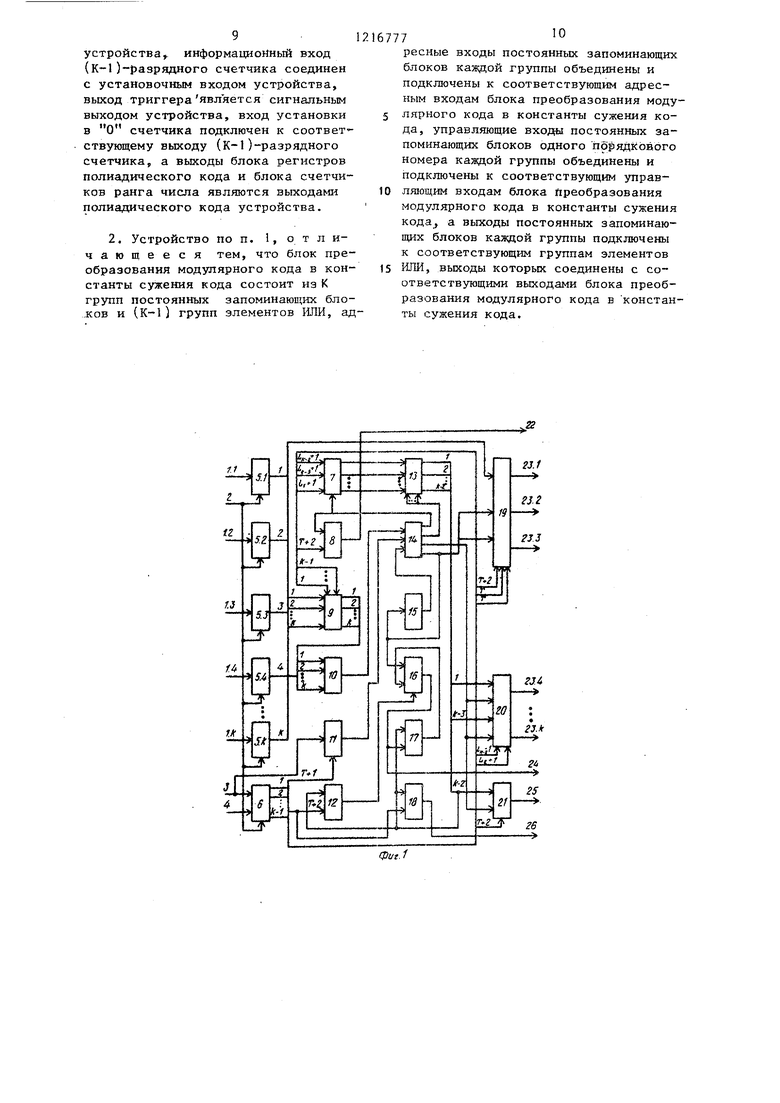

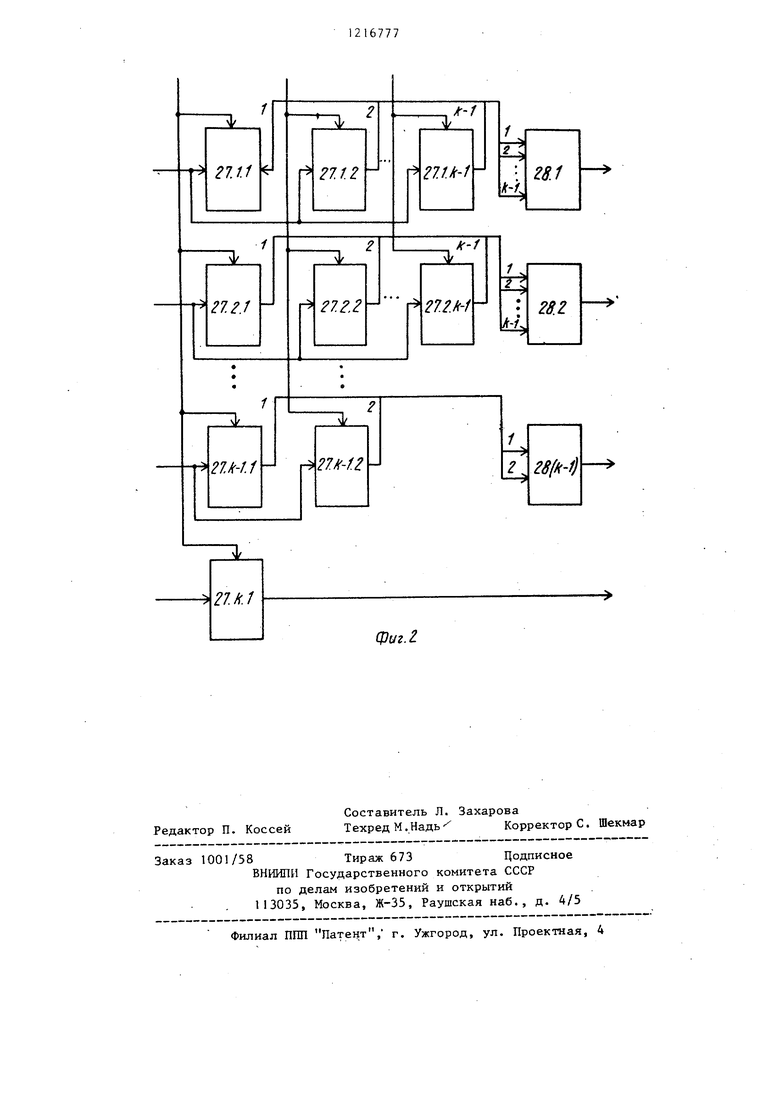

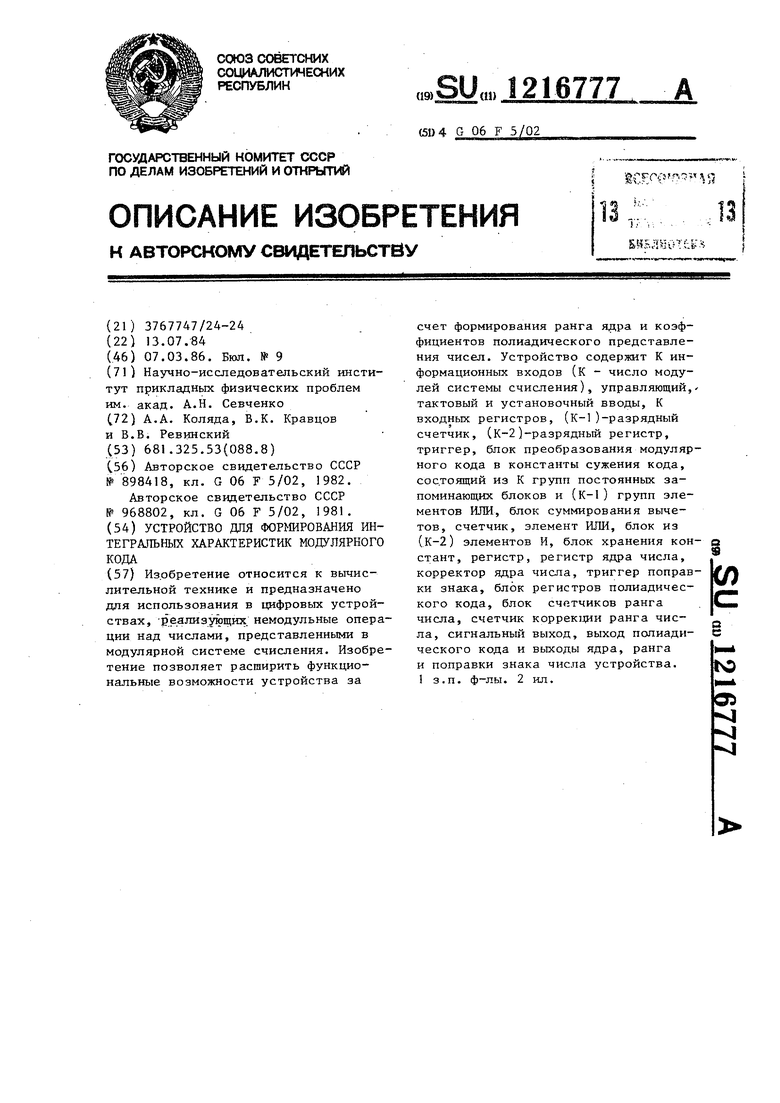

На фиг, 1 представлена структурная схема устройства для формирования интегральных характеристик модулярного кода; на фиг. 2 - выполнение блока преобразования модулярного кода в константы сужения кода.

Устройство содержит К -информационных входов 1 устройства (К - число модулей системы счисления),, управляющий вход 2 приема кода, тактовый вход 3, установочный вход 4 устройства, К входных регистров 5, кольцевой (К-1)-разрядный счетчик 6, (К-2) разрядньш регистр 7, триггер 8, блок 9 преобразования модулярного кода в константы сужения кода, блок 10 суммирования вычетов, счет- шк 11, элемент 12 ИЛИ, блок 3 из (К-2) элементов И, блок 14 хранения констант, вспомогательный регистр 15 регистр 16 ядра числа, корректор 17 ядра числа, триггер 8 поправки знака j блок 19 регистров полиадического кода, блок 20 счетчиков ранга числа, счетчик 21 коррекдаи ранга числа, сигнальный выход 22 устройства, выходы 23 полиадического кода устройства, выходы 24-26 соответственно ядра, ранга и поправки знака числа устройства.

Блок 9 преобразования модулярного кода в константы сужения кода содержит К групп постоянных запоминающих блоков 27 и (К-1) групп элементов .28 Ш1И.

Постоянный запоминающий блок 27 обладает емкостью m j слов, разрядность которых составляет b((,-j + i liogгInц-j.,Lбит. В память постоянного запоминакяцего блока 27 по адресу о(, 1 ,.. . ,т; -ij- записьгеается константа

,(L,)nLJbz ll/L, (i;

M

где М,, 1:;П , ., . . ,гпц - упорядоченные по убыванию основания мо

,

--,

2167772

дулярной системы счисления (); через 1 X обозначается наименьший неотрицательный вычет, сравнимый с величиной X по некоторому модулю Р, 5 ,CXj HJXC - соответственно ближайшие к X слева и справа целые числа.

Адресный вход с номером i блока 9 подключен к выходу соответствующего входного регистра 5, i-й выход - к

10 одноименному входу блока 10 суммирования вычетов, а j-й управляющий вход подключен к выходу (j-l)-ro разряда Ск-1)-разрядного счетчика 6 (i,2,,..,K; ,2,...,K-l; разря13 ды нумеруются начиная с О).

Блок 10 суммирования вычетов предназначен дпя сложения по модулю т па;к; (jCmj-l) за тактов (j 12 ,3,.;. ,KJ- наборов из К вьие20 тов по модулю т. Блок 10 имеет -Т-каскадную структуру и реализован на регистрах и сумматорах по модулю т.

Блок 19 регистров полиадического кода содержит три регистра для хра23 нения трех младших цифр кода. Информационный вход и выход i-ro регистра (.,2,3) подключены соответственно к i-M информационному входу и выходу блока 19, а управляющий вход приема

3Q кода - к 1-му управляющему входу блока 19 регистров. Блок 20 счетчика ранга числа состоит из счетчиков по модулям га, m5,-...,m. Счетный вход счетчика по модулю rrij подключен к . 1-му счетному входу блоки 19, управляющий вход приема кода - к i-му уп- равляиощему входу блока,- а выход является i-M выходом блока 20. Информационные входы всех счетчиков объе jj динёны и подключены к информационному входу блока 20 счетчиков.

Блок 14 хранения констант выполнен на основе долговременного злпр- 45 минающего устройства емкостью 2 5

слов разрядностью бит (Ъ , ,(K-l), ,3), bi llogjm,.

В память блока 14 хранения констант по адресу Q2 3 4-J2 записан набор константд

W,,, (Q,X).j , S.,, ,i, Q,X, 55 определяемый соотношениями

fO, если a..T,,j,, или если U - в остальных случаях.

О,если j 0

K-j

т./.

X.-J 1- 1

in

K-J

+ xlКРСЛИ J i 0 ;

л

o-K-J + i-A

LQ 1

если

Q

n

K.-J

K.-j + 1 J 0 ,

k-j

- X

h-,,

Корректор 17 ядра числа по входным величинам 1 0,1 .... , и ,1}, поступающим соответственно на второй и первый входы, определяет ядро числа по формуле

к-- к0кКорректор 17 ядра числа может быть реализован с помощью (1+Ь)-раз рядного вычитателя, или постоянного запоминающего устройства емкостью т слоен разрядностью (1+Ъ|) бит, где bK logjm.

Рассмотрим работу устройства для формирования интегральных характеристик модулярного кода. По сигналу, поступающему на управляющий вход 2 устройства, во входные регистры 5 и (К-1)-разрядный счетчик 6 через информационные входы 1 и установочный вход 4 устройства поступают соответственно модулярный код (Ьу, L5,...,Lx) исходного числа Af{0,l,.. ...,M-l} ()m,, ,2,...,K и двоичный код единицы, после чего начинается первый такт операции формирователя интегральных характеристик модулярного кода числа А.

Остаток о(; с выхода регистра 5 через блок 9 преобразования модулярного кода в константы сужения кода поступает на адресные входные шины соответствующего запоминающего блока 27, на управляющий вход выдачи кода которого с выхода (К-1)-разрядного счетчика 6 подается сигнал Sj-f для всех i 1 ,.2 ,.. . ,К; j l ,2 ,.. . ,К-1 . Так как на первом такте, работы устройства среди сигналов 6 , б ,. . . ,. . , О|.7. является лишь сигнал S(,, то на выходах блока 9 сформируется набор констант

U q,(L,), a,(L),...,q,(LK), считанный из памяти постоянных запоминающих блоков. 27. Компоненты набора Uy передаются в блок 10 суммирования вычетов, который по истечении очередных Т тактов определит величину

К

Q,, (Li).

На каждом йкте работы устройства по сигналу, подаваемому на тактовый вход 3 устройства, содержимое счетчика 6 сдвигается на один бит по направлению к старшим рядам, а содержимое счетчика 11 увеличивается на единицу. В результате этого на j-м такте (,3,...,К-1) в блоке 9 сработают постоянные запоминакдцие блоки 27, ив блок 10 суммирования поступает набор вычетов

(bi),qj(L),...,qj( ), и,.. . , и X.

Суммируя констаты набора Uj, блок 10 по истечении (T+j)-ro такта получает величину

J-H

«. II JjCLi).

1-1

На (Т+)-м такте в единичном состоянии находится Т-й разряд счетчика 6, поэтому на этом этапе счетчик 11 будет обнулен, а на (Т+2)-м такте в нулевое состояние установятся триггеры 8 и 18, так как на нулевые их входы поступает сигнал В этот же момент сигнал 1 через второй вход элемента 12 ИЛИ пройдет на управляющий вход блока 19 регистров и управляющий вход приема

кода блока счетчиков 20. В результате в блок 19 регистров через первый информационный его вход с вьосода соответствующего регистра 5 поступает остаток L, совпадающий с первой

цифрой а полиадического кода числа А, а в блок счетчиков 20 и регистр 16 с третьего и четвертого выходов блока 14 хранения констант поступают соответственно третья и

четвертая константы набора величин I

w,CQiX)5,s,,i,,,if ,X ,

формируемого согласно соотношениям С2-6) блоком 14 ко входным величинам Q, и X , поступающим соответственно с выходом блока 10 суммирования вычетов, счетчика 11 и вспомогательного регистра 15 (значение величины X на данном такте несущественно). д

Величина 7 записывается также в регистр 16 ядра. Согласно изложенному, на (T+j+2)-M такте (,2,...

..К-2) из памяти блока 14 хранения констант будет считан набор констан

л

j4 (Qj-nMvt-jii,9K-JsS.j sa.

§K-.J 1Так как на рассматриваемом такте

сигнал®. 1,. где L...|. l T+J + 11 К-1, то величина с р ётьего выхода блока 14 будет передала в (K-j+l)-ft счетчик блока 20 через информационный его вход, если ФК-2, и в третий регистр блока 19 при , величина с четвёртого выхода блока 14 передается в регистр 15, а также во второй регистр блока 19, если , Отметим, что величины, и а, получаемые ссотв ётственнр. на третьем и четвертом выходах блока 4 хранения констант в {Т+К)-м такте работы устройства ()5 являются соответственно второй и третьей цифрами полиадического представления числа А, , .

л

;.1Тризнак 8 с первого вькода блока 14 подается на единичный триггер и вход установки в О регистра 7, после чего в него записываются содержимое соответствующих разрядов счетчика б, а величина , вырабатьшэ.е мая на втором выходе блока 14, поступает па вторые входы элементов И блока 13 . Если 0 то и 8,, 0, поэтому в данном случае на выходах всех элементов И блока 3 отсутствует единичный сигнал, благодаря чем содержимое счетчиков блока 20 и счетчика 21, регистра 16 и триггера 18 останется неизменным, а в ()-й разряд регистра 7 с выхода разряда счетчика 6 поступает 1. Предположим теперь, что ,-,,,, . ., + , l, (существование указанного j следует из того, что в рамках реализуемого алгоритма всегда S 1}, Тогда на ()-M такте операции в старших J/J разрядах регистра 7 будут записаны .единшда (первый маркирующий код), вследствие чего на выходах блока 13 элементов И с номерами K-J-,,-,. ,,К-3 и К-2 формируются соответственно поправки знака числа .,,,,: ©k-f и Qj;, равные полученной на втором выходе блока.14 хранения констант величине 8 K-j, . Поправка подается на счетный вход счетчика 21 для коррекции ранга, первый вход корректо5

0

0

5

ра 17 ядра; единичный вход триггера 18 поправки знака числа и первый вход элемента 12 ИЛИ. Если 0,1, то корректор 17 ядра числа произведет коррекцию содержимого { регистра 16 и полученное, таким образом,, значение ядра к числа А с выхода коррек,тора 17 запишется в регистр 16 ядра, так как в данный момент на его управляющий вход приема кода с выхода элемента 12 ИЛИ поступает единичный сигнал, в счетчике 21 сформируется ранг числа А по формулер - + + 6, а в триггер 18 запишется поп- равка0| ;. Если6 к 0, то указанные действия не выполн.яются. В этом случае в регистре 16, триггере 18 и счетчике 21 находятся искомые значения соответствующих интегральных характеристик модулярного кода. Так как на рассматриваемом (T+j,+2)-M такте операции сформированный на первом выходе блока 14 хранения констант признак Э j.f регистр 7 обнуляется, после чего на его вхо- ды подается содержимое соответствующих разрядов счетчика 6, а триггер 8

установится в единичное состояние, сигнализируя тем самым посредством выхода 22 устройства о том, что на выходах 24-26 устройства сформированы соответственно ядро , ранг J и поправка знака числ а . отвечающие исходному числу А.

Если. , то наряду с описанным действиями на ()-M такте поправки ®K-. (,3,.,.,) с выхода ( элемента И блока 13 поступает на счетньй вход (K-j-l)-ro счетчика блока 20 и после коррекции его содержимого получается ()-я полиадического кода числа А

(а K-./H.Z |aK-j+2+ K-J iK остальные цифры полиадического кода числа А формируются аналогично на последующих тактах работу устройства. Пусть среди признаков S ,S ,. . , , f единичные .знач.етя принимают лишь признаки ,. . . , c5 K-Ji . где 0.1, , тогда, согласно изложенному по истечении (T+j,:,+2)-ro такта (г 1 ,2 , . . , ,-1 ) j старших разрядов регистра 7 будут обнулены, а на (T+j,, .+2)-м на втором такте в разрядах регистра 7 с но- . мера уги K-J-3, K-jr-4,. . ,K-jh4i 2 со- держатся единицы, вследствие чего

71

на j-M выходе блока 13 элементов И (, Pv-.1f,-3,...,K-j,-D формируется поправка знака числа 0. 2., равная величине ., полученной на втором выходе блока 14 хранения констант. Поправка Gj. поступает на счетный вход (j+3)-го счетчика блр- ка 20, где формируется (+3)-я цифра полиадического кода числа А по прави лу aj4j laj43+ ;-2l ;4-3- коррек ции на (Т+К)-м такте содержимых соответствующих счетчиков и получения второй и третьей цифр полиадического кода чиста А во.втором и третьем регистрах блока 19 процесс формирования полиадического кода числа А за- вершае.тся. Значения цифр а , а, . . . .а снимаются с выходов 23 устро11ства и на этом опе-рация формирования интегральных характеристик модулярного кода числа А заканчивается.

Формула изобретения

1. Устройство для формирования интегральных характеристик модулярного кода, содержащее К входных регистров, входы которых являются информационными входами устройства, блок преобразования модулярного кода в константы сужения кода, блок суммирования вычетов, блок из (К-2) элементов И, элемент ИЛИ и триггер поправки знака, выход которого является выходом поправки знака устройства, отличающее ся тем, что, с целью расширения функциональных возможностей путем формирования ранга, ядра и коэффициентов полиадического представления чисел, в него вве дены (К-1) -разрядный счетчик, (К-2)- разрядный регистр, триггер, счетчикj блок хранения констант, вспомогатель- ньй регистр, .регистр ядра числа, корректор ядра числа, блок .регистров полиадического кода, блоков счетчиков ранга числа и счетчик коррекции ранга числа, выходы К входных регист ров соединены с адресными входами блока преобразования модулярного кода в.константы сужения кода,управляю щие входы которого подключены к соответствующим выходам (К-1)-разряд- ного счетчика, а выходы - к соответствующим входам блока суммирования вьпетов, входы (К-2)-разрядного регистра соединены с соответствующими выходами (к-1)-разрядного счетчика.

6777

а вход установки в О объединен с единичным в.ходом триггера и подклю- чен к первому выходу блока хранения .констант, первый, второй и третий

5 входы которого подключены к выходам соответственно блока суммирования вычетов, счетчика и вспомогательного регистра, первые входы блока из {К-2 ) элементов И соединены с соот10 ветствующими выходами (К-2 )- разряд- ного регистра, вторые входы объединены и подключены к второму выходу блока хранения констант, первые выходы подключены к соответствующим

)5 входам блока счетчиков ранга числа, а второй выход соединен с единичньм входом триггера поправки знака, первым входом корректора ядра числа и первым входом элемента ИЛИ,, второй

20 .вход которого объединен с нулевыми входами триггера поправки знака и триггера, управляющими входами блока регистров полиадического кода и счетчика коррекции ранга числа и

25 подключен к соответствующему выходу (К-1)-разрядного счетчика, другие управляющие входы блока регистров полиадического кода и управляющие входы блока счетчиков ранга числа

3Q подключены к соответствующим выходам (к-1 )- р.азрядн 6го счетчика, первый информационный вход блока регистров полиадического кода, инфо рма-; ционные входы блока счетчиков ранга числа и счетчика коррекций ранга

числа .объединены-, и подключены к треt -

тьему выходу блока хранения констант,

второй информационный вход блока регистров полиадического кода, вход вспомогательного регистра и первый вход регистра ядра числа объединены и подключены к четвертому выходу блока хранения констант, третий информационный вход блока регистров полиадического кода подключен к выходу первого входного регистра, вто. рой вход регистра ядра числа соеди нен с выходом корректора ядра числа, второй вход которого соединен с выходом регистра ядра числа и выходом

5 ядра числа устройства, выход элемента ИЛИ подключен к входу приема кода регистра ядра числа, управляющие входыf( входных регй стров и (К-1)- разрядного счетчика объединены и

55 подключены к управляющему входу устройства, счетные входы счетчика и (К-1)-разрядного счетчика объединены и подключены к тактовому входу

35

40

45

9

устройства, информационный вход (К-1)-разрядного счетчика соединен с установочным входом устройства, выход триггера является сигнальным выходом устройства, вход установки в О счетчика подключен к соответ-- ствующему выходу (К-1)-разрядного счетчика, а выходы блока регистров полиадического кода и блока счетчиков ранга числа являются выходами полиадического кода устройства.

2. Устройство по п. 1, о т л и- чающееся тем, что блок преобразования модулярного кода в константы сужения кода состоит из К групп постоянных запоминающих бло- жов и (К-1) групп элементов ИЛИ, ад77710

ресные входы постоянных запоминающих блоков каждой группы объединены и подключены к соответствующим адресным входам блока преобразования моду- 5 лярного кода в константы сужения кода, управляющие входы постоянных запоминающих блоков одного поряДков,дго номера каждой группы объединены и подключены к соответствующим управ10 ляющим входам блока Преобразования модулярного кода в константы сужения кода а выходы постоянных запоминающих блоков каждой группы подключены к соответствующим группам элементов

15 ШШ, выходы которых соединены с соответствующими выходами блока преобразования модулярного кода в константы сужения кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования интегральных характеристик модулярного кода | 1984 |

|

SU1266009A1 |

| Устройство для формирования интегральных характеристик модулярного кода | 1986 |

|

SU1464293A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для вычисления экспоненциальной функции в модулярной системе счисления | 1985 |

|

SU1317433A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1989 |

|

SU1672448A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

Изобретение относится к вычислительной технике и предназначено для использования в цифровых устройствах, -реализующих, немодульные операции над числами, представленными в модулярной системе счисления. Изобретение позволяет расширить функциональные возможности устройства за счет формирования ранга ядра и коэффициентов полиадического представления чисел. Устройство содержит К информационных входов (к - число модулей системы счисления), управляющий, тактовый и установочный вводы, К входных регистров, (К-1)-разрядный счетчик, (К-2)-разрядный регистр, триггер, блок преобразования модулярного кода в константы сужения кода, состоящий из К групп постоянных запоминающих блоков и (К-1) групп элементов ИЛИ, блок суммирования вычетов, счетчик, элемент ИЛИ, блок из (К-2) элементов И, блок хранения констант, регистр, регистр ядра числа, корректор ядра числа, триггер поправки знака, блок регистров полиадического кода, блок счетчиков ранга числа, счетчик корреки 1и ранга числа, сигнальный выход, выход полиадического кода и выходы ядра, ранга и поправки знака числа устройства. 1 з.п. ф-лы. 2 ил. (Л % ю О) vl

Редактор П. Коссей

Составитель Л. Захарова

Техред М.Надь Корректоре. Шекмар

1001/58Тираж 673Цодписное

ВНИИПН Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

| Устройство для формирования позиционных признаков непозиционного кода | 1980 |

|

SU898418A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования позиционных характеристик непозиционного кода | 1981 |

|

SU968802A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-03-07—Публикация

1984-07-13—Подача