Изобретение относится к вычислительной технике и может быть использовано при обработке двумерных массивов данных большой размерности, например изображений.

Известно устройство параллельной обработки видеоинформации, выполняющее операцию цифровой двумерной свертки, и содержащее ЗУ входного изображения, ЗУ весовых коэффициентов, блок считывания входного изображения, блок считывания весовых коэффициентов, группу умножителей, древовидную сеть сумматоров, мультиплексор, сдвиговый регистр, блок управления, состоящий из генератора опорных сигналов и схемы выделения синхросигналов.

Недостатком данного устройства является низкое быстродействие, связанное с тем, что распараллеливание обработки локальных фрагментов изображения осуществляется только по строкам.

Известно устройство параллельной обработки видеоинформации, выполняющее операции цифровой двумерной свертки и скользящей эквализации гистограмм, содержащее два мультиплексора, коммутатор, стековое ЗУ, ЗУ весовых коэффициентов, группу умножителей, группу арифметических устройств, регистр, блок управления.

Недостатком известного устройства является низкое быстродействие, связанное с тем, что распараллеливание обработки лоVJ

со ю со

СЛ 4

калыных фрагментов изображения осущест- вляется только по строкам.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является устройство для параллельной обработки видеоинформации, содержащее N умножителей (где N размерность векторов А и В, А {At, A2

AN}, В { 81, 62,..., Вы}), N мультиплексоров, мультиплексор выбора элемента вектора А, ПЗУ, N групп элементов И, каждая из которых содержит (2Q+1) элементов И (где Q - разрядность информационных входов умножителей), N элементов ИЛИ, N-1 сумматоров, соединенных в виде древовидной сети, инвертор, первый информационный вход I- го умножителя (i 1,N) соединен с входом загрузки элемента AI вектора А, вторые информационные входы умножителей соединены с выходами соответствующих мультиплексоров, первый информационный вход i-ro мультиплексора соединен с входом загрузки элемента Bj вектора В, вторые информационные входы мультиплексоров объединены и соединены с выходом ПЗУ, адресный вход ПЗУ соединен с выходом мультиплексора выбора обрабатываемого элемента, а информационные входы этого мультиплексора соединены с соответствующими входами загрузки элементов AI, q-й разряд (q 1,2Q) выхода i-ro умножителя (i i,N) соединен с первым входом q-ro элемента И i-й группы, кроме того, 20-й разряд выхода 1-го умножителя соединен с первым входом (2Q+1}-ro элемента И i-й группы, выходы первого и (2Q+1)-ro элементов И каждой из N групп элементов И соединены с первым и вторым входами соответствующего элемента ИЛИ, вход задания операции устройства соединен с входом инвертора, управляющими входами мультиплексоров и вторыми входами q-x (q 1, 2Q) элементов И всех групп, выход инвертора соединен с вторыми входами (2Q+1)-x элементов И, входы сумматоров первой ступени древовидной сети соединены с выходами соответствующих двух элементов ИЛИ и выходами соответствующих двух групп q-x элементов И (q 2, 2Q), причем выходы элементов ИЛИ являются младшими разрядами входов сумматоров, а выходы элементов И - соответствующими старшими разрядами входов сумматоров, входы сумматоров последующих ступеней древовидной сети соединены с выходами двух сумматоров предыдущей ступени, выход сумматора последней ступени древовидной сети является выходом устройства, первые входы синхронизации умножителей объединены и соединены с первым входом синхронизации устройства.

вторые входы синхронизации умножителей объединены и соединены с вторым входом синхронизации устройства.

Недостатком данного устройства является то, что оно выполняет только линейные операции цифровой обработки сигналов, сводимые к скалярному произведению двух векторов, и операции, основанные на определении jpjnra произвольного эле0 мента A (i 1,N) среди элементов изображения, представленных в виде вектора А (Aii A2,..., AN), при этом под рангом понимается номер, который данный элемент AJ занимает в ряду расположенных по возра5 станию элементов вектора А. Данное устройство не позволяет выполнять операции, основанные на определении значения элемента изображения, который имеет заданный ранг среди элементов вектора А, т.е.

0 такие распространенные операции обработки изображений, как ранговая и медианная фильтрация. Это значительно ограничивает возможности использования устройства в составе вычислительных комп5 лексов обработки изображений.

Цель изобретения - расширение функциональных возможностей путем определения значения элемента вектора с заданным произвольным рангом.

0 Поставленная цель достигается тем, что в устройство, содержащее N умножителей, где N - размерность обрабатываемого вектора элементов изображения, N групп элементов И, N элементов ИЛИ, входной

5 мультиплексор, блок суммирования, блок постоянной памяти и элемент НЕ, причем

i-й вход (1 1N) элементов изображения

устройства подключен к первому информационному входу 1-го умножителя, выходы с

0 первого по (20-1)-й i-ro умножителя, где Q - разрядность элементов изображения, подключены соответственно к первым входам элементов И с первого по (20-1)-й i-й группы, 20-й выход i-ro умножителя подключен

5 к первым входам 2Q-ro и (2Q+1)-ro элементов И i-й группы, выходы первого и (2Q+1)-ro элементов И i-й группы подключены соответственно к первому и второму входам i-ro элемента ИЛИ, выходы элементов И с вто0 рого по 20-й каждой группы и выходы элементов ИЛИ с первого по N-й подключены соответственно к информационным входам блока суммирования, первый вход задания операции устройства подключен к вторым

5 входам элементов И с первого по 20-й всех групп и к входу элемента НЕ, выход которого подключен к вторым входам (2Q+l)-x элементов И всех групп, выход входного мультиплексора подключен к адресному входу блока постоянной памяти, введены N

17

сдвигающих регистров, выходной мультиплексор, первый и второй счетчики, блок синхронизации, дешифратор, регистр ранга, узел сравнения, вспомогательный регистр, блок обнуления счетчика, группа элементов ИЛИ, первый и второй элементы И и элемент ИЛ И-НЕ, причем информационный вход устройства подключен к первому информационному входу входного мультиплексора и к информационному входу регистра ранга, выход которого подключен к первому информационному входу узла сравнения, выход которого подключен к первым входам первого и второго элементов И, выходы которых подключены соответственно к входу синхронизации и счетному входу первого счетчика, информационный выход которого подключен соответственно к первым входам элементов ИЛИ группы и к первому информационному входу выходного мультиплексора, выход которого подключен к информационному выходу устройства, выход блока постоянной памяти подключен к первым информационным входам сдвигающих регистров с первого по N-й, информационные выходы которых подключены соответственно к вторым информационным входам умножителей с первого по N-й, первый вход задания операции устройства подключен к первому входу режима блока синхронизации, первый и второй выходы которого подключены соответственно к счетному входу второго счетчика и входу синхронизации вспомогательного регистра, прямой и инверсный выходы которого подключены соответственно к информационному входу первого счетчика и второму информационному входу входного мультиплексора, второй вход задания операции устройства подключен к управляющим входам входного и выходного мультиплексоров и второму входу режима блока синхронизации, третий и четвертый выходы которого подключены соответственно к входам синхронизации сдвигающих регистров и первым входам синхронизации умножителей, вход признака синхронизации весовых коэффициентов устройства подключен к входам сдвига сдвигающих регистров, вход весовых коэффициентов устройства подключен к второму информационному входу первого сдвигающего регистра, выход переноса j-ro сдвигающего регистра 0 1N-1) подключен к

второму информационному входу (j+1)-ro сдвигающего регистра, вход синхронизации и вход запуска устройства подключены соответственно к третьему и четвертому входам режима блока синхронизации, пятый выход которого подключен к вторым входам синхронизации умножителей с пер1732354

вого по N-й и к входу синхронизации б .ка обнуления счетчика, вход начальной установки устройства подключен к входам начальной установки блока обнуления

счетчика, блока синхронизации, к входу синхронизации регистра ранга и входу установки в О второго счетчика, информационный выход которого подключен к входу дешифратора, к-й, (к 1, ,,., Q-2), выход которого

0 подключен к второму входу соответствующего элемента ИЛИ группы, выходы которых подключены к информационным входам вспомогательного регистра, (СМ)-й выход дешифратора подключен к первому

5 управляющему входу блока обнуления счетчика, к первому входу элемента ИЛИ-НЕ и второму входу первого элемента И, Q-й выход дешифратора подключен к второму управляющему входу блока обнуления

0 счетчика и второму входу элемента ИЛИ- НЕ, выход которого подключен к второму входу второго элемента И, выход блока суммирования подключен к второму информационному входу выходного мультиплексора

5 и второму информационному входу узла сравнения, шестой выход блока синхронизации подключен к третьим входам первого и второго элементов И и к третьему и четвер- томууправляющим входам блока обнуления

0 счетчика, первый и второй выходы которого подключены соответственно к входу установки в О первого счетчика и выходу признака готовности устройства.

Блок обнуления счетчика может содер5 жать три элемента И, элемент ИЛИ и триггер, причем первый, второй, третий, четвертый управляющие входы блока, вход синхронизации и вход начальной установки блока подключены соответственно к перво0 му входу первого элемента И, к первому входу второго элемента И, к второму входу первого элемента И, к первому входу третьего элемента И и к первому входу элемента ИЛИ, выход которого подключен к первому

5 выходу блока, выходы первого и второго элементов И подключены соответственно к входу установки в единицу и входу установки в 0 триггера, выход которого подключен к второму выходу блока и второму входу

0 третьего элемента И, выход которого подключен к второму входу элемента ИЛИ.

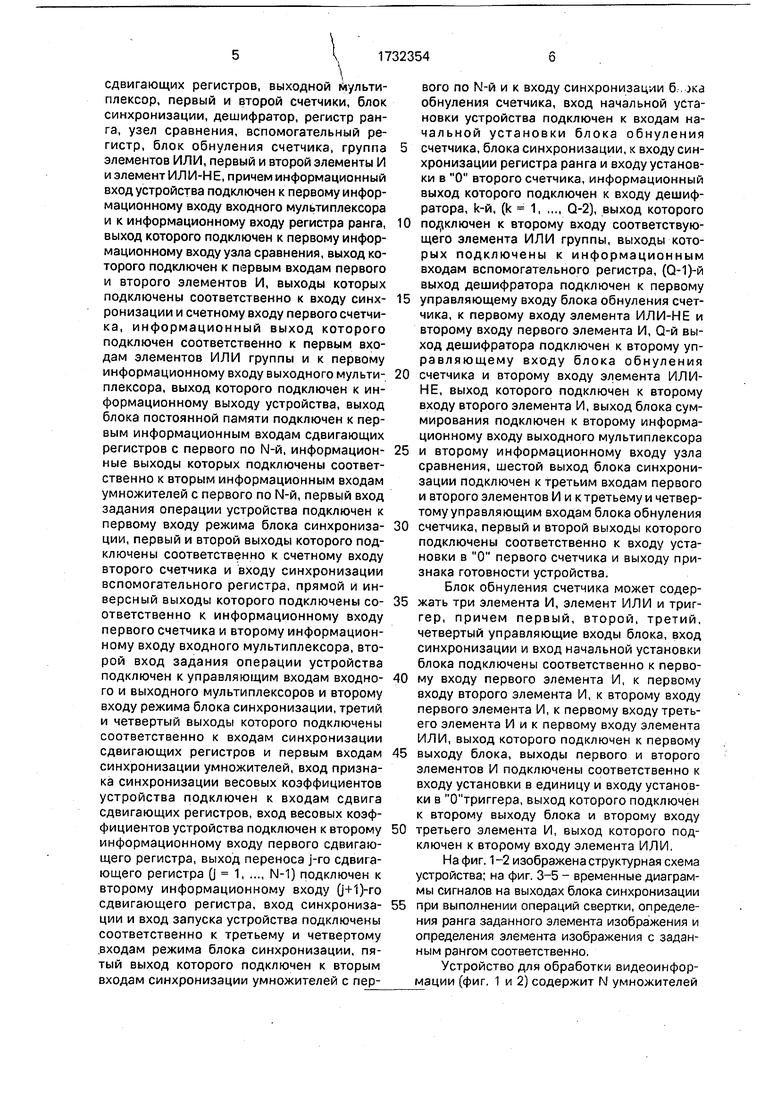

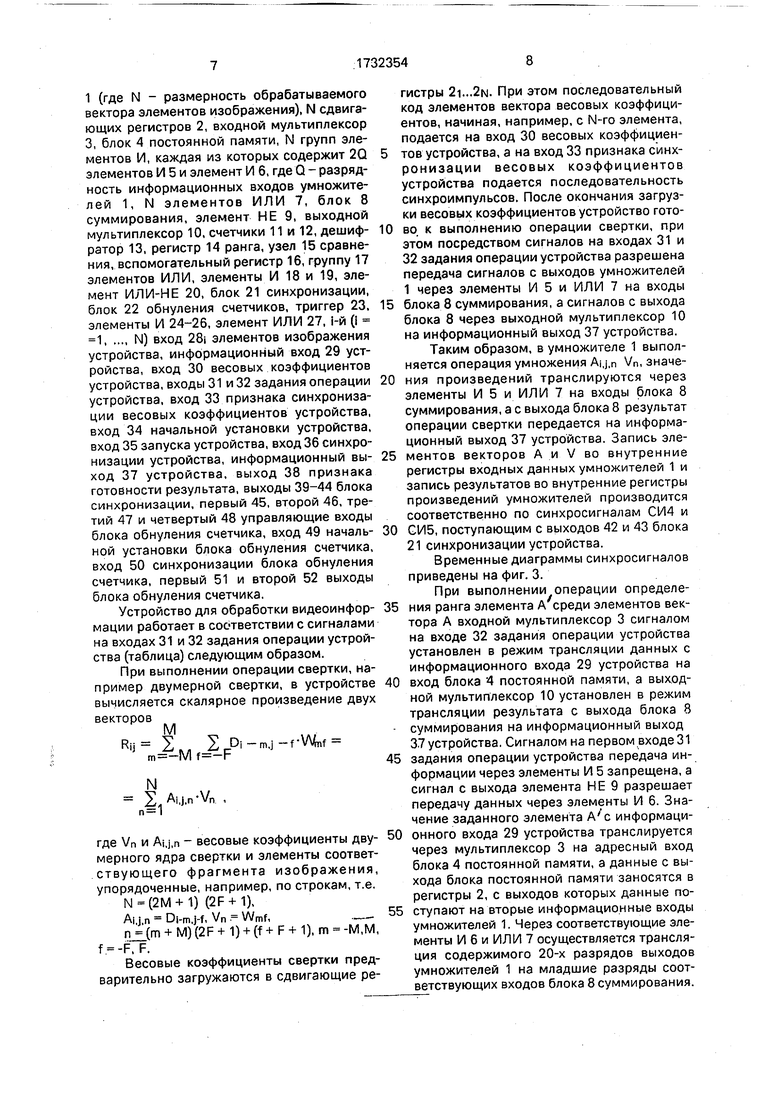

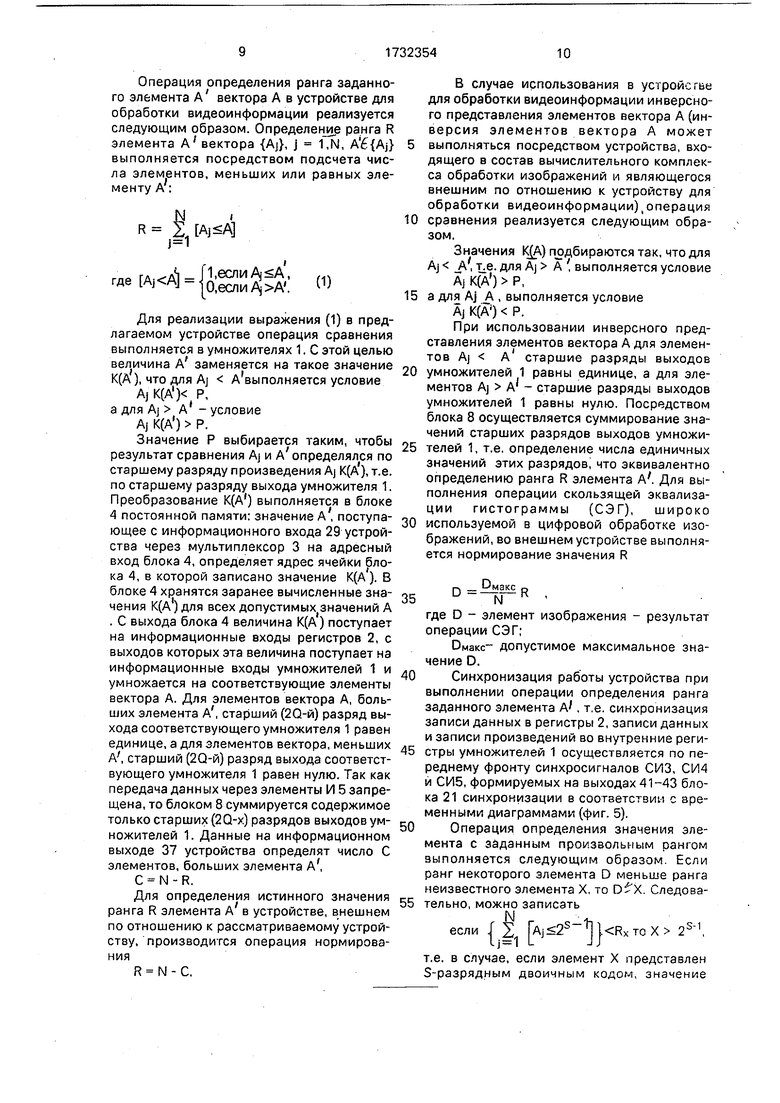

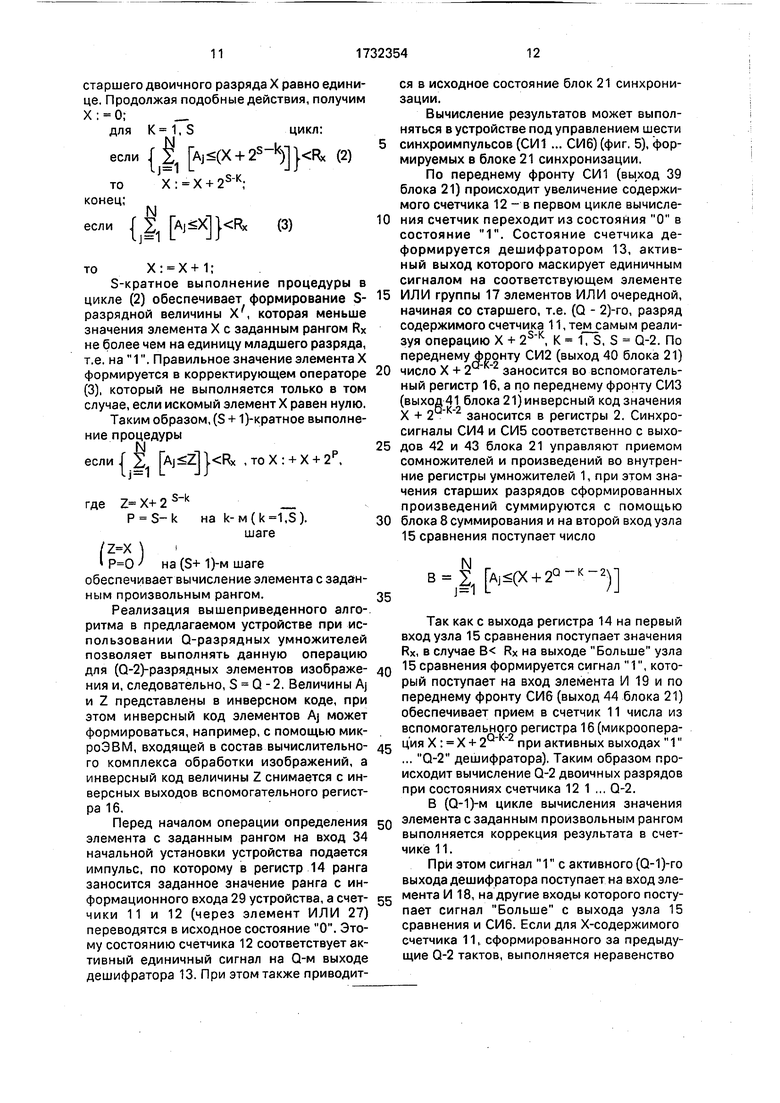

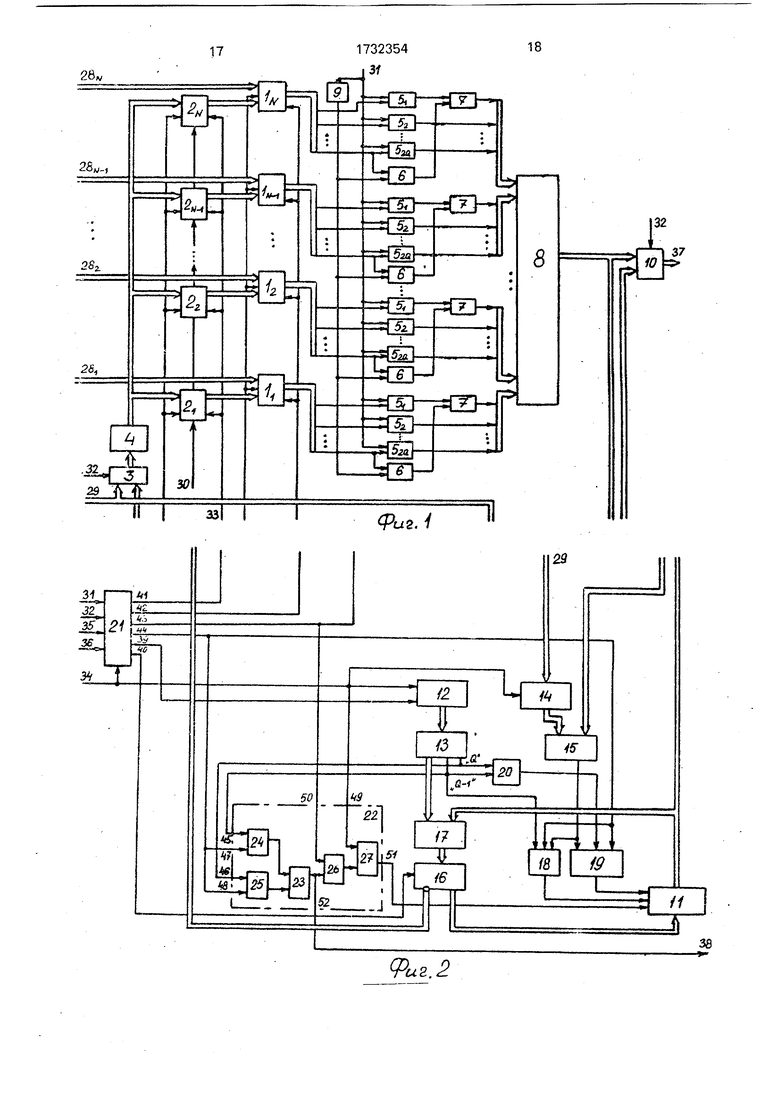

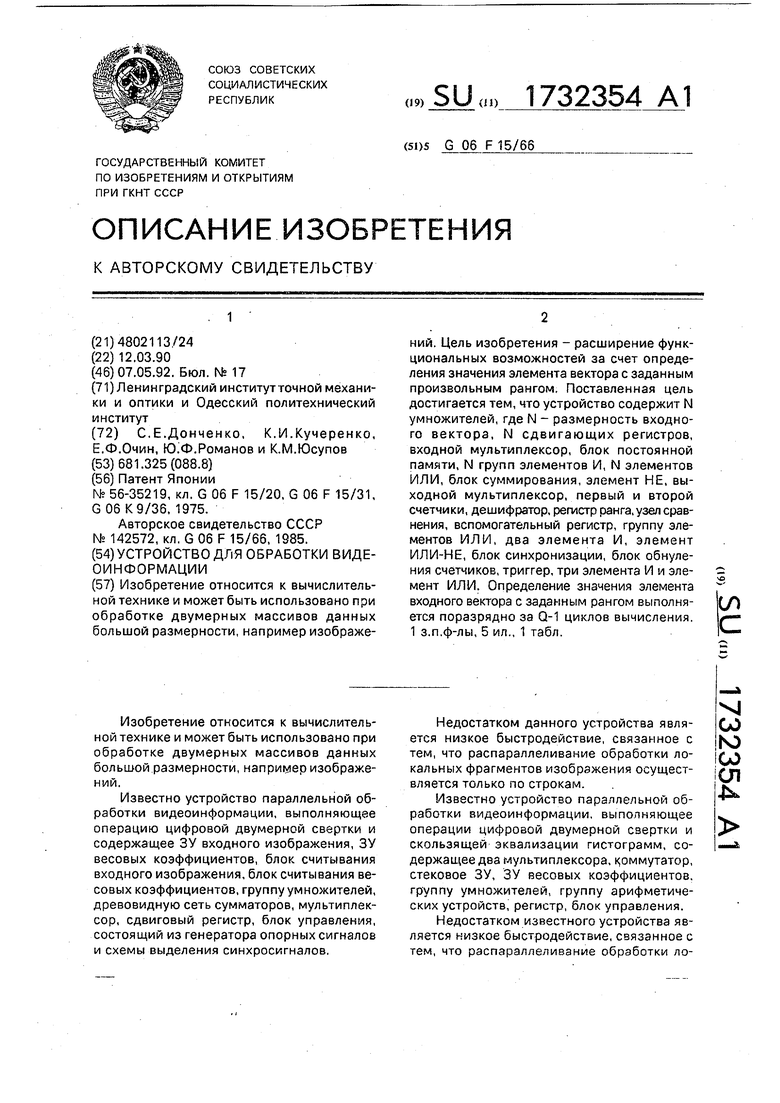

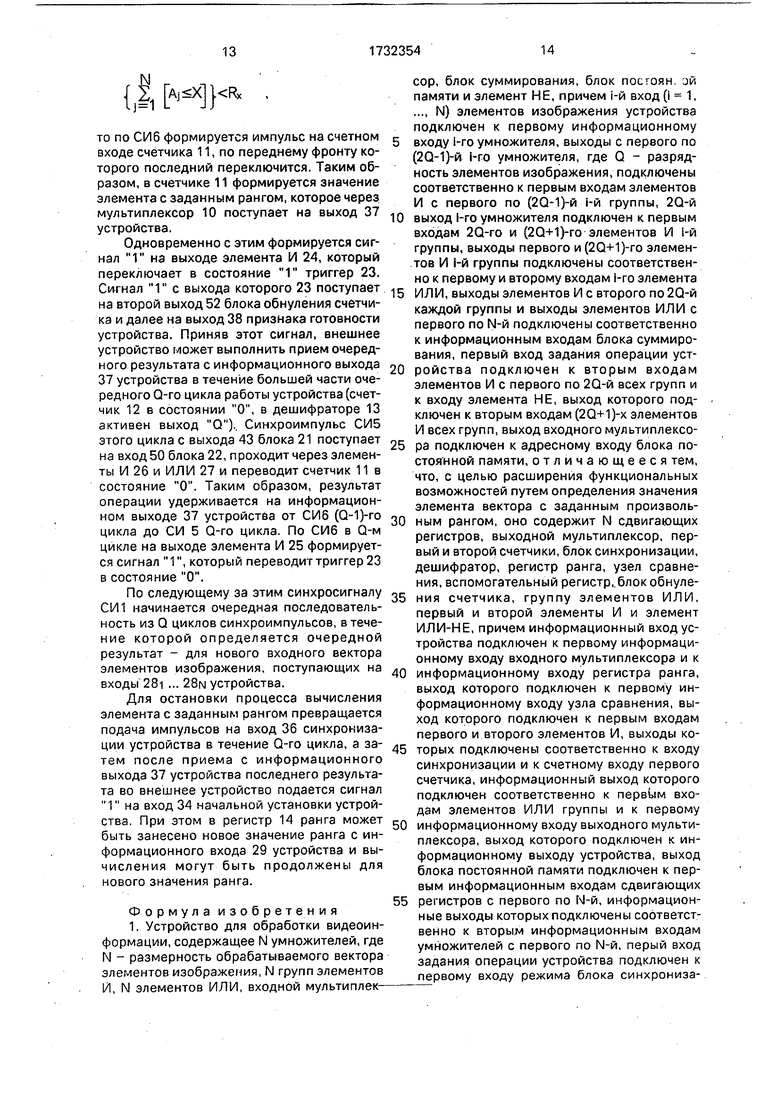

На фиг. 1 -2 изображена структурная схема устройства; на фиг. 3-5 - временные диаграммы сигналов на выходах блока синхронизации

5 при выполнении операций свертки, определения ранга заданного элемента изображения и определения элемента изображения с заданным рангом соответственно.

Устройство для обработки видеоинформации (фиг. 1 и 2) содержит N умножителей

1 (где N - размерность обрабатываемого вектора элементов изображения), N сдвигающих регистров 2, входной мультиплексор 3, блок 4 постоянной памяти, N групп элементов И, каждая из которых содержит 2Q элементов И 5 и элемент И б, где Q - разрядность информационных входов умножителей 1, N элементов ИЛИ 7, блок 8 суммирования, элемент НЕ 9, выходной мультиплексор 10, счетчики 11 и 12, дешифратор 13, регистр 14 ранга, узел 15 сравнения, вспомогательный регистр 16, группу 17 элементов ИЛИ, элементы И 18 и 19, элемент ИЛИ-НЕ 20, блок 21 синхронизации, блок 22 обнуления счетчиков, триггер 23, элементы И 24-26, элемент ИЛИ 27, i-й (i

1 N) вход 28i элементов изображения

устройства, информационный вход 29 устройства, вход 30 весовых коэффициентов устройства, входы 31 и 32 задания операции устройства, вход 33 признака синхронизации весовых коэффициентов устройства, вход 34 начальной установки устройства, вход 35 запуска устройства, вход 36 синхронизации устройства, информационный выход 37 устройства, выход 38 признака готовности результата, выходы 39-44 блока синхронизации, первый 45, второй 46, третий 47 и четвертый 48 управляющие входы блока обнуления счетчика, вход 49 начальной установки блока обнуления счетчика, вход 50 синхронизации блока обнуления счетчика, первый 51 и второй 52 выходы блока обнуления счетчика.

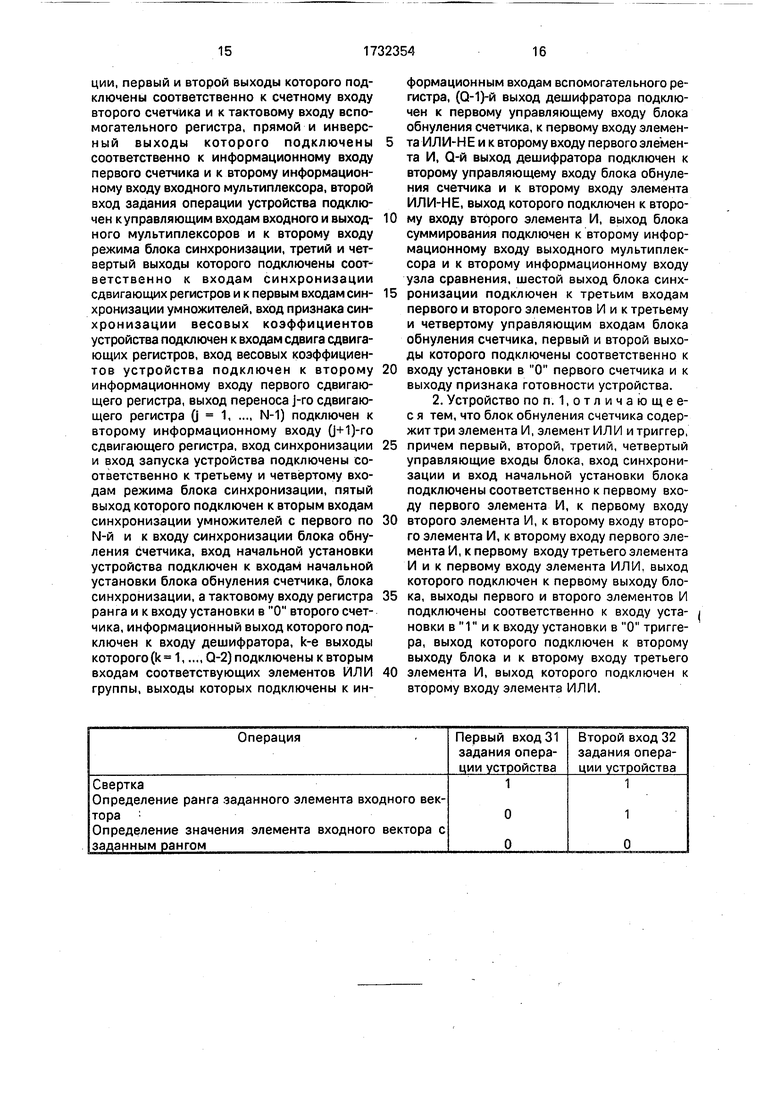

Устройство для обработки видеоинформации работает в соответствии с сигналами на входах 31 и 32 задания операции устройства (таблица) следующим образом.

При выполнении операции свертки, например двумерной свертки, в устройстве вычисляется скалярное произведение двух векторов

М

R|j 2 S Di-m,j-rWr,f

N

2 Aij.n-Vn

n l

где Vn и Aj.j.n - весовые коэффициенты двумерного ядра свертки и элементы соответствующего фрагмента изображения, упорядоченные, например, по строкам, т.е.

М-(2М + 1) (2F + 1).

Aij.n Di-mj-f, Vn Wmf,

n(m + M) (2F + 1) + (f + F + 1), m - -M,M, f -F, F.

Весовые коэффициенты свертки предварительно загружаются в сдвигающие регистры 2i.... При этом последовательный код элементов вектора весовых коэффициентов, начиная, например, с N-ro элемента, подается на вход 30 весовых коэффициентов устройства, а на вход 33 признака синхронизации весовых коэффициентов устройства подается последовательность синхроимпульсов. После окончания загрузки весовых коэффициентов устройство гото0 во. к выполнению операции свертки, при этом посредством сигналов на входах 31 и 32 задания операции устройства разрешена передача сигналов с выходов умножителей 1 через элементы И 5 и ИЛИ 7 на входы

5 блока 8 суммирования, а сигналов с выхода блока 8 через выходной мультиплексор 10 на информационный выход 37 устройства.

Таким образом, в умножителе 1 выполняется операция умножения Aj,j.n Vn, значе0 ния произведений транслируются через элементы И 5 и ИЛИ 7 на входы блока 8 суммирования, а с выхода блока 8 результат операции свертки передается на информационный выход 37 устройства. Запись эле5 ментов векторов А и V во внутренние регистры входных данных умножителей 1 и запись результатов во внутренние регистры произведений умножителей производится соответственно по синхросигналам СИ4 и

0 СИ5, поступающим с выходов 42 и 43 блока 21 синхронизации устройства.

Временные диаграммы синхросигналов приведены на фиг. 3.

При выполнении операции определе5 ния ранга элемента А среди элементов вектора А входной мультиплексор 3 сигналом на входе 32 задания операции устройства установлен в режим трансляции данных с информационного входа 29 устройства на

0 вход блока А постоянной памяти, а выходной мультиплексор 10 установлен в режим трансляции результата с выхода блока 8 - суммирования на информационный выход 37 устройства. Сигналом на первом входе 31

5 задания операции устройства передача информации через элементы И 5 запрещена, а сигнал с выхода элемента НЕ 9 разрешает передачу данных через элементы И 6. Значение заданного элемента А с информаци0 онного входа 29 устройства транслируется через мультиплексор 3 на адресный вход блока 4 постоянной памяти, а данные с выхода блока постоянной памяти заносятся в регистры 2, с выходов которых данные по5 ступают на вторые информационные входы умножителей 1. Через соответствующие элементы И 6 и ИЛИ 7 осуществляется трансляция содержимого 20-х разрядов выходов умножителей 1 на младшие разряды соответствующих входов блока 8 суммирования.

Операция определения ранга заданного элемента А вектора А в устройстве для обработки видеоинформации реализуется следующим образом. Определение ранга R элемента А вектора {Aj}, j 1,N, A Ј{Aj} выполняется посредством подсчета числа элементов, меньших или равных элементу А:

R

mo гд j1,ecnnAj A, m где о,еслиА1 А . 1

Для реализации выражения (1) в предлагаемом устройстве операция сравнения выполняется в умножителях 1. С этой целью величина А заменяется на такое значение К(А ), что для AJ А выполняется условие

AjK(A ) Р, а для AJ А - условие

AJ К(А ) Р.

Значение Р выбирается таким, чтобы результат сравнения AJ и А определялся по старшему разряду произведения AJ К(А), т.е. по старшему разряду выхода умножителя 1. Преобразование К(А ) выполняется в блоке 4 постоянной памяти: значение А , поступающее с информационного входа 29 устройства через мультиплексор 3 на адресный вход блока 4, определяет ядрес ячейки блока 4, в которой записано значение К(А ). В блоке 4 хранятся заранее вычисленные значения К(А) для всех допустимых значений А . С выхода блока 4 величина К(А) поступает на информационные входы регистров 2, с выходов которых эта величина поступает на информационные входы умножителей 1 и умножается на соответствующие элементы вектора А. Для элементов вектора А, больших элемента Аг, старший (20-й) разряд выхода соответствующего умножителя 1 равен единице, а для элементов вектора, меньших А , старший (20,-й) разряд выхода соответствующего умножителя 1 равен нулю. Так как передача данных через элементы И 5 запрещена, то блоком 8 суммируется содержимое только старших (2Q-x) разрядов выходов умножителей 1. Данные на информационном выходе 37 устройства определят число С элементов, больших элемента А ,

C N-R.

Для определения истинного значения ранга R элемента А в устройстве, внешнем по отношению к рассматриваемому устройству, производится операция нормирования

R N - С.

В случае использования в устройсгве для обработки видеоинформации инверсного представления элементов вектора А (инверсия элементов вектора А может

выполняться посредством устройства, входящего в состав вычислительного комплекса обработки изображений и являющегося внешним по отношению к устройству для обработки видеоинформации) перация

сравнения реализуется следующим образом.

Значения К(А) подбираются так, что для AJ А, т.е. для AJ А , выполняется условие AJ К(А ) Р,

а для Aj A., выполняется условие AJ К(А ) Р.

При использовании инверсного представления элементов вектора А для элементов AJ А старшие разряды выходов

умножителей 1 равны единице, а для элементов AJ А - старшие разряды выходов умножителей 1 равны нулю. Посредством блока 8 осуществляется суммирование значений старших разрядов выходов умножителей 1, т.е. определение числа единичных значений этих разрядов, что эквивалентно определению ранга R элемента А . Для выполнения операции скользящей эквализа- ции гистограммы (СЭГ), широко

используемой в цифровой обработке изображений, во внешнем устройстве выполняется нормирование значения R

п 0Макс о

где D - элемент изображения - результат операции СЭГ;

Омакс- допустимое максимальное значение D.

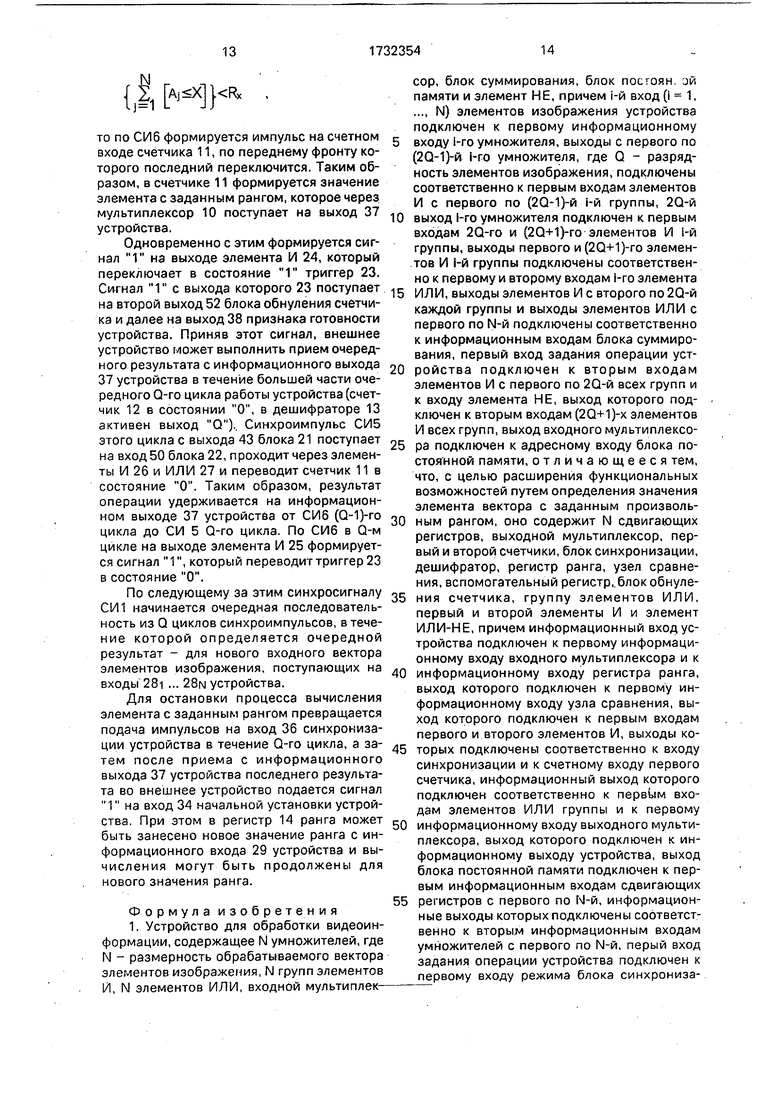

Синхронизация работы устройства при выполнении операции определения ранга заданного элемента А . т.е. синхронизация записи данных в регистры 2, записи данных и записи произведений во внутренние регистры умножителей 1 осуществляется по переднему фронту синхросигналов СИЗ, СИ4 и СИ5, формируемых на выходах 41-43 блока 21 синхронизации в соответствии с временными диаграммами (фиг. 5).

Операция определения значения элемента с заданным произвольным рангом выполняется следующим образом. Если ранг некоторого элемента D меньше ранга неизвестного элемента X. то . Следовательно, можно записать

N если | 2 Aj 2s ni RxToX 2s 1,

т.е. в случае, если элемент X представлен S-разрядным двоичным кодом, значение

старшего двоичного разряда X равно единице. Продолжая подобные действия, получим X : - 0;

для К 1, Sцикл:

если { | Aj(X + 2s-k) (2)

то конец;

S-K.

N

если { % Aj2ЈX } lb

(3)

то

Х: Х + 1;

S-кратное выполнение процедуры в цикле (2) обеспечивает формирование S- разрядной величины х , которая меньше значения элемента X с заданным рангом Rx не более чем на единицу младшего разряда, т.е. на 1. Правильное значение элементах формируется в корректирующем операторе (3), который не выполняется только в том случае, если искомый элемент X равен нулю.

Таким образом, (S + 1)-кратное выполнение процедуры

если

{-il ТоХ: + Х + 2р,

S-k

где Z X+ 2

P S-k на k-M(,S). шаге

/Z-X )

на (S+ 1)-м шаге обеспечивает вычисление элемента с заданным произвольным рангом.

Реализация вышеприведенного алгоритма в предлагаемом устройстве при использовании Q-разрядных умножителей позволяет выполнять данную операцию для (О2)-разрядных элементов изображения и, следовательно, S Q - 2. Величины AJ и Z представлены в инверсном коде, при этом инверсный код элементов AJ может формироваться, например, с помощью мик- роЭВМ, входящей в состав вычислительного комплекса обработки изображений, а инверсный код величины Z снимается с инверсных выходов вспомогательного регистра 16.

Перед началом операции определения элемента с заданным рангом на вход 34 начальной установки устройства подается импульс, по которому в регистр 14 ранга заносится заданное значение ранга с информационного входа 29 устройства, а счетчики 11 и 12 (через элемент ИЛИ 27) переводятся в исходное состояние О. Этому состоянию счетчика 12 соответствует активный единичный сигнал на Q-м выходе дешифратора 13. При этом также приводится в исходное состояние блок 21 синхронизации.

Вычисление результатов может выполняться в устройстве под управлением шести

синхроимпульсов (СИ1 ... СИ6) (фиг, 5), формируемых в блоке 21 синхронизации.

По переднему фронту СИ1 (выход 39 блока 21) происходит увеличение содержимого счетчика 12 - в первом цикле вычисления счетчик переходит из состояния О в состояние 1. Состояние счетчика деформируется дешифратором 13, активный выход которого маскирует единичным сигналом на соответствующем элементе

ИЛИ группы 17 элементов ИЛИ очередной, начиная со старшего, т.е. (Q - 2)-го, разряд содержимого счетчика 11, тегл самым реализуя операцию X + , К 1, S, S Q-2. По переднему фронту СИ2 (выход 40 блока 21)

число X + 2 2 заносится во вспомогательный регистр 16, а по переднему фронту СИЗ (выход 41 блока 21)инверсный код значения X + 2 2 заносится в регистры 2. Синхросигналы СИ4 и СИ5 соответственно с выходов 42 и 43 блока 21 управляют приемом сомножителей и произведений во внутренние регистры умножителей 1, при этом значения старших разрядов сформированных произведений суммируются с помощью

блока 8 суммирования и на второй вход узла 15 сравнения поступает число

N

35

В Aj(X + 2Q-K-2)

Так как с выхода регистра 14 на первый вход узла 15 сравнения поступает значения RX, в случае В RX на выходе Больше узла

15 сравнения формируется сигнал 1, который поступает на вход элемента И 19 и по переднему фронту СИ6 (выход 44 блока 21) обеспечивает прием в счетчик 11 числа из вспомогательного регистра 16 (микрооперац ия X : X + при активных выходах 1 ... Q-2 дешифратора). Таким образом происходит вычисление Q-2 двоичных разрядов при состояниях счетчика 12 1 ... Q-2.

В (Q-1)-M цикле вычисления значения

элемента с заданным произвольным рангом выполняется коррекция результата в счетчике 11.

При этом сигнал 1 с активного (СМ)-го выхода дешифратора поступает на вход элемента И 18, на другие входы которого поступает сигнал Больше с выхода узла 15 сравнения и СИ6. Если для Х-содержимого счетчика 11, сформированного за предыдущие Q-2 тактов, выполняется неравенство

{Ј

то по СИ6 формируется импульс на счетном входе счетчика 11, по переднему фронту которого последний переключится. Таким образом, в счетчике 11 формируется значение элемента с заданным рангом, которое через мультиплексор 10 поступает на выход 37 устройства.

Одновременно с этим формируется сигнал 1 на выходе элемента И 24, который переключает в состояние 1 триггер 23. Сигнал 1 с выхода которого 23 поступает на второй выход 52 блока обнуления счетчика и далее на выход 38 признака готовности устройства. Приняв этот сигнал, внешнее устройство может выполнить прием очередного результата с информационного выхода 37 устройства в течение большей части очередного Q-ro цикла работы устройства (счетчик 12 в состоянии О, в дешифраторе 13 активен выход Q)-. Синхроимпульс СИ5 этого цикла с выхода 43 блока 21 поступает на вход 50 блока 22, проходит через элементы И 26 и ИЛИ 27 и переводит счетчик 11 в состояние О. Таким образом, результат операции удерживается на информационном выходе 37 устройства от СИ6 (Q-1)-ro цикла до СИ 5 Q-ro цикла. По СИ6 в Q-м цикле на выходе элемента И 25 формируется сигнал 1, который переводит триггер 23 в состояние О.

По следующему за этим синхросигналу СИ1 начинается очередная последовательность из Q циклов синхроимпульсов, в течение которой определяется очередной результат - для нового входного вектора элементов изображения, поступающих на входы 28i ... 28м устройства.

Для остановки процесса вычисления элемента с заданным рангом превращается подача импульсов на вход 36 синхронизации устройства в течение Q-ro цикла, а затем после приема с информационного выхода 37 устройства последнего результата во внешнее устройство подается сигнал 1 на вход 34 начальной установки устройства. При этом в регистр 14 ранга может быть занесено новое значение ранга с информационного входа 29 устройства и вычисления могут быть продолжены для нового значения ранга.

Формула изобретения 1. Устройство для обработки видеоинформации, содержащее N умножителей, где N - размерность обрабатываемого вектора элементов изображения, N групп элементов И, N элементов ИЛИ, входной мультиплексор, блок суммирования, блок посгоян. эй памяти и элемент НЕ, причем i-й вход (, .... N) элементов изображения устройства подключен к первому информационному

входу 1-го умножителя, выходы с первого по (20-1)-й i-ro умножителя, где Q - разрядность элементов изображения, подключены соответственно к первым входам элементов И с первого по (20-1)-й i-й группы, 2Q-U

0 выход 1-го умножителя подключен к первым входам 2Q-ro и (2Q+1)-ro элементов И 1-й группы, выходы первого и (2Q+1)-ro элементов И i-й группы подключены соответственно к первому и второму входам i-ro элемента

5 ИЛИ, выходы элементов И с второго по 20-й каждой группы и выходы элементов ИЛИ с первого по N-й подключены соответственно к информационным входам блока суммирования, первый вход задания операции уст0 ройства подключен к вторым входам элементов И с первого по 2О-й всех групп и к входу элемента НЕ, выход которого подключен к вторым входам (2Q+1)-x элементов И всех групп, выход входного мультиплексо5 ра подключен к адресному входу блока постоянной памяти, отличающееся тем, что, с целью расширения функциональных возможностей путем определения значения элемента вектора с заданным произволь0 ным рангом, оно содержит N сдвигающих регистров, выходной мультиплексор, первый и второй счетчики, блок синхронизации, дешифратор, регистр ранга, узел сравнения, вспомогательный регистр, блок обнуле5 ния счетчика, группу элементов ИЛИ, первый и второй элементы И и элемент ИЛИ-НЕ, причем информационный вход устройства подключен к первому информационному входу входного мультиплексора и к

0 информационному входу регистра ранга, выход которого подключен к первому информационному входу узла сравнения, выход которого подключен к первым входам первого и второго элементов И, выходы ко5 торых подключены соответственно к входу синхронизации и к счетному входу первого счетчика, информационный выход которого подключен соответственно к первым входам элементов ИЛИ группы и к первому

0 информационному входу выходного мультиплексора, выход которого подключен к информационному выходу устройства, выход блока постоянной памяти подключен к первым информационным входам сдвигающих

5 регистров с первого по N-й, информационные выходы которых подключены соответственно к вторым информационным входам умножителей с первого по N-й, перый вход задания операции устройства подключен к первому входу режима блока синхронизации, первый и второй выходы которого подключены соответственно к счетному входу второго счетчика и к тактовому входу вспомогательного регистра, прямой и инверсный выходы которого подключены соответственно к информационному входу первого счетчика и к второму информационному входу входного мультиплексора, второй вход задания операции устройства подключен к управляющим входам входного и выходного мультиплексоров и к второму входу режима блока синхронизации, третий и четвертый выходы которого подключены соответственно к входам синхронизации сдвигающих регистров и к первым входам синхронизации умножителей, вход признака синхронизации весовых коэффициентов устройства подключен к входам сдвига сдвигающих регистров, вход весовых коэффициентов устройства подключен к второму информационному входу первого сдвигающего регистра, выход переноса j-ro сдвигающего регистра 0 1 N-1) подключен к

второму информационному входу С+1) го сдвигающего регистра, вход синхронизации и вход запуска устройства подключены соответственно к третьему и четвертому входам режима блока синхронизации, пятый выход которого подключен к вторым входам синхронизации умножителей с первого по N-й и к входу синхронизации блока обнуления счетчика, вход начальной установки устройства подключен к входам начальной установки блока обнуления счетчика, блока синхронизации, а тактовому входу регистра ранга и к входу установки в О второго счетчика, информационный выход которого подключен к входу дешифратора, к-е выходы

которого (к 1Q-2) подключены к вторым

входам соответствующих элементов ИЛИ группы, выходы которых подключены к информационным входам вспомогательного регистра, (СМ)-й выход дешифратора подключен к первому управляющему входу блока обнуления счетчика, к первому входу элемента ИЛИ-НЕ и к второму входу первого элемента И, Q-й выход дешифратора подключен к второму управляющему входу блока обнуления счетчика и к второму входу элемента ИЛИ-НЕ, выход которого подключен к второму входу второго элемента И, выход блока суммирования подключен к второму информационному входу выходного мультиплексора и к второму информационному входу узла сравнения, шестой выход блока синхронизации подключен к третьим входам первого и второго элементов Пик третьему и четвертому управляющим входам блока обнуления счетчика, первый и второй выходы которого подключены соответственно к

входу установки в О первого счетчика и к выходу признака готовности устройства.

2. Устройство поп. 1,отличающее- с я тем, что блок обнуления счетчика содержит три элемента И, элемент ИЛ И и триггер,

причем первый, второй, третий, четвертый управляющие входы блока, вход синхронизации и вход начальной установки блока подключены соответственно к первому входу первого элемента И, к первому входу

второго элемента И, к второму входу второго элемента И, к второму входу первого элемента И, к первому входу третьего элемента И и к первому входу элемента ИЛИ. выход которого подключен к первому выходу блока, выходы первого и второго элементов И подключены соответственно к входу установки в 1 и к входу установки в О триггера, выход которого подключен к второму выходу блока и к второму входу третьего

элемента И, выход которого подключен к второму входу элемента ИЛИ.

17

18

132

10

37

филЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для параллельной обработки видеоинформации | 1985 |

|

SU1425722A1 |

| Устройство для сортировки чисел | 1989 |

|

SU1793438A1 |

| Адаптивный автокоррелятор | 1990 |

|

SU1774345A1 |

| Вычислительное устройство для ранговой фильтрации | 1989 |

|

SU1656554A1 |

| Устройство для операций над матрицами | 1990 |

|

SU1737461A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1647592A1 |

| Устройство для определения среднего значения выборочного размаха | 1984 |

|

SU1363252A1 |

| Устройство для ранговой фильтрации с произвольной формой окна | 1990 |

|

SU1727137A1 |

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| Двухкаскадное устройство для ранговой фильтрации | 1985 |

|

SU1304036A1 |

Изобретение относится к вычислительной технике и может быть использовано при обработке двумерных массивов данных большой размерности, например изображений. Цель изобретения - расширение функциональных возможностей за счет определения значения элемента вектора с заданным произвольным рангом. Поставленная цель достигается тем, что устройство содержит N умножителей, где N - размерность входного вектора, N сдвигающих регистров, входной мультиплексор, блок постоянной памяти, N групп элементов И, N элементов ИЛИ, блок суммирования, элемент НЕ, выходной мультиплексор, первый и второй счетчики, дешифратор, регистр ранга,узел сравнения, вспомогательный регистр, группу элементов ИЛИ, два элемента И, элемент ИЛИ-НЕ, блок синхронизации, блок обнуления счетчиков, триггер, три элемента И и элемент ИЛИ. Определение значения элемента входного вектора с заданным рангом выполняется поразрядно за Q-1 циклов вычисления. 1 з.п.ф-лы, 5 ил., 1 табл. (Л С

9иг.2

/LJLJULJIJIJI-J

t t t

Сигнал на 36 синхро

Сигнал на 39,40,44

Сигнал на

41(СИЗ)

Сигнал на

42(СИП)

Сигнал на

43(СИ5)

Сигнал на входе 36 синхронизации

Сигнал на выходе

39(СЖ) Сигнал на выходе

40(CiK)

Сигнал.на выходе

41(СИЗ) Сигнал на выходе

42(C3I)

Сигнал на выходе

43(С И5)

Сигнал на выходе

44(С Ж)

Номер активного вихода . Т

Сигнал я вюсоце 3R

t t t

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Автомобилеопрокидыватель | 1960 |

|

SU142572A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-07—Публикация

1990-03-12—Подача