ройства, вторые входы предпоследних одноразрядных сумматоров столбцов с 2 по N соединены с входом логического нуля устройства, первый вход одноразрядного сумматора первого столбца соединен сг входом старшего разряда устройства, вход второго раз ряда которого соединен с вторьм входом одноразрядного сумматора первого столбца, выход которого соединен с вторым входом первого одноразрядного сумматора второго столбца, выход переноса первого одноразрядного сумматора первого столбца и выходы первых одноразрядных сумматоров осталь;ных столбцов являются соответствен4511

но выходами N старших разрядов результата устройства, выходы сумматора яв ляются соответственно выходами N младших разрядов результата устройства, входы разрядов подкоренного числа устройства соединены с соответствующими информационными входами коммутатора разрядов и входами дешифратора разрядов, выходы которого соединены с управляющими входами коммутатора разрядов и являются выходами порядка результата устройства, выходы коммутатора разрядов соединены с соответствующими разряд- да ными входами вычислительной матрицы .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1977 |

|

SU684540A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Устройство для извлечения квадратного корня | 1976 |

|

SU661550A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1124284A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Матричное устройство для извлечения квадратного корня | 1985 |

|

SU1260951A1 |

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1108440A1 |

УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ, содержащее вычислительную матрицу одноразрядных сумматоров, k-й столбец вычислительной матрицы содержит (k+1) одноразрядных сумматоров, элемент НЕ и k-2 сумматоров по модулю два (k 2, 3, ... N, где N - разрядность результата), выход i-ro сумматора по модулю два k-ro столбца соединен с первым входом (i+1)-ro одноразрядного сумматора (i 2,3, ..., k-2), выход i-ro одноразрядного сумматора k-ro столбца соединен с вторым входом (i-l)-ro одноразрядного сумматора (k+l)-ro столбца, выход первого одноразрядного сумматора k-ro столбца соединен с первым входом первого одноразрядного сумматора (k+1)-ro столбца, первыми входами всех сумматоров по модулю два (k+1)-ro столбца и вторыми входами k-x сумматоров по модулю два остальных столбцов, i-й и

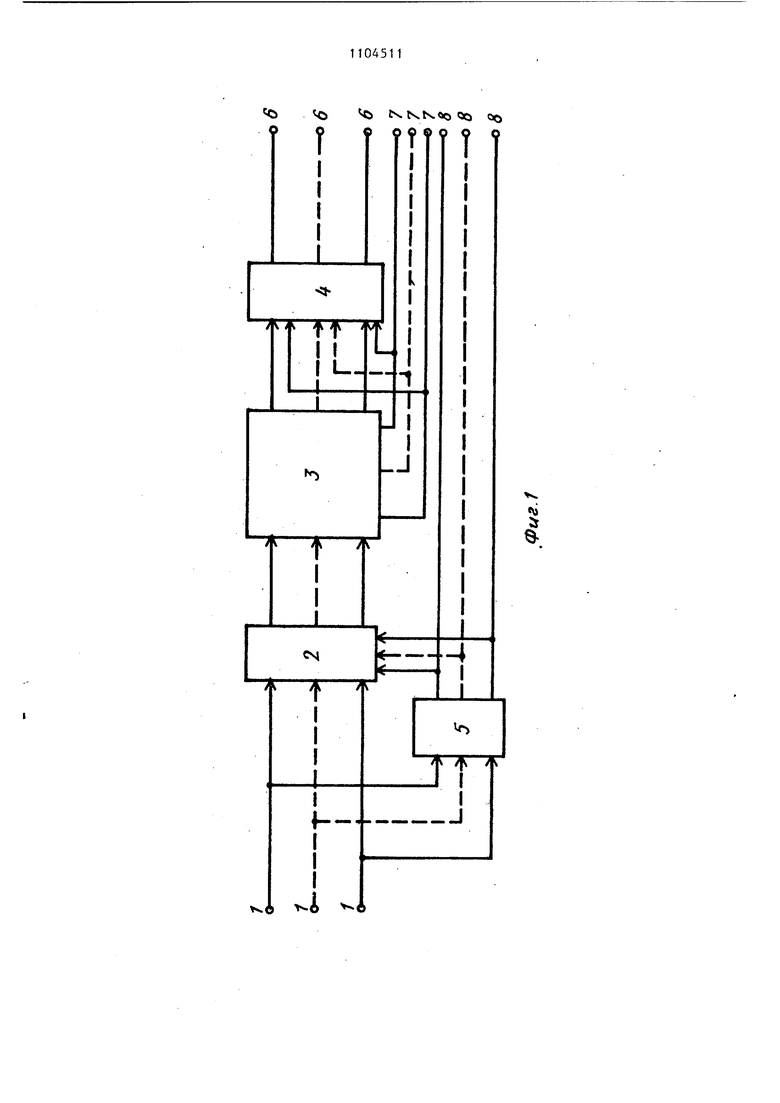

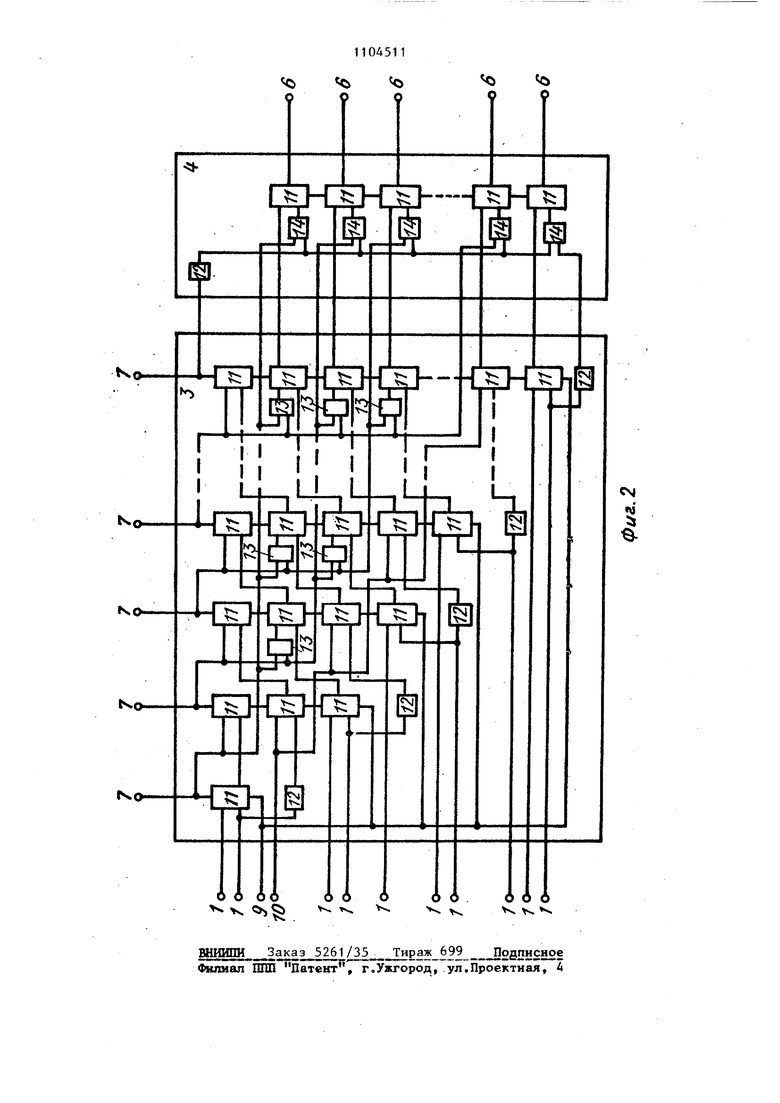

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах. Известно устройство для извлечения квадратного корня, содержащее ма рицу сумматоров-вычитателей, вход по коренного вьфажения устройства, вход нулевого и единичного потенциалов, элементы НЕ, разрядные выходы корня i Однако при вычислении квадратного корня из небольпшх чисел значительно увеличивается относительная погрешность, что приводит к тому, что в фо мате результата будет только одна ил несколько значащих цифр младших разрядов. Кроме того, вычислительная ма рица содержит сумматоры-вычитатели, обладающие низким бысТтродействием за счет переключения режима работы по сравнению с однофункциональными элементами, например сумматорами, и больщими аппаратурными затратами. Наиболее близким к изобретению является устройство для извлечения квадратного корня, содержащее вычислительную матрицу одноразрядных сумматоров, k-й столбец которой содержи k+1 одноразрядных сумматоров, элемент НЕ и k-2 сумматоров по модулю два, причем выход i-ro одноразрядног сумматора k-ro столбца соединен с входом i-1-го одноразрядного сумматора k+l-ro столбца, входы разрядов подкоренного числа устройства соединены с соответствующими входами вычислительной матрицы 2 . Недостатком известного устройства является низкая точность вычисления при мапых значениях подкоренного числа. Цель изобретения - повьшение точности вычисления квадратного,.корня. Поставленная цель достигается тем, что в устройство для извлечения квадратного корня, содержащее вычислительную матрицу одноразрядных сумматоров, k-й столбец вычислительной матрицы содержит (k+1) одноразрядных сумматоров, элементов НЕ и k-2 сумматоров по модулю два (k 2, 3, ..., N, где N - разрядность результата), выход i-ro сумматора по модулю два k-ro столбца соединен с первым входом (i+1)-ro одноразрядного сумматора (i 2,3, ..., k-2), вход i-ro одноразрядного сумматора k-ro столбца соединен с вторым входом (i-l)-ro одноразрядного сумматора (k+1)-ro столбца, выход первого одноразрядного сумматора k-ro столбца соединен с первым входом первого одноразрядного сумматора (k+1)-го столбца, первыми входами всех сумматоров по модулю два (k+1)-го столбца и вторыми входами k-x сумматоров по модулю два остальных столбцов, i-A и (i+1)-й раз4 яды подкоренного выражения устрой31ства (i 3, ..., 2N-1) подключены по парно соответственно к первому и второму входам последних одноразрядных сумматоров i-1-го столбца, 21 разряды подкоренного выражения устройства (, ..., N) соединены с входами соответствующих элементов НЕ i+1-го столбца, выходы которых соединены с первыми входами предпоследних одноразрядных сумматоров этого же столб ца, выход переноса (1+1)-го одноразрядного сумматора k-ro столбца соединен с входом переноса 1-го одноразряд ного сумматора этого же столбца, допо нительно введены коммутатор разрядов дешифратор разрядов, группа элементов И, элемент НЕ, одноразрядный сумматор в первый столбец, сумматор, входы первого слагаемого которого соединены с выходами соответствующих одноразрядных сумматоров последнего столбца вычислительной матрицы, входы второго слагаемого сумматора соединены с выходами соответствующих элементов И группы, первые входы кото рых соединены с выходами первых одноразрядных сумматоров соответствующи столбцов с первого по предпоследний, выход первого одноразрядного сумматора последнего столбца соединен с входом элемента НЕ, выход которого соединен с вторыми входами элементов И группы с первого по предпоследний и первым входом последнего элемента И группы, второй вход которого соеди нен с выходом элемента НЕ последнего столбца, вход которого соединен с младшим разрядом подкоренного числа, входы переноса последних одноразрядных сумматоров всех столбцов соединены с входом логической единицы устройства, вторые входы предпоследних одноразрядных сумматоров столбцов с 2 по N соединены с входом логического нуля устройства, первый вход одноразрядного сумматора первого столбца соединен с входом старшего разряда устройства, вход второго разряда которого соединен с вторым входом одноразрядного сумматора первого столбца, выход которого соединен с вторым входом первого одноразрядного сумматора второго столбца, выход переноса первого одноразрядного сумматора первого столбца и выходы первых одноразрядных сумматоров остальных столбцов являются соответственно выходами N старших разрядов результата устройства, выходы сумма11тора являются соответственно выходами N младших разрядов устройства, входы разрядов подкоренного числа устройства соединены с соответствующими информационными входами коммутатора разрядов и входами дешифратора разрядов, выходы которого соединены с управляющими входами коммутатора разрядов и являются выходами поряд а результата устройства, выходы коммутатора разрядов соединены с соответствующими разрядными входами вычислительной матрицы. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок-схема вычислительной матрицы одноразрядныхсумматоров и сумматора. Устройство содержит вход 1 подкоренного числа, коммутатор 2 разрядов, матрицу 3 одноразрядных сумматоров, сумматор 4, дешифратор 5 разрядов, выходы 6 младших разрядов результата, выходы 7 .старших разрядов результата, выходы 8 порядка, вход 9 логической единицы, вход 10 логического нуля. одноразрядный сумматор 11, элементы НЕ 12, сумматор 13 по модулю два, элементы И 14. Устройство работает следующим образом. Перед началом вычисления разряды подкоренного выражения по входам 1 подаются на дешифратор S разрядов. который анализирует попарно подкоренное вьфажение на наличие значащих цифр в старших разрядах входного кода и формирует код 8 порядка результата, который также управляет работой коммутатора 2 разрядов таким образом, что при наличии значащих цифр в первой, второй и т.д. паре цифр подкоренного выражения к первому, второму, третьему и т.д. входам подкоренного выражения вычислительной матрицы 3 подсоединяются соответственно первый, третий и т.д., второй, четвертый и т.д., третий, пятый и т.д. входы 1 подкоренного выражения устройства, которые затем заносятся попарно на входы одноразрядных сумматоров 11 младших разрядов катвдого столбца матрицы 3 одноразрядных сумматоров, на входы переноса которых постоянно подается 1. В первом столбце матрицы осуществляется сложение первых двух старших цифр подкоренного выражения и логической 1, поступающей на вход переноса, что равнозначно сложению первой пары цифр с кодом 11, Выход переноса одноразрядного сумматора 11 первого ртолбца является выходом старшей цифры результата d|. На выходе элемента 12 НЕ и одноразрядного сумматора 11 (первого столбца формируется код ос|татка, который подается на входы одно разрядных сумматоров 11 двух старших разрядов второго столбца, а на входы одноразрядного сумматора 11 младшего разряда второго столбца подается сле дующая пара цифр подкоренного выражения. Во втором столбце матрицы осуществляется сложение остатка с приписанной к нему справа второй парой цифр подкоренного выражения с кодом Id, 11, если первая цифра результата d 1, ис кодом О d,11, если первая цифра результата d. 0. Выход пе реноса одноразрядного .сумматора 11 старшего разряда второго столбца матрицы 3 одноразрядных сумматоров является второй цифрой результата dj Сдвинутый на один разряд в сторону старших разрядов код остатка подаетс на входы одноразрядных сумматоров 11 старших разрядов третьего столбца, а на входы младшего одноразрядного сумматора 1i этого столбца подается следующая пара цифр. В третьем столбце происходит сложение остатка с при писанной к нему справа третьей парой цифр подкоренного выражения с кодом d, d 11, если вторая цифра результата dj 1, и с кодом О 11, если вторая цифра результата d2 0. Выход переноса одноразрядного сумматора 11 старшего разряда третьего столбца является третьей цифрой результата d. Поскольку при d 1, d2 О, а при dy О, третья, начиная с младшей, цифра кода второго слагаемого всегда равна 0. Таким образом, на первые входы второго, начиная с младшего одноразрядного сумматора 11 каждого столбца, подается уровень логического нуля. Затем код остатка третьего столбца со сдвигом на один разряд в сторону старших разрядов подается на входы одноразрядных сумматоров 11 старших разрядов четвертого столбца и т.д. Инвертирование цифр результата в зависимости от последней цифры результата осуществляется с помощью сумматоров 13 по модулю два. На последнем п столбце одноразрядных сумматоров 11 вычислительной матрицы происходит сложение кода остатка предыдущего столбца, сдвинутого на один разряд в сторону старших разрядов, с приписанной справа последней парой Цифр подкоренного выражения с кодом 1 d d2, , d. 2 если предпоследч няя цифра результата d., 1, и с кодом 1 d,, djjd.2 Oil, если предпоследняя цифра результата d. 0. Выход переноса одноразрядного сумматора 11 старшего разряда последнего столбца является последней цифрой результата d. Сдвинутый на один разряд в сторону старших разрядов код остатка вычислительной матрицы 3 подается на входы блока восстановления остатка, что необходимо для восстановления истинного значения остатка в случае, когда последняя цифра результата d 0. Восстановление остатка происходит путем суммирования на одноразрядных сумматорах 11 кода остатка R,R2R,R, ..., R со значением d,d2d,d4, ..., d,, R,, при df, О и с нулевым кодом при d, 1. Указанные коды формируются с помощью элементов 14 И. На выходах 6 сумматоров 11 , появятся п разрядов восстановленного остатка, которые являются п младшими разрядами кода результата вычисления квадратного корня. Предлагаемое устройство для извлечения квадратного корня обладает более высокой точностью вычисления результата. Уменьшение относительной погрешности осуществляется за счет сдвига подкоренного выражения в сторону стар ших разрядов до появления значащих циф в одном из двух старших разрядов, чем уменьшается диапазон изменения „ подкоренного вьфажения 2 $ X 2 . Использование остатка вычислительной матрицы в качестве младших цифр корня уменьшает также абсолютную погрешность вычисления квадратного корня.

«

;:$

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 754411, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для извлечения квадратного корня | 1979 |

|

SU857981A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-23—Публикация

1983-02-07—Подача